### Verifying Layered Protocols – Leveraging Advanced UVM Capabilities

Parag Goel Sr. Corporate Application Engineer Synopsys India Pvt. Ltd.

# **SYNOPSYS**<sup>®</sup>

**Accelerating Innovation**

## Stack based architecture

- Reasons for adoption

- Breaking network designs into functional layers

- Enables each layer to be governed by simple protocols

- Each with a few well-defined tasks

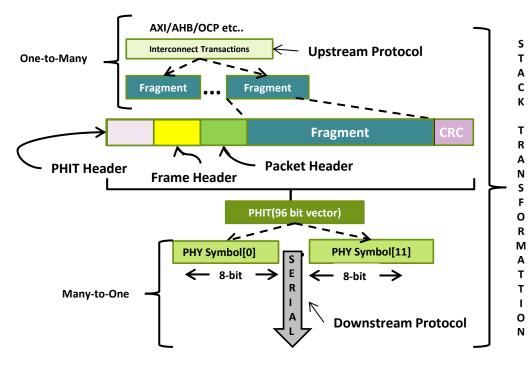

#### Signaling Interconnect Application saction Fragments Adaptation Laver Presentation 6 Session 5 Packets SAP-based Transport communication LLI Stack Network 3 Specification Frames Data Link -> 2 PHITs -> Symbols Physical Physical Media

### Easier Debug

- Faster convergence to where network failures originate

- The same user-level (application) program can be used over diverse communication networks.

- Same WWW browser can be used when you are connected to the internet via a LAN or a dial-up line.

### Agenda

### Verification IP & Testbench Challenges

- Architectural Challenges

- Stimulus generation Generate varied traffic corresponding to each layer

- Visibility and granularity of control retrieving transaction for analysis

- Support for intermediate layer and multi-lane scenarios

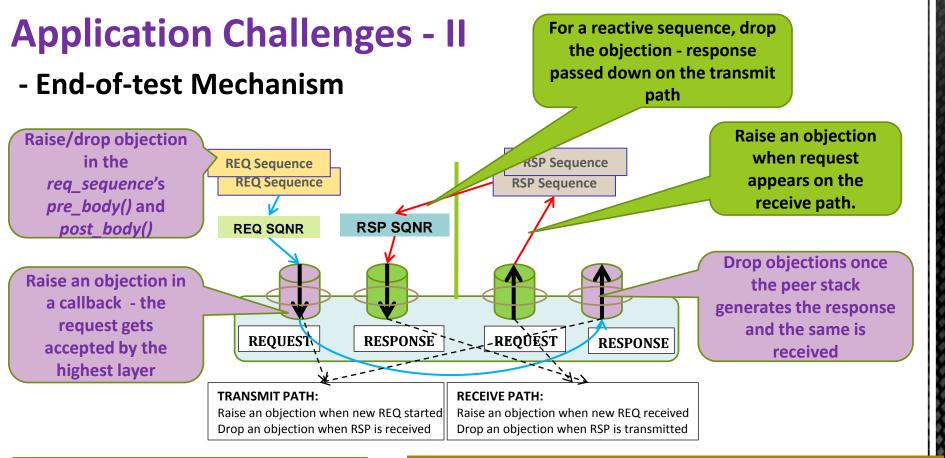

- Application Challenges

- Verifying Transformations

- Graceful End-of-test

- Enough debugging hooks

### Need to map verification challenges to existing methodologies

- Leverage available methodology capabilities

- Build intelligent layers around base classes for more powerful verification setup

### **Architectural Challenges - I**

#### - Stimulus Generation

- Ability to inject stimulus at any layer

- It should be possible to configure any of the layers as top-most layer generating the highest upstream sequence.

- Ability to arbitrate, i.e. mix and match stimulus from the upper layer as well as from the testbench

Ability to retrieve and modify the transaction at any specific layer via callbacks, factory mechanism and UVM command-line override.

### **Architectural Challenges - II**

#### - Verifying intermediate layer

Appropriate hooks/callbacks/ports for each component

- Retrieve the transactions from any layer

- Provision to hook up intermediate custom drivers which can then drive the interface between the layers.

- Callbacks across monitors to verify transformations across the layers.

### **Architectural Challenges - III**

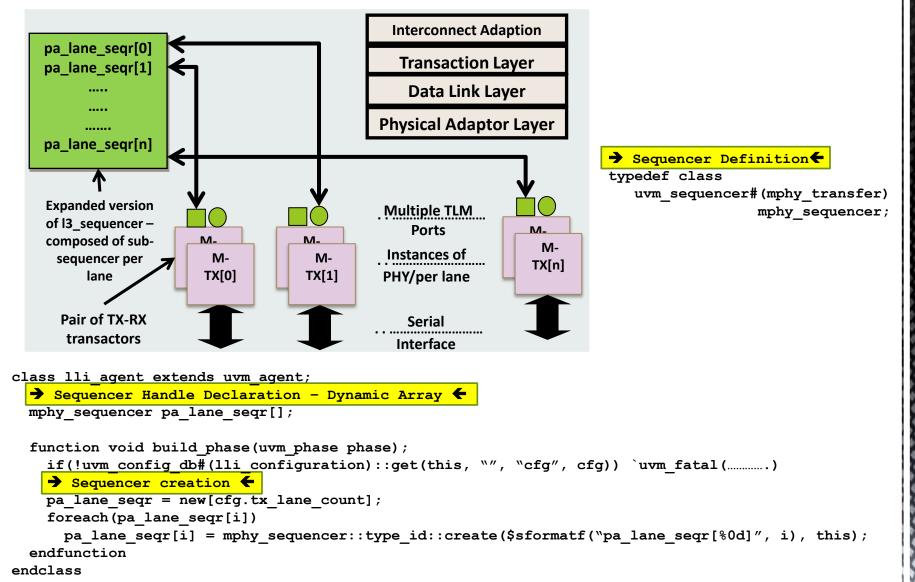

- Verifying multi-lane scenarios

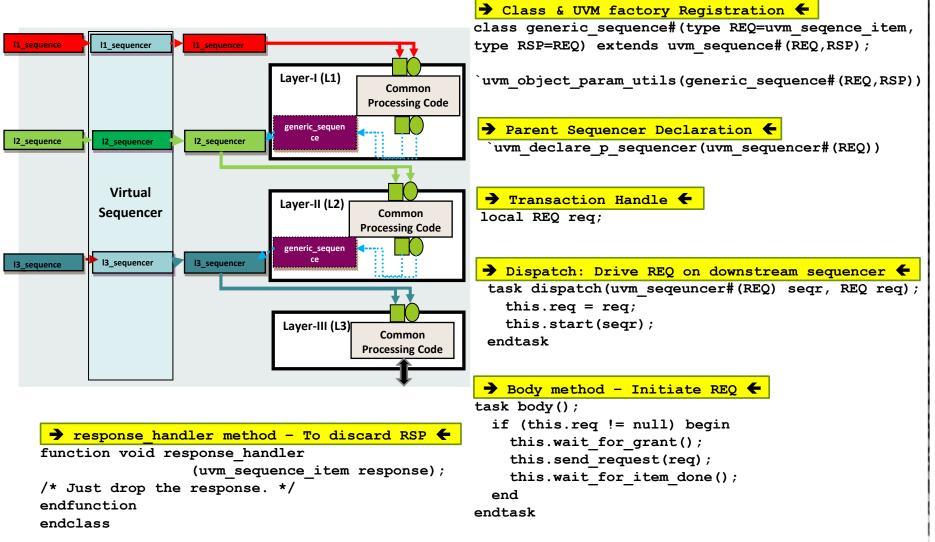

### **Addressing Architectural challenges - I**

#### - Generic architecture

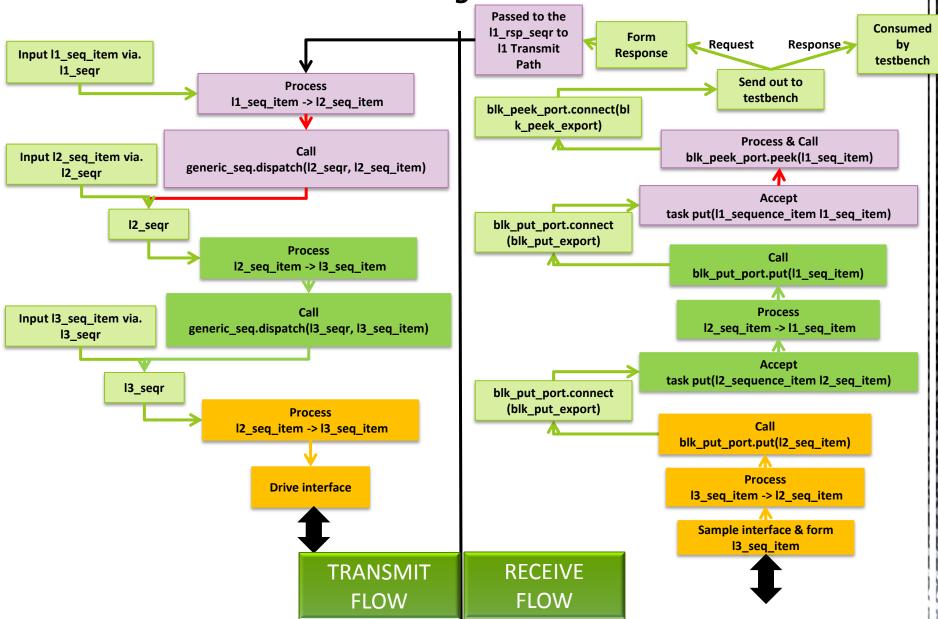

### **Addressing Architectural challenges - II**

#### - Generic architecture – Flow Diagram

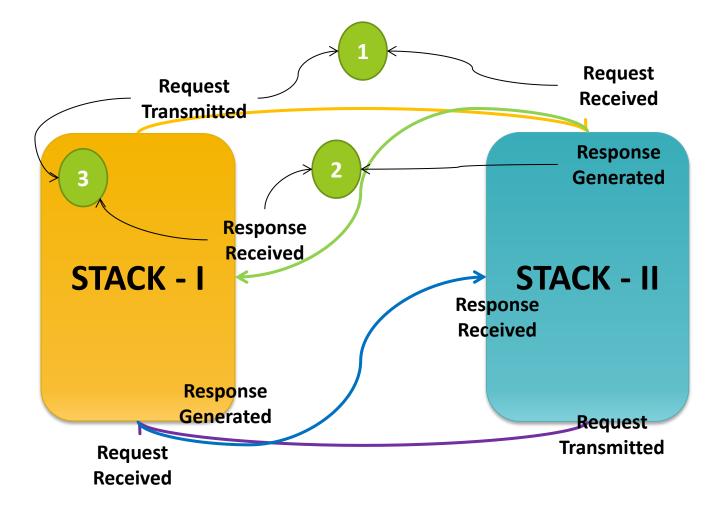

### **Application Challenges - I**

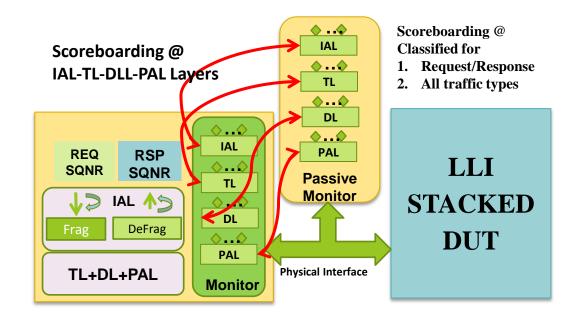

#### - Scoreboarding Challenges - I

Transformations that would need to be verified

- End to end transformations in the 'transmit' and 'receive' paths

- Transformations across all the traffic types

- For requests / responses

### **Application Challenges - I**

- Scoreboarding Challenges - Checking for equivalence

### **Addressing Scoreboarding Challenges**

Policy Based design :

- template taking several type parameters

- specialized to encapsulates orthogonal aspects of the behavior of the instantiated class

```

class lli_comp #(type T = int);

static uvm_comparer relevant_comparer = new();

static function bit comp(input T a, input T b);

relevant_comparer.physical = 1;

relevant_comparer.abstract = 0;

return a.compare(b, relevant_comparer);

endfunction

endclass

```

➔ Reporting results ←

class lli\_system\_env extends uvm\_env;

```

typedef lli_scoreboard#(svt_mipi_lli_transaction)

trans_scbd;

typedef lli_scoreboard#(svt_mipi_lli_packet)

pkt_scbd;

```

An instance of VIP AGENT - LLI Master/Slave svt\_mipi\_lli\_agent mstr, slv;

```

→ IAL Scoreboard Instances for request xact ←

trans_scbd m_s_ll_xact_sb;

trans scbd m s be xact sb;

```

```

Construct the IAL scoreboard instances

m_s_ll_xact_sb = new("m_s_ll_xact_sb", this);

m_s_be_xact_sb = new("m_s_be_xact_sb", this);

```

mstr.ial\_mon.tx\_ll\_ta\_xact\_observed\_port.

```

connect(m_s_ll_xact_sb.tx_export);

```

slv.ial\_mon.rx\_ll\_in\_xact\_observed\_port.

```

connect(m_s_ll_xact_sb.rx_export);

```

```

connect(m s be xact sb.rx export);

```

```

endclass

```

#### Drain Time - Amount of time to wait once all objections have been dropped

```

int stack_round_trip_time;

```

```

task main_phase(uvm_phase phase);

phase.phase_done.set_drain_time

(this, 2*stack_round_trip_time);

endtask

```

# **Global timeout** - The phase ends if the timeout expires even before all objections are dropped

```

`define HS_MODE_GLOBAL_TIMEOUT 5ms

`define LS_MODE_GLOBAL_TIMEOUT 25ms

function void test_base::build_phase(...);

→ Set the global timeout ←

if(sys_cfg.mode == LS_MODE)

set_global_timeout(`LS_MODE_GLOBAL_TIMEOUT);

else

set_global_timeout(`HS_MODE_GLOBAL_TIMEOUT);

endfunction

```

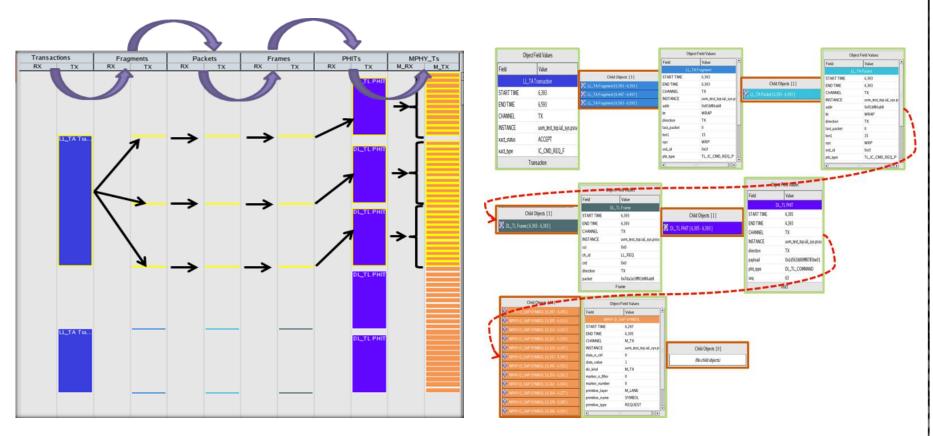

### **Application Challenges - III**

#### - Debug Abstraction

- Tracing the transformation across each layer

- Needs to be captured through TLM ports and dumped for Post processing

- Debug abstraction : Dumping of protocol objects

- Use transaction IDs to map across transformations

### **Summary**

- Layered architecture in network protocols bring in advanced functionalities but complex verification challenges

- Can be mapped across multiple new protocols (the MIPI family, PCIe, USB etc) and network designs

- UVM base classes provides the infrastructure on which required capabilities can be built

- user defined enhancing sequence layering, phase completion tracking, transformation monitoring

- Verification infrastructure should continue to evolve with added complexity in design