# **Verification of a Multi-language Components**

A case Study: Specman E Env with SV UVM VIP

Eran Lahav eranl@veriests.com

**SYSTEMS INITIATIVE**<sup>™</sup>

## Introduction

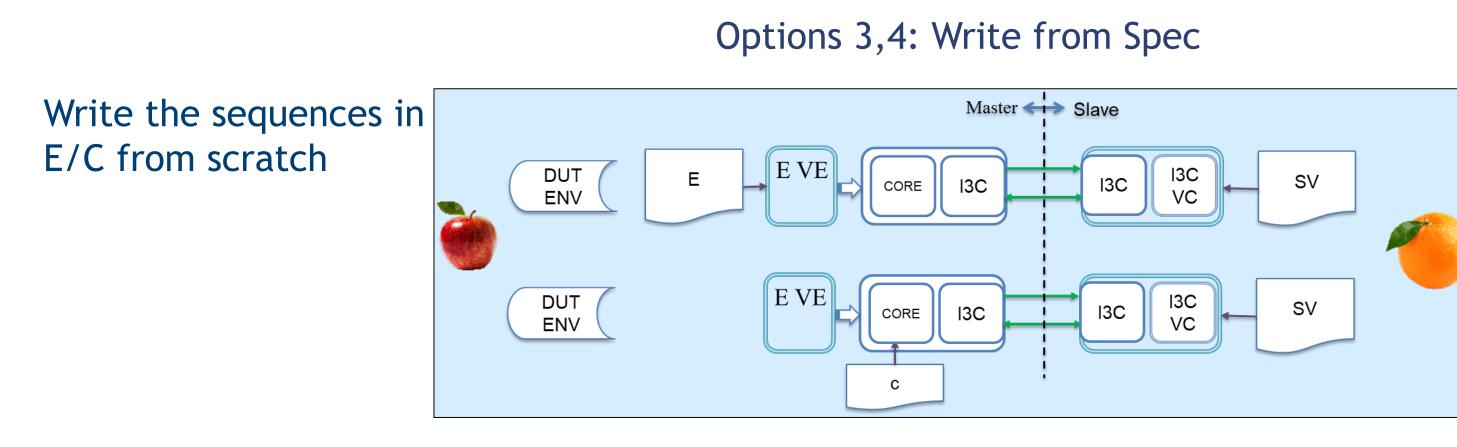

Multi-language Verification requires special considerations: Synchronization of test phases and events and moving data objects between the language's worlds. In some cases, re-writing part of the code, (either manually or automatically) could be a more reasonable solution. In this paper, we discuss the trade-off between the two alternatives: re-write the code and co-running with original languages.

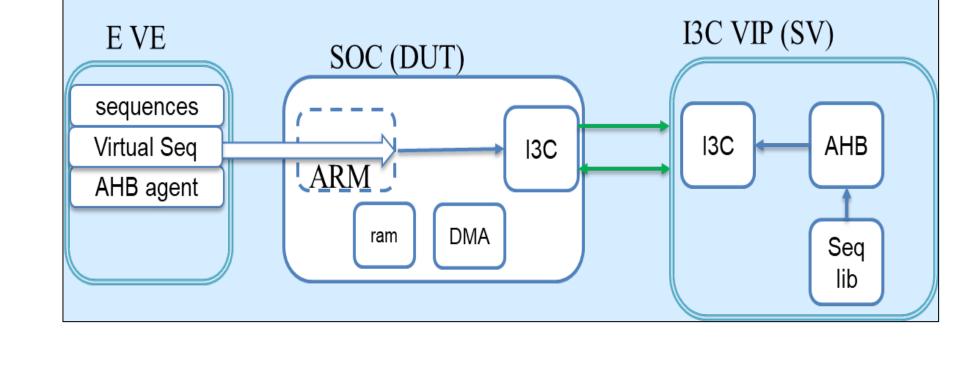

### The System

SOC with peripheral I3C, Driven by ARM trough

### **Configuration and Execution Options**

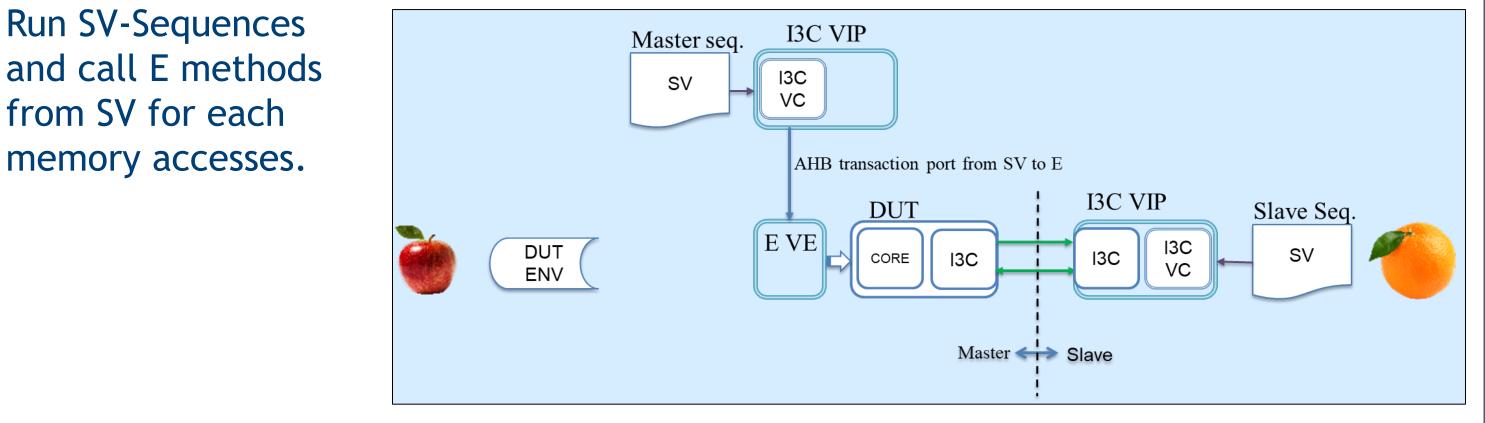

Translate SV-UVM VIP sequences to E and use them within the SoC virtual sequences

#### Master Seq. I3C VIP Slave Seq. I3C I3C VC I3C Stand SV I3C I3C Alone ENV sv E I3C VIP E VE DUT Slave Seq. DUT ENV I3C VC I3C I3C CORE Master 🔶 Slave

DESIGN AND VERIFICAT

**CONFERENCE AND EXHIBITION**

ELROPE

- Full E environment for SOC, including configurations, registers model, sequence, interrupt handling, bus drivers, etc.

- **I3C UVM VIP from** external vendor.

#### Consideration Compare Translation/Rewrite vs. co-run Rewrite Write in Notes Translate UVM

### Translation

Sequences translation was done with Python program:

- RAL to Specman register (vr\_ad like)

- UVM sequence library to E sequences (mostly body() task to body() TCM)

- It covers only small portion of the Language and uses shortcuts (as macro translation instead of expand)

- Neither all cases nor all commands are supported (less then 10%)

- It took 3-person week to complete

- We estimate a full SV to E Translator to require one person-year

## **Synchronization**

| 1 | $\Box$ ( | $\mathbf{C}$ | ~ | $\sim$ |

|---|----------|--------------|---|--------|

|   |                          |                                                        | to E | execute | from<br>Spec | С    |

|---|--------------------------|--------------------------------------------------------|------|---------|--------------|------|

| 1 | Coding<br>Effort         | Of Sequences                                           | MED  | LOW     | HIGH         | HIGH |

| 2 | Env Effort               | Test flow                                              | LOW  | HIGH    | LOW          | LOW  |

| 3 | Tests<br>Debug<br>Effort |                                                        | MED  | LOW     | HIGH         | HIGH |

| 4 | Preserve<br>Test Suit    | Run exact Vendor scenario and checks                   | HIGH | FULL    | LOW          | LOW  |

| 5 | Flexibility              | Running a different<br>scenario. Post silicon<br>debug | LOW  | LOW     | HIGH         | MED  |

| 6 | SW<br>reusability        | Using sequences as reference to SW                     | LOW  | LOW     | MED          | HIGH |

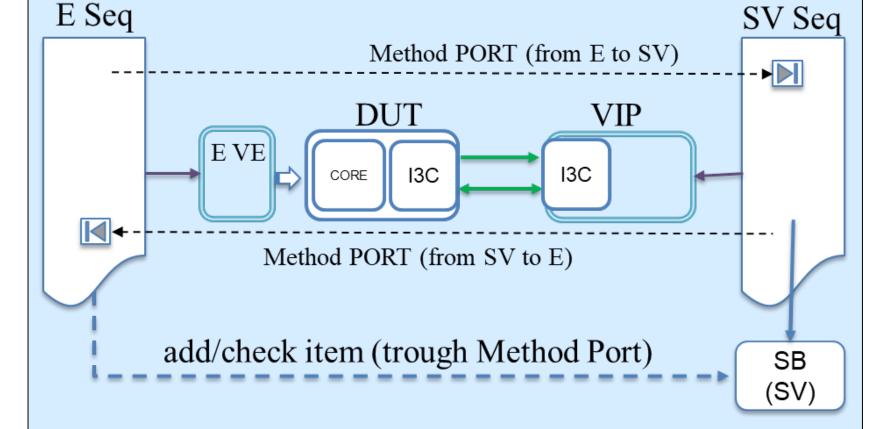

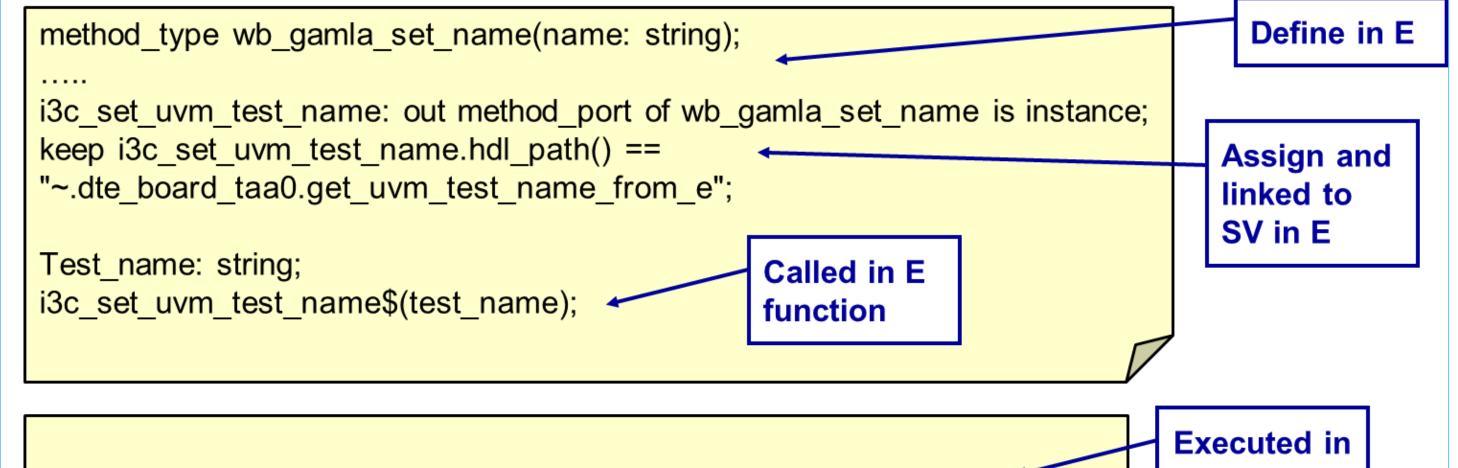

Synchronization between sequences and data objects between languages can be done either by E method ports or by TLM (Transfer Level Model) ports.

## **Code Examples**

## Conclusions

Combining a component with a different language into an existing verification environment depends on the characteristics of the system and the verification requirement. In some cases, partially translation can be more efficient and time/cost-effective than applying a standard language-tolanguage porting. We found that for sequences, particularly for those which produce memory access command, translation of the code is beneficial.

Using UVM-ML Open Architecture is a valuable way to connect

function void get\_uvm\_test\_name\_from\_e(string name);

sv\_test\_name = name; \$display(\$sformatf("I3C DTE Test is %s",sv\_test\_name)); endfunction

and run together components with different languages. Yet, the implementation of these kinds of systems requires a special attention for synchronization. Ports (TLM) between the components should close this gap and enable effective verification.

Project was done in collaboration with **Nuvoton** Technologies

© Accellera Systems Initiative