# UVM Testbench Considerations for Acceleration

Kathleen A Meade Cadence Design Systems, Inc

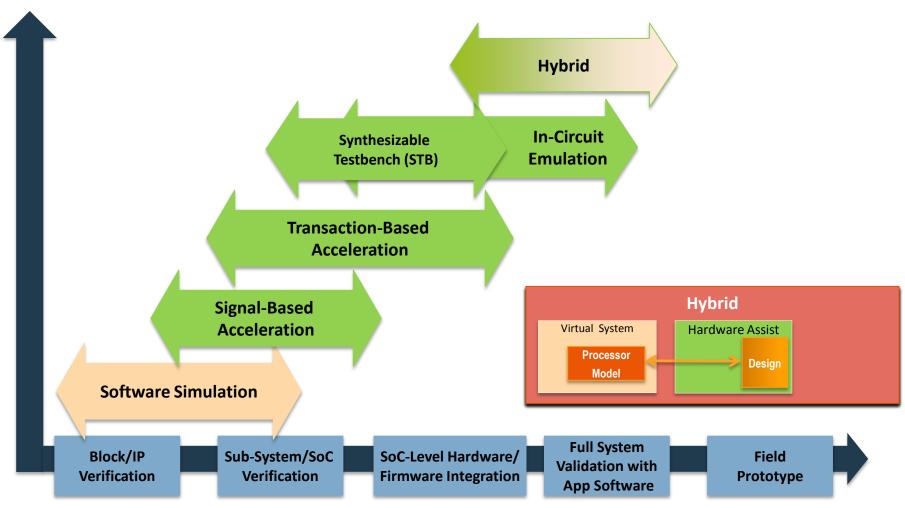

## Hardware-Assisted Verification Use Modes

Performance

# **Objectives of UVM Acceleration**

UVM provides methodology for verifying complex designs with a focus on reuse

- Reuse of verification components and environments between simulators and hardware acceleration is gaining momentum

- This session introduces methodology techniques for creating acceleration-friendly UVM environments

- Makes migration from simulation to acceleration much easier

- Will not have a negative impact on performance for pure simulation

- Ultimate goal: Enhance simulation performance to run more cycles and achieve desired coverage faster

#### Agenda

The following topics will be covered:

- Partitioning the top-level into a hardware and software top module

- Separating your UVM *monitor* into a *collector* (for signal-level information) and a *monitor* (for checking/coverage)

- Limiting access between the DUT and the testbench.

- Creating synthesizable interface tasks to:

- Take transactions and drive signals (*driver*)

- Reassemble transactions from signal-level details (*collector*)

- Removing timing from sequences

# Is Hardware Acceleration a Good Option?

Hardware Acceleration can improve performance to 300x (or more)

- Profile your environment with a long simulation runtime

- Check that a significant portion of time is being spent in the DUT

- Acceleration is usually not a good option for environments where the testbench time is significant and the DUT time is small

- Acceleration is also not a good option if your simulation runtimes are short

- Consider grouping short tests into one longer test with automatic checking

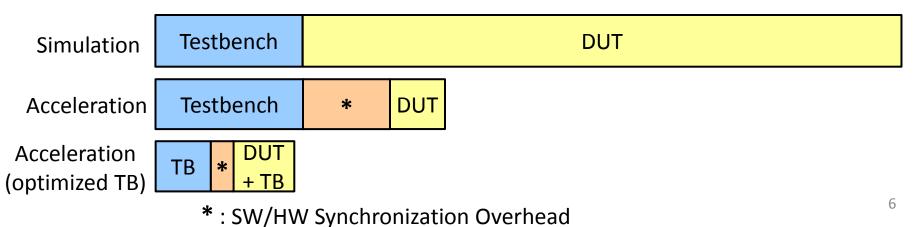

# **Acceleration Performance**

- The main factors in determining performance potential:

- <u>Testbench Runtime</u> Time spent in the simulator, including configuration and building of the UVM verification environment and DUT, driving stimulus, checking and sampling coverage

- <u>SW/HW Synchronizations</u> Signals and transactions sent between the UVM Testbench and DUT

- <u>DUT Runtime</u> Includes any aspect of the design (and testbench) that is executed on the acceleration hardware

# Analyzing Profile Results – An Example

Profiling a simulation run – for acceleration: Testbench takes 25% of simulation time DUT takes 60% Synchronization estimation is 15%

Maximum performance boost, if the DUT time is reduced to zero is:

HW\_TIME = 60% + 60%\*15% = 69%

Estimated speed-up (no opt) = 100/(100-HW\_TIME) = 3.2X

Increasing DUT time to 90% and reducing sync overhead to 5%:

HW\_TIME = 90% + 90%\*5% = 94.5%

Estimated speed-up = 100/(100-94.5) = 18.2X

Further testbench optimizations can be made for even better performance

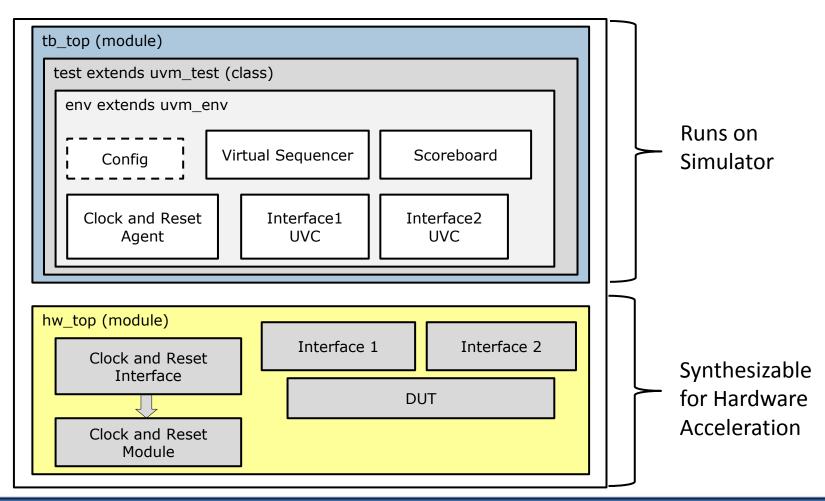

# Partitioning Your UVM Environment

• Partition your top-level module so the DUT and synthesizable components are in one module and the UVM testbench is in a separate module

8

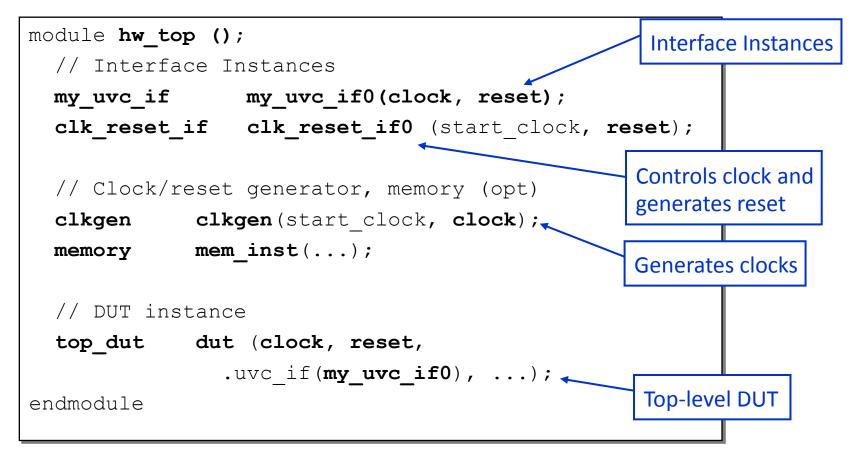

# Hardware Top-Module Example

• Includes the DUT instance, a clock generator, SystemVerilog interfaces and (optional) memory

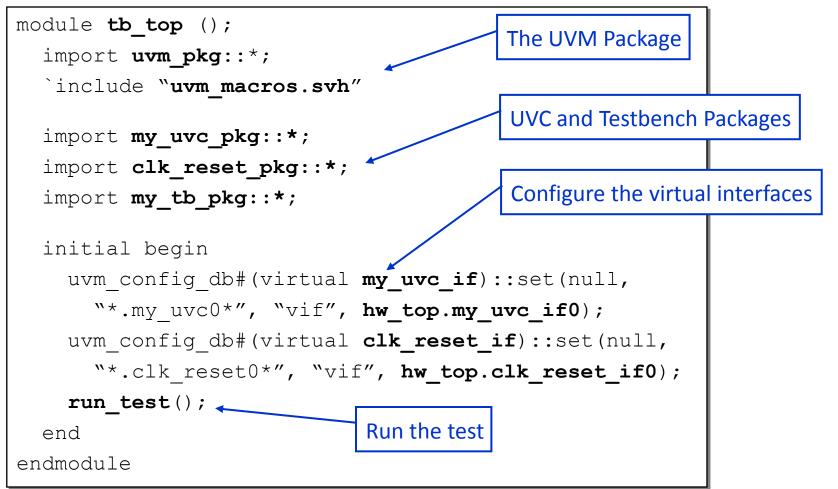

# Testbench Top-Module Example

Includes the UVM package, user-defined UVC packages, the toplevel testbench and test files and an initial block to configure and

10

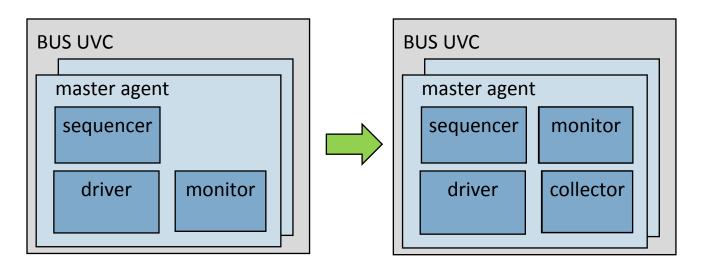

# Implement a Collector/Monitor Pair

- A UVM *monitor* to captures transactions from the DUT interface, performs checking, coverage & sends them to other components

- Split the monitor into a *collector* class for capturing signals and forming transactions and a *monitor* for transaction-level checking and coverage

- Similar to the *sequencer/driver* pair for creation of stimuli

#### Monitor/Collector Interaction

```

class my uvc monitor extends uvm monitor;

uvm analysis imp#(my uvc trans, my uvc monitor)

item in port;

uvm analysis port#(my uvc trans) item out port;

endclass

class my uvc collector extends uvm component;

uvm analysis port

uvm analysis port#(my uvc trans) item out port;

endclass

Monitor

class my uvc agent extends uvm agent;

uvm analysis imp

my uvc monitor

monitor;

uvm analysis port

my uvc collector collector;

//create in the build phase

Collector

// connect in the connect phase

collector.item out port.connect(

Monitor-Collector

monitor.coll in port );

Interaction

12

endclass

```

# Minimize Testbench and DUT Interaction

- Every interaction between the DUT and testbench initiates a synchronization event

- Limit interaction to the *collector* and *driver* only

- All other interactions must be addressed when the testbench is migrated to run on acceleration

- Identify: Two common places where this is found:

- Waiting for signals to change inside a sequence

- Waiting for reset not as critical as reset does not happen very often

- Address: Add a clock and reset agent and/or an interrupt agent to limit access to these signals and generate events related to them

# Signal-Based vs Transaction-Based

#### Acceleration

Usually the first step in migration

- Signal-based acceleration:

- Partition the UVM testbench to the simulator move the DUT to the hardware side

- Takes less time to implement and can produce results in the 3x-20x range

- Transaction-based acceleration:

- Part of the testbench is also moved to the hardware accelerator

- Interface between the testbench and the DUT is through task calls

- Reduces the number of synchronizations and can produce results in the 20x-300x range!

- Goal is to develop your testbench environment to be conducive for transaction-based acceleration (TBA)

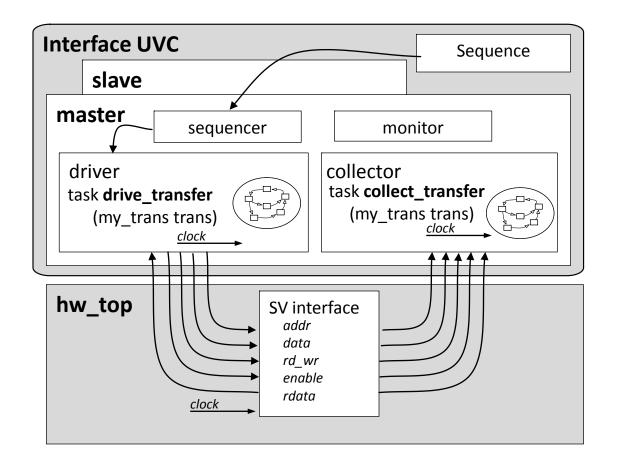

# Traditional UVC Structure

• Signals driven and clocks referenced from driver and collector class through a virtual interface handle

# UVM Driver Class – drive\_transfer() Task

• Signals driven and clocks referenced from driver and collector class through a virtual interface handle

```

class my uvc driver extends uvm driver;

task drive transfer(my trans type trans);

@(posedge vif.clock iff vif.reset)

vif.addr <= trans.addr;</pre>

vif.data <= trans.data;</pre>

vif.rd wr <= (trans.dir == READ) ? 1'b0 : 1'b1;

vif.enable <= 1'b1;</pre>

@(posedge vif.clock)

if (trans.dir == READ)

Virtual interface interactions

trans.data = vif.rdata;

cause a synchronization event

vif.enable <= 1'b0;</pre>

endtask

endclass

```

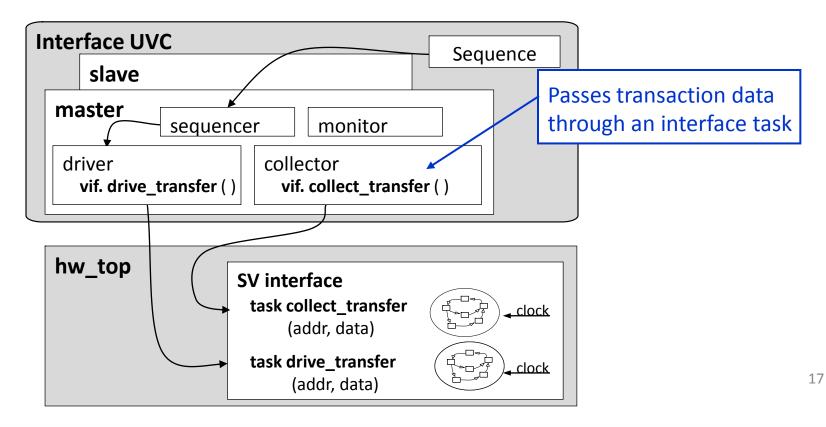

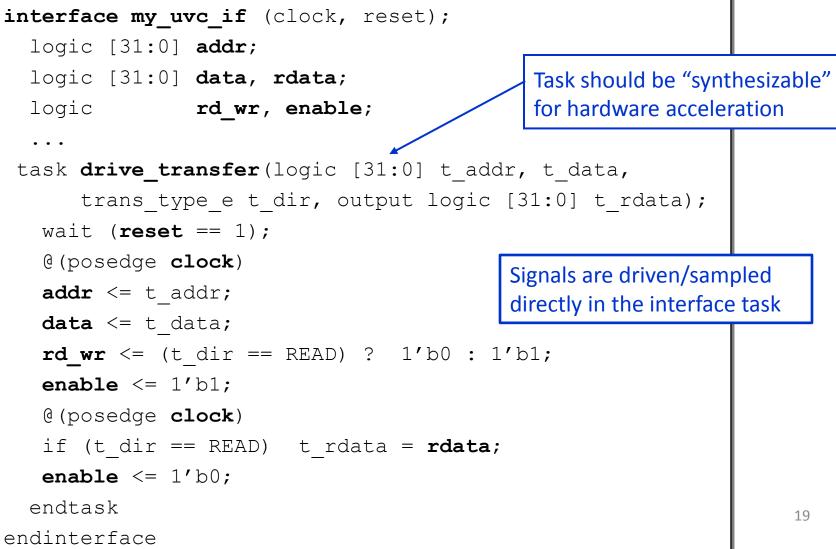

# Accelerated UVC Structure

- Driver and collector call time-consuming interface tasks.

- Signals driven and clocks referenced directly in the interface (synthesizable)

# UVM Driver Class – drive\_transfer() Task

- The driver's *drive\_transfer* task calls a time-consuming interface task

- Data fields can be passed directly or converted to a packed struct

```

class my_uvc_driver extends uvm_driver;

...

task drive_transfer(my_trans_type trans);

logic [31:0] rdata;

vif.drive_transfer(trans.addr,

trans.data,

trans.data,

trans.dir, rdata);

trans.data = rdata;

endtask

endclass

```

#### UVC Interface – drive\_transfer() Task

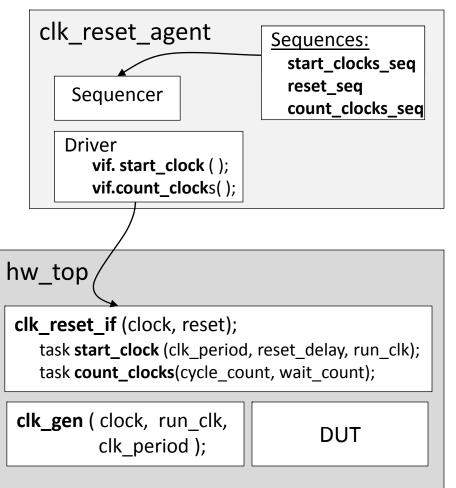

#### **Clocks and Reset**

- Clocks are critical in designing for acceleration

- They toggle frequently and cause synchronization events

- Implement a reusable agent to configure clocks, initiate resets and execute delay sequences from the testbench

- The implementation details are in a SV interface and are executed on the hardware

#### **Clock and Reset Item and Driver**

// `uvm\_component\_utils and constructor

// Get the vif in the connect\_phase

```

class clk_reset_item extends...;

rand int clk_period;

rand int reset_delay;

rand int cycle_count;

rand bit wait_count;

rand bit run_clk;

...

endclass

```

# **Removing Timing From Sequences**

- For optimum performance remove timing from the testbench

- Includes references to clocks and #delay's

- Waiting on transition of a DUT signal

- Use alternate methods of specifying delays within and between sequences

- Include a *delay\_clocks* task inside your interface UVC to delay clocks within a UVC sequence

- Use a clock and reset agent to execute sequences which starts the clocks and initiates resets (*start\_clocks\_seq*)

- Also use the clock and reset agent to execute a sequence

(count\_clocks\_seq) for clock delays (blocking) or timeouts

# Virtual Sequence with # Delays

```

class traffic vseq extends uvm sequence;

// `uvm object utils and constructor

// Interface UVC Sequences

my uvcl config seq uvcl config seq;

my uvc2 traffic seq uvc2 traffic seq;

task body();

#100 // Wait 100ns for reset to finish

// Configure via UVC 1

`uvm do on(uvcl config seq, p sequencer.uvcl master seqr)

// Run some traffic on UVC 2

`uvm do on(uvc2 traffic seq, p sequencer.uvc2 master seqr)

// Wait 30 clocks (300ns) to end simulation

#300;

endtask

endclass

```

# Virtual Sequence with Clock Sequences

```

class traffic vseq extends uvm sequence;

// `uvm object utils and constructor

// Other sequences: uvcl config seq, uvc2 traffic seq

start clocks seq clock seq;

count clocks seq delay seq;

// Other Sequences

task body();

// Start clocks and initiate reset

`uvm do on with(clock seq, p sequencer.clk reset seqr,

{ clock seq.clock period == 10;

clock seq.reset delay == 10;

clock seq.run clock == 1; } )

// Configure, run traffic

// Wait 30 clocks (#300) to end

`uvm do on with (delay seq, p sequencer.clk reset seqr,

{ delay seq.clock cycles == 30;

delay_seq.wait_count == 1; }

endtask

```

**DESIGN & VERIFICATION**

#### Summary

- Hardware acceleration of verification environments for performance is gaining momentum

- Spending time up front to construct UVM environments that are easily portable to hardware acceleration can reap big performance benefits

- The UVM recommendations introduced in this module

- Makes migration from simulation to acceleration much easier

- Will not have a negative impact on performance for pure simulation

- Enhance simulation performance to run more cycles and achieve desired coverage faster