# UVM/SystemVerilog based infrastructure and testbench automation using scripts

Prakash Parikh, Aquantia Inc., 700 Tasman Drive, Milpitas, CA pparikh@aquantia.com

#### Abstract :

Universal Verification Methodology (UVM) and SystemVerilog based testbenches are widely used in many of the new ASIC starts. Quite a few legacy Verilog based testbenches, Vera, Testbuilder, Specman "e" and SystemC based testbenches are being migrated to UVM based testbenches. Developing UVM based testbenches and infrastructure from scratch is time consuming and requires a good understanding of Object Oriented Programming from the entire team responsible for UVM based verification. Automation for block and top level verification testbenches based on Perl or C shell scripts can provide powerful methods to get the block and top level infrastructure ready in a short period of time while various verification team members get familiar with new concepts of UVM based verification methodology. This allows extra time for verification engineers to focus more on actual block verification aspects instead of spending more cycles on infrastructure development.

This paper discusses how the DSP (Digital Signal Processing) verification environment for the 10GBase-T chip was generated using the perl scripts. Further, it discusses how the driver, monitor, sequences, sequencer, agent, env and test classes generated from scripts. Finally it discusses how the verification is performed and how coverage data are generated.

## I. INTRODUCTION:

As UVM and SystemVerilog become more widely adopted in the industry, companies need to schedule significant amounts of time for their engineers to master the learning curve inherent in UVM, SystemVerilog, and even object-oriented programming. Worse, it is easy for engineers to make mistakes when coding up the first project in a new language. These mistakes cost debug time and can affect testbench coverage and quality. Also, whenever a testbench is composed of checkers coded up by more than one engineer, top level hookups can be inconsistent and error prone.

One way to mitigate some of the schedule and quality issues is to use a scripting based approach to create the top level and even some of the lower level structural code used in the system. This ensures a uniform coding style, consistent hookups, and enables the verification engineers to spend more time focusing on the actual block/system verification instead of infrastructure development.

There are two options available at the beginning of the project to create a verification environment. The first approach is to create individual block level environments hand coded from scratch and then stitch individual block level environment to create the top level environment. None of the code can be reused in this approach. The time it takes to create such an environment is proportional to the number of blocks in the environment. The second approach is to take advantage of similarity in the different blocks functionality that need to be verified and use scripting methods to generate various UVM components template codes and create uniform block level environment that is easily scalable to top level environment. The approach of generating infrastructure using scripts was followed for creating a DSP based verification environment.

### II. TOP LEVEL DSP SYSTEM:

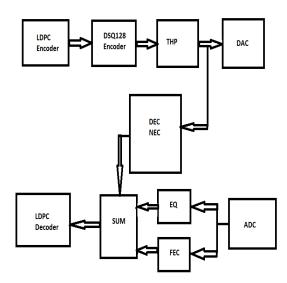

The following diagram (Figure 1) shows a typical block diagram of the DSP based system for which the UVM infrastructure was developed.

Figure 1: Block Diagram of the DSP system

Data Flow for the system shown in Figure 1 above is described below.

► The LDPC (Low density parity check) encoded data gets mapped to DSQ (Double Square Constellation) symbols.

► THP (Tomlinson Harashima Precoder) operation is performed on the mapped symbols.

► The transmit data is sent out after the DAC (digital-to-analog converter) operation.

► On the received side, the received data after ADC (analog-to-digital conversion) passes through EQ

(Equalization) and FEC (Far end cross talk cancellation).

► DEC (digital echo cancellation) and FEC (Far end cross talk cancellation) filtering is performed and output of DEC and NEC is added to the received data that undergo the EQ (Equalization) and FEC (Far end cross talk) filtering.

► The received data after DEC/NEC/EQ/FEC cancellation get decoded by LDPC decoder.

## III. UVM TESTBENCH FOR DSP SYSTEM:

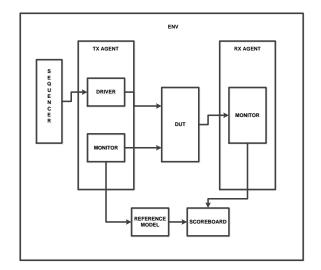

The following diagram (Figure 2) shows UVM agent for individual FFE/FEC/DEC/NEC filter blocks. This follows standard UVM methodology for block level testbench and infrastructure development.

Figure 2: Block level Environment

Each block level environment instantiates both a transmit agent and a receive agent. The Transmit Agent instantiates driver and transmit monitor. The Receive Agent instantiates receive monitor. Data collected by the transmit monitor gets passed to the reference model and the reference model output data is provided to the scoreboard. The data collected by the Receive Agent monitor is also provided to the scoreboard. The scoreboard does the comparison

between the reference model data and the Receive Agent monitor data.

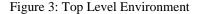

Following (Figure 3) shows a picture of top level env that instantiates various block level envs shown in Figure 2 above.

As shown in Figure 3 above, the top level DSP system instantiates FFE (Equalizer) env, FEC env, DEC env, NEC env and other miscellaneous env. For developing UVM infrastructure environment for the above complex system with strict deadlines, writing all the UVM driver, monitor, sequence, agent, etc. code for each of the block was not practical. So the following perl based methodology was used to generate each block UVM infrastructure code.

The script takes various arguments for the block specification and generates templates for the UVM

drivers. monitors, sequences, sequencers, scoreboards, coverage analysis, TX and RX agents, environments with default implementations of build, connect, run phases for each of these UVM components. As seen in the top level environment Figure 3 above, the system consists of various filters, FFE/FEC/DEC/NEC. These filters are all FIR filters but may vary in tap lengths and data and coefficients widths. The stimulus needed to verify these blocks with directed and random patterns could be similar. All the filters can use Impulse, DC, Incrementing, random, etc. patterns. Using perl scripts it is easy to generate templates for specific filters with parameters indicating name of the filter, transaction type and data and coefficients widths. The template code generated for driver, sequences and other UVM components is described in next sections.

## IV. DRIVER/MONITOR TEMPLATE CODE GENERATION :

Following shows the template of the UVM driver code generated using the script for the DSP chip block. Figure 4 below shows portion of perl script that is used for generating the driver code. The script can take block name, transaction type, bit widths for different inputs and outputs as arguments for the driver template generation.

```

#!/usr/bin/perl

$block_name = $ARGV[0];

tx_type = ARGV[1];

gen_template($block_name);

sub gen_template {

create_header($block_name);

create_uvm_class($block_name, $tx_type);

}:

sub create_header {

printf "\n* Description :UVM driver for block

$block_name";

printf"\n********************************/\n":

};

sub create_uvm_class {

printf "\n\nclass ${block_name}_driver extends

uvm_driver # ($tx_type); \n\n";

printf "\n

`uvm_component_utils(${block_name}_driver)";

printf "\n $tx_type tx_data;";

printf "\n virtual interface ${block_name}_if_data_input

dif data;";

```

printf "\n virtual interface \${block\_name}\_if\_ctrl\_input dif\_ctrl;"; printf "\n uvm\_analysis\_port #(\${tx\_type}) driver\_port;\n"; create\_new(\$block\_name); create\_build\_phase(\$block\_name); create\_run\_phase(\$block\_name); create\_drive\_dut(\$block\_name); create\_bind\_vis(\$block\_name); printf "\n\nendclass : \${block\_name}\_driver \n\n"; }; sub create\_new { printf "\n function new (string name = \"\${block\_name}\_driver\", uvm\_component parent);"; printf "\n\n super.new(name, parent);"; printf "\n\n endfunction \: new \n\n"; }; sub create\_build\_phase { printf "\n function void build\_phase(uvm\_phase phase);"; printf "\n\n string name;"; printf "\n super.build\_phase(phase);"; printf "\n driver\_port = new(\"driver\_port\", this);"; printf "\n\n endfunction \: build\_phase\n\n"; }; sub create\_run\_phase { printf"\n task run\_phase(uvm\_phase phase);"; printf"\n\n super.run\_phase(phase);"; printf"\n @(posedge dif data.reset n i);"; printf"\n @(aq\_dsp\_config::fw\_init\_done);"; printf"\n //Drive data now"; printf"\n forever"; printf"\n begin"; printf"\n @(posedge dif\_data.clk\_dsp);"; printf"\n seq\_item\_port.try\_next\_item(tx\_data);"; printf"\n drive\_dut();"; printf"\n driver\_port.write(tx\_data);"; printf"\n seq\_item\_port.item\_done();"; printf"\n end"; printf"\n\n endtask : run\_phase"; }; sub create\_drive\_dut { printf "\n\n function void drive\_dut();\n"; printf "\n dif\_data.a = tx\_data.a;"; printf "\n\n endfunction \: drive\_dut\n\n"; }: sub create\_bind\_vis { printf "\n\n function void bind\_vi\_data(virtual interface \${block}\_data\_input vif );\n"; printf "\n dif\_data = vif;"; printf "\n\n endfunction \: bind\_vi\_data\n\n"; printf "\n\n function void bind\_vi\_ctrl(virtual interface \${block} ctrl input vif);\n"; printf "\n dif\_ctrl = vif;"; printf "\n\n endfunction \: bind\_vi\_ctrl\n\n";

};

Figure 4: Perl code for generating UVM template

Perl script takes argument as block name, for ex. FFE and then generates the template code for driver, monitor, sequence, sequencer, TX agent, RX agent, etc. Similarly infrastructure code is generated for other UVM modules.

class aq\_dsp\_ffe\_driver extends uvm\_driver #

(aq\_dsp\_ffe\_transaction\_in);

`uvm\_component\_utils(aq\_dsp\_ffe\_driver)

aq\_dsp\_ffe\_transaction\_in tx\_data; virtual interface aq\_dsp\_ffe\_if\_data\_input dif\_data; virtual interface aq\_dsp\_ffe\_if\_ctrl\_input dif\_ctrl; uvm\_analysis\_port #(aq\_dsp\_ffe\_transaction\_in) driver\_port; function new (string name = "aq\_dsp\_ffe\_driver", uvm component parent): super.new(name, parent); endfunction function void build\_phase(uvm\_phase phase); string name; super.build\_phase(phase); driver\_port = new("driver\_port", this); endfunction function void bind\_vi\_data(virtual interface aq\_dsp\_ffe\_if\_data\_input vif);  $dif_data = vif;$ endfunction function void bind\_vi\_ctrl(virtual interface aq\_dsp\_ffe\_if\_ctrl\_input vif);  $dif_ctrl = vif;$ endfunction task run\_phase(uvm\_phase phase); super.run\_phase(phase); @(posedge dif\_data.reset\_n\_i); @(aq\_dsp\_config::fw\_init\_done); //Drive data now forever begin @(posedge dif\_data.clk\_dsp); seq\_item\_port.try\_next\_item(tx\_data); drive\_dut(); driver\_port.write(tx\_data); seq\_item\_port.item\_done();

end

endtask : run\_phase

function void drive\_dut(); dif\_data.rdl\_ffe\_rx\_data\_i[0] = tx\_data.rdl\_ffe\_rx\_data\_i[0]; endfunction

endclass: aq\_dsp\_ffe\_driver

#### Figure 5: UVM Driver code

As seen in the template code in the Figure 5 above, the "driver" class definition along with build phase, run phase, DUT driver code, etc. are generated through script. Verification engineers can now focus on writing or expanding "drive\_dut" function above for the DUT requirements instead of spending time on defining build/run phases, new function, call to `uvm\_component\_utils.

Similarly, template code can be generated for UVM monitors, UVM sequences, UVM scoreboards, UVM agents, UVM envs, UVM test classes, etc.

## V. SEQUENCE TEMPLATE CODE GENERATION :

**UVM Sequences for Filter**

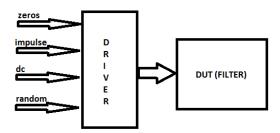

Figure 6: Filter UVM Sequences

For the top level DSP system used, DSP filter blocks have typical sequences such as zeros, impulse, incrementing, DC, decrementing, single tone, random, max positive and max negative. There are sequences needed for developing the testbench with easy debug and with the final goal of reaching towards random stimulus sequence. Since code for all the typical sequences mentioned above gets generated through scripts, it allows enough time to generate sequences for directed tests specific to particular functionality of the block. Following shows an example of code generated using the script. The perl script takes arguments for different sequences to be generated for a given filter and generates the following code. The following example shows DC sequence generated for a DEC filter.

class aq\_dsp\_ffe\_sequence\_base extends uvm\_sequence

#(aq\_dsp\_ffe\_transaction\_in);

`uvm\_object\_utils(aq\_dsp\_ffe\_sequence\_base)

function new (string name = "aq\_dsp\_ffe\_sequence\_base"

);

super.new(name);

endfunction : new

virtual task body(); endtask : body

endclass : aq\_dsp\_ffe\_sequence\_base

// DC scenario

class aq\_dsp\_ffe\_sequence\_dc extends

aq\_dsp\_ffe\_sequence\_base;

`uvm\_object\_utils(aq\_dsp\_ffe\_sequence\_dc)

```

function new (string name = "aq_dsp_ffe_sequence_dc" );

super.new(name);

endfunction : new

```

task pre\_body(); if(starting\_phase != null) begin starting\_phase.raise\_objection(this); end endtask

virtual task body();

repeat(no\_of\_iterations)

begin

`uvm\_do\_with(req,

{

req.rdl\_ffe\_rx\_data\_i[0] == ( DC\_VAL );

});

end

endtask : body

task post\_body(); if(starting\_phase != null) begin starting\_phase.drop\_objection(this); end endtask endclass : aq\_dsp\_ffe\_sequence\_dc

#### Figure 7: UVM sequence code for filter

The script can also be used to generate the base class for all FIRs sequences. This base class can contain all important sequences such as zeros, DC, impulse, incrementing and random. The sequence class template generated from the script can have the class derived from above base class.

Once the code is generated for driver, monitor, agents and sequences, the perl script takes arguments for different block level environments to be instantiated and generates the DSP top environment code. This DSP top environment can either instantiate block level agents or instantiate block level env directly based on the methodology followed. Finally the top env is instantiated in the UVM test code. Following screen shot shows example of DSP top env code generated through script.

class aq\_dsp\_env extends uvm\_env;

`uvm\_component\_utils(aq\_dsp\_env)

//Instantiate all the agents here. aq\_dsp\_ffe\_agent\_tx m\_ffe\_agent\_tx; aq\_dsp\_ffe\_agent\_rx m\_ffe\_agent\_rx; aq\_dsp\_ffe\_sb m\_sb; aq\_dsp\_ffe\_coverage m\_cov;

aq\_dsp\_fec\_sb m\_sb\_fec; aq\_dsp\_fec\_coverage m\_cov\_fec; aq\_dsp\_fec\_agent\_tx m\_fec\_agent\_tx; aq\_dsp\_fec\_agent\_rx m\_fec\_agent\_rx;

//Declare all interfaces

virtual aq\_dsp\_ffe\_if\_data\_input vif\_data\_input;

virtual aq\_dsp\_ffe\_if\_ctrl\_input vif\_ctrl\_input;

virtual aq\_dsp\_ffe\_if\_output vif\_output;

virtual aq\_dsp\_fec\_if\_data\_input vif\_fec\_data\_input; virtual aq\_dsp\_fec\_if\_ctrl\_input vif\_fec\_ctrl\_input; virtual aq\_dsp\_fec\_if\_output vif\_fec\_output;

function new (string name = "aq\_dsp\_env",

uvm\_component parent); super.new(name, parent); `uvm\_info(get\_name()," Env New ", UVM\_MEDIUM ); endfunction

function void build phase(uvm phase phase); string name; super.build\_phase(phase); m\_ffe\_agent\_tx = aq\_dsp\_ffe\_agent\_tx::type\_id::create("m\_ffe\_agent\_t x", this); m\_ffe\_agent\_rx = aq\_dsp\_ffe\_agent\_rx::type\_id::create("m\_ffe\_agent\_r x", this); m\_sb = aq\_dsp\_ffe\_sb::type\_id::create("m\_sb", this); m cov =aq\_dsp\_ffe\_coverage::type\_id::create("m\_cov", this); m fec agent tx =aq\_dsp\_fec\_agent\_tx::type\_id::create("m\_fec\_agent\_ tx", this); m fec agent rx =aq\_dsp\_fec\_agent\_rx::type\_id::create("m\_fec\_agent\_ rx", this);  $m_{sb_{fec}} =$ aq\_dsp\_fec\_sb::type\_id::create("m\_sb\_fec", this); m cov fec =aq\_dsp\_fec\_coverage::type\_id::create("m\_cov\_fec", this); function void end\_of\_elaboration\_phase(uvm\_phase phase); uvm\_top.print(); endfunction : end\_of\_elaboration\_phase function void report\_phase(uvm\_phase phase); report\_summarize(); endfunction : report\_phase

endclass: aq\_dsp\_env

Figure 8: UVM Env code

## VI. LIMITATIONS

The scripting method for generating the sequencer code for similar blocks such as FFE/FEC/DEC/NEC worked very well. There were other blocks such as RDL (Receive Delay Line) and AIF (Analog Interface) blocks in the DSP system. RDL block in the DSP system is responsible for sum of DEC, NEC, FFE and FEC filtered data. This RDL block functionality is much different from FIR filter functionality. In AIF block, there is glue logic for passing data from the digital domain to the analog domain. This functionality is also much different than FIR filter functionality. There are no data and coefficients interfaces for RDL/AIF blocks unlike FIR filters. The sequences that need to be generated for RDL and AIF blocks are much different from FIR filter sequences. In this scenario the same scripting code cannot be reused to the same extent as in the FIR filters sequences code.

In the project, there can be requirements to change the infrastructure code once block level verification gets started and new requirements are identified. Knowledge about the infrastructure and corresponding changes could be restricted to a single person owning the infrastructure development scripts and this can become a bottleneck in some cases as compared to distributed knowledge across the entire verification team.

## VII. RESULTS :

When there is similarity in functionality and hence testing methodology between different blocks of the top level system such as DEC/FEC/FFE/NEC filters in the DSP system, the script approach to create various templates codes for various UVM components such as driver, monitor, sequences, agents and envs is very useful. Approximately 60% of the code can be generated with this template and it requires filling the remaining 40% of the code with the block specific logic. Overall it saves a significant amount of time in coding.

Generation of block level testbenches takes a day using UVM automation scripts. Most of the randomized and directed tests are generated by these scripts based on the parameters provided to the scripts. The entire infrastructure for the UVM based environments can be developed in a matter of a few weeks instead of few months. Since all the block level testbenches are generated using scripts in an automated way, it imposes consistency in verification methodology for all the blocks of the chip and also between block level and top level verification. Scaling of the block level testbench to top level testbench becomes much easier since each block of the top level system uses the same modeling and verification infrastructure. Time saved in infrastructure development can be effectively used in thorough verification for block/top level verification.

These scripts can be modified further to generate a full chip environment where DSP top environment of the PHY (physical) layer and MAC (Media Access Control) layer top environment can be instantiated for the full chip verification. This allows easily reusable and uniform block level verification environment that can be scaled to DSP top level environment and is further scalable to a full chip PHY-MAC verification environment.

VIII. CONCLUSION:

Block and top level verification infrastructure development can be automated using scripts. This saves a significant amount of time that can be used for actual verification of the design.

## IX. REFERENCES:

- 1) Verification methodology cookbook, UVM, Mentor Graphics

- 2) UVM Golden Reference Guide, Doulos

- 3) 10GBASE-T, IEEE 802.3an, IEEE standard document.