# UVM-SystemC: Migrating complex verification environments

Stephan Gerth, Fraunhofer IIS/EAS

Akhila Madhukumar, Intel India Pvt. Ltd

# Agenda

- Preface: UVM-SystemC standardization update

- Main: Migrating complex verification environments

- Previous environment

- Randomziation using SCV & CRAVE

- Results

- Q&A

DESIGN AND VER

#### PART 0: UVM-SYSTEMC STANDARDIZATION UPDATE

# Updates since DVCon Europe 2016

- Register API: Basic backdoor implemented (no DPI)

- SystemC 2.3.2 compatibility

- Header includes

- Pkg-config

- Immediate notification mechanism

- UVM 1.2 Reporting API

- Stability review

#### Current status

- Effort currently shared within small group

- More input from interested parties welcome and needed

- Man power needs to be increased for faster development

- Preview release

- Final packaging & testing

- shortly after DVCon Europe 2017

# Plans for 2018

- Improve API compatibility to IEEE 1800.2-2017

- Complete Register API (frontdoor/backdoor)

- Simplify CRAVE integration

- Smart Pointer implementation

- Main branch: make API more clear about ownerships

- Separate branch: implement shared pointers in API

- Add more examples

- Ubus

- Codec

- User Guide

ESIGN AND VE

#### PART 1: PREVIOUSLY USED VERIFICATION ENVIRONMENT

© Accellera Systems Initiative

# Overview

- Previous verification environment

- Limitations and issues

- Migration details

- Layers

- Driver & Monitors

- Transactions

DESIGN AND VERIFIC

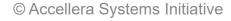

#### Conventional SystemC Testbench

- Custom test functions & test engine

- test functions (test ports) created to mimic bus transaction drivers; one per transaction type

- Individual functions for each test scenarios

- Distinct methods for writes and reads

- Number of methods depends on types of valid write/read as per the protocol being implemented viz. single, burst, posted or non-posted

- Self-checking and parametrized tests

- Additional task created for running multiple tests in parallel from different interfaces

- Vector classes used to keep track of test functions being launched from each interface

DESIGN AND VERIFICA

#### Limitations and potential reasons for UVM-SystemC

- Limitations of Non-UVM-SC testbench

- Higher learning curve for new user as TB has no standardized architecture

- Minimal reuse of tests/components across projects

- Configurability of testbench is limited

- Inadequate constrained randomization

- Narrow scope of IP to SoC reuse (SoC usually has UVM-SV based framework)

- Reasons for UVM-SC adoption:

- Re-usability

- Configurability

- Constrained randomization

- Standardization across languages

- Easier adoption for UVM-SV users

© Accellera Systems Initiative

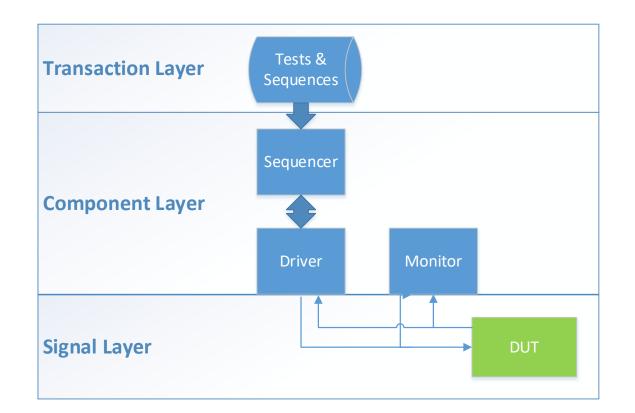

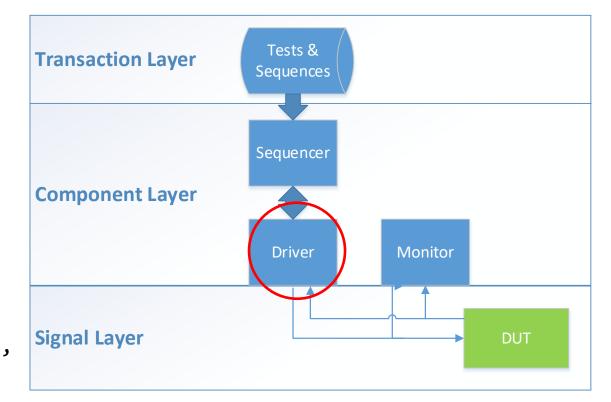

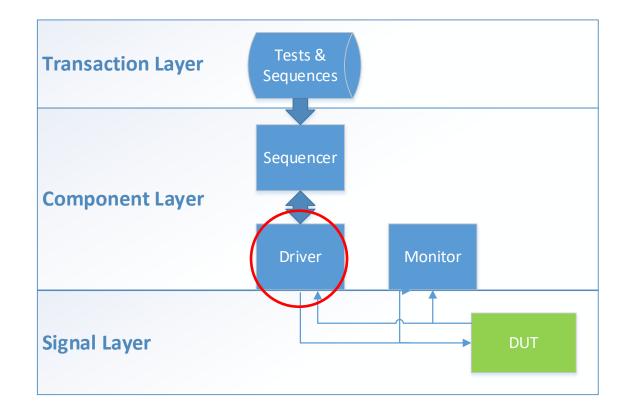

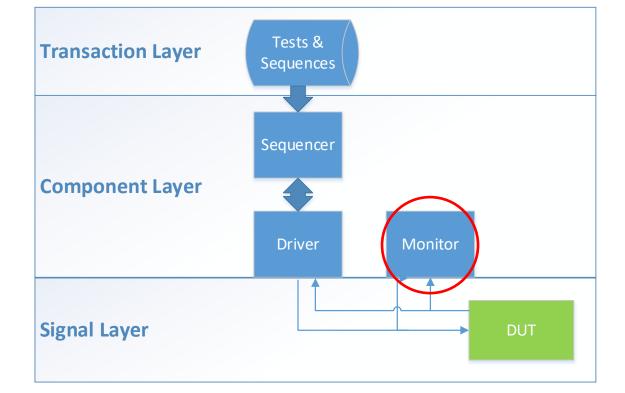

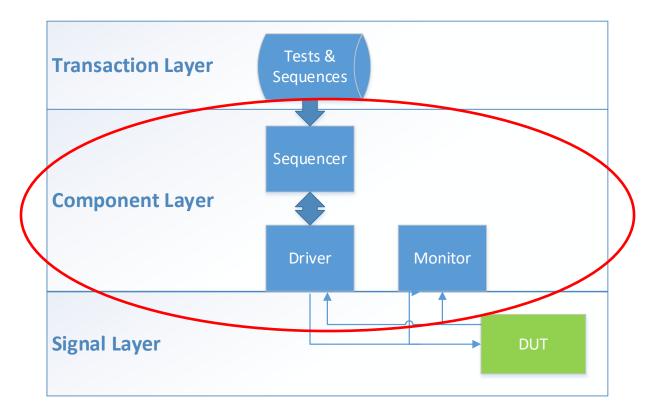

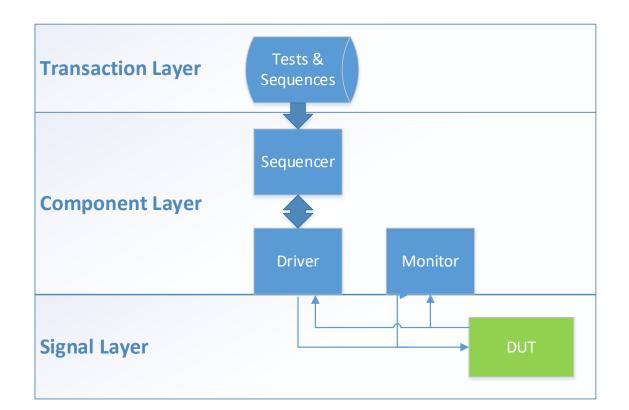

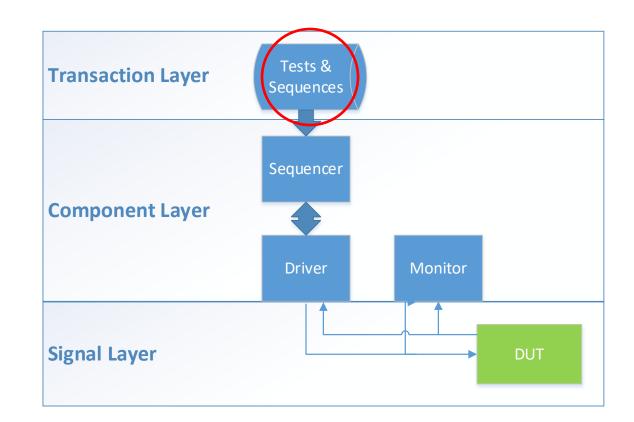

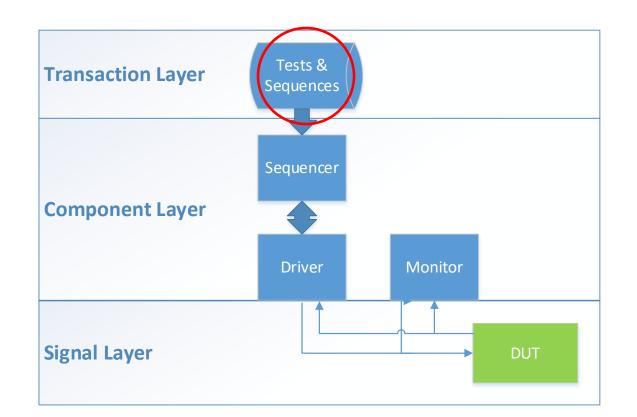

# Migrating to UVM-SystemC framework

- UVM-SystemC adheres to the UVM-SystemVerilog standard layered architecture

- Migration of previous components to their respective layers required

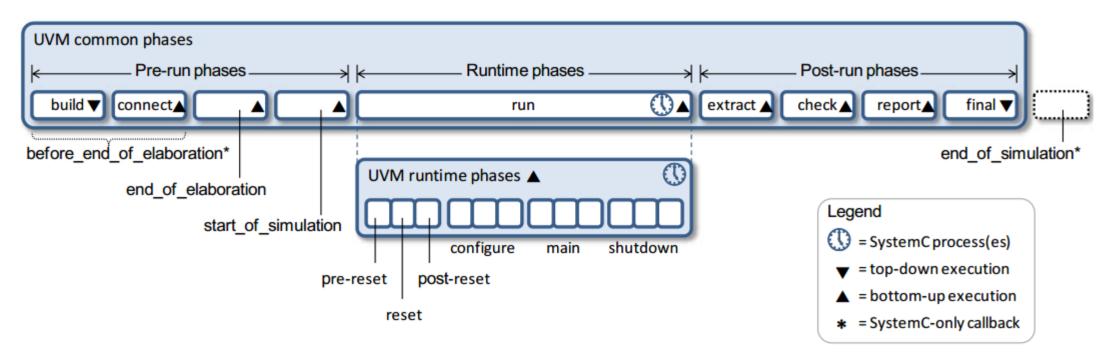

#### **UVM-SystemC** Phasing

- UVM phases are mapped to the System-C phases

- Completion of a runtime phase happens as soon as there are no objections (anymore) to proceed to the next phase.

- All UVM components have the phases associated with them

DESIGN AND VERIFI

# Build flow of UVM-SystemC(1/2)

- GCC used for compiling UVM-SystemC framework with SystemC DUT

- VCS used for compiling UVM-SystemC framework with RTL DUT

- run\_test("<test\_name>");

- Simulator looks for a component *registered* with the name <test\_name>

- Executes the build\_phase (from top-down) of all the uvm components

- Elaborates the hierarchy and understands the component connections

- Executes the run\_phases of all the components (in parallel)

- Enters post\_run phases and finished once all objections are dropped

#### Build flow of UVM-SystemC(2/2)

Starting SC tests ... 0 s: build\_phase top\_test 0 s: constructor top\_env 0 s: build\_phase top\_test.top\_env 0 s: constructor agent 0 s: build\_phase top\_test.top\_env.agent 0 s: constructor ahb\_sequencer\_inst 0 s: constructor ahb\_driver\_inst 0 s: constructor ahb\_driver\_inst 0 s: build\_phase top\_test.top\_env.agent.ahb\_monitor\_inst 0 s: connect\_phase top\_test.top\_env.agent 0 s: connect\_phase top\_test.top\_env in ahb\_reset\_proc begin 0 s: UVM test with ahb\_wr\_rd\_seq started top\_test in ahb\_reset\_proc end 100 ns: UVM test with ahb\_wr\_rd\_seq started top\_test

1732630 ns: UVM test with ahb\_wr\_rd\_seq finished top\_test

--- UVM Report Summary ---\*\* Report counts by severity UVM ERROR : 0 UVM FATAL : 0 UVM INFO : 0 UVM WARNING : 0 \*\* Report counts by id [RNTST] 1 [agent] 1 [ahb driver\_inst] 1705 [ahb monitor inst] 19 [ahb seq] 2609 [pp dynamic cfg\_seq] 8

.....

#### **Transaction Layer**

- Create interface and transaction classes as needed by the protocol

- Connect DUT to the interface

- Pass this interface to other components throughout the testbench hierarchy

```

int sc_main(int, char*[]) {

ahb_clk_reset_gen* clk_rst_gen

= new ahb_clk_reset_gen("clk_rst_gen");

```

```

ahb_if* dut_if_in = new ahb_if("dut_if_in");

dut_if_in->hclk(clk_rst_gen->ahb_clk);

dut_if_in->hresetn(clk_rst_gen->reset_val);

```

```

dut ahb_dut("ahb_dut");

ahb_dut.hclk(clk_rst_gen->ahb_clk);

ahb_dut.hresetn(clk_rst_gen->reset_val);

ahb_dut.haddr(dut_if_in->haddr);

```

```

• • •

```

```

uvm::uvm_config_db<ahb_if*>::

set(0, "*", "vif", dut_if_in);

uvm::uvm_config_db<sc_event*>::

set(0, "*", "reset_done", clk_rst_gen->reset_done);

run_test("ahb_wr_rd_test");

return 0;

```

SIGN AND VER

}

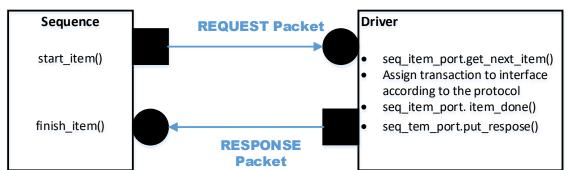

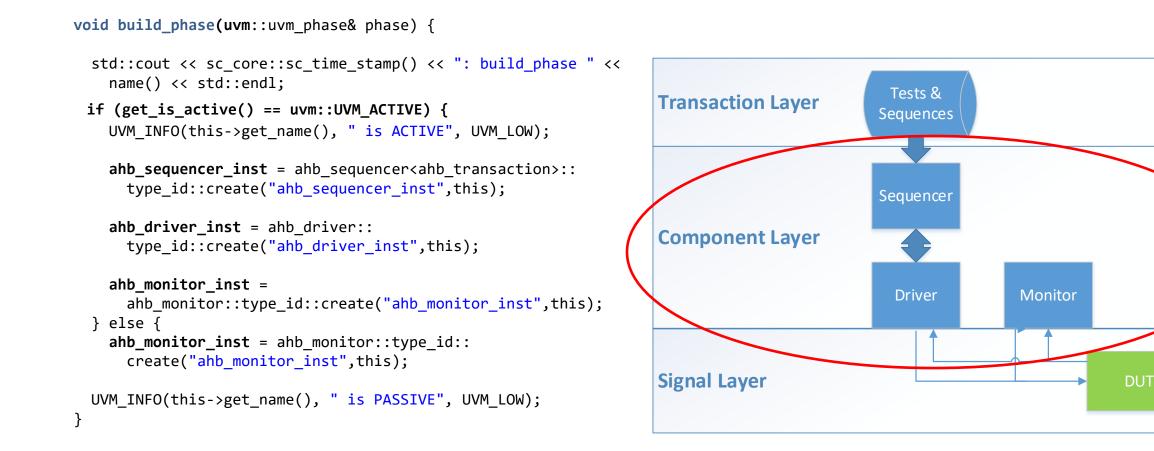

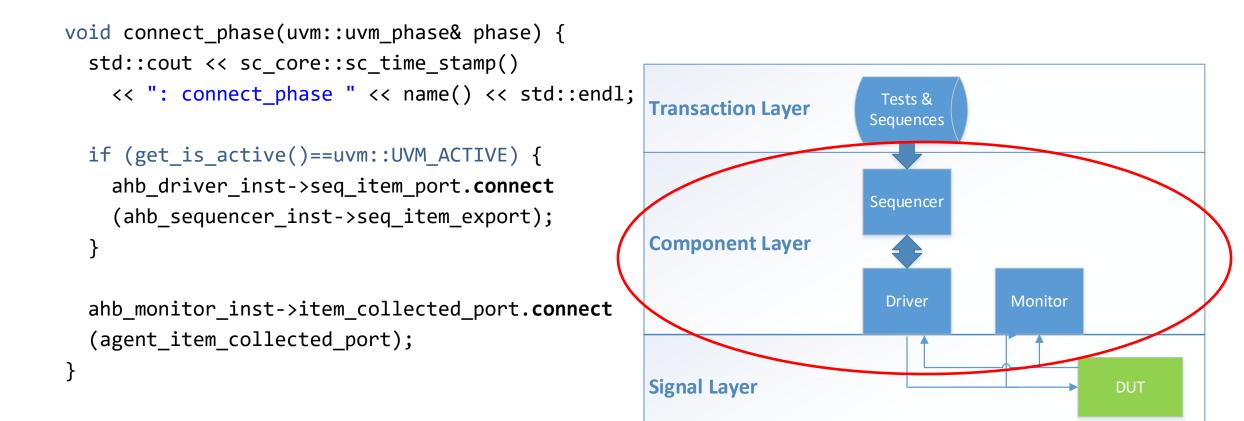

# **Component Layer**

- All components in this layer, are mapped to a transaction type

- The transaction class constitutes on the packet type which is being transmitted across components

- Driver-Sequencer to follow a standard handshaking interface as per UVM standard

- Driver is the key component where all protocol intelligence has to be implemented

- Monitor can implement protocol checks, data integrity checks etc.

- Taps the DUT signal directly

ESIGN AND VERIFI

# AHB Driver Component(1/6)

- Driver is derived from uvm\_component base class

- uvm\_components are created statically during the simulation, unlike uvm\_objects

- Module registered to factory by using "UVM\_COMPONENT\_PARAM\_UTILS"

- Enables component overrides using factory

- build\_phase() "creates" the component and gets the virtual interface handle

- Virtual interface is the mode of communication between the DUT and the UVM\_COMPONENTs

- Interface contains variables which are to be passed across the components.

- These contain all of the *transaction object* variables and some additional sideband signals, if any (based on the protocol of the driver)

# AHB Driver Component(2/6)

```

class ahb_driver: public

uvm::uvm_driver<ahb_transaction> {

```

#### public:

. . .

```

UVM_COMPONENT_PARAM_UTILS(ahb_driver);

ahb_if* ahb_vif;

sc_event* reset_event_driver;

sc semaphore ahb pipeline lock;

```

```

ahb_driver(

uvm::uvm_component_name name

= "ahb_driver"

):uvm::uvm_driver<ahb_transaction>(name),

ahb_pipeline_lock(1)

{

```

# AHB Driver Component(3/6)

void build\_phase(uvm::uvm\_phase& phase) {

```

UVM_INFO(this->get_name(),"build_phase entered",UVM_LOW);

uvm_driver<ahb_transaction>::build_phase(phase);

reset_event_driver = new sc_event("reset event driver");

if (!uvm config db<ahb if*>::

get(this, "*", "vif", ahb_vif))

UVM_FATAL(this>get_name(),

"AHB Virtual Interface missing");

}

if (!uvm config db<sc event*>::

get(this, "*", "reset done", reset event driver))

UVM FATAL(this->get name(), "Reset event missing");

```

DESIGN AND VÈRI

# AHB Driver Component(4/6)

- Run\_phase()

- This is the phase where simulation time advances

- This phase is supposed to handle the pre-reset and post-reset behavior of the driver

- The variables in the virtual interface are assigned values based on various modes of operation of the driver (as per the protocol)

- All the DUT interface signals which are to be driven by the testbench, should be assigned in this phase

- Driver receives the transaction object from the sequencer

- The communication (between driver and sequencer/sequence) is as per a UVM standard protocol

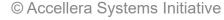

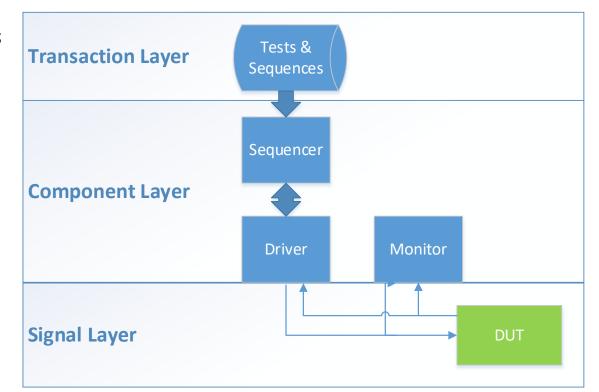

#### **Driver-Sequence Interactions**

- Driver waits for a transaction item in the run\_phase() by calling get\_next\_item() method of the driver analysis port.

- Once the sequence is started (from the uvm test), the start\_item() method will be called and a transaction item reference will be passed

- Driver receives this and assigns relevant values to the sequence item

- Item\_done() method call in driver indicates the transaction is updated and ready to be sent back to the sequence

- Driver can choose to call put\_response() method and send a response packet with updated response fields (like status, data etc.)

- Sequence finished the item processing once the response is received and calls finish\_item()

DESIGN AND VERIF

# AHB Driver Component(5/6)

```

void run_phase(uvm::uvm_phase& phase) {

UVM_INFO(this->get_name(),

Tests &

Transaction Layer

"run phase entered", UVM LOW);

Sequences

if (ahb vif->hresetn == 0) wait(*reset event driver);

Sequencer

while(true) {

Component Layer

SC_FORK

sc_spawn(sc_bind(

Driver

Monitor

&ahb_driver::send_transaction,this),"drive1"),

sc_spawn(sc_bind(

&ahb driver::send transaction,this),"drive2")

Signal Layer

SC JOIN

UVM_INFO(this->get_name(),

"run_phase finished", UVM_LOW);

```

DUT

}

#### AHB Driver Component(6/6)

```

void send_transaction() {

ahb transaction req, rsp;

ahb_pipeline_lock.wait();

UVM_INFO(this->get name(),

"send transaction: next item",UVM_LOW);

this->seq_item_port->get_next_item(req);

ahb vif->htrans

= req.htrans;

ahb vif->haddr

= req.haddr;

ahb vif->hsize

= req.hsize;

. . .

wait(AHB CLK);

while (ahb vif->hready != 1) wait(AHB CLK);

rsp.set_id_info(req);

this->seq_item_port->item_done();

this->seq_item_port->put_response(rsp);

ahb_pipeline_lock.post();

```

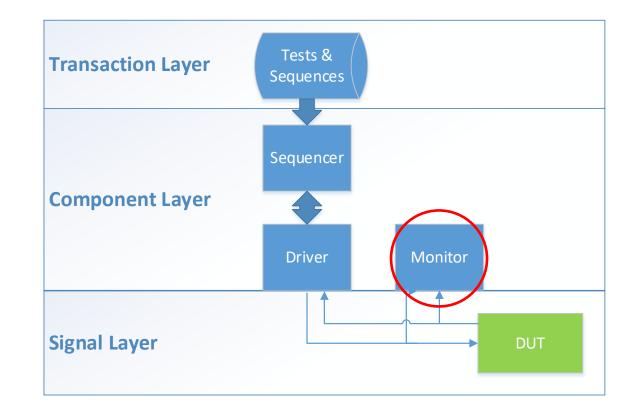

# AHB Monitor Component(1/3)

- Monitor is derived from uvm\_monitor/uvm\_component base class

- Consist of an analysis port

- build\_phase() "creates" the component and gets the virtual interface handle

- run\_phase()

- Monitor receives the transaction items through the virtual interface and creates an internal packet from it

- If a broadcast packet is needed, monitor can write this packet to an analysis port and any other components can receive this by connecting to this port

- Protocol checks and assertions are implemented to validate the transaction item values

- Fatal/Error/Warning messages can be flagged based on the protocol failure severity

# AHB Monitor Component(2/3)

```

class ahb_monitor : public uvm::uvm_monitor {

public:

uvm::uvm_analysis_port<ahb_transaction>

item_collected_port;

ahb_if* vif;

ahb_monitor(

uvm::uvm_component_name name = "ahb_monitor"):

uvm_monitor(name),

item_collected_port("item_collected_port"),

vif(0)

{ ... }

```

UVM\_COMPONENT\_UTILS(ahb\_monitor);

```

void build_phase(uvm::uvm_phase& phase) {

uvm::uvm_monitor::build_phase(phase);

if (!uvm::uvm_config_db<ahb_if*>::

get(this, "*", "vif", vif)) {

UVM_FATAL(name(),

"Virtual interface not defined!");

}

```

#### AHB Monitor Component(3/3)

```

void run_phase( uvm::uvm_phase& phase ) {

```

ahb\_transaction pkt;

```

while (true) { // monitor forever

std::ostringstream str;

wait( vif->hresetn.posedge event());

```

```

if (vif->hclk == 0)

sc_core::wait(vif->hclk.posedge_event());

```

```

pkt.htrans = vif->htrans;

pkt.haddr = vif->haddr;

...

```

```

item_collected_port.write(pkt);

```

```

// Checks on the packet items

AddressByteAlligned(pkt.haddr);

SlaveErrorResponse(pkt);

```

# AHB Agent (1/3)

```

class ahb agent : public uvm::uvm agent {

public:

ahb_driver* ahb_driver_inst;

ahb_monitor* ahb_monitor_inst;

ahb_sequencer<ahb_transaction>* ahb_sequencer_inst;

uvm::uvm analysis port<ahb transaction>

agent_item_collected_port;

ahb_agent(uvm::uvm_component_name name = "ahb_agent"):

uvm_agent(name), ahb_sequencer_inst(0),

ahb_driver_inst(0) , ahb_monitor_inst(0),

agent item collected port("agent item collected port")

std::cout << sc_core::sc_time_stamp()</pre>

<< ": constructor " << name << std::endl;

}

```

# AHB Agent (2/3)

# AHB Agent (3/3)

#### AHB Basic Env

```

class ahb basic env : public uvm::uvm env {

public:

UVM COMPONENT UTILS(ahb basic env);

ahb agent* agent;

ahb basic env(

uvm::uvm component name name=

"ahb basic env"): uvm::uvm env(name), agent(0) {

std::cout << sc core::sc time stamp()</pre>

<< ": constructor " << name << std::endl;

}

void build phase(uvm::uvm phase& phase) {

std::cout << sc_core::sc_time_stamp()</pre>

<< ": build phase " << name() << std::endl;

agent = ahb agent::type id::create("agent", this);

uvm::uvm_config_db<int>::

set(this, "agent", "is active", uvm::UVM_ACTIVE);

```

DESIGN AND VERI

};

# Transaction Layer (UVM Tests) (1/3)

- UVM\_TESTs are responsible for building the top level environment and initiating the start of the required sequence

- UVM runs tasks on objections and all the components wishing to perform a task are expected to raise an objection

- build\_phase() "creates" the component

- run\_phase()

- Objection is raised and dropped in this phase

- Sequence handle is created and sequence is started by calling the start() method

- The sequencer on which the sequence should be run is also specified

- Multiple sequences can be started at the same time on different sequencers

# Transaction Layer (UVM Tests) (2/3)

```

class ahb_wr_rd_test : public uvm::uvm_test {

public:

ahb_wr_rd_sequence* ahb_wr_rd_seq;

```

```

ahb_basic_env* top_env;

```

```

UVM_COMPONENT_UTILS(ahb_wr_rd_test);

ahb_wr_rd_test( uvm::uvm_component_name

name = "ahb_wr_rd_test"):

uvm::uvm_test( name ), top_env(0) {}

```

# Transaction Layer (UVM Tests) (3/3)

```

virtual void run_phase(uvm::uvm_phase& phase) {

std::cout << sc_core::sc_time_stamp()

<< ": UVM test with ahb_wr_rd_seq started "

<< name() << std::endl;</pre>

```

```

phase.raise_objection(this);

```

```

ahb_wr_rd_seq =

new ahb_wr_rd_sequence("ahb_wr_rd_seq");

ahb_wr_rd_seq->start(top_env->

agent->ahb_sequencer_inst);

```

```

phase.drop_objection(this);

std::cout << sc_core::sc_time_stamp()

<< "UVM test with ahb_wr_rd_seq finished"

<< name() << std::endl;</pre>

```

}

#### PART 2: RANDOMIZATION USING SCV & CRAVE

© Accellera Systems Initiative

# Overview

- Sequence randomization

- SCV

- CRAVE

- Sequence randomization sample

# Random Sequences Using SCV (1/2)

- While using SCV for randomizing the sequence item, scv\_extensions are to be created

- SCV\_EXTENSION consist of the transaction fields to be randomized

- SCV\_CONSTRAINTS can be added for all of the scv\_extension variables as per the required constrained randomization

- In a sequence, the scv\_constraint object is created and next() method is called to get a set of random values

- These are assigned to the scv\_smart\_ptr for the transaction class

- Multiple random values can be received by calling next() method each time

# Random Sequences Using SCV (2/2)

Create scv extensions for the sequence item class i.e. for the transaction type SCV EXTENSIONS(ahb transaction) { public: scv\_extensions<sc\_uint<ahbConfig::AhbAddrWidth>> haddr; scv\_extensions<sc\_uint<ahbConfig::AhbDataWidth>[BURSTLENGTH]> hwdata; scv extensions< sc uint<ahbConfig::AhbBurstSize>> hburst; scv extensions< sc uint<ahbConfig::AhbSize>> hsize; SCV\_EXTENSIONS\_CTOR(ahb\_transaction) { SCV FIELD(haddr); SCV FIELD(hburst); SCV FIELD(hsize); SCV FIELD(hwdata); bool has valid extensions() { return true; } };

```

Create constraints class using smart_ptr of sequence item class type

```

```

class ahb_trans_constraints : virtual public scv_constraint_base {

public:

scv_smart_ptr<ahb_transaction> req;

SCV_CONSTRAINT_CTOR(ahb_trans_constraints) {

SCV_CONSTRAINT((req->haddr() * 0x3) == 0x0);

SCV_CONSTRAINT(

(req->hburst() >= ahbConfig::HBURST_SINGLE) &&

(req->hburst() <= ahbConfig::HBURST_INCR16)

);

SCV_CONSTRAINT(

(req->hsize() >= ahbConfig::HSIZE_BYTE) &&

```

```

(req->hsize() <= ahbConfig::HSIZE_WORD)</pre>

```

);

);

DESIGN AND VERIFIC

```

((req->haddr() * 0x7) != 0x0) );

```

### Hierarchical Sequences using Random Sequence Items (SCV)(1/2)

```

class ahb wr rd sequence : public

uvm::uvm sequence<ahb transaction>

public:

UVM OBJECT UTILS(ahb wr rd sequence);

UVM DECLARE P SEQUENCER(ahb sequencer<ahb transaction>);

ahb if* ahb vif seq;

ahb wr rd sequence( const std::string&

name = "ahb wr rd sequence") :

uvm::uvm sequence<ahb transaction> ( name ){}

uint8 t xactType;

unsigned addrValue;

unsigned dataValue;

void body()

UVM_INFO(this->get name(), "Starting sequence",

uvm::UVM INFO);

ahb_trans_constraints constr_req("constr_req");

> scv_smart_ptr<ahb_transaction>

rand_smart_ptr_ahb_pkt;

ahb basic sequence* ahb seq;

ahb seq = new ahb basic sequence("ahb seq");

```

```

constr_req.next();

rand smart ptr ahb pkt.write(constr req.req.read());

ahb seq->xactType = rand smart ptr ahb pkt ->hwrite;

ahb seq->hburstValue =

rand smart ptr ahb pkt ->hburst;

ahb seq->addrValue = rand smart ptr ahb pkt ->haddr;

ahb seq->dataValue = 0xabababab;

ahb seq->start(m sequencer);

constr req.next();

rand smart ptr ahb pkt.write(constr reg.reg.read());

ahb_seq->xactType = rand_smart_ptr_ahb_pkt ->hwrite;

ahb seq->hburstValue =

rand smart ptr ahb pkt ->hburst;

ahb seq->addrValue = rand_smart_ptr_ahb_pkt ->haddr;

ahb_seq->start(m_sequencer);

UVM INFO(this->get name(),

"Finishing sequence", uvm::UVM INFO);

```

#### Hierarchical Sequences using Random Sequence Items (SCV)(2/2)

```

class ahb basic sequence : public

uvm::uvm sequence<ahb transaction>

public:

UVM OBJECT UTILS(ahb basic sequence);

uint8 t xactType;

unsigned addrValue,dataValue;

unsigned hburstValue, hsizeValue;

ahb basic sequence( const std::string&

name = "ahb basic sequence") :

uvm::uvm_sequence<ahb_transaction> ( name ) {}

void body()

UVM_INFO(this->get name(), "Starting

sequence ahb basic sequence", uvm::UVM INFO)

ahb transaction* req pkt;

ahb transaction* rsp;

req pkt = new ahb transaction();

= new ahb transaction();

rsp

single wr rd(addrValue, xactType, dataValue,

req_pkt, rsp);

```

```

void single wr rd(unsigned addrValue,

unsigned xactType,

unsigned dataValue,

ahb transaction* req pkt,

ahb transaction* rsp)

{

UVM_INFO(this->get_name(), "Initiating

non-burst accesses", uvm::UVM INFO);

reg pkt->haddr = addrValue;

reg pkt->hsel = 1;

req pkt->hready = 1;

req pkt->htrans = ahbConfig::HTRANS NONSEQ;

req pkt->hsize = hsizeValue;

req pkt->hwrite = xactType;

reg pkt->hwdata[0] =

(sc uint<32>)dataValue;

this->start item(req pkt);

this->finish_item(req_pkt);

this->get response(rsp);

```

ESIGN AND VERIFIC

# Random Sequences Using CRAVE

- Transaction class need to be derived from uvm\_randomized\_sequence\_item()

- Variables to be randomized are declared as crv\_variables

- Constraints can be specified by using crv\_constraint method

- base sequence using the transaction item, should call the randomize() method to get random values for the crv\_variables

- values should be assigned to the transaction packets fields, as per requirement and sent to the DUT

- UVM\_DO\* macros can be called to specify which transaction object has to be sent to the driver and with what random values

#### Sequence Item Using CRAVE

```

class ahb_transaction : public uvm_randomized_sequence_item {

public:

UVM_OBJECT_UTILS(ahb transaction);

```

```

// define some rand variables

crv_variable< sc_uint< ahbConfig::AhbAddrWidth > > haddr;

crv_variable< sc_uint< ahbConfig::AhbSize > > hsize;

crv_variable< sc_uint< ahbConfig::AhbDataWidth> > hwdata[BURSTLENGTH];

crv variable< unsigned > hburst;

```

#### // Add some constraints

```

crv_constraint valid_hburst_range {HBURST_SINGLE <= hburst() <= HBURST_INCR16};

crv_constraint valid_hsize_range {HSIZE_BYTE <= hburst() <= HSIZE_WORD};

crv_constraint valid_addr_range {haddr() * 0x3 == 0x0};

crv_constraint addr_for_wrap_burst {if_then(hburst() == HBURST_WRAP4, (haddr() * 0x7) != 0x0)};

```

#### // Constructor

```

ahb_transaction(crv_object_name name = "ahb_transaction") : uvm_randomized_sequence_item(name) {

...

};

```

};

© Accellera Systems Initiative

# Hierarchical Sequences using Random Sequence Item (CRAVE)

#include "ahb\_basic\_sequence.h"

```

class abb wr rd sequence : public uvm randomized sequence<abb transaction>

public:

UVM_OBJECT_UTILS(ahb_wr_rd_sequence);

ahb wr rd sequence( crave::crv object name name = "ahb wr rd sequence") :

uvm randomized sequence<ahb transaction> ( name )

ł

cout << "Entered constructor of ahb wr rd sequence " << endl;</pre>

}

void body()

UVM INFO(this->get name(), "Starting sequence", uvm::UVM INFO);

ahb basic sequence* ahb seq;

ahb seq = new ahb_basic_sequence("ahb_seq");

ahb seq->hburstValue = ahbConfig::HBURST SINGLE;

ahb seq->start(m sequencer);

UVM INFO(this->get name(), "Finishing sequence", uvm::UVM INFO);

```

};

DESIGN AND VER

#### Base sequence with crv\_variable

```

class abb basic sequence : public

uvm randomized sequence<ahb transaction>

public:

UVM_OBJECT_UTILS(ahb_basic_sequence);

crv_variable<uint8_t > xactType;

crv variable<unsigned > addrValue;

crv variable<unsigned > dataValue;

ahb basic sequence( crave::crv object name

name= "ahb basic sequence") :

uvm_randomized_sequence<ahb transaction> ( name )

{}

virtual ~ahb basic sequence() {

};

void body()

UVM INFO(this->get name(), "Starting sequence

ahb basic sequence", uvm::UVM INFO);

ahb transaction* req pkt;

ahb transaction* rsp;

req pkt = new ahb transaction();

= new ahb transaction();

rsp

single wr rd(addrValue, xactType, dataValue, req pkt,

rsp);

```

```

void single wr rd(unsigned addrValue,

unsigned xactType,

unsigned dataValue,

ahb transaction* req pkt,

ahb transaction* rsp)

UVM INFO(this->get name(), "Initiating non-burst

accesses", uvm::UVM INFO);

this->randomize();

req pkt->haddr = addrValue;

req pkt->hsel = 1;

req pkt->hready = 1;

req pkt->htrans = ahbConfig::HTRANS NONSEQ;

req pkt->hsize = hsizeValue;

req pkt->hwrite = xactType;

UVM DO WITH(req pkt, req pkt->haddr() == addrValue);

UVM INFO(this->get name(), "Exiting non-burst

accesses", uvm::UVM INFO);

}

```

DESIGN AND VERIFIC

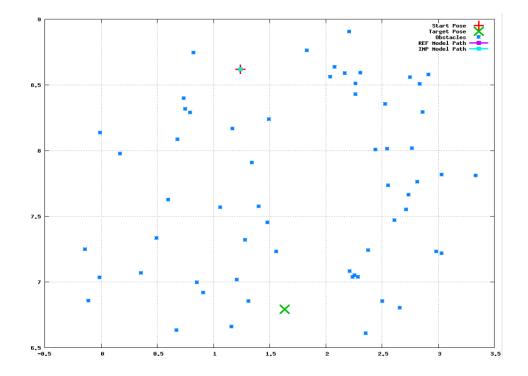

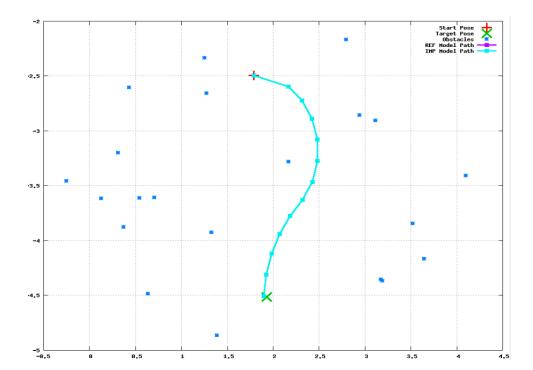

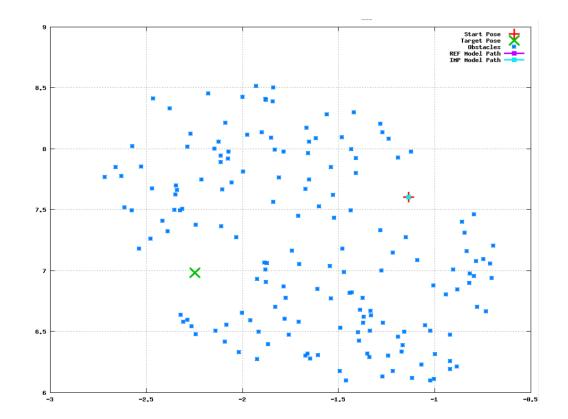

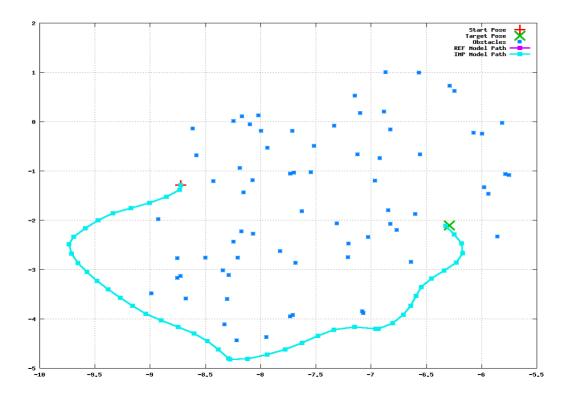

# SCV Sequence Randomization Sample

- SCV constraints written to configure the IP parameter randomly

- The IP is designed to find a path between point 'A' and 'B' without colliding to any obstacles on its path. Start, target and the obstacle map is an input to the IP.

- Test ends when an Interrupt is asserted by the IP; interrupt status of 1 => Valid output ready, interrupt status of 2 => No valid output(path) possible

- SCV library does not have scv\_extensions added for fixed point data types yet.

- Hence, constrained randomization attained using rand() method.

- Sample plots show the capability of randomization to generate distinct scenarios.

### Code Snippet for Randomizing Fixed Point Variables(1/2)

```

sc fixed<32,8> TP_X, TP_Y, TP_PHI;

while(1)

sc fixed<32,8> omap X, omap Y;

{

sc fixed<32,8> rand SP PHI;

TP X = (sc fixed<32,8>)(rand() / (RAND MAX / 18.0) ) +

(-9.0);

sc fixed<32,8> rand TP PHI;

TP Y = (sc fixed<32,8>)(rand() / (RAND MAX / 18.0) ) +

(-9.0);

sc fixed<32,8> eucDistObsSP;

eucDistSPTP = sqrt((TP X-SP X)*(TP X-SP X) + (TP Y-

sc fixed<32,8> eucDistObsTP;

SP Y)*(TP Y-SP Y));

sc fixed<32,8> eucDistSPTP;

if( (eucDistSPTP > 0.4) && (eucDistSPTP < 3) )

omap_count = (rand()%161) + 20; // obs points between 20

{

and 180

cout << "EP is " << TP X << endl;</pre>

ahb seq->addrValue = TARGETPOSEX;

SP X = (sc fixed<32,8>)(rand() / (RAND MAX / 18.0) ) + (-

wr data.range(31,24) = TP X.range(31,24);

9.0);

wr data.range(23,0) = TP X.range(23,0);

SP Y = (sc fixed<32,8>)(rand() / (RAND MAX / 18.0) ) + (-

9.0);

ahb seq->dataValue = wr data;

// Value between -1.5708 to 1.5708 i.e -90 to 90

ahb seq->start(m sequencer);

rand SP PHI = -1.5708 + (sc fixed<32,8>)(1.5708 * (rand())

break;

/ (RAND_MAX + (-1.5708))));

rand TP PHI = -1.5708 + (sc fixed<32,8>)(1.5708 * (rand())

/ (RAND MAX + (-1.5708))));

}

```

sc fixed<32,8> SP\_X, SP\_Y, SP\_PHI;

# Code Snippet for Randomizing Fixed Point Variables(2/2)

// Keep finding obst points for the required omap count. Ignore points which are close to  $\ensuremath{\mathsf{SP/TP}}$

```

while(1)

```

```

{

```

```

omap_X = (sc_fixed<32,8>)(rand() / (RAND_MAX / 18.0) ) + (-

9.0);

```

```

omap_Y = (sc_fixed<32,8>)(rand() / (RAND_MAX / 18.0) ) + (-

9.0);

```

```

// Calculate euc dist of obt point from SP and TP

eucDistObsSP = sqrt((SP_X-omap_X)*(SP_X-omap_X) + (SP_Y-

omap_Y)*(SP_Y-omap_Y));

eucDistObsTP = sqrt((TP_X-omap_X)*(TP_X-omap_X) + (TP_Y-

omap_Y)*(TP_Y-omap_Y));

```

```

if( (eucDistObsSP > 0.3)

&& (eucDistObsSP < (1.25*eucDistSPTP) )

&& (eucDistObsTP > 0.3)

&& (eucDistObsTP < (1.25*eucDistSPTP) )) {

act_omap_count++;

omap_cfg << omap_X << " " << omap_Y;

}</pre>

```

Sample SCV for fixed point variables(not supported yet):

SCV\_EXTENSIONS(PathPoints)

public:

```

scv_extensions<

sc_fixed<32,8,SC_DEFAULT_Q_MODE_,

SC_DEFAULT_0_MODE_,SC_DEFAULT_N_BITS_>>

targetPoseXY;

```

```

SCV_EXTENSIONS_CTOR(PathPoints)

{

SCV_FIELD(targetPoseXY);

}

bool has_valid_extensions() {return

true;}

```

#### Sample IP outputs (1/2)

2017 DESIGN AND VERIFICATION

CONFERENCE AND EXHIBITION

#### Sample IP outputs (2/2)

DESIGN AND VERIFICATION

CONFERENCE AND EXHIBITION

#### PART 3: MIGRATION RESULTS & CONCLUSION

© Accellera Systems Initiative

#### Overview

- Benefits

- Tooling

- Conclusion

#### Potential benefits of UVM-SystemC methodology

- Less design time for testbench components

- Base library provides analysis ports and callbacks

- Low learning curve for new users to the IP

- Testbench framework well known in verification circles

- Less time in test coding for IP validation at SoC level using UVM-SV

Language specific updates between SC and SV via simple script

- Reduced coding time for testbench components for IP at SoC level

Re-use of custom bus functional model written at IP level

- Reduced man power required

- Same owner can work on IP and SoC validation

# Sample Conversion Capabilities of the UVM-SC to UVM-SV script

- Changing class extension syntax

- class ahb\_transaction : public uvm\_randomized\_sequence\_item to

class ahb\_transaction extends public uvm\_randomized\_sequence\_item

- Updating the component phase arguments

- void run\_phase(uvm::uvm\_phase& phase) to function void run\_phase(uvm::uvm\_phase phase)

- Modifying the constructor calls

```

- ahb_driver( uvm::uvm_component_name name = "ahb_driver"):

uvm::uvm_driver<ahb_transaction>( name ),ahb_pipeline_lock(1)

{ ... } to

function new (string name = "ahb_driver"):

super.new(name);

endfunction

```

- Replacing loop constructor brackets with begin-end

- if(!uvm\_config\_db<ahb\_if\*>::get(this, "\*", "vif", ahb\_vif)) { ... } to

if(!uvm\_config\_db<ahb\_if\*>::get(this, "\*", "vif", ahb\_vif)) begin ... end

# Summary

- What went well

- Availability of all uvm component base classes enabled fast bring up of the UVM-SystemC framework (reporting, objection handling etc.)

- Visibility of source code helped in component development

- What could be improved

- SCV randomization limitations with fixed point data types

- Multiple vendor simulator support for UVM-SystemC compile/elab

- More examples of complete validation framework will be useful for beginners (maybe put up our example for reference)

# Conclusion

- UVM-SystemC based validation framework enables development of configurable, re-usable and structured components

- standard implementation technique enables resilient testbench across multiple users

- methodology should be adopted across companies and EDA vendors to make validation truly language agnostic and enhance the UVM-SystemC VIP portfolio

# References

- UVM-SystemC

- http://www.accellera.org/images/downloads/drafts-review/

- CRAVE

- http://www.systemc-verification.org/crave/

© Accellera Systems Initiative

#### Questions