# UVM-SystemC Applications in the real world

<u>Stephan Schulz</u>, <u>Thilo Vörtler</u>, Karsten Einwich (Fraunhofer IIS/EAS)

Martin Barnasconi (NXP)

IIS

Fraunhofer

## Outline

- Introduction and Motivation

- Universal Verification Methodology (UVM) ... what is it?

- Why UVM in SystemC/C++/SystemC-AMS?

- UVM-SystemC overview

- UVM foundation elements

- UVM test bench and test creation

- Randomization and coverage

- Standardization within Accellera

- Applications and use cases of UVM-SystemC

- Summary and outlook

## Outline

- Introduction and Motivation

- Universal Verification Methodology (UVM) ... what is it?

- Why UVM in SystemC/C++/SystemC-AMS?

- UVM-SystemC overview

- UVM foundation elements

- UVM test bench and test creation

- Randomization and coverage

- Standardization within Accellera

- Applications and use cases of UVM-SystemC

- Summary and outlook

## Introduction: UVM - what is it?

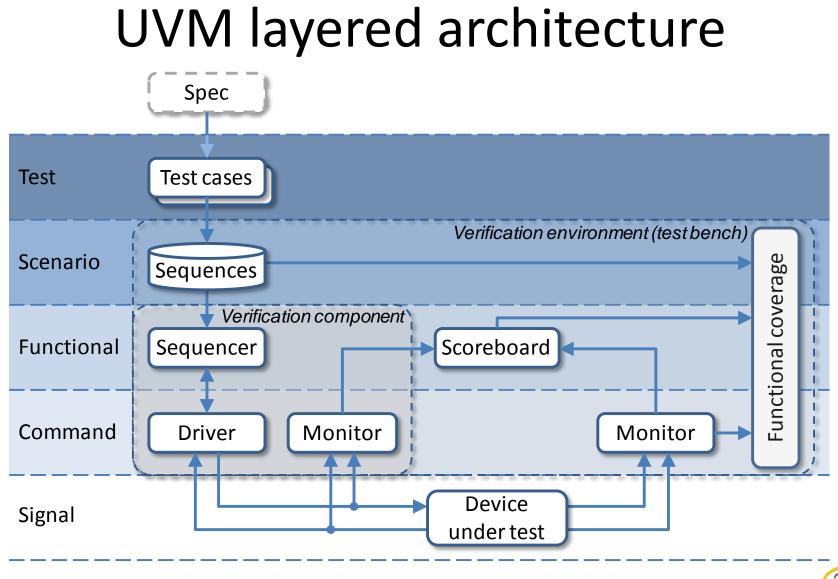

- Universal Verification Methodology facilitates the creation of modular, scalable, configurable and reusable test benches

- Based on verification components with standardized interfaces

- **Class library** which provides a set of built-in features dedicated to simulation-based verification

- Utilities for phasing, component overriding (factory), configuration, comparing, scoreboarding, reporting, etc.

- Environment supporting migration from directed testing towards Coverage Driven Verification (CDV)

- Introducing automated stimulus generation, independent result checking and coverage collection

## Motivation

- No structured nor unified verification methodology available for ESL design

- UVM (in SystemVerilog) primarily targeting block/IP level (RTL) verification, not system-level

- Porting UVM to SystemC/C++ enables

- creation of more advanced systemlevel test benches

- reuse of verification components between system-level and block-

level verification

<sup>\*</sup>UVM-SystemC = UVM implemented in SystemC/C++

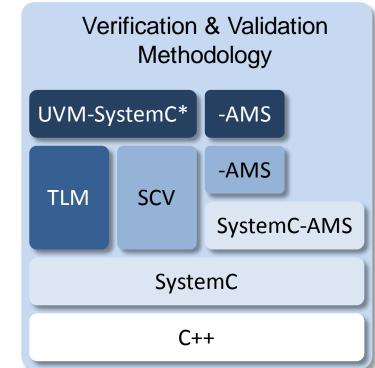

### Why UVM in SystemC/C++ and SystemC-AMS?

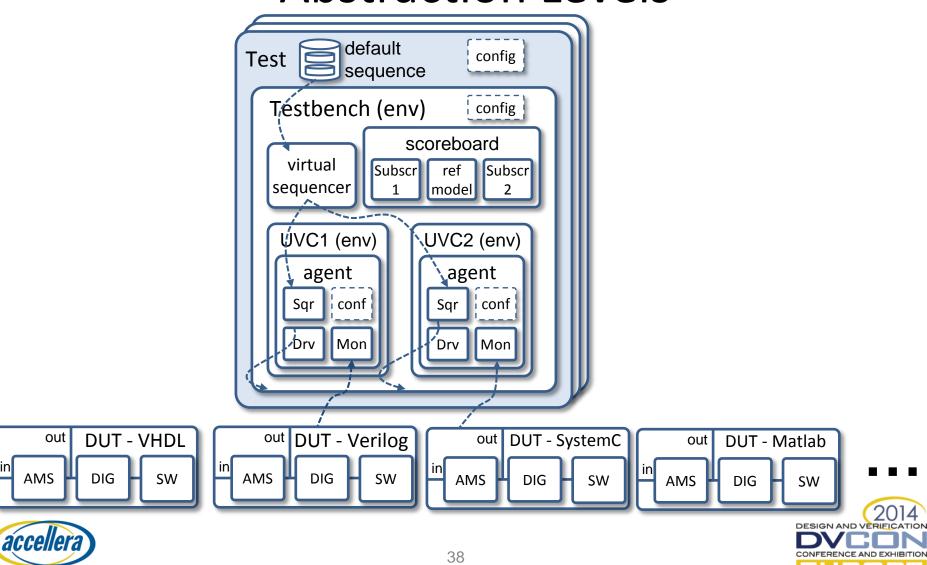

- Strong need for a system-level verification methodology for embedded systems which include HW/SW and AMS functions

- SystemC is the recognized standard for system-level design, and needs to be extended with advanced verification concepts

- SystemC AMS available to cover the AMS verification needs

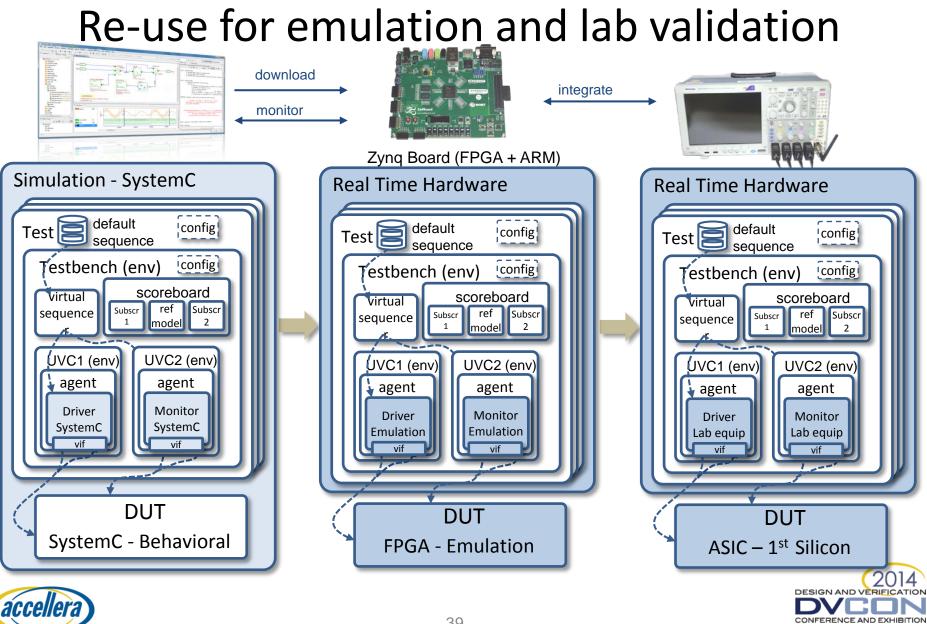

- Reuse tests and test benches across verification (simulation) and validation (HW-prototyping) platforms

- This requires a portable language like C++ to run tests on HW prototypes and even measurement equipment

- Enabling Hardware-in-the-Loop simulation or Rapid Control Prototyping

#### Why UVM in SystemC/C++ and SystemC-AMS?

- Benefit from proven standards and reference implementations

- Leverage from existing methodology standards and reference implementations, aligned with best practices in verification

# Outline

Introduction and Motivation

- Universal Verification Methodology (UVM) ... what is it?

- Why UVM in SystemC/C++/SystemC-AMS?

- UVM-SystemC overview

- UVM foundation elements

- UVM test bench and test creation

- Randomization and coverage

- Standardization within Accellera

- Applications and use cases of UVM-SystemC

- Summary and outlook

#### UVM-SystemC overview

| UVM-SystemC functionality                                                                          | Status       |

|----------------------------------------------------------------------------------------------------|--------------|

| Test bench creation with component classes:<br>agent, sequencer, driver, monitor, scoreboard, etc. |              |

| Test creation with test, (virtual) sequences, etc.                                                 |              |

| Configuration and factory mechanism                                                                |              |

| Phasing and objections                                                                             |              |

| Policies to print, compare, pack, unpack, etc.                                                     |              |

| Messaging and reporting                                                                            |              |

| Register abstraction layer and callbacks                                                           | development  |

| Coverage groups                                                                                    | development  |

| Constrained randomization                                                                          | SCV or CRAVE |

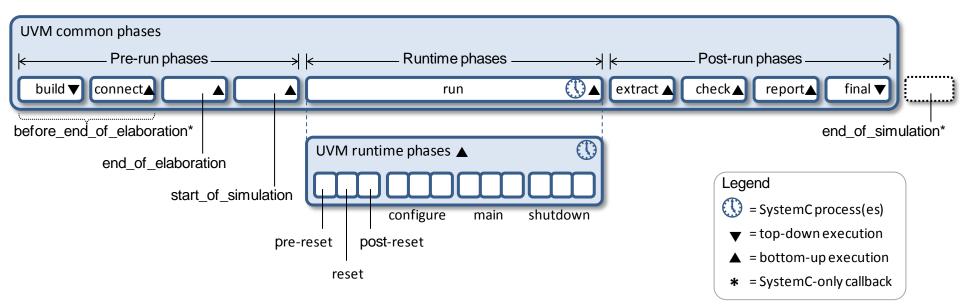

## **UVM-SystemC** phasing

- UVM phases are mapped on the SystemC phases

- UVM-SystemC supports the 9 common phases and the (optional) refined runtime phases

- Completion of a runtime phase happens as soon as there are no objections (anymore) to proceed to the next phase

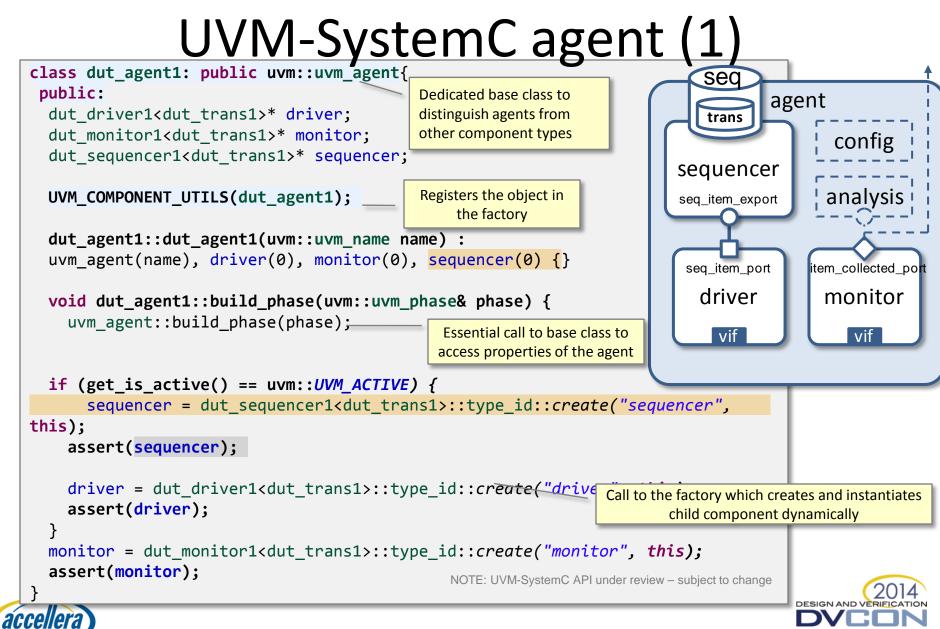

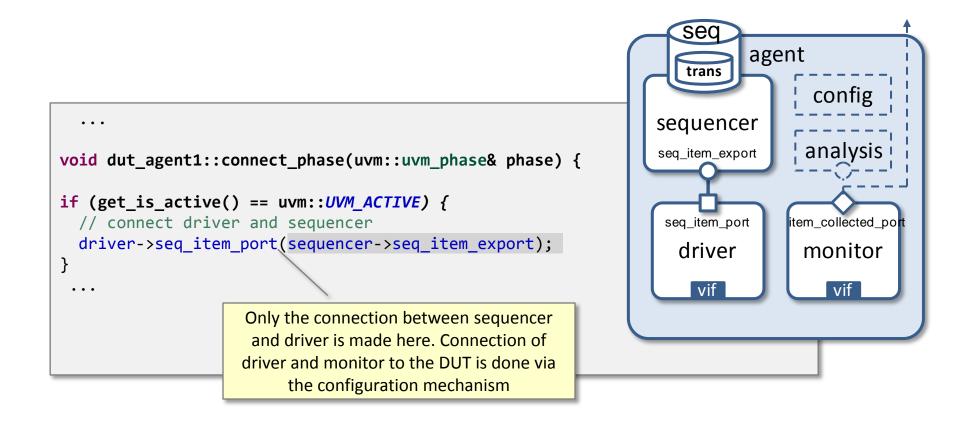

## UVM agent

- Component responsible for driving and monitoring the DUT :

- Typically contains three components

- Sequencer

- Driver

- Monitor

- Can contain analysis functionality for basic coverage and checking

- Possible configurations

- Active agent: sequencer and driver are enabled

- Passive agent: only monitors signals (sequencer and driver are disabled)

- C++ base class: uvm\_agent

| Seq ag          | gent                |

|-----------------|---------------------|

| (Tails)         | config              |

| sequencer       |                     |

| seq_item_export | analysis            |

|                 |                     |

| seq_item_port   | item_collected_port |

| driver          | monitor             |

| vif             | vif                 |

|                 |                     |

SYSTEMS INITIATIVE

#### UVM-SystemC agent (2)

NOTE: UVM-SystemC API under review - subject to change

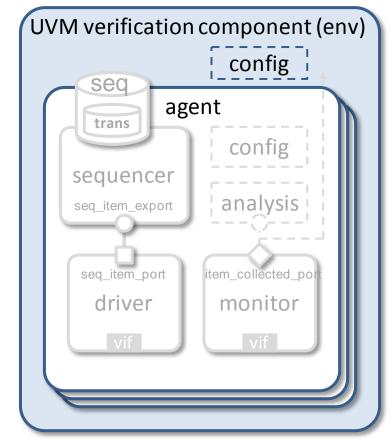

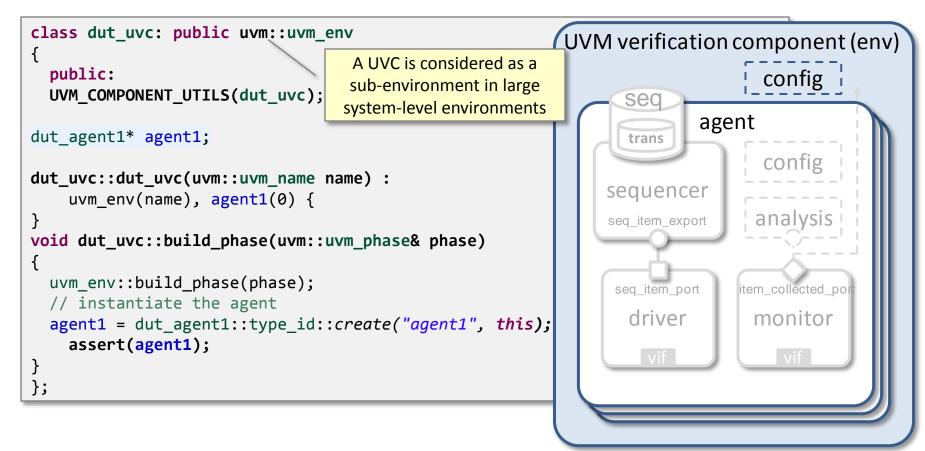

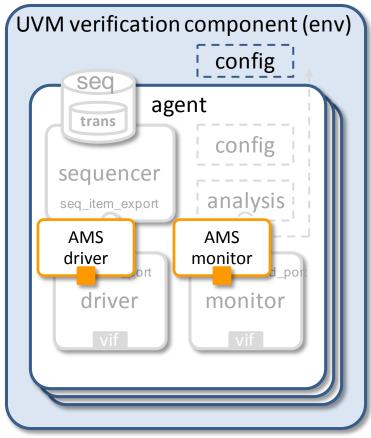

## UVM verification component

- A UVM verification component (UVC) is an environment which consists of one or more cooperating agents

- UVCs or agents may set or get configuration parameters

- Each verification component is connected to the DUT using a dedicated interface

- C++ base class: uvm\_env

#### UVM-SystemC verification component

In this example, the UVM verification component (UVC) contains only one agent

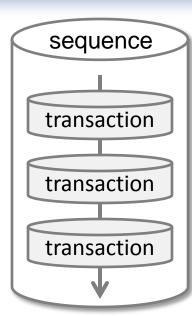

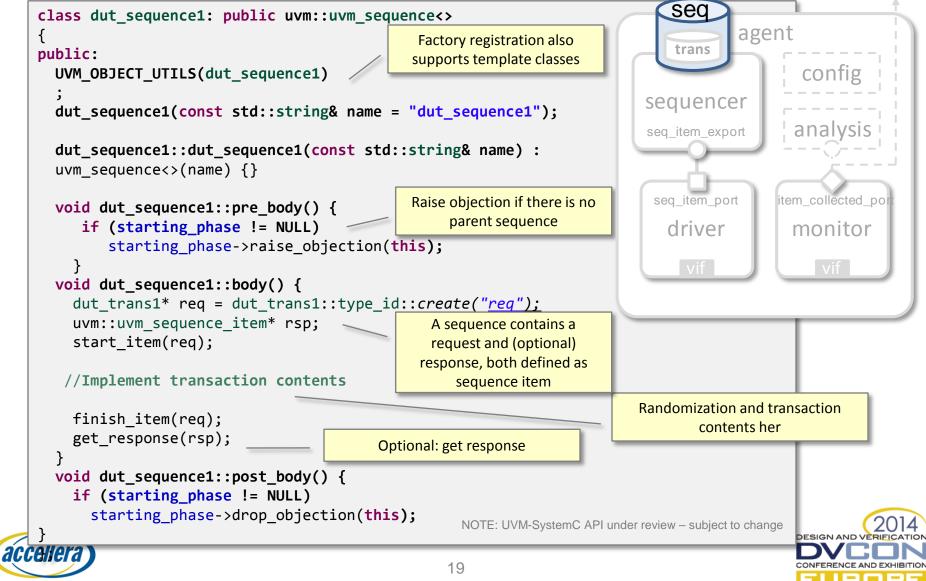

## UVM sequences

- Sequences are part of the test scenario and define streams of transactions

- The properties (or attributes) of a transaction are captured in a sequence item

- Sequences are not part of the test bench hierarchy, but are mapped onto one or more sequencers

- Sequences can be layered, hierarchical or virtual, and may contain multiple sequences or sequence items

- Sequences and transactions can be configured via the factory

seq1

trans

trans

seq2

trans

trans

seq

seq1

seq2

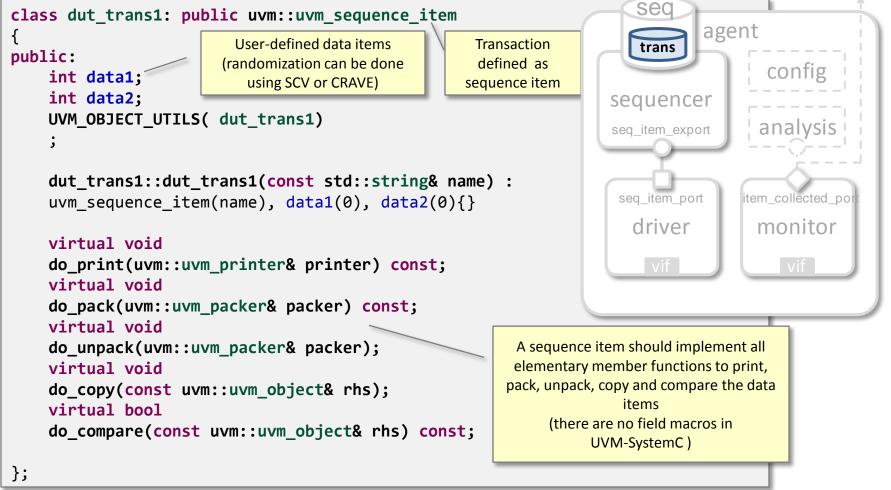

#### **UVM-SystemC** sequence item

NOTE: UVM-SystemC API under review - subject to change

#### UVM-SystemC sequence

SYSTEMS INITIATIVE

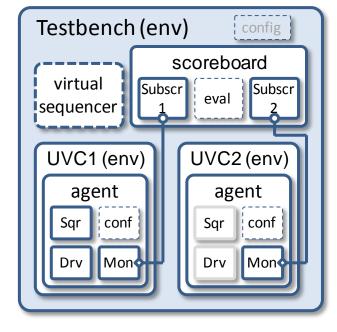

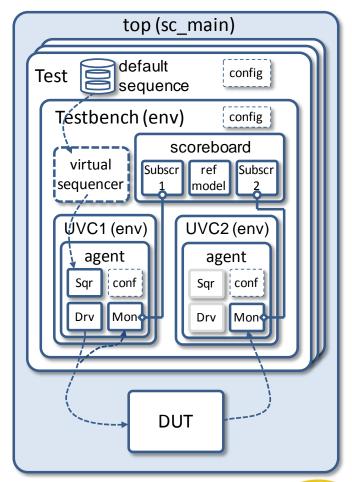

## UVM environment (test bench)

- A test bench is the environment which instantiates and configures the UVCs, scoreboard, and (optional) virtual sequencer

- The test bench connects

- Agent sequencer(s) in each UVC with the virtual sequencer (if defined)

- Monitor analysis port(s) in each UVC with the scoreboard subscriber(s)

- Note: The driver and monitor in each agent connect to the DUT using the interface stored in the configuration database

- C++ base class: uvm\_env

accellera

SYSTEMS INITIATIVE

### UVM-SystemC test bench (1)

class testbench : public uvm\_env

{

. public:

> vip\_uvc\* uvc1; vip\_uvc\* uvc2; virt\_sequencer\* virtual\_sequencer; scoreboard\* scoreboard1;

All components in the test bench will be dynamically instan-tiated so they can be overidden by the test if needed

```

UVM_COMPONENT_UTILS(testbench);

```

```

testbench( uvm_name name )

: uvm_env( name ), uvc1(0), uvc2(0),

virtual_sequencer(0), scoreboard1(0) {}

```

```

virtual void build_phase( uvm_phase& phase )

{

```

```

uvm_env::build_phase(phase);

```

```

uvc1 = vip_uvc::type_id::create("uvc1", this);

assert(uvc1);

uvc2 = vip_uvc::type_id::create("uvc2", this);

assert(uvc2);

```

```

set_config_int("uvc1.*", "is_active", UVM_ACTIVE); ___

set_config_int("uvc2.*", "is_active", UVM_PASSIVE);

```

Definition of active or passive UVCs

NOTE: UVM-SystemC API under review – subject to change

. . .

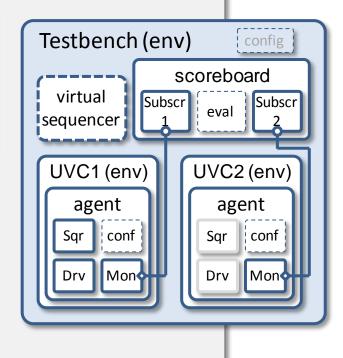

## UVM-SystemC test bench (2)

```

virtual sequencer = virt_sequencer::type_id::create(

Testbench (env)

"virtual sequencer", this);

assert(virtual sequencer);

virtual

Subscr

scoreboard1 =

sequencer

scoreboard::type_id::create("scoreboard1", this);

assert(scoreboard1);

UVC1 (env)

Virtual sequencer points to

}

UVC sequencer

agent

virtual void connect phase( uvm phase& phase )

conf

Sar

{

virtual sequencer->vip seqr = uvc1->agent->sequencer;

Mon

Drv

uvc1->agent->monitor->item collected port.connect(

scoreboard1->xmt listener imp);

uvc2->agent->monitor->item collected port.connect(

scoreboard1->rcv listener imp);

}

Analysis ports of the

monitors are connected to

};

the scoreboard subscribers

(listeners)

```

NOTE: UVM-SystemC API under review – subject to change

config

Subscr

scoreboard

eval

Sqr

Drv

UVC2 (env)

agent

conf

Mon

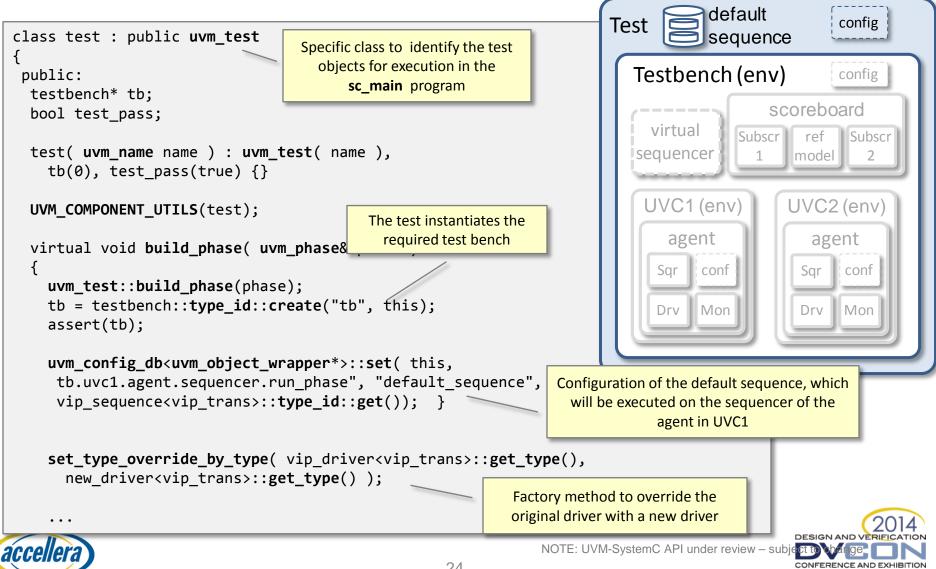

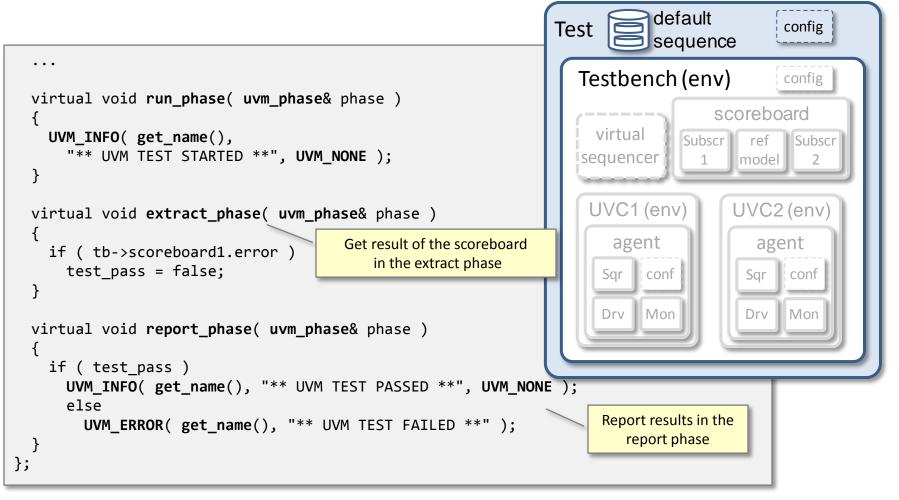

## UVM test

- Each UVM test is defined as a dedicated test class, which instantiates the test bench and defines the test sequence(s)

- Reuse of tests and topologies is possible by deriving tests from a test base class

- The UVM configuration and factory concept can be used to configure or override UVM components, sequences or sequence items

|       | C++ base class | : uvm | _test |

|-------|----------------|-------|-------|

| llera |                |       | 23    |

| Test default config             |

|---------------------------------|

| Testbench (env) [config]        |

| virtual<br>sequencer 1 subscr 2 |

| UVC1 (env) UVC2 (env)           |

| agent agent                     |

| Sqr conf Sqr conf               |

| Drv Mon Drv Mon                 |

### UVM-SystemC test (1)

SYSTEMS INITIATIVE

## UVM-SystemC test (2)

NOTE: UVM-SystemC API under review - subject to change

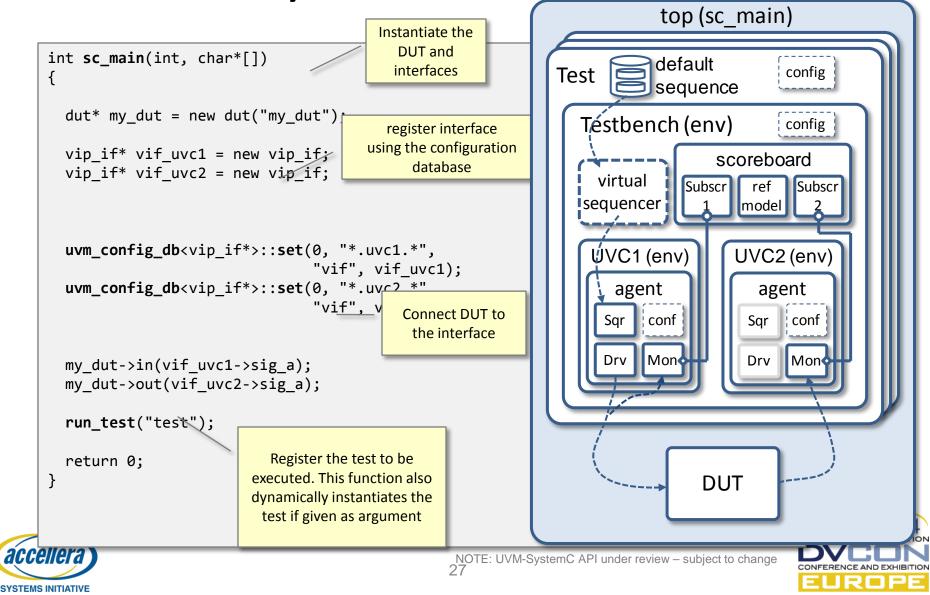

# The main program (top-level)

- The top-level (e.g. sc\_main) contains the test(s) and the DUT

- The interface to which the DUT is connected is stored in the configuration database, so it can be used by the UVCs to connect to the DUT

- The test to be executed is either defined by the test class instantiation or by the argument of the member function run\_test

#### UVM-SystemC main program

# Constrained randomization and functional coverage in UVM-SystemC

- Constrained randomization libraries for SystemC are available

- SystemC Verification Library (SCV)

- Constrained Random Verification Environment (CRAVE)

- No standardized functional coverage API in SystemC available

- Proprietary/commercial SystemC coverage APIs available, but not offered (yet) for standardization

- Proposals for randomization and coverage APIs exist

#### Demo

## UVM-SystemC-AMS

- The UVM-SystemC infrastructure can also handle AMS verification

- Transactions will program analog driver and monitors

- Drivers generate analog signals, Monitors analyze analog signals and extracting properties like amplitude, spectrum, ... and transfer them via transactions

- AMS verification requires continuous distribution function (and not PWC only)

- Randomization of DUT parameters is essential

# UVC with AMS driver and monitor using SystemC-AMS

- Regular UVM-SystemC drivers and monitors are used in which SystemC-AMS Timed Data Flow (TDF) modules are instantiated

- For the SystemC-AMS modules, TDF ports are necessary to allow read / write operations to the analog interface

- The parent driver and monitor establish the connection from the TDF ports to the interface via the configuration mechanism

SYSTEMS INITIATIVE

# Further UVM-SystemC-AMS extensions

- UVM AMS extensions will not break the existing UVM

- Time annotation to transaction

- Decoupled sequence time

- Data dependent synchronization

- Introducing of a pre-build phase under discussion

- Is executed before the DUT is instantiated

- Permits the setting of parameter, which influence the DUT creation

#### Demo

# Outline

- Introduction and Motivation

- Universal Verification Methodology (UVM) ... what is it?

- Why UVM in SystemC/C++/SystemC-AMS?

- UVM-SystemC overview

- UVM foundation elements

- UVM test bench and test creation

- Randomization and coverage

- Standardization within Accellera

- Applications and use cases of UVM-SystemC

- Summary and outlook

#### Standardization within Accellera

- UVM-SystemC Standardization within Accellera Verification WG is under way

- UVM-SystemC Language

Reference Manual (LRM)

available

- UVM-SystemC Proof-of-Concept implementation exists, released under Apache 2.0 license

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | L                     |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | L                     |

|        | UVM-SystemC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | L                     |

|        | (UVM-SC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                       |

|        | Language Reference Manual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | L                     |

|        | 1.0 DRAFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |

|        | 6.4 uvm_factory<br>The class wwm_factory implements a factory pattern. A singleton factory instance is created for a given us<br>run. Object and component types are registered with the factory using proxies to the actual objects and com-<br>being created. The classes wwm_object_registry=T> and wwm_component_registry=T> are used to prox<br>of type wwm_object and wwm_component respectively. These registry classes both use the wwm_object_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | aponents<br>y objects |

|        | 6.4.1 Class definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |

| 1 Octo | <pre>class uvm_factory {     public:     uvm_factory();     ~uvm_factory(); </pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                       |

|        | <pre>// Group: Begistering types void do_register' { uvm_object_vrapper' obj }; // is 'register' in UVN standard // area a a standard because the standard b</pre> |                       |

|        | // Group: Type & instance overrides<br>UVM-SystemC (UVM-SC) Language Reference Masual = 1.0 DRAFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Page 52               |

# Outline

- Introduction and Motivation

- Universal Verification Methodology (UVM) ... what is it?

- Why UVM in SystemC/C++/SystemC-AMS?

- UVM-SystemC overview

- UVM foundation elements

- UVM test bench and test creation

- Randomization and coverage

- Standardization within Accellera

- Applications and use cases of UVM-SystemC

- Summary and outlook

#### Applications and use cases of UVM-SystemC

- Enables new use cases

- New re-use scenarios

- IP protected, language and simulator independent verification IP

- Enables System-level UVM based verification

- Simplifies development of UVM based verification methods for AMS systems

#### Re-use across Languages, Simulators, Abstraction Levels

SYSTEMS INITIATIVE

IN

SYSTEMS INITIATIVE

# UVM for System-level / Functional verification

#### • Vision

- Translating specifications (documents, standards) to readable – also for non verification experts - test scenarios, this should also include ranges and uncertainties

- No separation between analog/digital, hard- and software

- "real" system-level verification

#### • Main question:

– Will the system work for the purposes for which it will be built?

# Challenges for UVM System-level

- No executable reference model available

- Complex stimulation and expected sequences

- Coverage measure is different to implementation level

- How much of the possible application scenarios, input stimuli, operating conditions, specification items are verified?

→ UVM methodology/best practices have to be extended for system level!

→ UVM framework is generic enough to realize the required extensions needed for System level verification!

## Outline

- Introduction and Motivation

- Universal Verification Methodology (UVM) ... what is it?

- Why UVM in SystemC/C++/SystemC-AMS?

- UVM-SystemC overview

- UVM foundation elements

- UVM test bench and test creation

- Randomization and coverage

- Standardization within Accellera

- Applications and use cases of UVM-SystemC

- Summary and outlook

## Summary and outlook (1)

- Universal Verification Methodology created in SystemC/C++

- Fully compliant with UVM standard

- Target is to make all essential features of UVM available in SystemC/C++

- UVM-SystemC language definition and proof-of-concept implementation contributed to Accellera Systems Initiative

- SystemC-AMS is used for AMS system-level verification use cases

## Summary and outlook (2)

#### • Ongoing developments

- Extend UVM-SystemC with constrained randomization capabilities using SystemC Verification Library (SCV) or CRAVE

- Introduction of randomization and functional coverage features

- Add register abstraction layer and callback mechanism

- Develop UVM based AMS and system-level verification methods

### Acknowledgements

The development of the UVM-SystemC methodology and library has been supported by the European Commission as part of the Seventh Framework Programme (FP7) for Research and Technological Development in the project 'VERIFICATION FOR HETEROGENOUS RELIABLE DESIGN AND INTEGRATION' (VERDI). The research leading to these results has received funding from the European Commission under grand agreement No 287562.

#### Resources

- SystemC, SystemC-AMS, UVM Standards

- <u>www.accellera.org</u>

- SystemC proof-of-concept

- <u>www.accellera.org/downloads/standards/systemc</u>

- SystemC-AMS proof-of-concept

- www.coside.de/open source.html

- Verdi project site (e.g. publications, tutorials for UVM SystemC)

- <u>www.verdi-fp7.eu</u>

- Crave randomization library

- www.systemc-verification.org/

#### Questions

# Guidelines (1)

Please keep the default font size for main lines at 28pt (or 26pt)

- And use 24pt (or 22pt) font size for the sub bullets

- Use the default bullet style and color scheme supplied by this template

- Limited the number of bullets per page.

- Use keywords, not full sentences

- Please do not overlay Accellera or DVCon logo's

- Check the page numbering