UVM Rapid Adoption: A Practical Subset of UVM

Stuart Sutherland, Sutherland-HDL, Inc. Tom Fitzpatrick, Mentor Graphics Corp. presented by Gordon Allan, Mentor Graphics, Corp

### The Problem...

SYSTEMS INITIATIVE

The UVM 1.2 Library has 357 classes, 938 functions, 99 tasks, and 374 macros

### The Goals of this Paper

- Understand why the UVM library is so complex

- Examine UVM from three different perspectives

- The Environment Writer

- The Test Writer

- The Sequence Writer

- Define a practical subset of UVM that meets the needs of nearly all verification projects

- A subset makes UVM easier to learn, use & maintain!

You will be amazed at how small of a subset of UVM you really need!

# Why the UVM Library Is Overly Large and Complex

- Why 357 classes, 1037 methods, 374 macros?

- The history of UVM adds to UVM's complexity

- UVM evolved from OVM, VMM and other methodologies

- UVM adds to and modifies previous methodologies

- UVM contains "old ways" and "new ways" to do things

- Object Oriented Programming adds complexity

- OOP extends and inherits functionality from base classes

- uvm\_driver inherits from uvm\_component which inherits from uvm\_object which inherits from ...

- Only a small number of UVM classes, methods and macros are intended to be used by end users

- Much of the UVM library is for use within the library

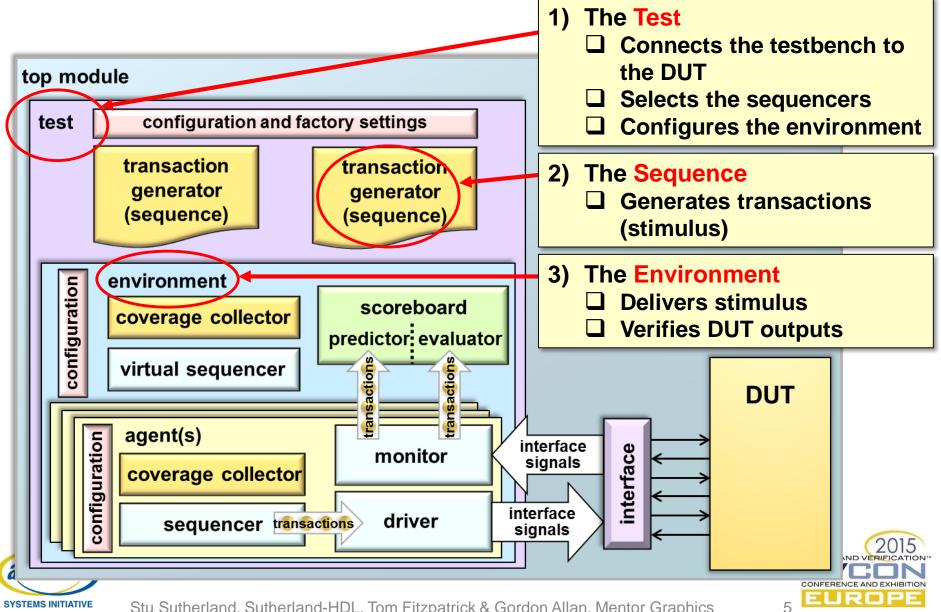

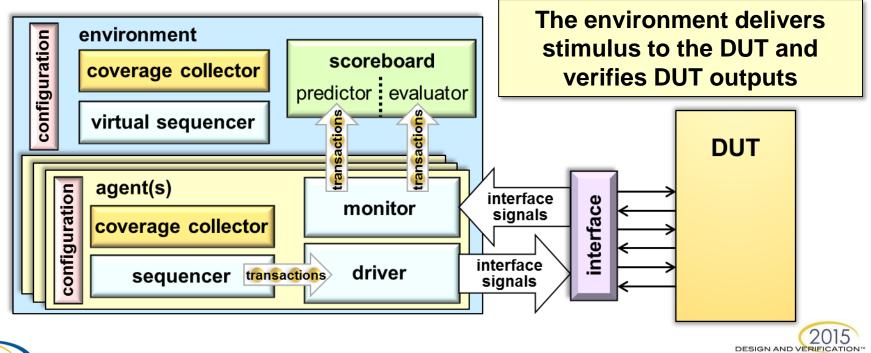

### Three Aspects of a UVM Testbench

# UVM Constructs Used By The Environment Writer

2015 DESIGN AND VERIFICATION THE CONFERENCE AND EXHIBITION EUROPE

## The Role of the Environment Writer

- The **Environment Writer** defines the testbench parts

- Agents

- Monitors

Sequencers

- Scoreboards

- Drivers

Coverage collectors

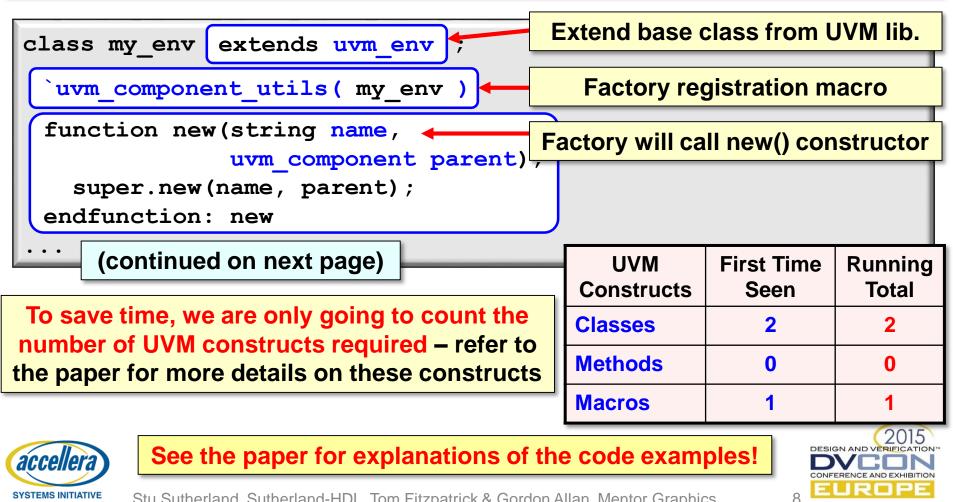

### The Environment Component

About the examples in this presentation:

- UVM-specific constructs are shown in **blue** text

- UVM constructs not shown in previous examples are shown in boxed text

## The Environment Component (cont.)

| <ul> <li>Environments encapsulate</li> </ul>                                                                                                                                                             | UVM<br>Constructs                                     | First Time<br>Seen         | Running<br>Total |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------|------------------|--|

| an agent and scoreboard                                                                                                                                                                                  | Classes                                               | 0                          | 2                |  |

|                                                                                                                                                                                                          | Methods                                               | 4                          | 4                |  |

|                                                                                                                                                                                                          | Macros                                                | 0                          | 1                |  |

| <pre>my_agent agent;<br/>my_scoreboard scorebd;</pre>                                                                                                                                                    | The "build phase" uses factory to "create" components |                            |                  |  |

| <pre>function void build_phase(uvm_phase phase);     agent = my_agent::type_id::create("agent", this);     scorebd = my_scoreboard::type_id::create("scorebd", this);     endfunction: build_phase</pre> |                                                       |                            |                  |  |

| <pre>function void connect_phase(uvm_phase phase);     agent.dut_inputs_port.connect(scorebd.dut_in_imp_export);     agent.dut_outputs_port.connect(scorebd.dut_out_imp_export);</pre>                   |                                                       |                            |                  |  |

| endfunction: connect_phase<br>endclass: my env                                                                                                                                                           | The "conne<br>"connect"                               | ct phase" is<br>' componer |                  |  |

| accellera                                                                                                                                                                                                |                                                       |                            |                  |  |

CONFERENCE AND EXHIBITION

Q

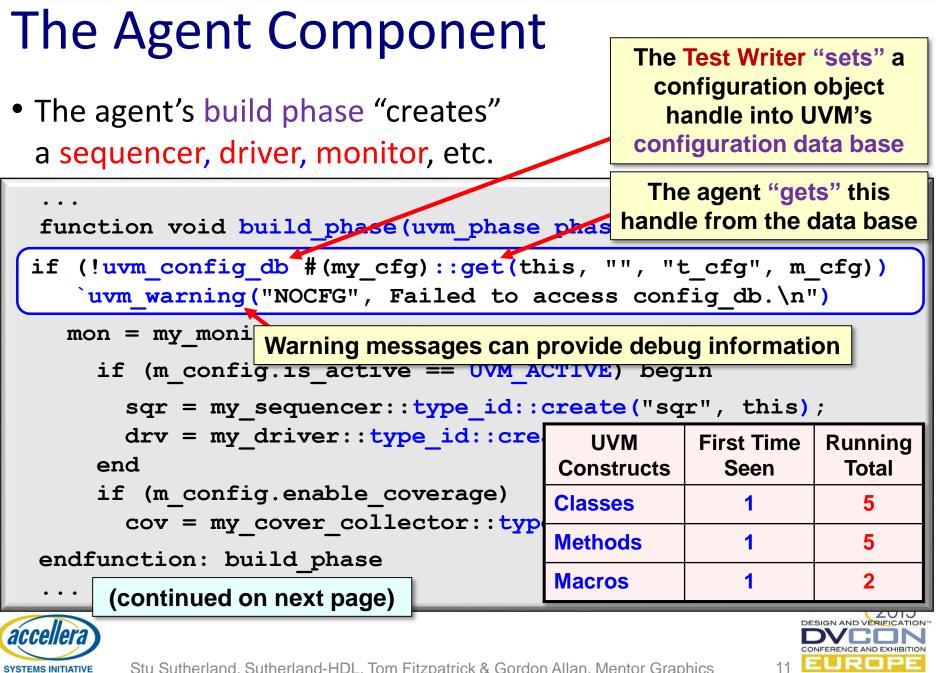

## The Agent Component

An agent encapsulates low-level components needed to drive and monitor a specific interface to the DUT

| <pre>class my_agent extends uvm_agent ; &lt;</pre>                                                      | Extend agent's UVM base class |                            |                  |  |

|---------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------|------------------|--|

| <pre>`uvm_component_utils(my_agent) function new(string name, uvm compo</pre>                           | UVM<br>Constructs             | First Time<br>Seen         | Running<br>Total |  |

| <pre>super.new(name, parent);</pre>                                                                     | Classes                       | 2                          | 4                |  |

| endfunction: new                                                                                        | Methods                       | 0                          | 4                |  |

| <pre>// handles for agent's components</pre>                                                            | Macros                        | 0                          | 1                |  |

| my_sequencer sqr;                                                                                       |                               |                            |                  |  |

| <pre>my_driver drv;<br/><br/>// handles to the monitor's ports</pre>                                    | dd ports to t<br>defined in   | the monitor<br>the UVM lik | ·                |  |

| <pre>uvm_analysis_port #(my_tx) dut_inputs_port;<br/>uvm_analysis_port #(my_tx) dut_outputs_port;</pre> |                               |                            |                  |  |

| (continued on next page)                                                                                |                               |                            | (2015)           |  |

| SYSTEMS INITIATIVE Stu Sutherland, Sutherland-HDL, Tom Fitzpatrick & Gordon                             | n Allan, Mentor Gran          | hics 10                    |                  |  |

# The Agent Component (continued)

• The agent's connect\_phase connects the agent's components together No additional UVM

| • • •                                                                                                                                | l    | cons            | tructs need        | ed!              |

|--------------------------------------------------------------------------------------------------------------------------------------|------|-----------------|--------------------|------------------|

| <pre>function void connect_phase(uvm_pha     // set agent's ports to point to</pre>                                                  |      | UVM<br>nstructs | First Time<br>Seen | Running<br>Total |

| dut_inputs_port = mon.dut_inputs                                                                                                     | Clas |                 | 0                  | 5                |

| <pre>dut_outputs_port = mon.dut_output</pre>                                                                                         | Met  | hods            | 0                  | 5                |

| <pre>if (is_active == UVM_ACTIVE)     // connect driver to sequencer</pre>                                                           | Mac  | ros             | 0                  | 2                |

| drv.seq_item_port.connect(sqr.seq_item_export);                                                                                      |      |                 |                    |                  |

| if (enable_coverage)                                                                                                                 |      |                 |                    |                  |

| <pre>// connect monitor to coverage collector     mon.dut_inputs_port.connect(cov.analysis_export); endfunction: connect_phase</pre> |      |                 |                    |                  |

| endclass: my_agent                                                                                                                   |      |                 |                    |                  |

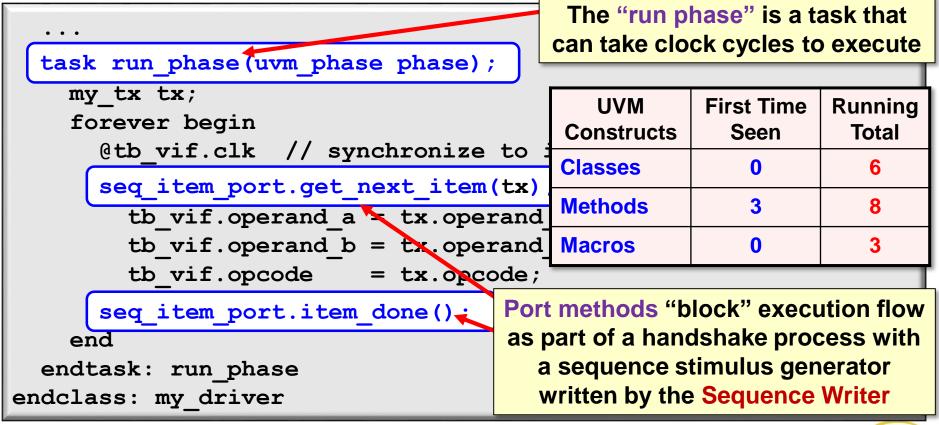

## The Driver Component

• The driver receives transactions from a sequencer and drives values to the DUT via a virtual interface

| <pre>class my_driver extends uvm_driver #(my_tx) ;</pre>           |                                |                    |                  |  |

|--------------------------------------------------------------------|--------------------------------|--------------------|------------------|--|

| <pre>`uvm_component_utils(my_driver)</pre>                         | Extend driver's UVM base class |                    |                  |  |

| <pre>function new(string name, uvm_component parent);</pre>        |                                |                    |                  |  |

| <pre>super.new(name, parent); endfunction</pre>                    | UVM<br>Constructs              | First Time<br>Seen | Running<br>Total |  |

| <pre>virtual tb_if tb_vif; // virtual i</pre>                      | Classes                        | 1                  | 6                |  |

| function void build_phase(uvm_phase                                |                                | 0                  | 5                |  |

| <pre>if (!uvm_config_db #(virtual my_d</pre>                       | Macros                         | 1                  | 3                |  |

| <pre>`uvm_fatal("NOVIF", Failed virtutal interface from db")</pre> |                                |                    |                  |  |

| endfunction: build_phase A fatal er                                | ror report te                  | rminates si        | mulation         |  |

|                                                                    |                                |                    | 2015             |  |

# The Driver Component (continued)

The driver receives transactions from a sequencer and drives values to the DUT via a virtual interface

# **Additional Components**

- UVM<br/>ConstructsFirst Time<br/>SeenRunnin<br/>g TotalClasses39Methods210Macros25

- A sequencer routes stimulus to driver

- Specializes the uvm\_sequencer base class

- No additional UVM constructs are needed

- A monitor observes DUT ports via a virtual interface

- Extends the uvm\_monitor base class

- Only additional UVM construct needed that has not already been shown is an analysis port write() method

- A scoreboard verifies DUT output value correctness

- Extends uvm\_subscriber or uvm\_component

- Only additional UVM constructs that might be needed are: report\_phase(), `uvm\_info() and `uvm\_analysis\_imp\_decl()

- A coverage collector performs functional coverage

- No additional UVM constructs are needed

# UVM Constructs Used By The Test Writer

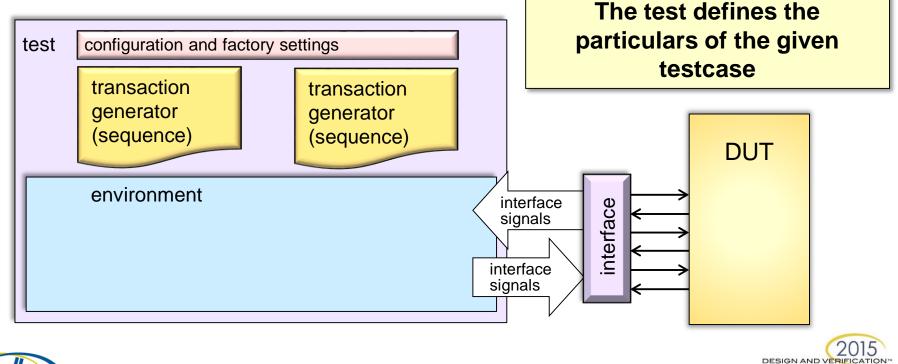

## The Role of the UVM Test Writer

- The Test Writer defines the specifics of a testcase

- Connects the testbench to the DUT

- Selects the sequences

- Configures the environment

# The Top-Level Module

| <ul> <li>Top-level module connects<br/>DUT and starts test</li> </ul>                                                                                | UVM<br>Constructs                                                                  | First Time<br>Seen | Running<br>Total |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------|------------------|--|

| module test top;                                                                                                                                     | Classes                                                                            | 0                  | 9                |  |

| import uvm pkg::*;                                                                                                                                   | Methods                                                                            | 2                  | 12               |  |

| <pre>import my_test_pkg::*;</pre>                                                                                                                    | Macros                                                                             | 0                  | 5                |  |

| <pre>my_dut_interface my_dut_if();<br/>my_dut_rtl my_dut(.if(my_dut_if()))<br/>initial begin</pre>                                                   | The "set" method is how the Test<br>Writer sends information down<br>the hierarchy |                    |                  |  |

| uvm config db #(virtual my dut interface)::set(null,                                                                                                 |                                                                                    |                    |                  |  |

| <pre>uvm_config_db #(virtual my_dut_interface)::set(hull,                                  "uvm_test_top", "DUT_IF", my_dut_if); end endmodule</pre> |                                                                                    |                    |                  |  |

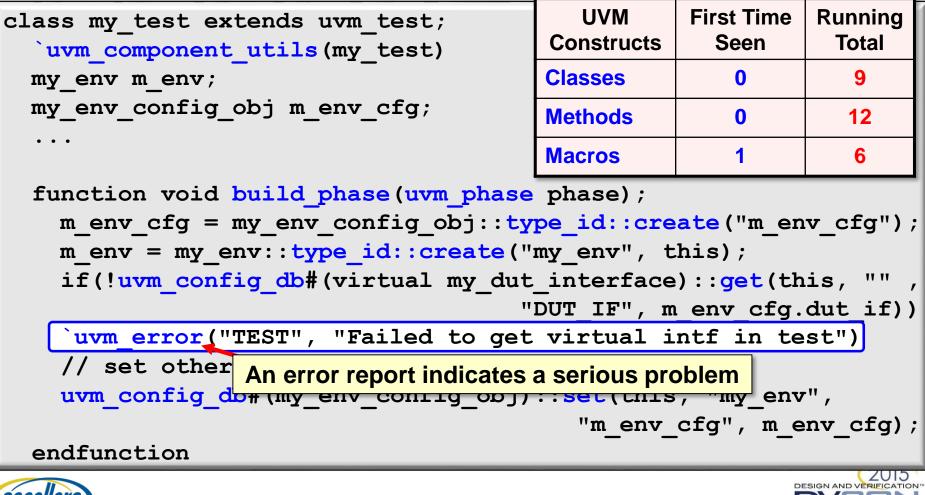

### The Base Test

#### Test instantiates & configures the environment

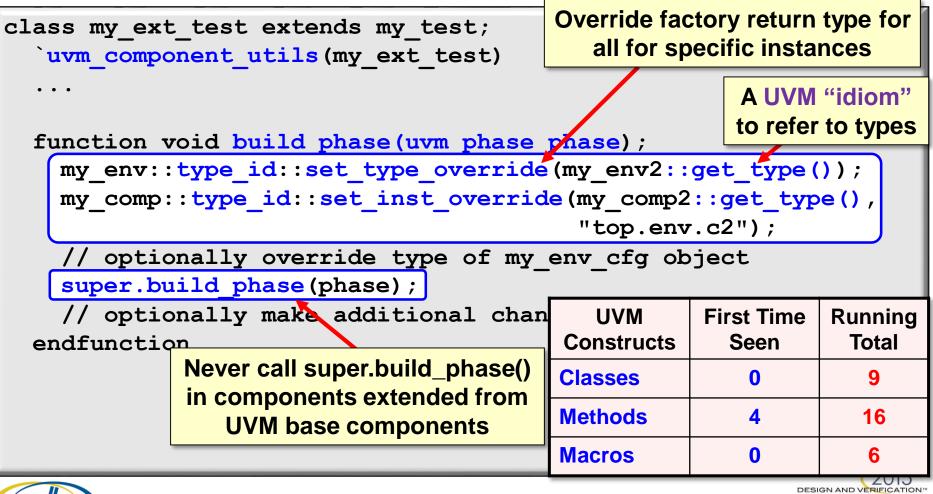

## The Extended Test

• The extended test specializes the base test

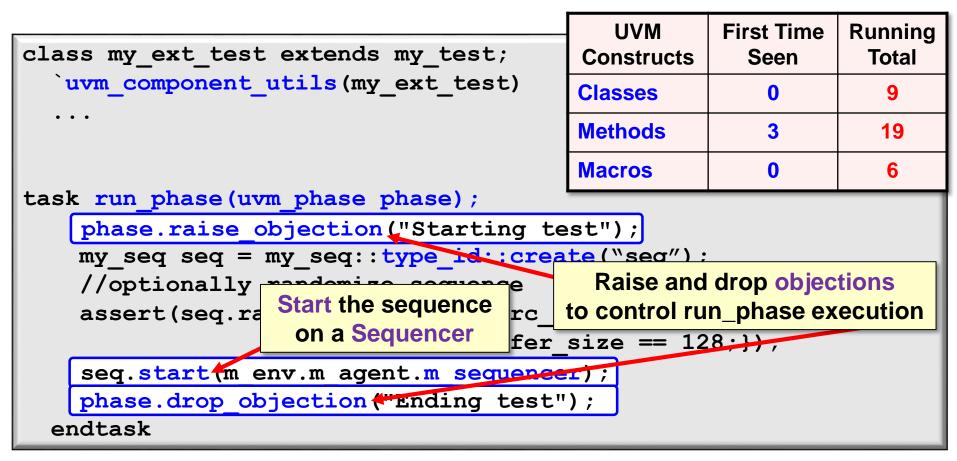

## The Extended Test

• The test starts sequences and manages objections

# UVM Constructs Used By The Sequence Writer

### The Sequence Writer

- Each sequence defines stimulus and/or response functionality

- Provide list of sequence types and sequencer types to start them on

- Inheritance hierarchy and other details irrelevant to Test Writer

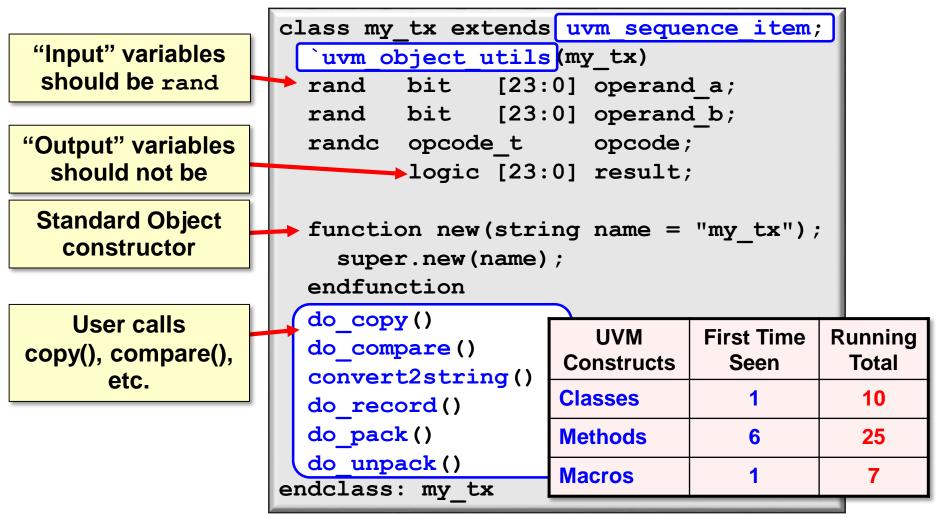

### **Designing a Sequence Item**

Alternately use `uvm\_field\_xxx macros (73) to auto-generate the do\_ methods

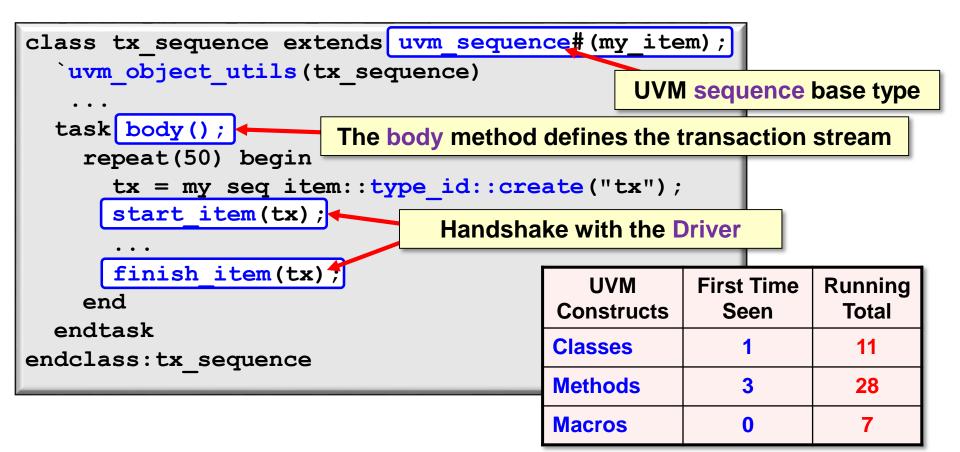

### The Sequence Body Method

• The body method defines the transactions to generate

## The Virtual Sequence

• The virtual sequence starts subsequences

```

class my vseq extends uvm sequence#(uvm sequence item);

bus sequencer t bus sequencer;

gpio sequencer t gpio sequencer;

virtual function void init(uvm sequencer bus seqr,

uvm sequencer gpio seqr);

bus sequencer = bus seqr;

First Time

Running

gpio sequencer = gpio seqr;

UVM

Constructs

Seen

Total

endfunction

Classes

11

0

task body();

Methods

0

28

aseq.start( bus sequencer , this )

Macros

0

7

bseq.start( gpio sequencer , this

endtask

endclass

```

# UVM Constructs Used For Advanced Examples

2015 DESIGN AND VERIFICATION CONFERENCE AND EXHIBITION

## phase\_ready\_to\_end

• Delay the end of a phase when necessary

| <pre>function void my_comp::phase_ready_to if( !is_ok_to_end() ) begin     phase.raise_objection( this , "no     fork begin</pre> |                   | Delay and          | of phase         |

|-----------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------|------------------|

| <pre>wait_for_ok_end();     phase.drop_objection( this , "o     end     join none</pre>                                           | ok to end pł      | nase");            |                  |

| end<br>endfunction : phase ready to end                                                                                           | UVM<br>Constructs | First Time<br>Seen | Running<br>Total |

|                                                                                                                                   | Classes           | 0                  | 11               |

|                                                                                                                                   |                   |                    |                  |

|                                                                                                                                   | Methods           | 1                  | 29               |

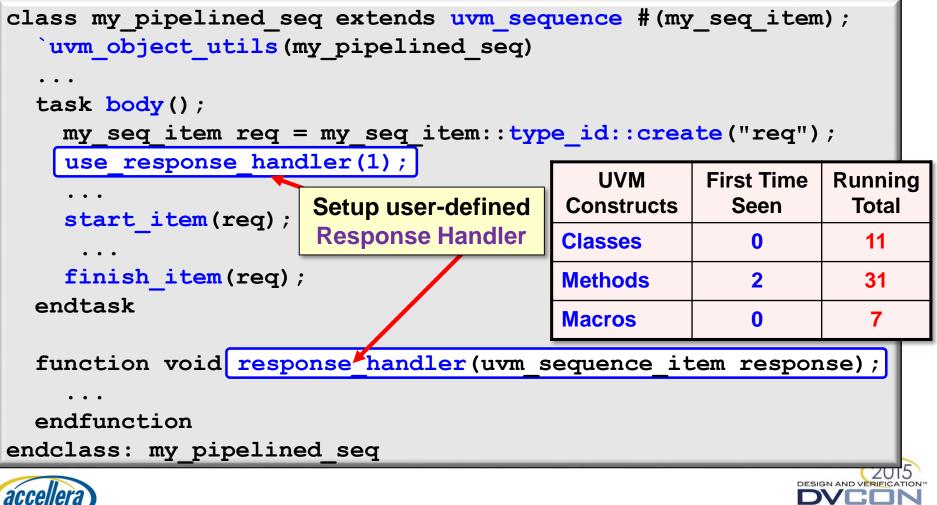

## **Pipelined Protocols**

• Use the Response Handler in the sequence

SYSTEMS INITIATIVE

Stu Sutherland, Sutherland-HDL, Tom Fitzpatrick & Gordon Allan, Mentor Graphics

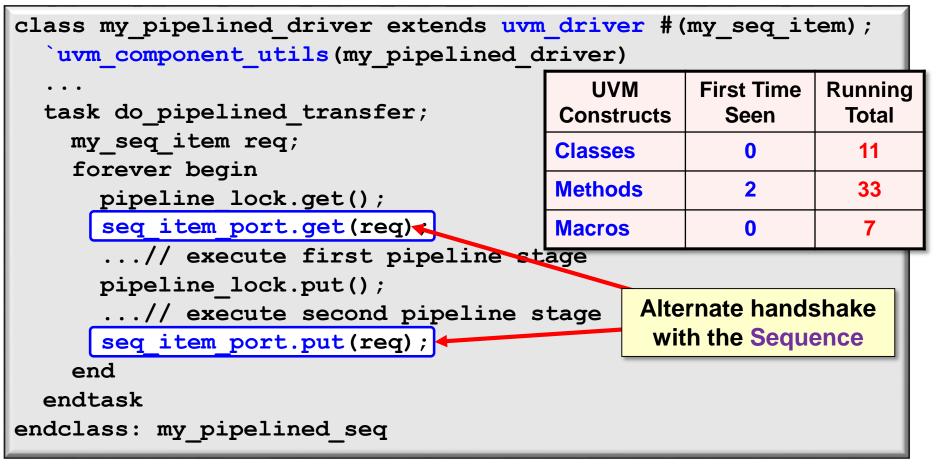

# **Pipelined Protocols**

• Driver uses one thread per pipeline stage

20

DESIGN AND VERIEI

### **UVM Features to Avoid**

- Phase Jumping

- Callbacks

- Most UVM 1.2 features

- These features only make UVM unnecessarily complex, difficult to code, and difficult maintain, and difficult to re-use

### The Solution...

The UVM 1.2 Library has 357 classes, 938 functions, 99 tasks, and 374 macros

- Our recommended subset in the paper uses 11 classes, 33 tasks/functions and 7 macros

- You really only need to learn 3% of UVM to be productive!

- 2% of classes

- 3% of methods