# **Using Mutation Coverage** for Advanced Bug Hunting

#### Vladislav Palfy & Nicolae Tusinschi—OneSpin Solutions

making electronics reliable

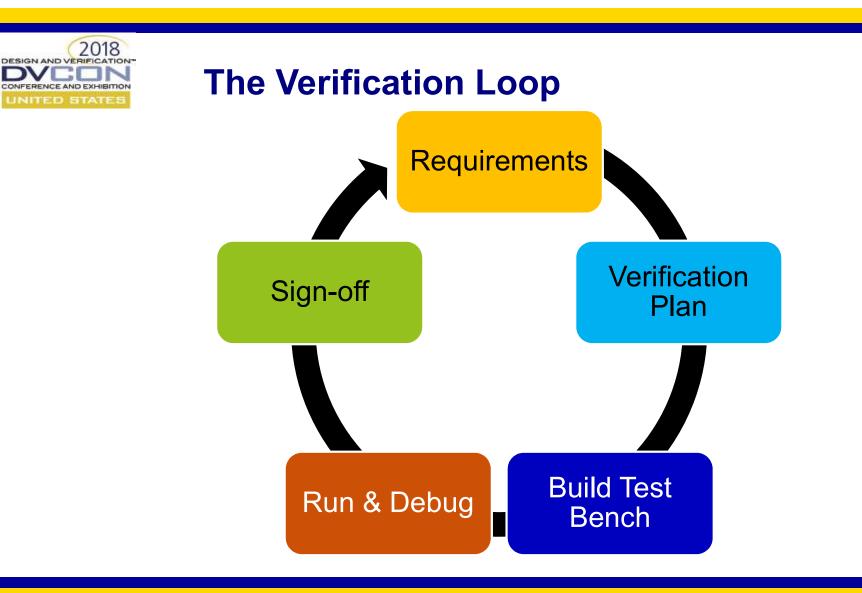

# Assessing Quality of Verification

If you don't measure, you don't know

#### When am I done?

Have I written enough stimuli to cover all requirements?

What part of the design has been exercised by my assertions/covers?

Have I written good quality checks?

Which parts of the design have been checked by my checkers?

Are all specified functions implemented?

Are all specified functions verified?

**Coverage & Bug Hunting** Two sides of the same coin

- Both coverage and bug hunting are important

- Where coverage is analytical, bugs are anecdotal

- ✤ 100% coverage with bugs in the design is unacceptable

- Extracting coverage should be quick and easy

- Report data must be meaningful

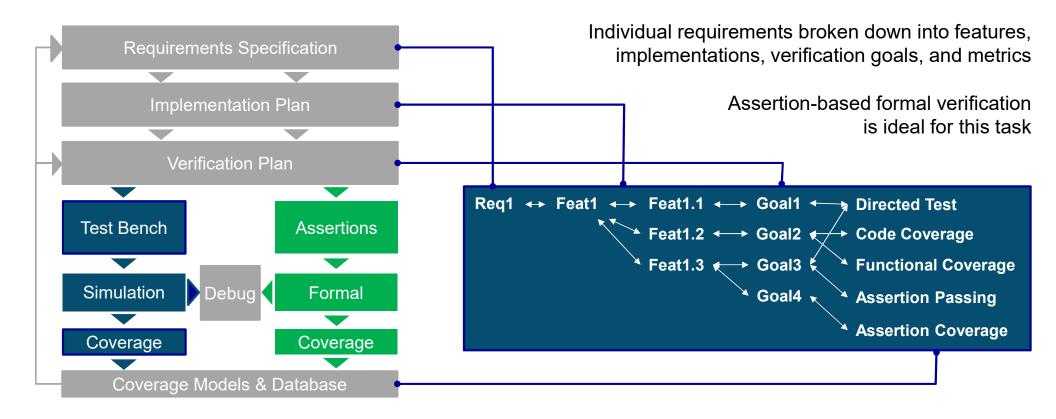

#### **Quantify MDV Overview** Multi-dimensional view—quantity and quality

#### Assessing the *quality* of verification by providing a *quantitative* metric

#### Quantify

- Takes as input a hardware design and a formal test bench

- One push of a button produces a metric-driven sign-off report as output

#### Structural Coverage (Quantity)

Control & Observation Coverage—provides quantitative assessment

#### Functional Coverage (Quality)

✤ Assertion Coverage—provides qualitative assessment

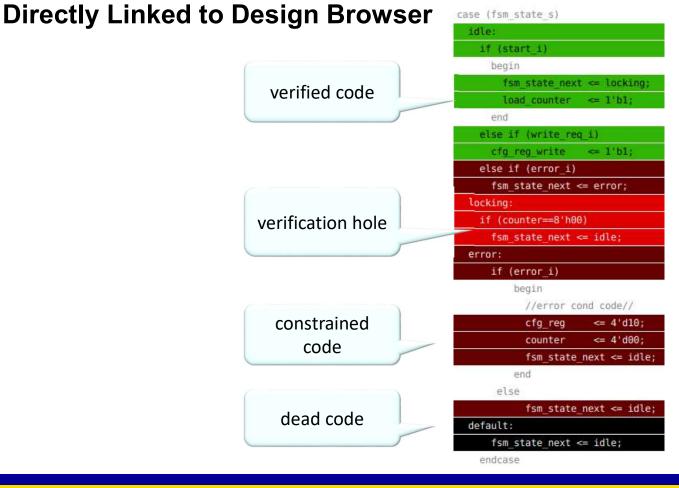

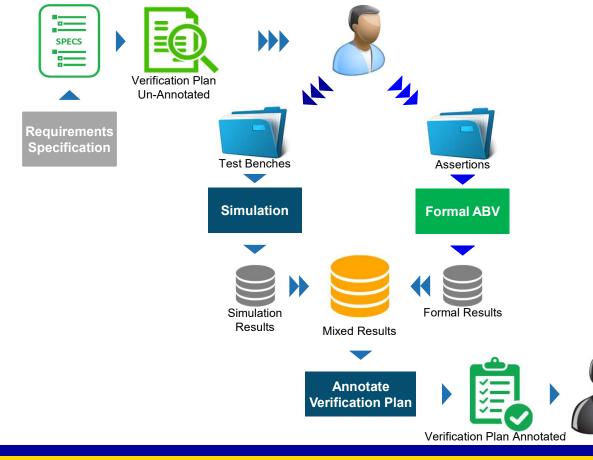

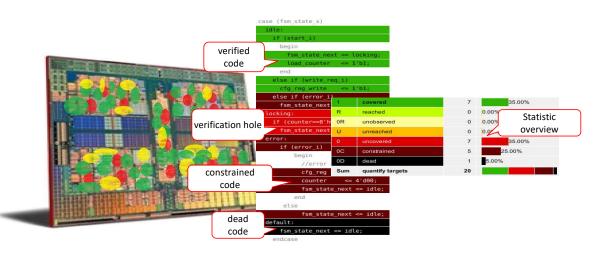

## **Coverage Solution: Provides Meaningful Metrics** Continuous feedback for design and verification

#### Designer Bring Up: Get feedback on the quality of design bring up

- Dead code; reachability

- Redundant code

#### Verification: When quality and quantity both matter

- Metrics should indicate gaps in verification and show you where these are

- Missing checks

- Over-constraints

- Find bugs

# **Quantify Report**

#### **Color-coded highway to sign-off**

|                 | Result      | Meaning                                       |  |  |  |

|-----------------|-------------|-----------------------------------------------|--|--|--|

|                 | Reached     | Reached by an Assertion                       |  |  |  |

| Controllability | Constrained | Unreachable & Unobservable Due to Constraints |  |  |  |

|                 | Dead        | Unreachable and Unobservable                  |  |  |  |

|                 | Uncovered   | Not Reached and Not Observed                  |  |  |  |

| Observability   | Covered     | Observed and Reached                          |  |  |  |

|                 | Unobserved  | Reached and Not Observed                      |  |  |  |

## **Quantify Dashboard View: Important Components**

| Struc  | ctural Coverage Overview      |          |        |              |            |          |              |              |            |  |

|--------|-------------------------------|----------|--------|--------------|------------|----------|--------------|--------------|------------|--|

| Status | s                             | nts      |        |              | Branch     | ies      |              |              |            |  |

| 1      | covered                       | 12       |        | 80.00%       |            | 4        |              | 100.00%      |            |  |

| R      | reached                       | 0        | 0.00%  |              |            | 0        | 0.00%        |              |            |  |

| U      | unknown                       | 0        | 0.00%  |              |            | 0        | 0.00%        |              |            |  |

| 0R     | unobserved                    | 3        | 20.    | .00%         |            | 0        | 0.00%        |              |            |  |

| 0      | uncovered                     | 0        | 0.00%  |              |            | 0        | 0.00%        |              |            |  |

| 0C     | constrained                   | 0        | 0.00%  |              |            | 0        | 0.00%        |              |            |  |

| 0D     | dead                          | 0        | 0.00%  |              |            | 0        | 0.00%        |              |            |  |

| Sum    | quantify targets              | 15       |        |              |            | 4        |              |              |            |  |

| Exclu  | uded Code Overview            |          |        |              |            |          |              |              |            |  |

| Code   | Status                        | Statemer | nts    |              |            | Branches |              |              |            |  |

| Xu     | excluded by user              | 0        | 0.00%  | Ó            |            |          | 0.00%        |              |            |  |

| Xr     | excluded redundant code       | 0        | 0.00%  | 0%           |            | 0        | 0.00%        |              |            |  |

| Xv     | excluded verification code    | 15       |        | 50.00%       |            | 8        | 66.67        | 66.67%       |            |  |

| 0/1/U  | quantify targets              | 15       |        | 50.00%       |            | 4        | 33.33%       | 33.33%       |            |  |

| Sum    | total code                    | 30       |        |              |            | 12       |              |              |            |  |

| Asse   | rtion Coverage                |          |        |              |            |          |              |              |            |  |

| ld     | Property                      | ł        | Kind   | Proof Result | Proof Radi | us       | Cover Result | Cover Radius | Quantified |  |

| 0      | sva/as_empty_from_fullassert  |          | issert | FORMAL_PROOF | infinite   |          | COVER_PASS   | 9            | yes        |  |

| 1      | sva/as full from empty        | a        | assert | FORMAL_PROOF | infinite   | 1        | COVER_PASS   | 1            | yes        |  |

| 2      | sva/u fifo /as ordering check | a        | ssert  | FORMAL_PROOF | infinite   |          | COVER PASS   | 2            | yes        |  |

# **Quantify Dashboard**

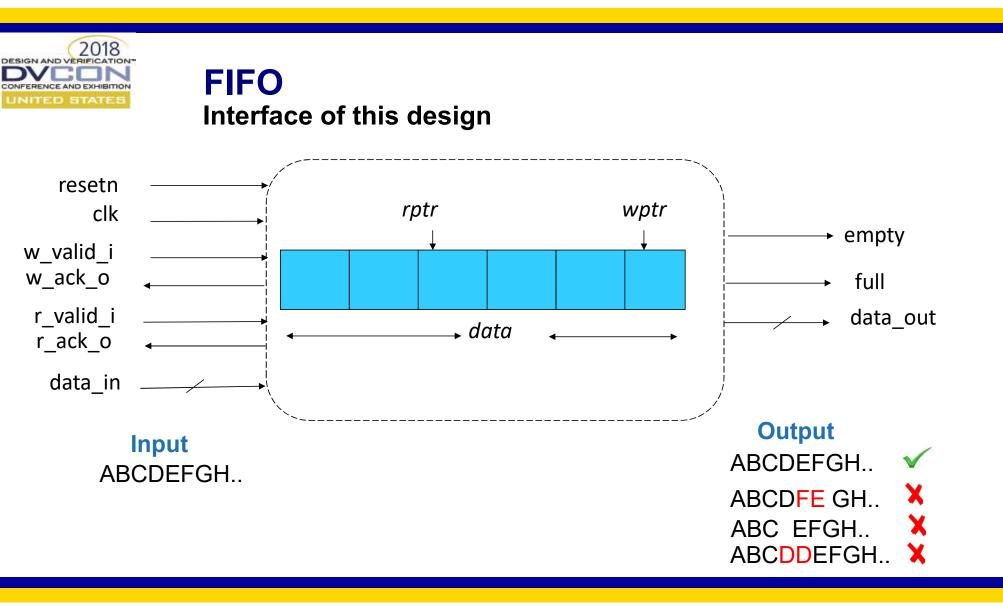

# **Quantify in Action**

**FIFO Example**

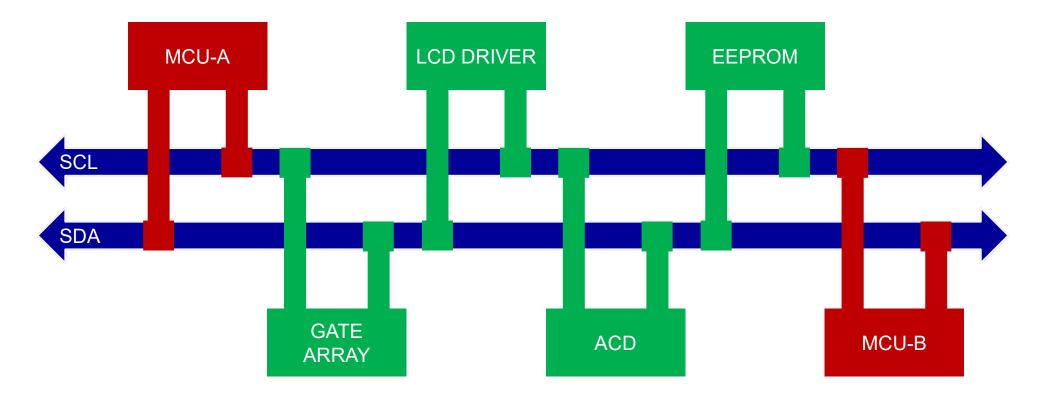

# **Requirements for Verification**

| Ordering is correct                                                                                                                 |  |

|-------------------------------------------------------------------------------------------------------------------------------------|--|

| No duplication                                                                                                                      |  |

| No data loss                                                                                                                        |  |

| No data corruption                                                                                                                  |  |

| Empty and full checks                                                                                                               |  |

| <ul> <li>Must be empty at the right time</li> <li>Must be full at the right time</li> <li>If empty, then eventually full</li> </ul> |  |

✤If full, then eventually empty

#### **Quantify on FIFO Example—I** With no checks at all

| Struct | ural Coverage Overview | 1        |         |        |     |         |          |

|--------|------------------------|----------|---------|--------|-----|---------|----------|

| Status |                        | Statemen | IS      | Branch | nes |         |          |

| 1      | covered                | 0        | 0.00%   | 0      | 0.0 | 0%      |          |

| \$     | reached                | 0        | 0.00%   | 0      | 0.0 | 0%      |          |

| U      | unknown                | 0        | 0.00%   | 0      | 0.0 | 0%      |          |

| 0R     | unobserved             | 0        | 0.00%   | 0      | 0.0 | 0%      |          |

| )      | uncovered              | 22       | 100.00% | 7      |     | 100.00% | VERIFICA |

| )C     | constrained            | 0        | 0.00%   | 0      | 0.0 | 0%      |          |

| 0D     | dead                   | 0        | 0.00%   | 0      | 0.0 | 0%      |          |

| Sum    | quantify targets       | 22       |         | 7      |     |         |          |

| Asser | tion Coverage |      |              |              |              |              |            |

|-------|---------------|------|--------------|--------------|--------------|--------------|------------|

| ld    | Property      | Kind | Proof Result | Proof Radius | Cover Result | Cover Radius | Quantified |

| File Status |               |          |        |                                                                  |  |  |  |

|-------------|---------------|----------|--------|------------------------------------------------------------------|--|--|--|

| ld          | File          | Language | Kind   | Full Name                                                        |  |  |  |

| 0           | <u>fifo.v</u> | verilog  | design | /home/onespin/my_labs/fifo_quantify_demo_v2/no_checks/rtl/fifo.v |  |  |  |

## Quantify on FIFO Example—II Design View

| 43 | always @(posedge clk or negedge resetn)                                  |              |

|----|--------------------------------------------------------------------------|--------------|

| 44 | if (!resetn)                                                             | 0            |

| 45 | $w_ack \ll 1'b1;$                                                        | 0            |

| 46 | else if (!full)                                                          | 0            |

| 47 | w_ack <= 1'bl;                                                           | 0            |

| 48 | else if (full)                                                           | 0            |

| 49 | w_ack ⊲= 1'b0;                                                           | 0            |

| 50 |                                                                          |              |

| 51 | assign w_ack_o = w_ack;                                                  | 0            |

| 52 | <pre>assign r_ack_o = empty ? 1'b0 : (full ? 1'b0 : 1'b1);</pre>         | 0            |

| 53 | assign w_hsk = w_valid_i && w_ack_o;                                     | 0            |

| 54 | assign r_hsk = r_valid_i && r_ack_o;                                     | 0            |

| 55 | assign nxt_wptr = wptr + w_hsk;                                          | 0            |

| 56 | assign nxt_rptr = rptr + r_hsk;                                          | 0            |

| 57 | assign nxt_empty = (empty    r_hsk) && !w_hsk && (nxt_rptr == nxt_wptr); | 0            |

| 58 |                                                                          |              |

| 59 | // Registered calculations for empty, wptr and rptr                      |              |

| 60 | always @(posedge clk or negedge resetn)                                  |              |

| 61 | if (!resetn)                                                             | 0            |

| 62 | begin                                                                    |              |

| 63 | empty ⊲= l'bl;                                                           | 0            |

| 64 | wptr <= (DEPTH_BITS(1'b0));                                              | 0            |

| 65 | <pre>rptr == {DEPTH_BITS(1'b0)};</pre>                                   | 0            |

| 66 | end                                                                      |              |

| 67 | else                                                                     | - <b>0</b> / |

| 68 | begin                                                                    |              |

| 69 | empty ⊲= nxt_empty;                                                      | 0            |

| 70 | wptr ⊲= nxt_wptr;                                                        | 0            |

| 71 | rptr <= nxt_rptr;                                                        | 0            |

| 72 | end                                                                      |              |

| 73 | // Write the data on a w_hsk                                             |              |

| 74 | always @(posedge clk)                                                    |              |

| 75 | if (w_hsk)                                                               | 0            |

| 76 | data[wptr]                                                               | 0            |

| 77 | //···· Read the data on a r_hsk                                          |              |

| 78 | always @(posedge clk)                                                    |              |

| 79 | if (r_hsk)                                                               | 0            |

| 80 | data_int <= data[rptr];                                                  | 0            |

| 81 | assign full = !empty && (rptr == wptr);                                  | 0            |

| 82 | assign empty_o = empty;                                                  | 0            |

| 83 | mssign full_o = full;                                                    | 0            |

| 84 | assign data_o = data_int;                                                | 0            |

| 85 | endmodule                                                                |              |

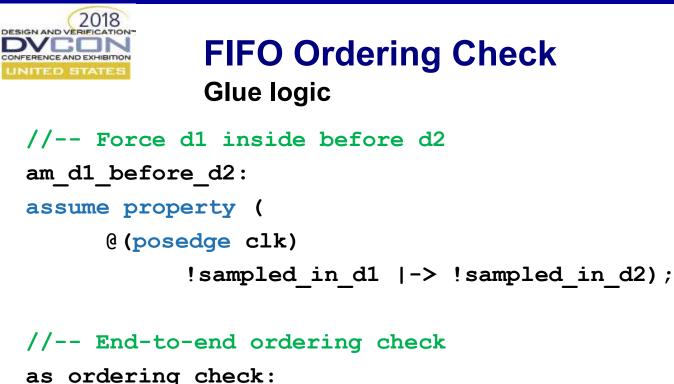

## **FIFO Verification Strategy** Uses symbolic and data abstraction

- Use two symbolic transactions for tracking all possible data values

- Send these symbolic values in a pre-determined order in the FIFO

- Ensure that they come out of the FIFO in the same order

- Use four sampling registers

- sampled\_in\_d1

- sampled\_in\_d2

- sampled\_out\_d1

- sampled\_out\_d2

- One side constraint

- One main ordering check

```

as_ordering_check:

assert property (

@(posedge clk) disable iff (!resetn)

sampled_in_d1 && sampled_in_d2 && !sampled_out_d1

|-> !sampled_out_d2);

```

# Quantify on FIFO Example—III With just ordering check

|                                          | ural Coverage Overview                                                                                               |                                 |                          |   |                  |                      |   |                           |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------|---|------------------|----------------------|---|---------------------------|

| Status                                   |                                                                                                                      | Statemen                        | ts                       |   | Branches         |                      |   |                           |

| 1                                        | covered                                                                                                              | 14                              | 63.64%                   |   | 63.64% de        | sign cov <u>ered</u> |   |                           |

| R                                        | reached                                                                                                              | 0                               | 0.00%                    |   | 0 0              | 0.00%                |   |                           |

| U                                        | unknown                                                                                                              | 0                               | 0.00%                    |   | 0 0              | 0.00%                |   |                           |

| 0R                                       | unobserved                                                                                                           | 7                               | 31.82%                   | 4 | 2                | 28.57%               |   | 31.82% Design Unobserved  |

| 0                                        | uncovered                                                                                                            | 1                               | 4.55%                    |   | 4.55% Desi       | gn Uncovered         |   | J1.02/0 Design Onobserved |

| 0C                                       | constrained                                                                                                          | 0                               | 0.00%                    |   | 0 0              | 0.00%                |   |                           |

| 0D                                       | dead                                                                                                                 | 0                               | 0.00%                    |   | 0                | 0.00%                |   |                           |

| Sum                                      | quantify targets                                                                                                     | 22                              |                          |   | 7                |                      |   |                           |

| Exclud                                   | ded Code Overview                                                                                                    |                                 |                          |   |                  |                      |   | 1                         |

|                                          |                                                                                                                      | Statemen                        | ts                       |   | Branches         |                      |   |                           |

| Code S                                   |                                                                                                                      | Statemen<br>0                   |                          |   |                  | 0.00%                |   |                           |

| Code S<br>Xu                             | tatus                                                                                                                | 100000000000000                 |                          | - | 0                | 0.00%                | - |                           |

| Code S<br>Xu<br>Xr                       | tatus<br>excluded by user                                                                                            | 0                               | 0.00%                    | - | 0                |                      |   |                           |

| Code S<br>Xu<br>Xr                       | tatus<br>excluded by user<br>excluded redundant code                                                                 | 0<br>0                          | 0.00%<br>0.00%           | _ | 0                | 0.00%                |   |                           |

| Code S<br>Xu<br>Xr<br>Xv                 | tatus<br>excluded by user<br>excluded redundant code<br>excluded verification code                                   | 0<br>0<br>14                    | 0.00%<br>0.00%<br>38.89% |   | 0<br>0<br>4      | 0.00%<br>36.36%      |   |                           |

| Code S<br>Xu<br>Xr<br>Xv<br>0/1/U        | tatus<br>excluded by user<br>excluded redundant code<br>excluded verification code<br>quantify targets               | 0<br>0<br>14<br>22              | 0.00%<br>0.00%<br>38.89% |   | 0<br>0<br>4<br>7 | 0.00%<br>36.36%      |   |                           |

| Code S<br>Xu<br>Xr<br>Xv<br>0/1/U<br>Sum | tatus<br>excluded by user<br>excluded redundant code<br>excluded verification code<br>quantify targets               | 0<br>0<br>14<br>22              | 0.00%<br>0.00%<br>38.89% |   | 0<br>0<br>4<br>7 | 0.00%<br>36.36%      |   |                           |

| Code S<br>Xu<br>Xr<br>Xv<br>0/1/U<br>Sum | tatus<br>excluded by user<br>excluded redundant code<br>excluded verification code<br>quantify targets<br>total code | 0<br>0<br>14<br>22<br><b>36</b> | 0.00%<br>0.00%<br>38.89% |   | 0<br>0<br>4<br>7 | 0.00%<br>36.36%      |   |                           |

| fifo s | <u>sva.sv</u> 14              |        |                   | 4            |              |              |            |              |

|--------|-------------------------------|--------|-------------------|--------------|--------------|--------------|------------|--------------|

| Ass    | ertion Coverage               |        |                   |              |              |              |            |              |

| ld     | Property                      | Kind   | Proof Result      | Proof Radius | Cover Result | Cover Radius | Quantified |              |

| 0      | sva/u fifo /as ordering check | assert | FORMAL_PROOF      | infinite     | COVER_PASS   | 2            | yes        | Single Check |

| 1      | sva/u fifo /am d1 before d2   | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        | <b>J</b>     |

| 2      | sva/u fifo /am intf full      | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |              |

| 3      | sva/u fifo /am stable d1      | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |              |

| 4      | sva/u fifo /am stable d2      | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |              |

| File Status |               |          |        |                                                                                       |  |  |  |

|-------------|---------------|----------|--------|---------------------------------------------------------------------------------------|--|--|--|

| ld          | File          | Language | Kind   | Full Name                                                                             |  |  |  |

| 0           | <u>fifo.v</u> | verilog  | design | /home/onespin/my_labs/fifo_quantify_demo_v2/Step2_ordering_check_only/rtl/fifo.v      |  |  |  |

| 1           | fifo sva.sv   | verilog  | design | /home/onespin/my_labs/fifo_quantify_demo_v2/Step2_ordering_check_only/sva/fifo_sva.sv |  |  |  |

#### **Quantify on FIFO Example—IV** What's still missing?

| 42         w_ack c = 1'bj         0R           43         else if (full)         0R           44         w_ack c = 1'bj         0R           45         else if (full)         0R           46         w_ack c = 1'bj         0R           47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 41   | if (!resetn)                                                             | 0R |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------|----|

| 44     w_ack (* a'bi;     0R       45     else if (vil)     0       46     w_ack (* a'bi;     0       47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 42   | w_ack <= 1'b1;                                                           | 0R |

| 46         else if (foll)         0           46         w_ack < 1'bo;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 43   | else if (!full)                                                          | 0R |

| 46       w_akk (> 1'b3;       0         47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 44   | w_ack <= 1'b1;                                                           | 0R |

| assign w_ack_po = w_ack;         OR           48         assign w_ack_po = wepty ? 1'bo: 1'b1;         0           50         assign m_ack_po = wepty ? 1'bo: 1'b1;         1           51         assign m_hkk = w_alid1 & & w_ack_p;         0R           52         assign m_hkk = w_alid1 & & w_ack_p;         0R           53         assign m_hk = w_alid1 & & w_ack_p;         1           54         assign nxt_mptr = wptr + w_bk;         1           55         assign nxt_mptr = rptr + n hk;         1           56         sign nxt_mptr = wptr + w_bk;         1           56         if (freestr)         1           57         always @(posedge clk or negodge resetn)         1           58         if (freestr)         1           59         begin         1           50         emptr < (DEFH_BITS(1'b0));                                                                                   | 45   | else if (full)                                                           | 0  |

| 48     assign w_ack_o = w_ack;     OR       49     //assign r_ack_o = eepty 7 1 bb : 1 bb ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 46   | w_ack <= 1'b0;                                                           | 0  |

| 49       //ssign r_sk_o = empty % 1'b0: 1'b1;       1         50       assign r_sk_o = empty % 1'b0: 1'b1;       1         51       assign r_sk_s = r_valid_i && r_ack_o;       0R         52       assign r_sk_s = r_valid_i && r_ack_o;       1         53       assign nxt_ptr = sptr + r_bk;       1         54       assign nxt_ptr = rptr + r_bk;       1         55       assign nxt_co = cempty, wptr and rptr       1         56       if (lresetm)       1         57       abusys &@(posdeg clk or negedge resetn)       1         58       if (lresetm)       1         59       begin       1         60       eepty c '10;       0R         61       wptr c (DEPH_dITS(1'b0));       1         62       rptr c (DEPH_dITS(1'b0));       1         63       end       1         64       else       1         65       segin       1         66       eepty (rit_back_back_back_back_back_back_back_back | 47   |                                                                          |    |

| 50     assign n_ack_o = empty 7 1'b0 : (full 7 1'b0 : 1'b1);     1       51     assign n_bk = n_walid_i && m_ack_o;     0R       52     assign n_bk = n_walid_i && m_ack_o;     1       53     assign n_bt = mytr + w_bk;     1       54     assign n_t_ptr = mytr + w_bk;     1       55     assign n_t_ptr = nytr + w_bk;     1       56     assign n_t_ptr = mytr + w_bk;     1       57     assign n_t_ptr = coptr + n_bk;     1       58     if (lresetn)     1       59     bgin     1       60     empty << 1'bi;                                                                                                                                                                                                                                                                                                                                                                                              | 48   | assign w_ack_o = w_ack;                                                  | 0R |

| 51     assign w_hsk = w_walid_i && w_ack_o;     0R       62     assign n,hk = r_walid_i && r_ack_o;     1       63     assign n,hk = r_walid_i && r_ack_o;     1       64     assign n,t wptr = wptr + w_hsk;     1       65     assign n,t_eptr = nptr + n_hsk;     1       66     assign n,t_eptr = nptr + n_hsk;     1       67     always @(posedge clk or negedge resetn)     1       68     if (lresetn)     1       69     begin     0R       60     empty <= 1'bi;                                                                                                                                                                                                                                                                                                                                                                                                                                            | 49   | //assign r_ack_o = empty ? 1'b0: 1'b1;                                   |    |

| 52       assign n.hsk = r_valid_i && r_ack_0;       1         53       assign nxt_wptr = uptr + w_hsk;       1         54       assign nxt_wptr = uptr + w_hsk;       1         55       assign nxt_wptr = uptr + w_hsk;       1         56       if (ruset)       1         57       always @(posedge clk on egedge resetn)       1         58       if (resetn)       1         59       begin       0R         60       empty <= 1/bi;                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 50   | assign r_ack_o = empty ? 1'b0 : (full ? 1'b0 : 1'b1);                    | 1  |

| 33       assign nxt_mptr = wptr + w_hsk;       1         64       assign nxt_mptr = cempty    r_hsk) && ks (nxt_mptr == nxt_mptr);       1         55       assign nxt_mptr = cempty    r_hsk) && ks (nxt_mptr == nxt_mptr);       1         56       // Registered calculations for empty, wptr and mptr       1         57       always @(posedge clk or negedge resetn)       1         58       if (iresetn)       1         59       begin       0         60       empty <= 1'bi;                                                                                                                                                                                                                                                                                                                                                                                                                               | 51   | assign w_hsk = w_valid_i && w_ack_o;                                     | 0R |

| 54       assign nxt_rptr = rptr + n hsk;       1         65       assign nxt_rempty = (empty    r_nsk) && lnyk && (nxt_rptr == nxt_wptr);       1         66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 52   | assign r_hsk = r_valid_i && r_ack_o;                                     | 1  |

| 55       assign nxt_empty = (empty    r_hsk) && lw_hsk && (nxt_rptr *= nxt_wptr);       1         56       // Registered calculations for empty, wptr and rptr       1         57       always @(posedge clk or negedge resetn)       1         58       if (tresetn)       1         59       begin       0R         60       empty << 1'bi;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 53   | assign nxt_wptr = wptr + w_hsk;                                          | 4  |

| 58       // Registered calculations for empty, wptr and rptr         57       always @(posedge clk or negedge resetn)         58       if (iresetn)       1         59       begin       0R         60       empty <= 1'bl;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 54   | assign nxt_rptr = rptr + r_hsk;                                          | 1  |

| 57       always @(posedge clk or negedge resetn)       1         58       if (Iresetn)       1         59       begin       0         60       empty <= 1'bi;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 55   | assign nxt_empty = (empty    r_hsk) && lw_hsk && (nxt_rptr == nxt_wptr); | 1  |

| 58       if (!resetn)       1         59       begin       0         60       empty <= 1'bi;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 56   | // Registered calculations for empty, wptr and rptr                      |    |

| 59         begin         00           60         empty <= 1'b1;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 57   | always @(posedge clk or negedge resetn)                                  |    |

| constraint         OR           empty <= 1'b1;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 58   | if (Iresetn)                                                             | 1  |

| 61         wptr <= (DEPTH_BITS(1'b0));                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59   | begin                                                                    |    |

| 62         rptr << (DEPTH_BITS(1'b0));                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 60   | empty <= 1'b1;                                                           | 0R |

| 63     end     1       64     else     1       65     begin     1       66     empty <= nxt_empty;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 61   | wptr <= {DEPTH_BITS(1'b0}};                                              | 1  |

| 64     else     1       65     begin     7       66     empty <= nxt_empty;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 62   | rptr <= {DEPTH_BITS(1'b0}};                                              | 1  |

| 66         begin         0           66         empty <= nxt_empty;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 63   | end                                                                      |    |

| 66         empty <= nxt_empty;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 64   | else                                                                     | 1  |

| 67         wptr <= nxt_mptr;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 65   | begin                                                                    |    |

| 68         rptr <= mxt_ptr;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 66   | <pre>empty &lt;= nxt_empty;</pre>                                        | 1  |

| 69         end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 67   | wptr <= nxt_wptr;                                                        | 1  |

| 70       // write the data on a w_hsk       1         71       always @(posedge clk)       1         72       if (w_hsk)       1         73       data[wptr] << data_i;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 68   | <pre>rptr &lt;= nxt_rptr;</pre>                                          | 1  |

| 71       always @(posedge clk)       1         72       if (w_hsk)       1         73       data[wptr] < data_i;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 69   |                                                                          |    |

| 172         if (w_hsk)         1           73         data[wptr] << data i;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 70   |                                                                          |    |

| 73       data[wptr] <= data_i;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |                                                                          |    |

| 74     // Read the data on a r_isk       75     always @(posedge clk)       76     if (r_isk)       77     data_int <= data[rtr];                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |                                                                          | 1  |

| 75       always @(posedge clk)         76       if (n_hsk)       1         77       data_int <= data[rptr];                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |                                                                          | 1  |

| if (r_hsk)         1           77         data_int <= data[rptr];                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 74   |                                                                          |    |

| 77     data_it <= data[rptr];                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |                                                                          |    |

| 78         assign full = lempty && (rptr == wptr);         1           79         assign empty_o = empty;         OR           80         assign full_o = full;         OR           81         assign data_o = data_int;         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | if (r_hsk)                                                               |    |

| 79         assign empty_o = empty;         OR           80         assign full_o = full;         OR           81         assign data_o = data_int;         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |                                                                          |    |

| 80         assign full_o = full;         OR           81         assign data_o = data_int;         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1000 |                                                                          |    |

| 81 assign data_o = data_int; 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.10 |                                                                          |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 80   | assign full_o = full;                                                    | 0R |

| 82 endmodule                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | assign data_o = data_int;                                                | 1  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 82   | endmodule                                                                |    |

#### **Missing coverage**

- Unobserved

- Uncovered

**Quantify on FIFO Example—V** Let's add checks on empty and full

as\_empty\_to\_full: assert property (@(posedge clk) disable iff (!resetn) empty\_o ##1 (push\_i && !pop\_i)[\*FIFO\_DEPTH] |=> full\_o);

as\_full\_to\_empty: assert property (@(posedge clk) disable iff (!resetn) full\_o ##1 (pop\_i && !push\_i)[\*FIFO\_DEPTH] |=> empty\_o);

as empty after reset:

assert property (@(posedge clk) !resetn |=> empty);

#### Quantify on FIFO Example—VI How did we do now?

| Struc  | Internal Coverage Overview |           |        |        |                   |  |  |

|--------|----------------------------|-----------|--------|--------|-------------------|--|--|

| Status |                            | Statement | ts     | Branch | es                |  |  |

| 1      | covered                    | 16        | 72.73% | 72.7   | 3% design covered |  |  |

| R      | reached                    | 0         | 0.00%  | 0      | 0.00%             |  |  |

| U      | unknown                    | 0         | 0.00%  | 0      | 0.00%             |  |  |

| 0R     | unobserved                 | 6         | 27.27% | 3      | 42.86%            |  |  |

| 0      | uncovered                  | 0         | 0.00%  | 0      | 0.00%             |  |  |

| 0C     | constrained                | 0         | 0.00%  | 0      | 0.00%             |  |  |

| 0D     | dead                       | 0         | 0.00%  | 0      | 0.00%             |  |  |

| Sum    | quantify targets           | 22        |        | 7      |                   |  |  |

| Exclu  | Excluded Code Overview     |           |        |          |        |  |  |  |

|--------|----------------------------|-----------|--------|----------|--------|--|--|--|

| Code S | itatus                     | Statement | ts     | Branches |        |  |  |  |

| Xu     | excluded by user           | 0         | 0.00%  | 0        | 0.00%  |  |  |  |

| Xr     | excluded redundant code    | 0         | 0.00%  | 0        | 0.00%  |  |  |  |

| Xv     | excluded verification code | 14        | 38.89% | 4        | 36.36% |  |  |  |

| 0/1/U  | quantify targets           | 22        | 61.11% | 7        | 63.64% |  |  |  |

| Sum    | total code                 | 36        |        | 11       |        |  |  |  |

| Structural Coverage by File |            |          |  |  |  |  |

|-----------------------------|------------|----------|--|--|--|--|

| File                        | Statements | Branches |  |  |  |  |

| fifo.v                      | 22         | 7        |  |  |  |  |

| fifo sva.sv                 | 14         | 4        |  |  |  |  |

| Assertion Coverage |                                  |        |                   |              |               |              |            |  |

|--------------------|----------------------------------|--------|-------------------|--------------|---------------|--------------|------------|--|

| ld                 | Property                         | Kind   | Proof Result      | Proof Radius | Cover Result  | Cover Radius | Quantified |  |

| 0                  | sva/u fifo /as empty after reset | assert | FORMAL_PROOF      | infinite     | COVER_PASS    | 1            | yes        |  |

| 1                  | sva/u fifo /as empty to full     | assert | FORMAL_PROOF      | infinite     | COVER_PASS    | 1            | yes        |  |

| 2                  | sva/u fifo /as full to empty     | assert | FORMAL_VACUOUS    | infinite     | COVER_VACUOUS | infinite     | no         |  |

| 3                  | sva/u fifo /as ordering check    | assert | FORMAL_PROOF      | infinite     | COVER_PASS    | 2            | yes        |  |

| 4                  | sva/u fifo /am d1 before d2      | assume | FORMAL_ASSUMPTION | infinite     | N/A           | 0            | N/A        |  |

| 5                  | sva/u fifo /am intf full         | assume | FORMAL_ASSUMPTION | infinite     | N/A           | 0            | N/A        |  |

| 6                  | sva/u fifo /am stable d1         | assume | FORMAL_ASSUMPTION | infinite     | N/A           | 0            | N/A        |  |

| 7                  | sva/u fifo /am stable d2         | assume | FORMAL_ASSUMPTION | infinite     | N/A           | 0            | N/A        |  |

| File | File Status |          |        |                                                                                          |  |  |  |

|------|-------------|----------|--------|------------------------------------------------------------------------------------------|--|--|--|

| ld   | File        | Language | Kind   | Full Name                                                                                |  |  |  |

| 0    | fifo.v      | verilog  | design | /home/onespin/my_labs/fifo_quantify_demo_v2/Step3_with_empty_full_checks/rtl/fifo.v      |  |  |  |

| 1    | fifo sva.sv | verilog  | design | /home/onespin/my_labs/fifo_quantify_demo_v2/Step3_with_empty_full_checks/sva/fifo_sva.sv |  |  |  |

#### Vacuous Failure

#### Problem with debugging unreachables

#### **Quantify on FIFO Example—VII** Where are the missing coverage targets?

| 42 | if (!resetn)                                                             | 0R |

|----|--------------------------------------------------------------------------|----|

| 43 | w_ack <= 1'b1;                                                           | 0R |

| 44 | else if (!full)                                                          | 0R |

| 45 | w_ack <= 1'b1;                                                           | 0R |

| 46 | else if (full)                                                           | 0R |

| 47 | w_ack <= 1'b0;                                                           | 0R |

| 48 |                                                                          |    |

| 49 | assign w_ack_o = w_ack;                                                  | 0R |

| 50 | assign r_ack_o = empty ? 1'b0 : (full ? 1'b0 : 1'b1);                    | 1  |

| 51 | assign w_hsk = w_valid_i && w_ack_o;                                     | 0R |

| 52 | assign r_hsk = r_valid_i && r_ack_o;                                     | 1  |

| 53 | assign nxt_wptr = wptr + w_hsk;                                          | 1  |

| 54 | assign nxt_rptr = rptr + r_hsk;                                          | 1  |

| 55 | assign nxt_empty = (empty    r_hsk) && !w_hsk && (nxt_rptr == nxt_wptr); | 1  |

| 56 | // Registered calculations for empty, wptr and rptr                      |    |

| 57 | always @(posedge clk or negedge resetn)                                  |    |

| 58 | if (Iresetn)                                                             | 1  |

| 59 | begin                                                                    |    |

| 60 | empty <= 1'bl;                                                           | 1  |

| 61 | <pre>wptr &lt;= {DEPTH_BITS{1'b0}};</pre>                                | 1  |

| 62 | <pre>rptr &lt;= {DEPTH_BITS{1'b0}};</pre>                                | 1  |

| 63 | end                                                                      |    |

| 64 | else                                                                     | 1  |

| 65 | begin                                                                    |    |

| 66 | <pre>empty &lt;= nxt_empty;</pre>                                        | 1  |

| 67 | <pre>wptr &lt;= nxt_wptr;</pre>                                          | 1  |

| 68 | <pre>rptr &lt;= nxt_rptr;</pre>                                          | 1. |

| 69 | end                                                                      |    |

| 70 |                                                                          |    |

| 71 | // Write the data on a w_hsk                                             |    |

| 72 | always @(posedge clk)                                                    |    |

| 73 | if (w_hsk)                                                               | 1  |

| 74 | data[wptr] <= data_i;                                                    | 1  |

| 75 |                                                                          |    |

| 76 | // Read the data on a r_hsk                                              |    |

| 77 | always @(posedge clk)                                                    |    |

| 78 | if (r_hsk)                                                               | 1  |

| 79 | data_int <= data[nptn];                                                  | 1  |

| 80 |                                                                          |    |

| 81 | assign full = lempty && (rptr == wptr);                                  | 1  |

| 82 | assign empty_o = empty;                                                  | 0R |

| 83 | assign full_o = full;                                                    | 1  |

| 84 | assign data_o = data_int;                                                | 1  |

| 85 | endmodule                                                                |    |

| -  |                                                                          |    |

#### **Missing coverage**

- Unobserved code

- Cannot observe empty!

#### Quantify on FIFO Example—VIII A closer look

| 42 | if (!resetn)                                         | 0  |

|----|------------------------------------------------------|----|

| 43 | w_ack <= 1'b1;                                       | 0  |

| 44 | else if (!full)                                      | 0R |

| 45 | w_ack <= 1'b1;                                       | 0R |

| 46 | else if (full)                                       | 0R |

| 47 | w_ack <= 1'b0;                                       | 0R |

| 48 |                                                      |    |

| 49 | assign w_ack_o = w_ack;                              | 0R |

| 50 | assign r_ack_o = empty ? 1'b(: (full ? 1'b0 : 1'b1); | 1  |

| 51 | assign w_hsk = w_valid_i && w_ack_o;                 | 0R |

This looks buggy ... Let's go and fix it!

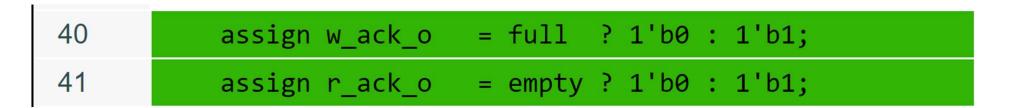

#### **Quantify on FIFO Example—IX** After the bug fix on r\_ack\_o design

| Status |                  | Statement | ts     | Branch | es                 |

|--------|------------------|-----------|--------|--------|--------------------|

| 1      | covered          | 17        | 77.27% | 77.    | 27% design covered |

| R      | reached          | 0         | 0.00%  | 0      | 0.00%              |

| U      | unknown          | 0         | 0.00%  | 0      | 0.00%              |

| 0R     | unobserved       | 5         | 22.73% | 3      | 42.86%             |

| 0      | uncovered        | 0         | 0.00%  | 0      | 0.00%              |

| 0C     | constrained      | 0         | 0.00%  | 0      | 0.00%              |

| 0D     | dead             | 0         | 0.00%  | 0      | 0.00%              |

| Sum    | quantify targets | 22        |        | 7      |                    |

| Exclu       | Excluded Code Overview     |            |        |          |        |  |  |  |

|-------------|----------------------------|------------|--------|----------|--------|--|--|--|

| Code Status |                            | Statements |        | Branches | 5      |  |  |  |

| Xu          | excluded by user           | 0          | 0.00%  | 0        | 0.00%  |  |  |  |

| Xr          | excluded redundant code    | 0          | 0.00%  | 0        | 0.00%  |  |  |  |

| Xv          | excluded verification code | 14         | 38.89% | 4        | 36.36% |  |  |  |

| 0/1/U       | quantify targets           | 22         | 61.11% | 7        | 63.64% |  |  |  |

| Sum         | total code                 | 36         |        | 11       |        |  |  |  |

| Structural Cove | erage by File |          |  |  |

|-----------------|---------------|----------|--|--|

| File            | Statements    | Branches |  |  |

| <u>fifo.v</u>   | 22            | 7        |  |  |

| FF              | 44            |          |  |  |

| Ass | ssertion Coverage                |        |                   |              |              |              |            |  |

|-----|----------------------------------|--------|-------------------|--------------|--------------|--------------|------------|--|

| ld  | Property                         | Kind   | Proof Result      | Proof Radius | Cover Result | Cover Radius | Quantified |  |

| 0   | sva/u fifo /as empty after reset | assert | FORMAL_PROOF      | infinite     | COVER_PASS   | 1            | yes        |  |

| 1   | sva/u fifo /as empty to full     | assert | FORMAL_PROOF      | infinite     | COVER_PASS   | 1            | yes        |  |

| 2   | sva/u fifo /as full to empty     | assert | FORMAL_PROOF      | infinite     | COVER_PASS   | 5            | yes        |  |

| 3   | sva/u fifo /as ordering check    | assert | FORMAL_PROOF      | infinite     | COVER_PASS   | 2            | yes        |  |

| 4   | sva/u fifo /am d1 before d2      | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |  |

| 5   | sva/u fifo /am intf full         | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |  |

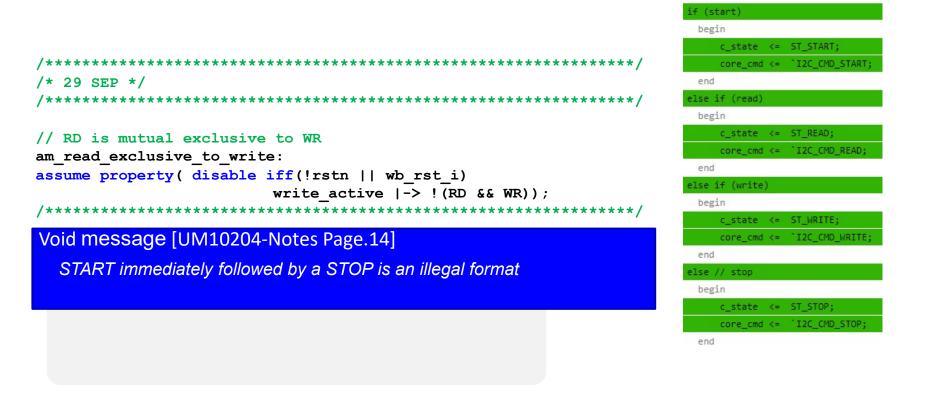

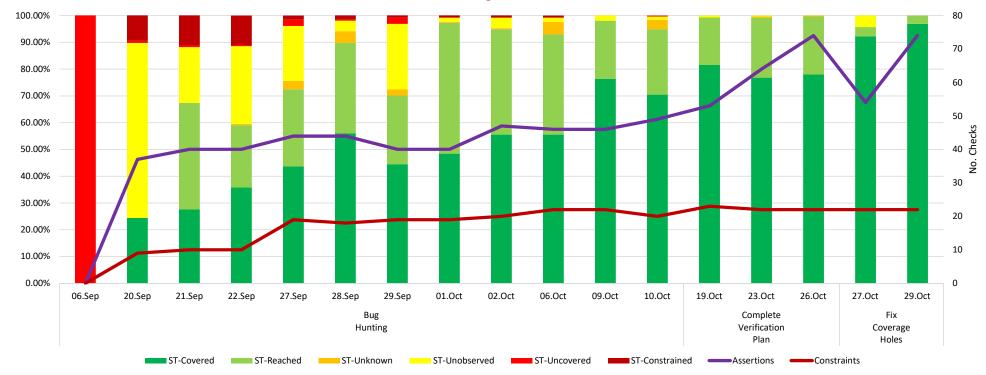

| 6   | sva/u fifo /am stable d1         | assume | FORMAL_ASSUMPTION | infinite     | N/A          | 0            | N/A        |  |