#### Using Formal Verification to Exhaustively Verify **SoC Assemblies**

by

Mark Handover **Applications Engineer** Mentor Graphics Corp. Kenny Ranerup **ASIC Consultant** ST-Ericsson

#### **Agenda**

- Introduction

- SoC Assembly Verification

- ST-Ericsson's SoC Assembly Verification Approach

- Types of Checking

- Connectivity Specifications

- Keys to success

- Results & Conclusions

#### Introduction

- We will discuss a project at ST-Ericsson for which Formal verification was successfully deployed in the task of SoC Assembly verification

- We will describe the methods used and the types of checking employed

- We will present results and conclusions including the elements that led to successful deployment

#### **SoC Assembly Verification**

- SoC assembly verification is the process of checking that blocks of logic are correctly connected

- Traditionally verified using Dynamic Approach

- Constructing a set of simulation stimuli to toggle source nodes and observe the behavior at the destination

- Challenges

- Likely requires directed approach not Constrained Random

- Requires huge number of tests and potentially many test environments

- Creating and managing test suites

- Observability & debug

## **SoC Assembly Verification**

- Static Approach

- Using Formal tools to exhaustively check all connectivity in the SoC

- Challenges

- Requires the creation of the property set

- Running Formal on SoC

- Benefits

- Simplified debug

- No requirement to create tests

- Time to Results

#### **ST-Ericsson Project**

- ST-Ericsson modem subsystem

- ~ 50 IP blocks, VHDL and Verilog implementation

- Several processors, bus interconnect, 400 memory instances

- Multi-Power domains, clock gating

- General Verification Approach

- Constrained Random and software driven verification

- Connectivity checking Verification

- Traditionally has used directed tests

- Bugs seen here have a large impact on other verification tasks

- Time consuming and considerable effort involved

### **ST-Ericsson Project**

- Looked to deploy formal for connectivity checking to improve throughput and results

- IP connectivity, Reset, Clocking and DFT checks

- Connectivity Specifications

- Many types

- Integration spreadsheet

- Port lists

- Memory lists

- Architecture specification

- Created and used for both SoC Construction/generating RTL and for verification

- Scripted for auto-generation of properties

#### **Types of Checks**

- Many types of connectivity checks can be performed

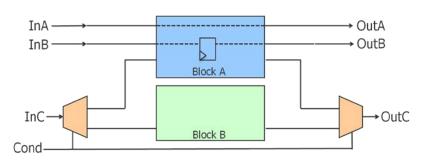

- IP Connectivity

- Unconditional Point to Point

- Point to Point With Delay

- Point to Point With Condition

- Resets

- Reset source correctly controls the correct block reset

- Correct reset values appear on outputs of blocks/subsystems

- DFT

- Memory BIST control & BIST status checking, Clocking, Resets

- Clocks

- Clock is successfully applied to destination when enabled

## Specifications and property generation

- Automation of the property set is a key requirement

- Specification has to facilitate automation

- Scripts written to create properties from specification

- Specification Example 1

```

{check}

CDR connection NO-N4,

Main PLL

{src}

$syscon main pll cdr entity

{srcports}

tst_pll_pf_n0,

tst pll pf n1,

tst_pll_pf_n2,

tst pll pf n3,

tst pll pf n4,

tst_pll_pf_enable

{dst}

$syscon main pll entity

{dstports}

NO, N1, N2, N3, N4, ENABLE

{tag}

main pll n ctrl

```

- Specification Example 2

- Allows for generating RTL and Verification of the connectivity

- Compact formal allows for greater readability

```

cpu.paddrdbq[11..2]

;db.paddr[11..2]

cpu.paddrdbq31

;db.paddr[31]

ac.prdata[31..0]

;pb0.ac_prd[31..0]

ac.psel_vec_a

ipb0.ac evec psel

cpu.rstreq

;_to_open

cpu.nopwrdwn

;_to_open

;_to_constant ;(OTHERS => '0')

cpu.addr[31..12]

cpu.addrv

;_to_constant ;'0'

```

- Property examples

- Port connectivity

```

assert_in1__blockb_port1:

assert property (

dut.in1 == dut.a.b.port1

);

```

```

DUT

Block A

Block B

➤ Port1

In1

Port2

In2

Select

{check} DUT, Block B

{src}

$DUT

in2

{srcports}

$BlockB

{dst}

Port2

{dstports}

{tag}

select

```

```

assign select = ((dut.c1 == 1) && (dut.c2 == 1));

assert_select_in2__b_port2:

assert property

select |-> dut.in2 == dut.a.b.port2

);

```

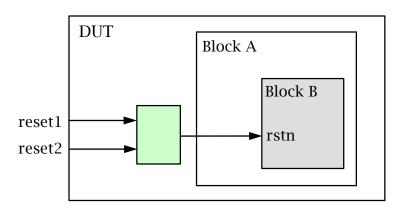

- Reset Connectivity

- Multiple reset sources to a block

```

assert_reset1_blocka_rst:

assert property (

dut.reset1 == 0 |->

!dut.a.b.c.blocka.rstn

);

assert_reset2_blocka_rst:

assert property (

dut.reset2 == 0 |->

!dut.a.b.c.blocka.rstn

);

```

Reset Value check

```

module reset_checker ( input ref_clk );

default clocking ref clock @(posedge ref clk);

endclocking

assume property (dut.core_rst_n == 0);

assume property (dut.dbg rst n == 0);

assert rst mem m0 awsize:

assert property ( dut.mem_m0 awsize == 0);

assert rst mem m0 awvalid:

assert property ( dut.mem m0 awvalid == 0);

endmodule

bind dut reset checker i reset checker (.*);

```

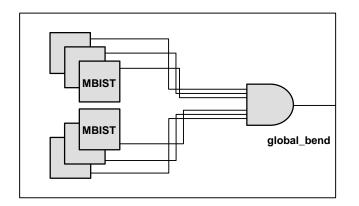

- Verifying a global logic function

- MBIST status signals are combined from all controllers to a global output port using AND or OR logic.

- This is very difficult to verify in simulation.

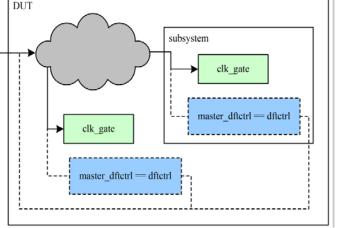

- Design Regularity

- Can take advantage of regularity to greatly simplify property generation

Use SystemVerilog bind statement to bind checker module to all instances thereby avoid listing all instance paths.

- bind clk\_gate checker i\_checker(.\*);

#### **Results and Conclusions**

- ST- Ericsson have successfully developed an approach and deployed connectivity checking using formal verification

- Exhaustive verification of SoC assemblies

- New design project

- 100+ bugs were found

- Simple connectivity to interface bugs

- Property set for project included

- 3500+ automatically generated properties

- 300+ semi automated properties

- 100+ manually created constraints

- Subsequent project, same structural design but with some new functionality, 40 bugs found

#### **Results and Conclusions**

- Keys to success

- Automation

- Its essential that the Connectivity specifications lend themselves to automation of properties

- SoC's will generate thousands of checks to be verified

- Design regularity and consistency

- Considerations for Formal

- Application doesn't require high level of Formal competence

- Properties are typically simple

- SoC's will contain blocks which are non-friendly to formal tools

- ST-Ericsson continue to use and develop formal based connectivity checking

Sponsored By:

# **THANK YOU**