#### Using Formal Applications to Create Pristine IPs

#### Lee Burns, Cypress Semiconductor David Crutchfield, Cypress Semiconductor Bob Metzler

Hithesh Velkooru, Cypress Semiconductor

- Why use Formal apps

- Starting point for introduction of Formal apps

- Implementation of Formal apps in the flow

- Connectivity Checks

- Coverage Closure

- Register Verification

- Code Quality

- Usage and results

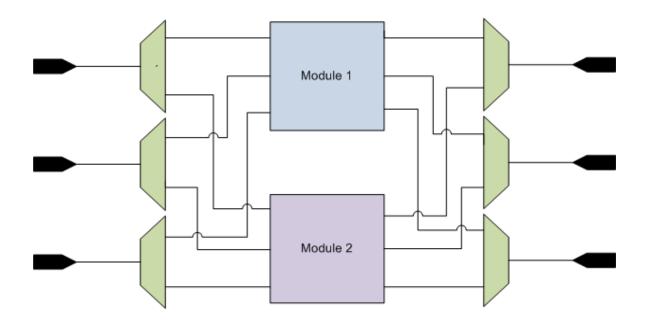

#### CONFERENCE AND EXHIBITION UNITED STATES Verification Pain Points -Conference and exhibition Connectivity

- Function routing through an IP

- Programmable interconnect

- Exhaustive verification is time consuming

- Chip level interconnect

- Fully verified IP

- Exhaustive verification of all connections is time consuming

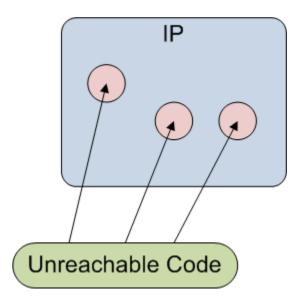

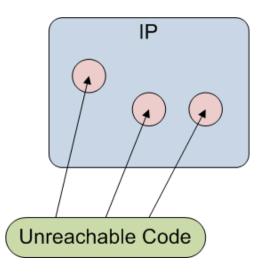

#### CONFERENCE AND EXHIBITION UNITED STATES Verification Pain Points -Coverage

- Goal is 100% code and functional coverage

- Mining for unreachable code is time consuming

- Iterative process

- Develop tests

- Review coverage

- Consult IP owner

- Create exclusions

- Develop more tests

- Repeated with code changes

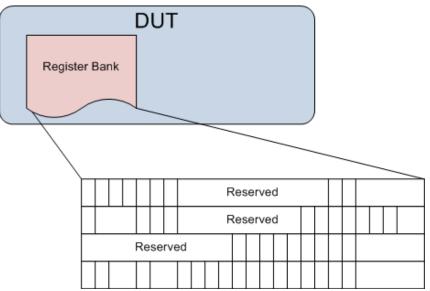

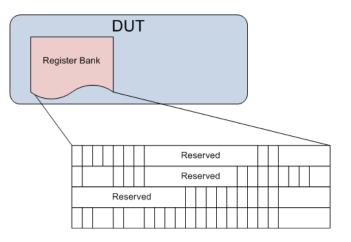

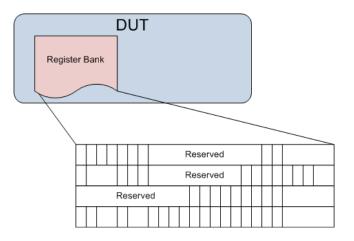

### Verification Pain Points -UNITED STATES Verification Pain Points

- Functional simulation using UVM\_REG is time consuming

- Read and understand spec

- Not all bits are used within a register (requires noncontiguous masking)

- Develop tests

- Debug results

- 4-6 weeks for 50K design

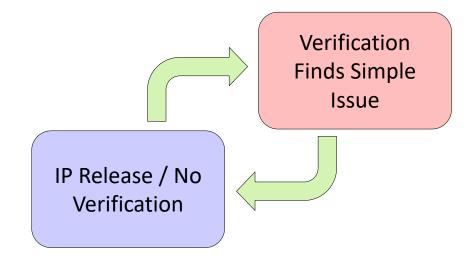

#### Verification Pain Points – CONFERENCE AND EXHIBITION UNITED STATES

- Design team does minimal testing

- No formal test bench / may not compile

- Verification finds simple issues

- Locked state machine

- Combinational loop

- Logic contention

- Cycles of code quality

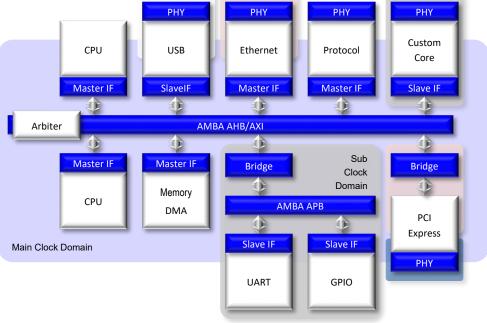

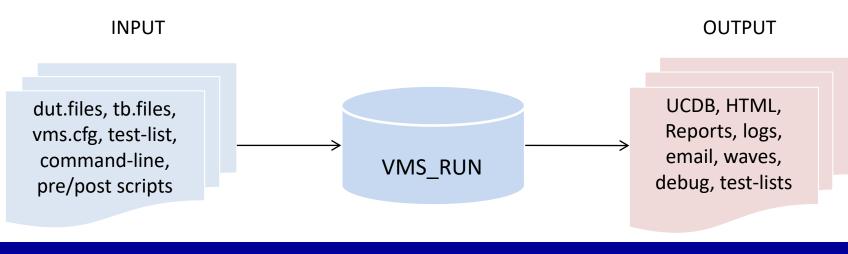

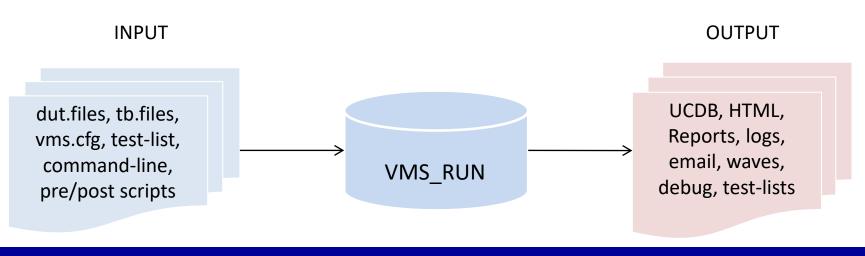

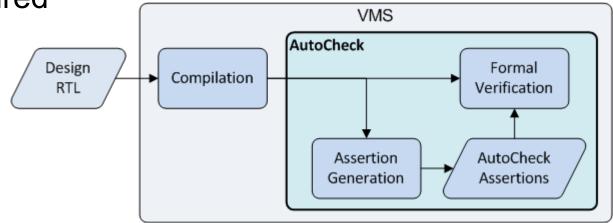

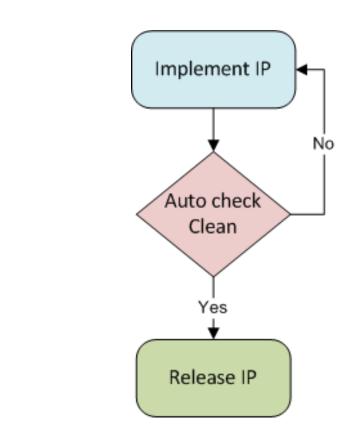

# **Existing Verification System**

- VMS Verification Management System

- Established a standard approach to:

- Design and test bench organization

- Specification of tools arguments

- Test list creation

- Regression status / coverage

- VMS manages compilation and simulation jobs through Mentor's Questa VRM (Verification Run Management)

- VMS needs to provide

- Additional steps for Formal applications

- Additional inputs to feed Formal applications

- Standard interface for Functional and Formal verification

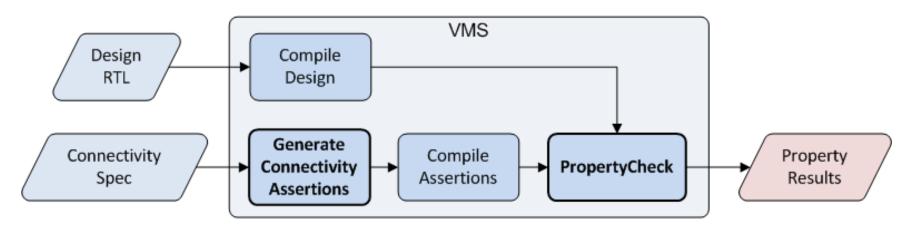

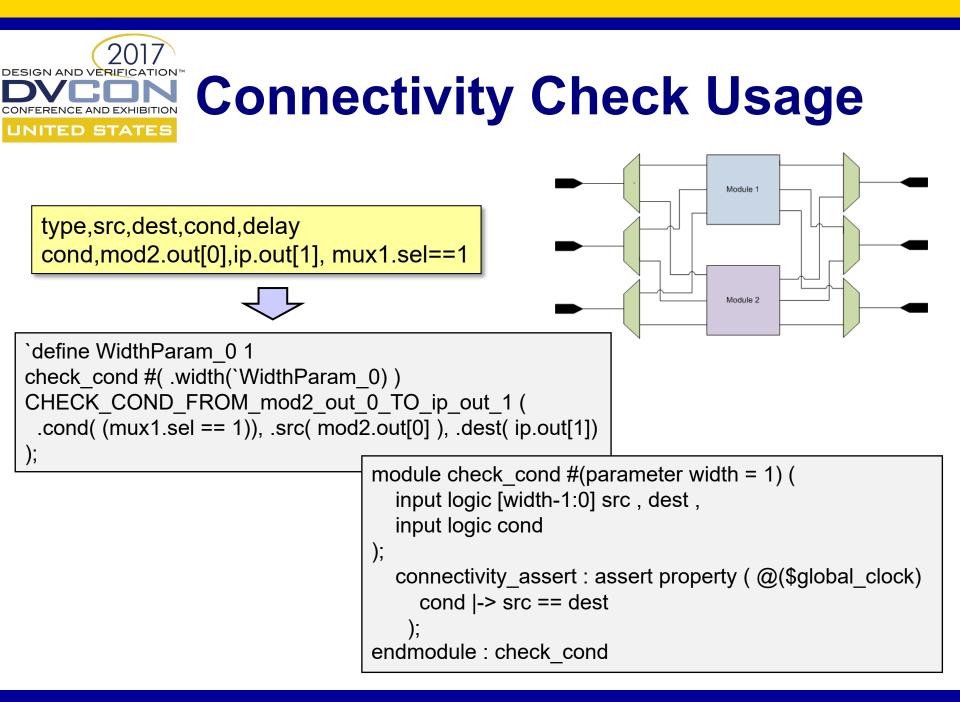

- Two new steps in VMS:

- Generate connectivity properties

- Verify properties with Formal tool (Questa PropertyCheck)

- New input to VMS: Connectivity spec (CSV)

- If all properties pass then connections are true

- No test bench required

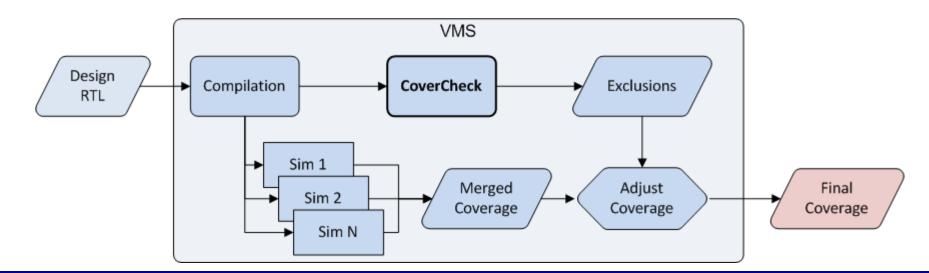

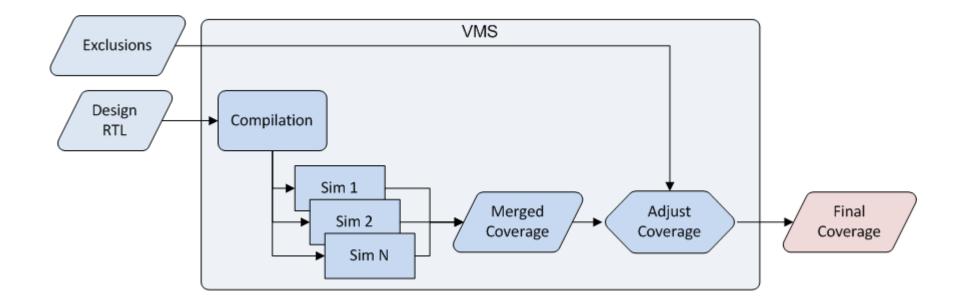

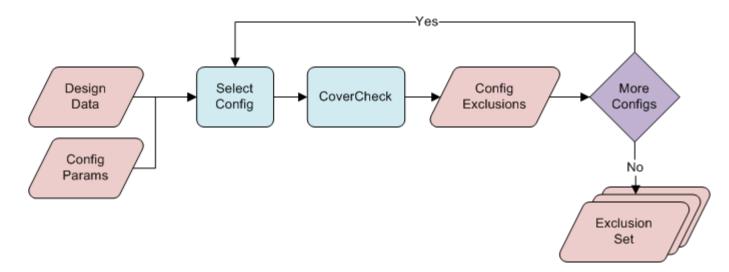

# **Coverage Closure (Flow 1)**

- One new step in VMS:

- Generate exclusions with Formal tool (Questa CoverCheck)

- Exhaustive search for unreachable code (time consuming)

- Simulation optional to just generate exclusions

- No test bench required / exclusions without test knowledge

- No new steps in VMS / Normal exclusion flow

- Exclusions generated in previous run

- Coverage adjusted after regression run

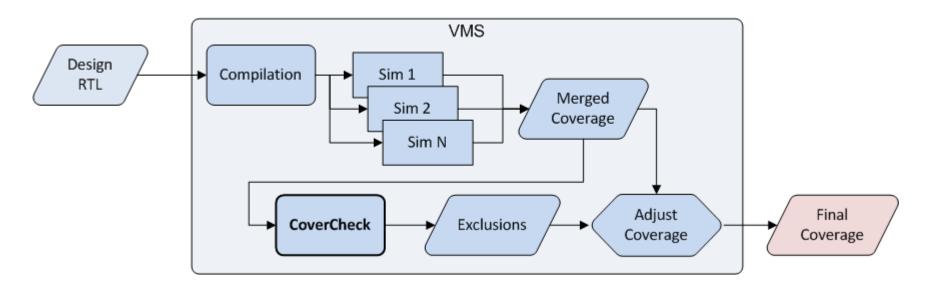

# **Coverage Closure (Flow 3)**

- One new step in VMS:

- Generate exclusions with Formal tool (Questa CoverCheck)

- Seed code coverage to minimize search for unreachable code (less time consuming)

- Test bench and tests required

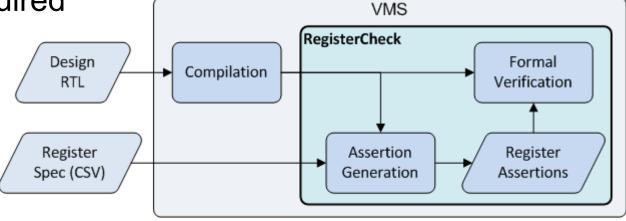

- One new step in VMS:

- Verify registers with Formal tool (Questa RegisterCheck)

- New input to VMS: Register spec (CSV)

- RegisterCheck:

- Generates assertions from CSV

- Formally proves assertions against design

- No test bench required

- One new step in VMS:

- Apply standard checks against design with Formal tool (Questa AutoCheck)

- AutoCheck:

- Generates assertions based on desired checks

- Formally proves assertions against design

- No test bench required

- Completed routing verification of PLD like IP in 1 week

- Savings > 4 person weeks (exhaustive simulation)

- Identified major bug (likely missed in functional simulation)

- Automated chip level connectivity verification through CSV generation from spec

| Block | Route<br>Inputs | Route<br>Outputs | Control<br>Register<br>Bits | # Lines in<br>CSV File | Formal<br>Runtime<br>(minutes) |

|-------|-----------------|------------------|-----------------------------|------------------------|--------------------------------|

| 1     | 408             | 308              | 962                         | 5266                   | 2                              |

| 2     | 408             | 308              | 962                         | 5266                   | 2                              |

| 3     | 312             | 256              | 786                         | 5127                   | 2                              |

| 4     | 312             | 256              | 786                         | 5127                   | 2                              |

### CONFERENCE AND EXHIBITION UNITED STATES Concerns / Lessons

- Knowing when to use Formal connectivity checks

- How to combine Formal results with simulation coverage

- Good specifications of connectivity are needed

- Strict code modularity / limit modules to specific behaviors

- Automation of connectivity CSV is key for savings

Results of example IP without tests provided

- Approximately 1 hour execution

- 17783 unreachable items found

- Branch 8489

- Condition 22

- Expression 1517

- FSM States 0

- FSM Transitions 0

- Statement 7577

- Toggle 178

- Coverbin 0

- Exclusions generated for each

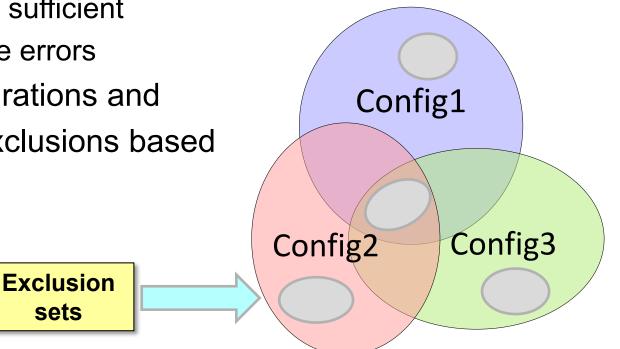

## **Coverage Closure Issue**

- Parameter passing to highly configurable IP

- Questa Formal can only process one configuration

- Coverage exclusions can change for each configuration

- Intersection is not sufficient

- Union could cause errors

- Iterate over configurations and selectively apply exclusions based on configuration

#### CONFERENCE AND EXHIBITION UNITED STATES CONFERENCE AND EXHIBITION CONFERE

- Questa CoverCheck analyze configuration parameters

- Select configuration

- Execute CoverCheck

- Repeat for more configurations

- Categorize exclusions based on configuration

### **Register Check Usage**

Register CSV and control file generated from internal specification

|                                                                                                                                   | amba_ahb<br>0x0000000<br>uvm        |                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------------------------------------------------------------------------------------------|

| -interface_port<br>-interface_port<br>-interface_port<br>-interface_port<br>-interface_port<br>-interface_port<br>-interface_port | hselx<br>hwrite<br>haddr<br>hresetn | <pre>= mmio_hready = mmio_hsel = mmio_hwrite = mmio_haddr = rst_hf_act_n = clk_sys</pre> |

Register Name,Register Description,Register Address,Register Width,Register Access,Register Reset Value,Register Reset Mask,Field Name,Field Description,Field Offset,Field Width,Field Access,Field Reset Value,Field Reset Mask,Field Is Covered,Field Is Reserved,.memmap\_write\_internal botsel\_I,"comment",0x00007808,32,RW,0x0,0xfffffff,clk\_sel0,"comment",0,2,RW,0x0,0xffffffff,,,, botsel\_I,"comment",0x00007808,32,RW,0x0,0xfffffff,clk\_sel1,"comment",2,2,RW,0x0,0xffffffff,,, botsel\_I,"comment",0x00007808,32,RW,0x0,0xffffffff,clk\_sel2,"comment",4,2,RW,0x0,0xffffffff,,, botsel\_I,"comment",0x00007808,32,RW,0x0,0xffffffff,clk\_sel2,"comment",4,2,RW,0x0,0xffffffff,,,, botsel\_I,"comment",0x00007808,32,RW,0x0,0xffffffff,clk\_sel3,"comment",6,2,RW,0x0,0xfffffffff,,,,

- PLD like IP (full configuration) functional simulation

- 2781 registers = 27,105 register fields

- Approximately 55,000 AHB accesses for full verification

- > 50 CPU Hours

- Evaluating RegisterCheck

- 10 register fields

- 32 CPU min for design compilation

- 76 CPU min for proving properties

- 7.6 min per / register field \* 27,105 fields = 143 CPU days!

- Black boxing could provide 20x improvement

- More work / profiling to make performance reasonable

- Unique register access not understood

- Address aliasing

- Address ganging

- Non-uniform register variable naming

- Makes automation of register specification difficult

- Approximately 30 min execution time

- Results of PLD like IP

- Block Unreachable

- Bus Multiply Driven

- Bus Undriven

- Bus Value Conflict

- Combo Loop

- Declaration unused

- Init X Unresolved

- Logic Unused

- Port Unused

1690

2

2

2

114

36

71

31

9067

- Formal applications

- Can be leveraged for automation

- Good first step into Formal techiniques

- Can get started without a test bench

- Connectivity and Code Quality Checks show the most promise

- Coverage and Register Checks need more investigation

and tool enhancements for flow integration