# Using an Enhanced Verification Methodology for Back-to-Back RTL/TLM Simulation

Frank Poppen and Ralph Görgen, OFFIS Institute for Information Technology

Kai Schulz, Andreas Mauderer and Jan-Hendrik Oetjens, Robert Bosch GmbH

Joachim Gerlach, Hochschule Albstadt-Sigmaringen

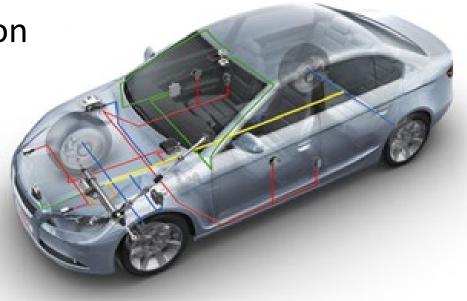

# The Challenge

- electronics in heterogeneous systems

- ambient and safety relevant

- increasing complexity

- design and verification

- lining up for the task

- tailored solutions

- standards

- languages

- tools

## No "One Size Fits All"

- verification engineers choose and combine what ...

- fits best for the company

- the design-team

- the application domain

- the abstraction level

- (budget, roadmap, ...)

- deep roots in the design process

- changes endanger productivity

- change carefully and incrementally

- Motivation

- What is the Integrated Functional Verification

Script Environment (IFS) and why use it?

- What was missing and what did we add to IFS?

- Making use of it for Back-to-Back comparison between RTL and TLM

- Conclusions

# IFS long before SystemC/-Verilog

- enhanced from VHDL with ...

- VHDL-AMS

- SystemC

- Matlab/Simulink

- SystemVerilog and UVM

- SystemC based library simulates with any simulator (IEEE 1666)

- tailored to relevant use scenarios in special contexts

- simple IFS command language for (self-checking) test cases

- digital designer

- analog designer

- verification engineer

- system engineer

- software engineer

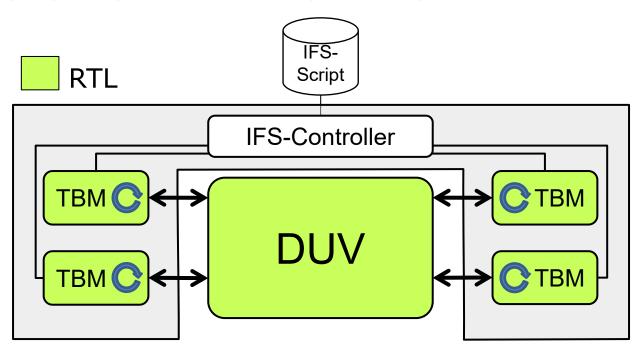

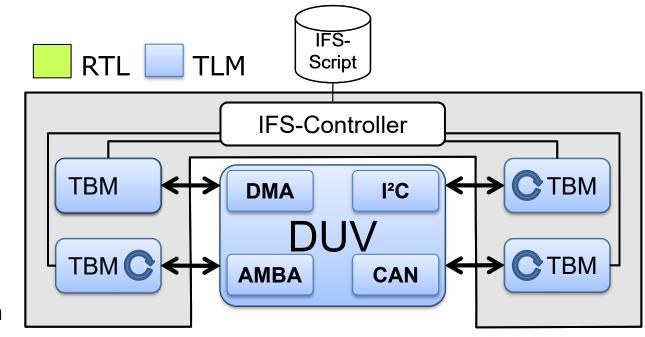

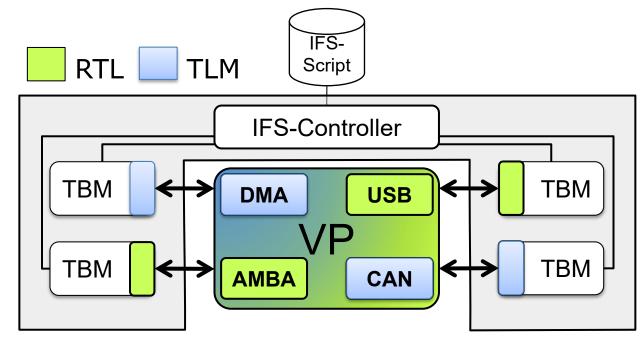

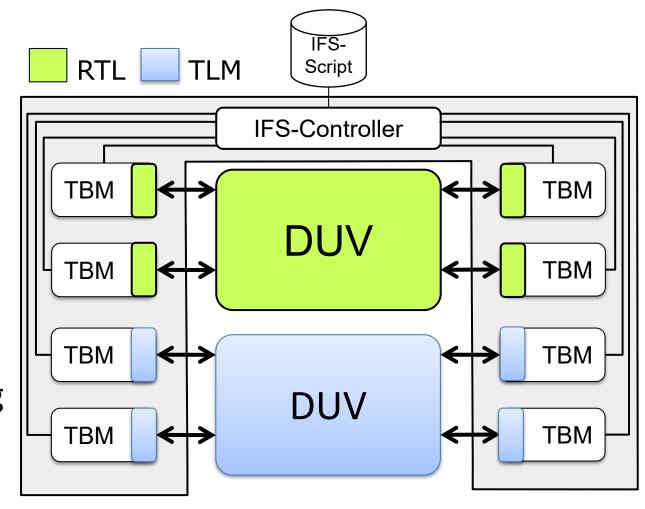

#### **IFS Simulation Environment**

- design under

verification

- testbenchmodules

- cmd loop

- predef. cmd

- user def. cmd

- IFS-controller

- IFS-script

```

TBM_1 PRINT "Executing Test" -- predef. module cmd

```

**#LOOP 100** -- predef. controller cmd -- predef. controller cmd

TBM\_1 write \$(100+#i) -- user def. module cmd

TBM\_2 read \$(100+#i) -- user def. module cmd

**#EOL** -- predef. controller cmd

**IFS QUIT** -- predef. controller cmd

- Motivation

- What is the Integrated Functional Verification

Script Environment (IFS) and why use it?

- What was missing and what did we add to IFS?

- Making use of it for Back-to-Back comparison between RTL and TLM

- Conclusions

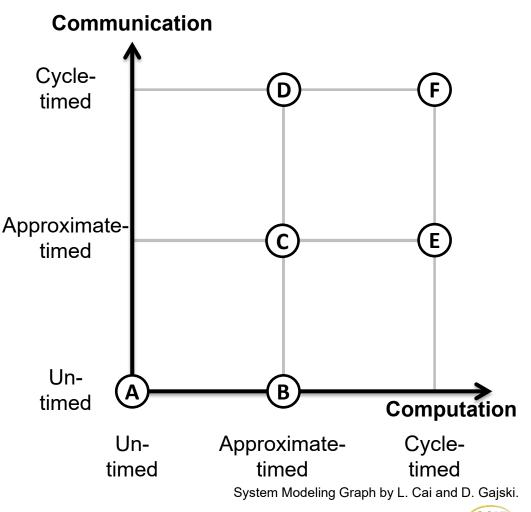

#### Communication Abstraction

# Mixing Communication Abstraction

#### Interface Definition

```

struct master rt if : public master if base

// Ports

sc in< bool > clk; // clock

sc in< bool > rst; // reset

sc out< bool > req; // master request

sc in < bool > gnt; // grant from arbiter

sc out< bool > rreq; // read request

sc out< bool > wreq; // write request

sc out< sc dt::sc bv<16> > addr; // address

sc out< sc dt::sc bv<32> > wdata; // write data

sc in < sc dt::sc bv<32> > rdata; // read data

sc in < bool > ack; // acknowledge

void if write( unsigned int , unsigned int );

unsigned int if read( unsigned int );

master rt if();

};

```

```

struct master_if_base

{

// IF methods

virtual

void if_write( unsigned int, unsigned int ) = 0;

virtual

unsigned int if_read( unsigned int ) = 0;

// Module methods

virtual

void ack_write_msg( int, unsigned int ) = 0;

virtual

void ifs_error( const char * ) = 0;

};

```

#### Communication Behavior

```

unsigned int

master rt if::if read( unsigned int address )

// set request

req.write(true);

// wait for grant

wait(gnt.posedge event());

wait(clk.posedge event());

// set read request and address

rreq.write(true);

addr.write(address);

// wait for acknowledge

wait(ack.posedge event());

wait(clk.posedge event());

// deassert request and read request

req.write(false);

rreq.write(false);

return rdata.read().to int();

```

```

unsigned int

master tl if::if read( unsigned int address )

/// transaction pointer

tlm::tlm generic payload* trans =

new tlm::tlm generic payload;

sc time delay = sc time(30, SC NS);

unsigned int data = 0;

// Initialize 8 out of the 10 attributes

trans->set comand( tlm::TLM READ COMMAND );

trans->set address(address);

trans->set data ptr( reinterpret cast

<unsigned char*> (&data) );

// ...

// Blocking transport call

socket->b transport( *trans, delay );

// obliged to check response status

if ( trans->is response error() )

ifs error("TLM-2.0: Response error");

// ...

return data

```

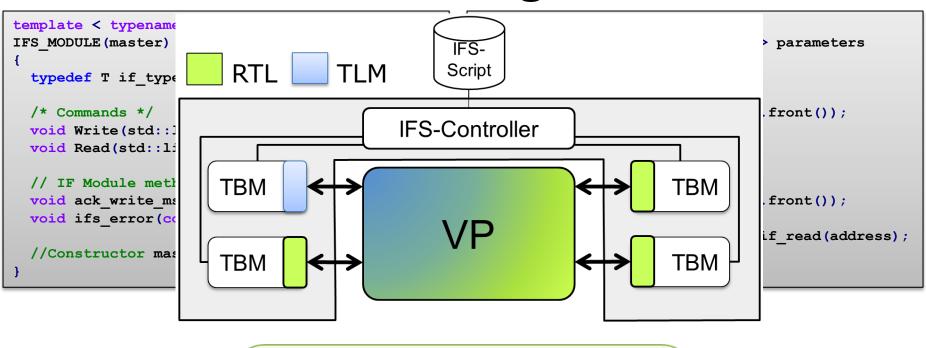

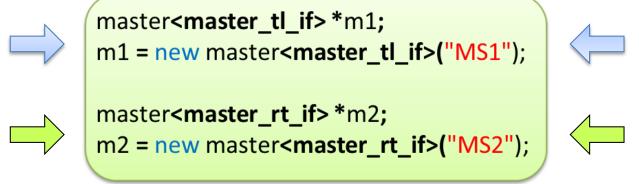

## Instantiating TBM

- Motivation

- What is the Integrated Functional Verification

Script Environment (IFS) and why use it?

- What was missing and what did we add to IFS?

- Making use of it for Back-to-Back comparison between RTL and TLM

- Conclusions

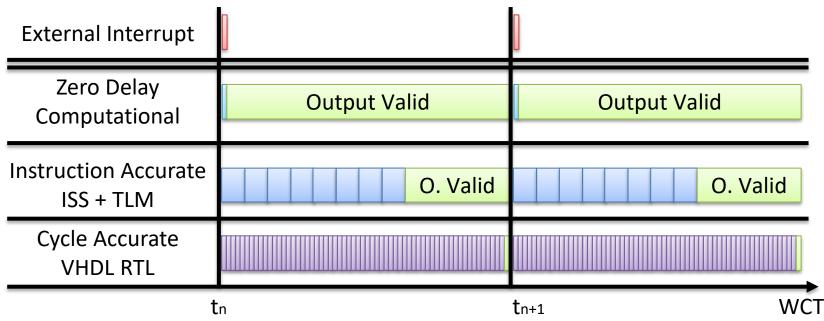

#### **Back-to-Back Simulation**

- methodology for V-model verification

- DSP from RTL to ISS + TLM

- abstraction

implies

changed timing

behavior.

#### **Abstraction and Time**

- simulated time (SIT)

- model execution time (MET)

- SIT and MIT differ across abstractions

- A. Specification

- B. Component-assembly

- C. Bus-arbitration

- D. Bus-functional

- E. Cycle-accurate computation

- F. Implementation

# Synchronization of BtB

- high abstraction is expected to execute faster

- sequence of results not guaranteed to be identical

- BtB requires synchronization

- generally not a trivial task to accomplish

- this scenario allows sync to external IRQ

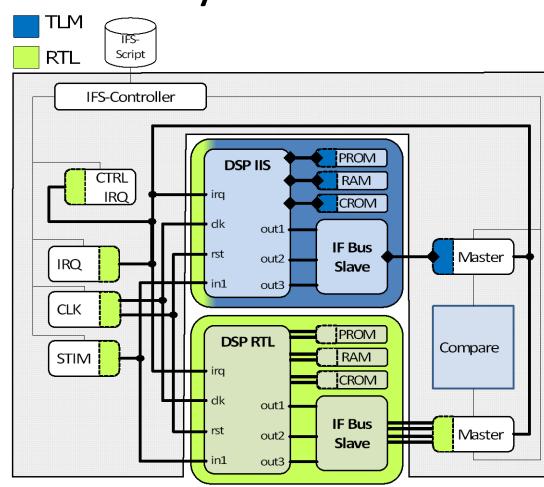

# BtB Verification Setup for DSP at RTL VHDL and IIS SystemC

- IRQ, CLK and stimuli connected parallel

- Script(s) define test(s)

- IRQ used for sync of both DUV + script

- same TBM master in two flavor

- automatic compare

- manual analysis in one waveform viewer

- Motivation

- What is the Integrated Functional Verification

Script Environment (IFS) and why use it?

- What was missing and what did we add to IFS?

- Making use of it for Back-to-Back comparison between RTL and TLM

- Conclusions

#### Conclusion

- seamless flow combining several languages and abstraction levels

- comfortable adaption of test environment to DUT variants and abstraction level

- comfortably analyzing deviations between models

- automatically generated assertions through BtB

- human readable tests specified in IFS scripts

- easier to understand than generated test vectors

- BtB across abstractions requires synchronization

#

**Acknowledgements:** This work has been funded by the German Federal Ministry for Education and Research (Bundesministerium für Bildung und Forschung, BMBF) under the grant 01IS13022 (project EffektiV). The content of this publication lies within the responsibility of the authors.