# UPF GENERIC REFERENCES: UNLEASHING THE FULL POTENTIAL

Jitesh Bansal (Mentor Graphics)

Durgesh Prasad (Mentor Graphics)

## **Agenda**

- Introduction

- Power Aware Verification using Unified Power Format (UPF)

- UPF Generic References

- Usage

- Isolation Specification and Verification

- Retention Specification and Verification

- UPF Extensions required

- Conclusion

## Introduction

#### **Today's SoCs**

- Are incredibly Complex

- Have sophisticated power management strategies for highly power efficient design

- Integrate variety of implementation cells like isolation and retention

#### **They Must**

- Verify the power management

- early in the design flow

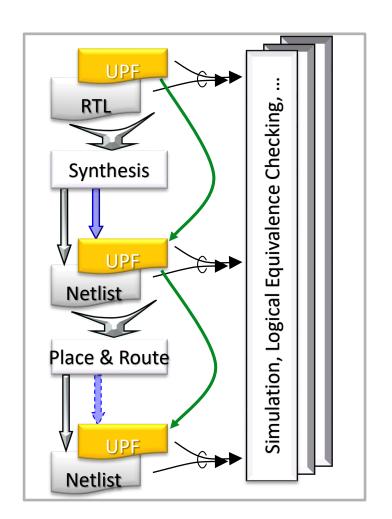

# Unified Power Format(UPF)

- RTL is augmented with a UPF specification

- To define the power architecture for a given implementation

- RTL + UPF drives implementation tools

- Synthesis, place & route, etc.

- RTL + UPF also drives poweraware verification

- Ensures that verification matches implementation

### PA Verification with UPF

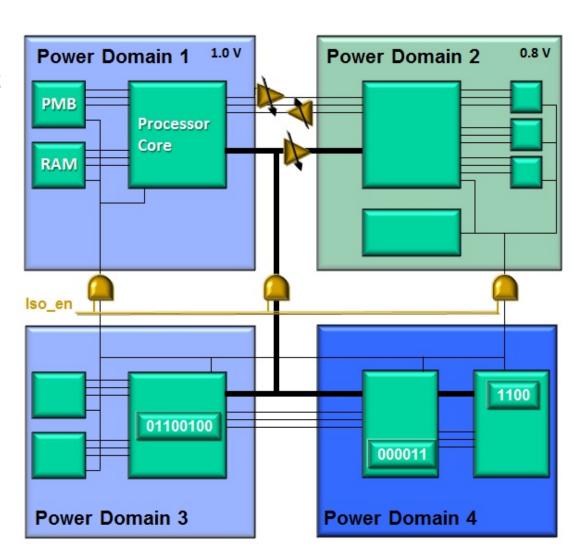

- Different Systems have different power management

- Power Gating

- Isolation

- Retention

- Multi-Voltage

- Level Shifting

- Body Bias and DVFS

- UPF provides commands to

- express the power management strategies

e.g set\_isolation

- verify the power architecture e.g bind\_checker

### **UPF Generic References**

- UPF generic references were first introduced in UPF 2.0 (IEEE\_1801\_2009).

- The generic references provide reserved keywords that cannot be redefined and would accept values depending on the context of their use.

- Types of UPF Generic References

- UPF\_GENERIC\_CLOCK Refers to the clock of a sequential logic.

- UPF\_GENERIC\_DATA Refers to the data pin of a sequential logic or isolation input pin.

- UPF\_GENERIC\_ASYNC\_LOAD Refers to the asynchronous pins of a sequential flop.

- UPF\_GENERIC\_OUTPUT Refers to the output of a sequential logic or isolation cell.

## **UPF Generic References**

#### UPF Generic References in Verilog Asynchronous Flop

| UPF Generic References | Signals |

|------------------------|---------|

| UPF_GENERIC_CLOCK      | clk     |

| UPF_GENERIC_DATA       | d       |

| UPF_GENERIC_ASYNC_LOAD | reset   |

| UPF_GENERIC_OUTPUT     | q       |

## **UPF Generic References**

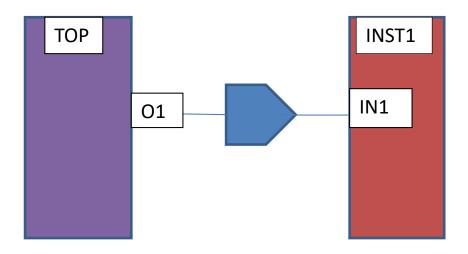

#### **UPF** Generic References in Isolation Cell Insertion

| UPF Generic References                   | Signals                                   |

|------------------------------------------|-------------------------------------------|

| UPF_GENERIC_DATA                         | O1 ('actual' for the 'formal' port 'IN1') |

| UPF_GENERIC_OUTPUT                       | IN1                                       |

| UPF_GENERIC_CLOCK/UPF_GENERIC_ASYNC_LOAD | Not Applicable                            |

# **Isolation Specification**

- map\_isolation\_cell/use\_interface\_cell

- Used for custom isolation cell

```

module SFX_ISO(input ISO, input I,output Z);

```

```

set_isolation ISO -domain PD -elements {IN1 IN2 IN3} \

-isolation_signal {iso_en}

```

## **Isolation Specification**

```

map_isolation_cell ISO \

-domain PD -elements {IN1}\

-lib_model_name {SFX_ISO}\

-ports "ISO io_en" \

-ports "I O1" \

-ports "Z IN1"

map_isolation_cell ISO \

...

```

```

map_isolation_cell ISO \

-domain PD \

-lib_model_name {SFX_ISO} \

-ports "ISO iso_en" \

-ports "I UPF_GENERIC_DATA" \

-ports "Z UPF_GENERIC_OUTPUT"

```

#### Benefits

- No need to find out the actúal

- multiple map commands not required.

- No worry about effective elements list

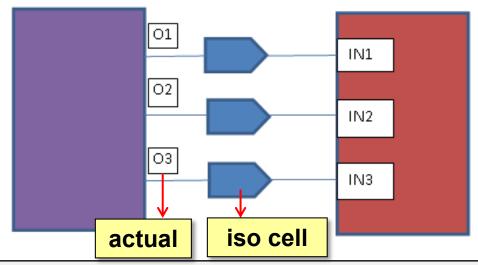

### **Isolation Verification**

- ISO cell acts like buffer in non-isolation period

- Use bind checker

```

iso checker(input iso in, output iso out, input iso en);

```

**UPF** bind checker command(No generic references)

```

bind_checker IN1_iso_checker_inst -module iso_checker \

-ports {{iso_in O1} {iso_out IN1} {iso_en iso_en}}

bind_checker IN2_iso_checker_inst -module iso_checker \

-ports {{iso_in O2} {iso_out IN2} {iso_en iso_en}}

```

## Isolation Verification

**UPF** bind checker command(with generic references)

```

array set Iso_Strat \

[query_isolation ISO -domain PD -detailed]

UPF query commands to fetch strategy details

bind_checker iso_checker_inst \

-module iso_checker \

-elements $Iso_Strat(elements) \

-ports {{iso_in UPF_GENERIC_DATA} \

{iso_out UPF_GENERIC_OUTPUT} \

{iso_en iso_en}}

```

Users need not to worry about specifying input/output of isolation cell.

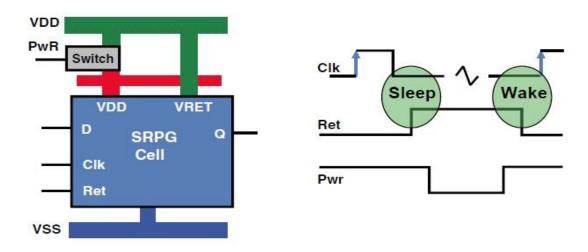

UPF provides set\_retention command with following options to customize retention behavior

- **-elements** To select a particular set of sequential elements.

- -save\_signal/-restore\_signal Logic signals to save and restore the register value.

- -save\_condition/-restore\_condition/-retention\_condition Boolean conditions that should be true for save/restore/retention operations.

- Basic Retention Strategy

- Retain all the sequential elements of power domain

- Save/Restore signals are only used to control

```

set_retention RET -domain PD -save_signal {SAVE posedge} \

-restore_signal {RESTORE posedge}

```

- Advanced Retention Strategy

- save\_condition/restore\_condition/retention\_condition are used along with save/restore signals to control retention

- Save/Restore event depends on clock/async\_load of sequential element

```

set_retention RET -domain PD -save_signal {SAVE posedge} \

-restore_signal {RESTORE posedge} -restore_condition {!CLOCK}

```

Controlling Retention behavior according to clock/async\_load is not easy and poses following problems

- Clock/Async load signals vary with each sequential element

- Difficult to determine clock/async\_load for each sequential element

- Need to write multiple retention strategies

- One strategy for each unique clock/async\_load signal

- Numerous retention strategies will make the UPF file huge and errorprone

- Custom assertions for retention cells, if written by users, are numerous and tough to maintain.

- Design is not scalable

- Modification in RTL require changes in retention strategies

| Sequential Elements                            | Retention Strategies                                                 |

|------------------------------------------------|----------------------------------------------------------------------|

| always @ (posedge CLOCK1,                      | set_retention RET1                                                   |

| posedge RESET)                                 | -domain PD                                                           |

| begin                                          | -save_signal {SAVE posedge}                                          |

| if(RESET)                                      | -restore_signal {RESTORE                                             |

| Q1 $\leq$ 1'b0;                                | posedge}                                                             |

| else                                           | -restore_condition {!CLOCK1}                                         |

| Q1 <= D;                                       | -elements {Q1}                                                       |

| end                                            |                                                                      |

| always @ (posedge CLOCK2, posedge RESET) begin | <pre>set_retention RET2 -domain PD -save_signal {SAVE posedge}</pre> |

| if(RESET)                                      | -restore signal {RESTORE                                             |

| Q2 <= 1'b0;                                    | posedge}                                                             |

| else                                           | -restore_condition {!CLOCK2}                                         |

| Q2 <= D;                                       | -elements {Q2}                                                       |

| end                                            |                                                                      |

Use of UPF generic references — UPF\_GENERIC\_CLOCK and UPF\_GENERIC\_ASYNC\_LOAD

```

set_retention RET -domain PD -save_signal {SAVE posedge } \

-restore_signal {RESTORE posedge} \

-restore_condition {!UPF_GENERIC_CLOCK}

```

- Only one set\_retention strategy is required to cover all different types of clock/aync\_load signals.

- EDA tools parse these UPF generics in restore\_condition and replace it with the specific clock of each sequential element for application of retention strategy.

- Automated, robust, and easier flow for designers.

- Scalable design, addition or deletion of sequential elements in a design does not require any change in the UPF.

| Sequential Elements                                                      | UPF generic Retention Strategy                                  |

|--------------------------------------------------------------------------|-----------------------------------------------------------------|

| <pre>always @ (posedge CLOCK1, posedge RESET) begin     if (RESET)</pre> | set retention RET                                               |

| else<br>Q1 <= D;<br>end                                                  | -domain PD -save_signal {SAVE posedge} -restore_signal {RESTORE |

| <pre>always @ (posedge CLOCK2, posedge RESET) begin     if (RESET)</pre> | <pre>posedge} -restore_condition {!UPF_GENERIC_CLOCK}</pre>     |

| Q2 <= D;<br>End                                                          |                                                                 |

## **Retention Verification**

- UPF bind checker command is used to verify the retention behavior of design

- Assertions are written in a checker module and bind to the specific instances of design using bind\_checker command

Checker module interface -

```

module ret_checker(input restore_condition,

input ret_ff, input restore_signal);

```

## **Retention Verification**

- Multiple bind\_checker statements are required for different clock/async\_load signals

- With UPF generic references, only one statement is required

- UPF\_GENERIC\_OUTPUT is retained element {Q1 Q2}

- RESTORE\_COND is !UPF\_GENERIC\_CLOCK.

- Command is applied to each element of the bind\_checker command and UPF\_GENERIC\_CLOCK in the restore condition is replaced by the corresponding CLOCK of each sequential element.

# Sequential Element TED STATES Verification

- UPF generic references can be used for custom verification of each sequential element with the help of the bind checker command.

- Example: User wants to verify that clock should be off when async load is active.

#### Checker Module -

```

module checker { input clk, input async load, input seq elem};

always @ (posedge async load)

begin

assert (!clk) else $display ("Error : CLK is not

OFF, Element value is '%b'", seq elem);

end

endmodule

```

# Sequential Element Verification TED STATES Verification

```

array set RET STRTGY [query retention RET -domain PD -detailed]

set ELEMENTS $RET STRTGY(elements)

bind checker checker inst -module checker -elements $ELEMENTS\

-ports { {clk UPF GENERIC CLOCK} \

{ async load UPF GENERIC ASYNC LOAD} \

seq elem UPF GENERIC OUTPUT } }

```

The above command would bind checker instance for each sequential element and the UPF generic references would be replaced by corresponding Clock/Async load/Output in port list.

### **UPF Extensions**

- Enhancements are required in UPF LRM to allow usage of UPF Generic References in various commands

- set retention

- Accept UPF generic references and their simple expressions in save\_condition/restore\_condition/retention\_condition

```

set_retention RET -domain PD \

-retention_condition {!UPF_GENERIC_CLOCK}

```

- query\_\* commands

- Allow query\_retention to return various condition in terms of UPF generic references to be used in bind\_checker.

## **UPF Extensions**

- bind\_checker

- Allow -ports option to accept generic references as well as their simple expressions for port mapping

```

bind_checker checker_inst -module checker -elements $ELEMENTS\

-ports { clock_signal UPF_GENERIC_CLOCK} }

```

- ports option also accepts the UPF generic references returned by query\_commands in its port mapping

```

set_retention RET -domain PD -save_condition\

{UPF_GENERIC_CLOCK && save}

bind_checker checker_inst -module checker -elements $ELEMENTS\

-ports { {save_cond $ret_array(save_condition)} ...

```

## **UPF Extensions**

- bind\_checker

- Allow -elements option to accept the list of signals. Also, the checker instance name needs to be modified for different signals in its -elements list.

```

bind_checker checker_inst -module checker \

-elements {inst1/q1 inst1/q2} ...

```

In the above case, 'q1' and 'q2' are signals within the instance 'inst1'. The expected behavior of the above command should be to bind two instances, namely 'checker\_inst\_q1' and 'checker\_inst\_q2' in the scope 'inst1'.

### **Extensions in EDA Tools**

EDA tools should be able to process UPF generic references in their context

```

set_retention RET -domain PD \

-save_condition {UPF_GENERIC_ASYNC_LOAD && !UPF_GENERIC_CLOCK}

```

EDA tools should replace save\_condition for each sequential element with their respective clocks/async loads.

```

set_retention RET -domain PD -elements {q1 q2} ... \

bind_checker checker_inst -module checker -elements $ELEMENTS\

-ports { clock_signal UPF_GENERIC_CLOCK} ...

```

Tools should be able to extract the respective clocks of 'q1' and 'q2' signals and bind the ports accordingly

#### Conclusion

- UPF Generic references are easy to use and provide automation

- Facilitate writing of a concise, scalable, and less error-prone UPF

- Very helpful in specifying custom cells and verifying various power aware cells

- requires few UPF extensions

#### Thank You