## Unique Verification Case Studies of Low Power Mixed Signal Chips

Jeff Goswick – Principle Design Engineer, NXP Semiconductors

Venkatesh Ranga – Architect, NXP Semiconductors

Madhusudhan Subramanya – Architect, NXP Semiconductors

Anand Shirwal – Department Manager, NXP Semiconductors

Pramod Rajan K S – Senior Design Engineer, NXP Semiconductors

SECURE CONNECTIONS FOR A SMARTER WORLD

### **Agenda**

- Introduction

- Four Real Life Challenges Encountered in Low Power Mixed Signal SoC Verification

- Conclusion

#### Introduction

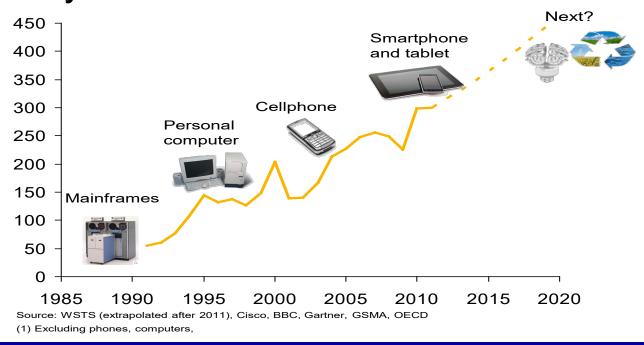

Internet of Things (IoT) is a fast growing application domain and is a key driver in taking the semiconductor industry revenue to over 400 billion dollars by 2020.

#### Introduction

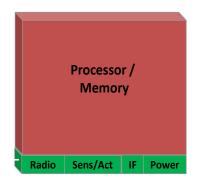

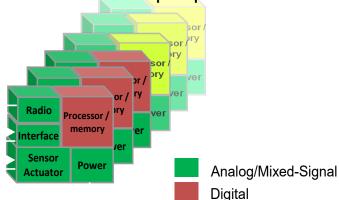

From the chip design perspective, the IoT application area moves the focus away from the big system on chip (SOC) to the mixed signal world.

#### Digital age

▶ SoC Centric

▶ 100's of nodes per person

### **Applications of the Case Studies**

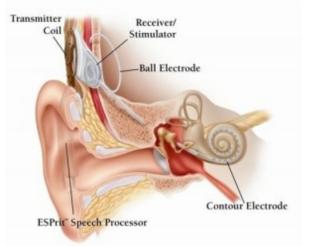

### Low-power, Compact solution for temperature logging with NFC

This cost-effective, small-form-factor solution enables long-lasting time-temperature integrators (TTIs).

#### **Wearable Product in Health Care Sector**

Highly integrated ultra-low power operation, encompassing highly sensitive analogue front-ends, low power DSP, NVM, and wireless connectivity streaming data and audio robustly around and safely though the body.

#### Ideal solutions for micro speakers:

Class-D Audio Amplifier

Louder, Deeper, Better, & Safer

# Real Life Challenges Low Power Mixed Signal SoC Verification

- 1. Modeling induced power devices in CPF and verification environment implications

- 2. Analog behavioral modeling for verification of complex power management systems

- 3. Self-checking test bench environment and formal checks for connectivity

- 4. Low drop out (LDO) sign-off criteria

# Real Life Challenges Low Power Mixed Signal SoC Verification

## Modeling induced power devices in CPF and verification environment implications

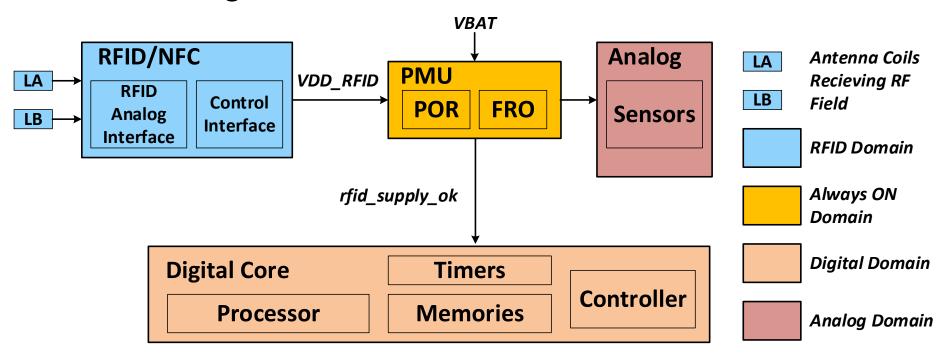

- Challenge: model the RFID/NFC power domain and verify its structure using CPF.

- Power diagram of the NFC sensor:

#### **RFID Domain Power**

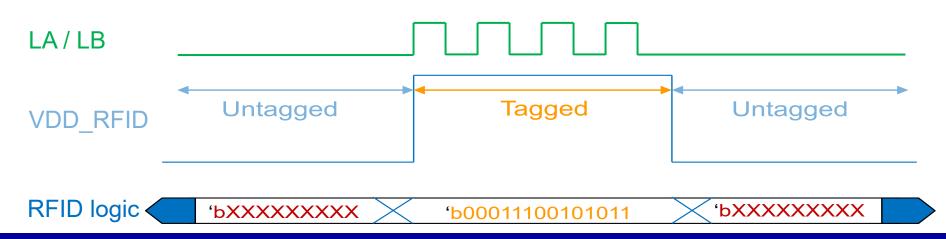

- The RFID is powered when the chip is "tagged" meaning when the antennas are receiving RF power from an NFC reader.

- To verify correct isolation and tagged/untagged transitions, in simulation the RFID logic should be corrupted when the chip is "untagged".

# The Issue: RFID Domain Isolation

- Power intent

- The PMU sets "rfid\_supply\_ok" to 1 or 0 based on the presence or absence of VDD\_RFID respectively.

- This signal is used as the 'isolation\_condition' in the CPF isolation rules for signals output from PD\_RFID.

- Initially, "rfid\_supply\_ok" was also used in the CPF for the 'shutoff condition' of the PD RFID domain.

- The same CPF is used for synthesis, simulation, and formal low power verification.

# The Issue: RFID Domain Isolation

- In simulation PD\_RFID logic is correctly corrupted when unpowered, but

- When VDD\_RFID=0, the PD\_RFID domain is OFF, and the CPF causes simulation tools treat all outputs of PD\_RFID as X.

- This makes "rfid\_supply\_ok" to go X as well.

- In order to bring the PD\_RFID domain back to ON again, the 'shutoff\_condition' signal 'rfid\_supply\_ok' needs to be made as 1.

- But since 'rfid\_supply\_ok' is derived from 'VDD\_RFID' itself, this cannot happen, a catch-22 situation.

#### Solution, almost

- Define PD\_RFID (create\_power\_domain in CPF) with "-external\_controlled\_shutoff" option without any "-shutoff\_condition".

- This models the "self-powered" aspect of PD\_RFID domain correctly in CPF.

- This makes the simulation tools to see "rfid\_supply\_ok" as 0 when PD\_RFID is OFF, and as 1 whenever PD\_RFID is ON.

- BUT the simulator doesn't corrupt the logic in PD\_RFID when the "vdd\_rfid" power is off because of the "-external\_controlled\_shutoff" option.

### **Solution Implemented**

The test bench was modified to replicate the tool behavior. It corrupts the signals in the switched off domain when an "untagged" event is detected.

```

task corrupt rfid signals(input bit yes);

begin

if(yes)

begin

force dut.Signals = 'bx;

end

Tagged

Untagged

Untagged

else

begin

release dut.Signals;

end

end

bXXXXXXXXX

'bXXXXXXXXX

'b00011100101011

endtask

```

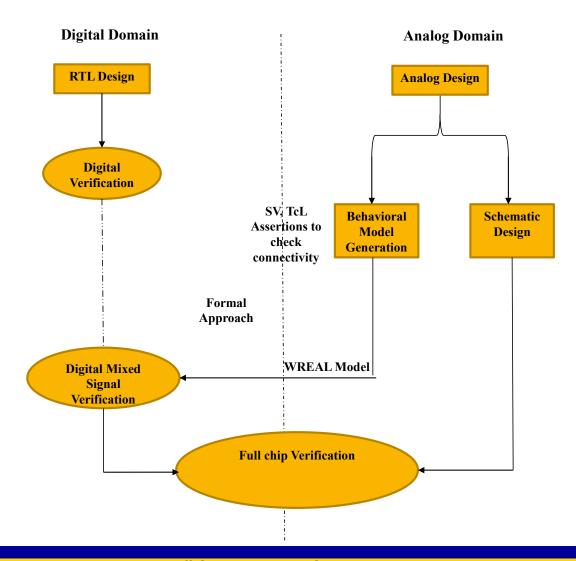

## Analog behavioral modeling for verification of complex power management systems

- Models of analog blocks are critical for mixed signal chip verification.

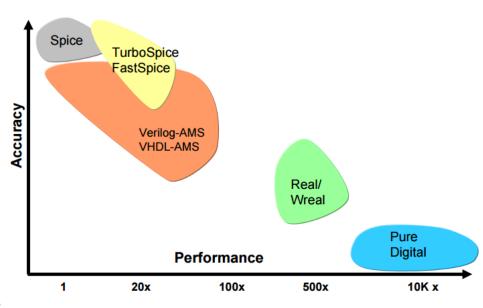

- Different abstraction levels are used in the project life cycle to tradeoff speed versus accuracy.

- System Verilog (SV):

Fast digital model with

advantages for timing variation

- Verilog wreal:

Psuedo-analog model that runs

on a digital simulation engine

- Verilog AMS:

Analog model for AMS

simulations but faster than spice

## Analog behavioral modeling for verification of complex power management systems

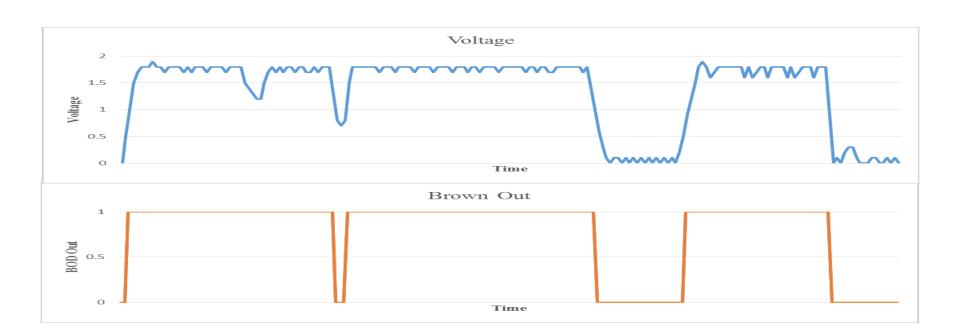

Example: Supply voltage brown out detector (BOD)

## Analog behavioral modeling for verification of complex power management systems

- System Verilog

- Allows randomization of the analog parameters to better match reality.

## Analog behavioral modeling for verification of complex power management systems

#### Wreal

- Allows real number values to propagate on Verilog wires and ports.

- Runs with only the digital simulation engine and license.

- Can model simple ideal behavior or very complex behavior.

- Can create a complex hierarchical model that can also aid in verifying the analog block itself by modeling "bottom up" using a Verilog netlist from a schematic capture tool (e.g. Cadence Virtuoso) and modeling leaf cells only.

## Analog behavioral modeling for verification of complex power management systems

Ideal wreal model

```

inout vdd dig;

wreal vdd dig;

real vdd dig p;

reg vdd dig hist;

// vdd dig hyst = rising supply

always @ ( vdd dig ) begin

vdd dig hyst = vdd dig > vdd dig p ? 1:0;

vdd dig p = vdd dig;

end

assign a2a bod vdig = !p2a bod ldo dig enable ? 1'b0 :

(pmu bod ldo dig ?

((vdd dig > 0.495 + p2a bod ldo dig thr set * 0.025 +

vdd dig hyst * p2a bod hyst set * 0.0165) ? 1'b0 :

1'b1)

: 1'bZ);

```

## Analog behavioral modeling for verification of complex power management systems

- Bottom up / netlisted hierarchical models

- Create hierarchical model from existing schematics

- Port directions, names, bus widths, etc., automatically correct

- Leaf cell behavioral models are simpler, easier to write, not as error prone

- Top level model is largely correct by construction

- Analog IP bugs often found during model creation

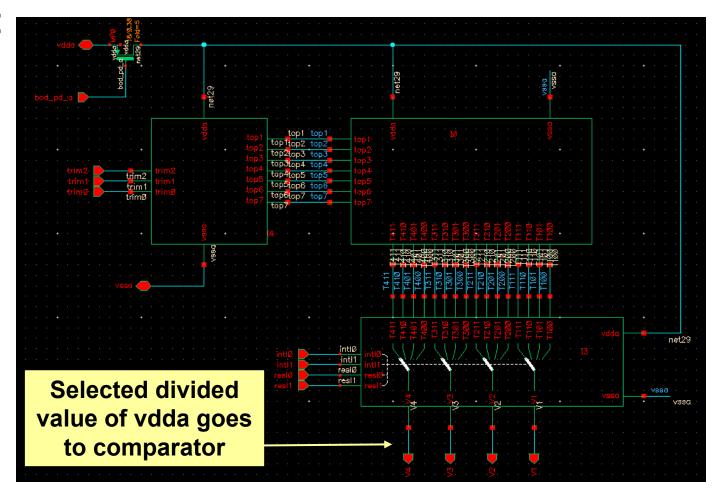

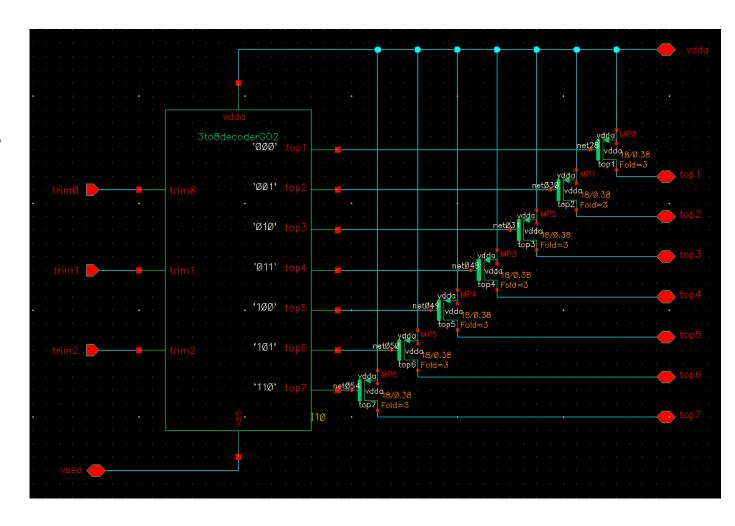

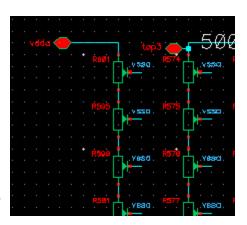

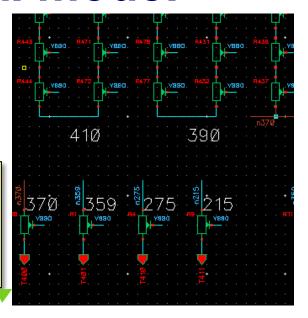

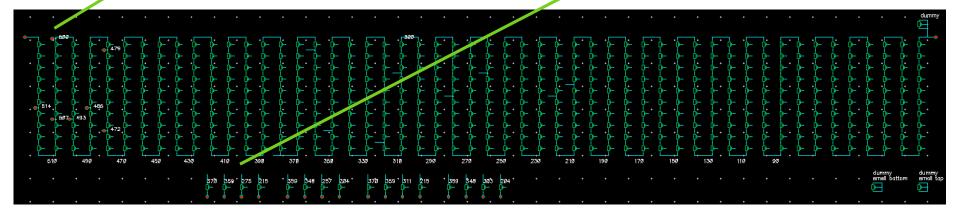

#### **BOD** circuits:

- 1. Trim mux

- 2. Vdd resistor divider

- 3. Trip level select mux

Trim mux:

3 to 7 decoder & 7 pass gates to connect vdda to top tap points in resistor divider

#### Resistor divider:

Trim supply input taps "top1", "top2", etc.

Divider output taps T400, T401, etc.

```

module divider string bod lp ( T100, T101, T110, T111, T200,...

inout top1, top2, top3, top4, top5, top6, top7, vdda, vssa;

output T100, T101, T110, T111, T200,...

wreal T100, T101, T110, T111, T200,...

always @(top1 or top2 or top3 or top4 or top5 or top6 or top7)

begin

bad rladder = 0;

if (top7 === 1)

ladder length = 472;

else

bad rladder = 1;

end

assign vdda_value_i = bad_rladder === 0 ? vdda_value

: `wrealXState;

assign T100 = vdda value i * 273 / ladder_length;

assign T101 = vdda value i * 231 / ladder length;

```

## Analog behavioral modeling for verification of complex power management systems

Verilog AMS model snippet

```

always @ (threshold, hyst) begin

rvref lo = rvin + `step size trig * (threshold);

rvref hi = rvin + `step size trig * (threshold) +

`step size hyst * (hyst);

end

a2d \#(.vh(0.001),.vl(-0.001)) i convert lo(comparator lo,

ref lo e);

a2d #(.vh(0.001),.vl(-0.001)) i convert hi(comparator hi,

ref hi e);

analog begin

V(ref lo e,n) \leftarrow V(p,n)-transition(rvref lo,0,100n,100n);

V(ref hi e,n) <+ V(p,n)-transition(rvref hi,0,100n,100n);</pre>

end

```

## Self-checking testbench and verification environment for mixed signal SoCs

- Leverage the digital verification techniques for mixed signal designs.

- Employ assertion techniques such as PSL and SVA.

- SV bind capability enables assertions developed at module level to be re-used at top level.

## Self-checking testbench and verification environment for mixed signal SoCs

Several methods of connectivity checks at the digital and analog boundary interface were deployed including a formal approach and a TcL based connectivity check.

```

TcL:

check_connectivity $path(SOURCE) $path(DESTINATION)

```

### Self-checking testbench and verification environment for mixed signal SoCs

Assertions were coded in SV to check on the internal supply voltage of an analog block to be within a threshold level.

Self-Checking Testbench and Verification Environment for Mixed Signal SoCs

- Incisive Formal Verifier (IFV/ IEV) from Cadence was used for Formal Verification.

- Conformal Low Power used for Formal Power Intent Verification.

- Cadence's "Enterprise Planner" was used to track the verification progress. This tool supports a methodology to maintain the traceability matrix.

# Case Study: 4 LDO Sign off Criteria

- To design a low power compact LDO an accurate model of the chip power behavior across the various operating modes is needed.

- Around 5 use-cases were identified per LDO which simulated the different modes like startup mode, idle mode, processor running at different speeds etc. on the synthesized netlist initially and finally on the back annotated clock tree inserted netlist.

- Simulation data was given to red hawk tool to generate the Chip Power Models-CPM for the above scenarios.

# Case Study: 4 LDO Sign off Criteria

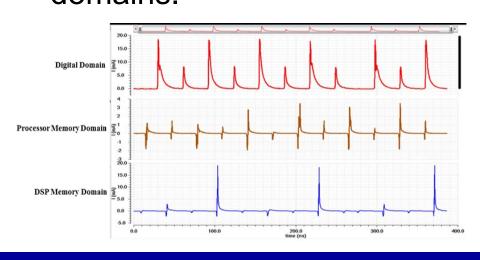

- These SPICE level chip power models were used in the LDO sign off simulations to finalize the design of the LDO blocks and determine the amount of de-caps to be used in the chip for every domain to ensure power integrity.

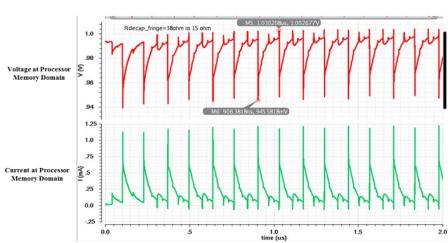

- Figure shows the SPICE simulation snapshot of peak current excursion for the digital, processor memory and DSP memory domains.

Low drop out (LDO) sign-off criteria.

Table below outlines the peak to average current consumption ratio, which turned out to be high for the memory domain.

| Domains          | Peak Current (mA) | Average<br>Current (mA) |

|------------------|-------------------|-------------------------|

| Digital Domain   | 18.8              | 1.53                    |

| Processor Memory | 19                | 0.211                   |

| domain           |                   |                         |

| DSP Memory       | 3.51              | 0.0668                  |

| Domain           |                   |                         |

The processor memory domain suffered from excessive voltage drop in these simulations. This was fixed by increasing the number of de-caps in this domain.

#### **Conclusion**

- While CPF supports classical power scenarios like always on, shut off it required changes in the environment to model the Induced Power scenario.

- Power management systems have very intricate dependencies between the analog and the digital controller. To jump start the verification we started using randomized System Verilog models then replaced it with Wreal models and finally the Verilog AMS models, thus achieving high accuracy in final sims while reducing overall verification time.

- Digital techniques like assertions and formal checks proved to be useful in the mixed signal world. Continuing along these lines we intend to evaluate UVM for future chips.

- A robust method to sign off LDO resulted in the accurate verification of power supply which is key in ensuring silicon power integrity.

### **Questions?**

### **Thank You**