# Unified Test Writing Framework for Pre and Post Silicon Verification

Rahulkumar Patel

Pablo Cholbi

Sivasubrahmanya Evani

Raman K

# Agenda

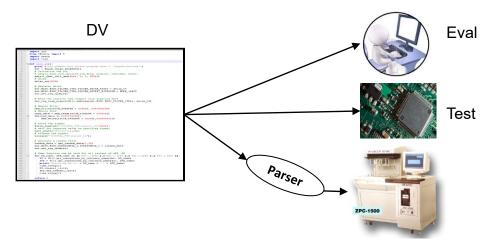

- DV Environment overview

- The Journey

- Challenges Faced

- Solutions

- Results

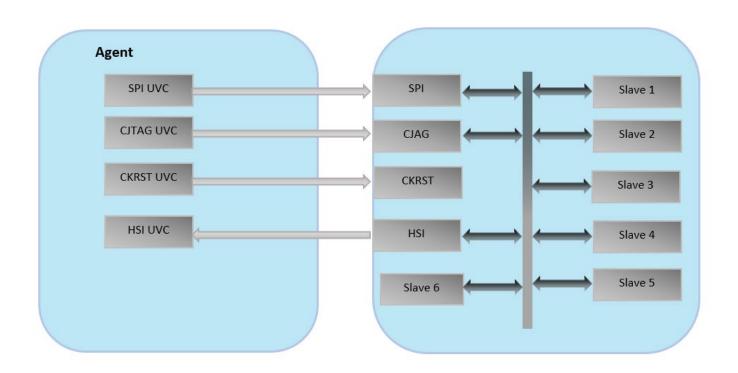

## **DV Environment Overview**

Top Level view of verification environment

## **Problem Statement**

- Why is this framework needed?

- P1: Test writing in UVM for non digital folks is a challenge.

How do we get them on board (especially for mixed signal simulation)?

- P2: How can we reuse all/most of the pre silicon infrastructure developed to enable faster post silicon debug?

Problem1: How do we get more people on board?

```

//configure spi

spi_cnfg 0x01 0x01;

spi_write 0xF001604c 0x04 0x12345678;

spi_read 0xF001604c 0x04 0x12345678;

force_ivalue_signal `CHIPTOP.muxout_in 0xFFFE;

wait_pin GPIO[1] 0 10;

delay 20;

force_ivalue_signal `CHIPTOP.muxout_in 0x01;

mait_pin GPIO[1] 1 10;

```

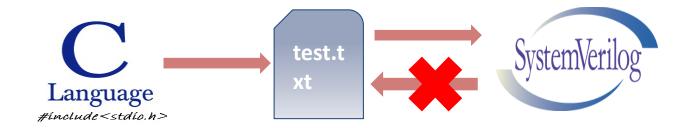

test.txt

- Pros

- Simple txt interface, easy to write.

- Saves Compilation time

- Cons

- Easy to write but difficult to maintain

- Vulnerable to regMap changes

- Difficult to port across products

## Cont...

Problem1: How do we get more people on board?

test.c

- C wrapper on text based interface

- Bit field Centric

- Pros

- Easy to write/understand

- Portable

- Allows to develop layers of functions

- Cons

- Unidirectional, no conditional loops/branches

## Cont...

- Key Feature Set

- MMR read/write

- Memory read/write

- Analog node voltage probing

- Force/Release/Wait on digital nodes

- Waiting for specific voltage on analog node

- Delay

## Cont...

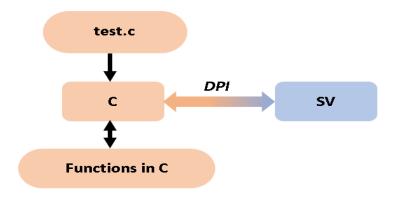

- Recap :

- Unidirectional communication

How to mimic the host processor?

### Cont...

- Direct Programming Interface (DPI)

- Import of the C functions and export the SV functions

Cont...

Taped Out...!!!

Silicon Arrived...!!!

## Cont...

• Problem2: How can we reuse the pre-silicon infrastructure for post-silicon?

#### **Eval. Engineers:**

Develop the test cases in Python

#### **DV Engineers:**

Develop the test cases in C/SV/UVM

• C is well suited in communicating with the simulators, it is not that well suited to communicate with lab equipment

## Challenges

- Python <=> SV

- SV can't communicate directly with Python

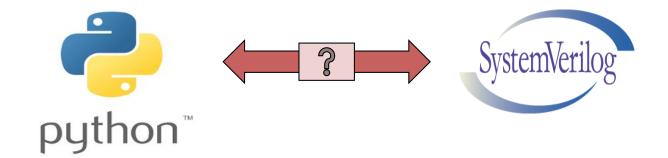

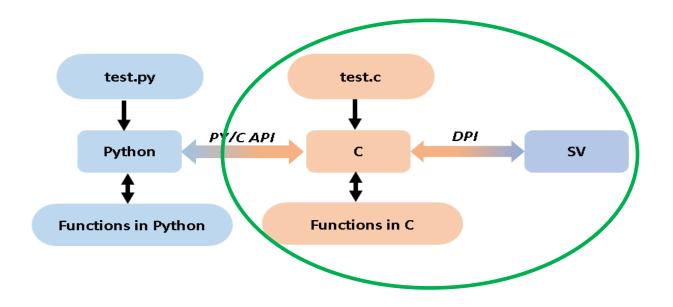

### Solution

- API-DPI Cascade Bridge

- Direct Programming Interface (DPI) for SystemVerilog—C

- Python-C API for Python—C

- API provides access to the Python interpreter from C code.

- **Embedding Python:** Inserting calls to Python interpreter into your C application and Calling Python code at specific time

- Extending Python: Python interpreter loads the set of C functions as part of import statement

## Solution

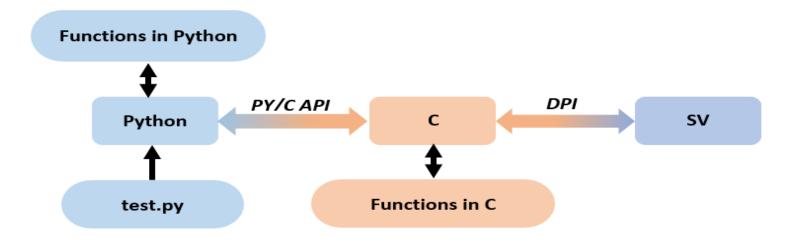

### Cont...

#### **Embedding Python:** Call python method *main\_py* of *test.py* from C

```

#include <Python.h>

#include <stdlib.h>

extern void PyInit CModule();

int command main() {

setenv("PYTHONPATH",".",1);

/* Add a built-in module, before Py Initialize */

PyImport AppendInittab("CModule", PyInit CModule);

/* Initialize the Python Interpreter */

Py_Initialize();

/*Get a reference to the test.main py function*/

PyObject *pFunc, *u_name, *module;

PyObject *args:

PyObject *kwargs;

PyObject *result = 0;

int retval;

/*Get a reference to the test.main py function*/

u name = PyUnicode_FromString("test");

module = PyImport Import(u name);

Py DECREF(u name);

pFunc = PyObject GetAttrString(module, "main py");

/* Make sure we own the GIL(global interpreter

lock) */

PyGILState STATE state = PyGILState Ensure();

/* Verify that func is a proper callable */

if (!PyCallable Check(pFunc)) {

fprintf(stderr, "call_func:expected a

callable \n");

goto fail;

/* Build arguments */

args = Py_BuildValue("()");

kwargs = NULL;

```

```

/* Call the function */

result = PyObject Call(pFunc, args, kwargs);

Py DECREF(args);

Py XDECREF(kwargs);

/* Check for Python exceptions (if any) */

if (PyErr Occurred()) {

PyErr Print():

goto fail;

}

/* Verify the result is a int object */

if (!PyLong Check(result)) {

fprintf(stderr, "call func: callable

didn't return a Long\n");

goto fail:

}

/* Create the return value */

retval = PyLong_AsLong(result);

Py DECREF(result):

/* Restore previous GIL state and return */

PyGILState Release(state):

/* Done */

Py DECREF(pFunc):

Py Finalize();

return 0;

fail:

Py XDECREF(result);

abort(); // Change to something more

appropriate

```

#### **Extending Python:** Create a module which contain set of C functions

```

//initCModule.c

#if PY MAJOR VERSION >= 3

static struct PyModuleDef moduledef = {

#include <Python.h>

PyModuleDef HEAD INIT, /* m base */

#include "basic op.h"

/* m name */

"CModule",

/* m doc */

NULL,

/* This is a wrapper function for C function "mem write". */

/* m size */

-1,

static PyObject* py mem write(PyObject* self, PyObject*

/* m methods */

CModule methods

args)

};

#endif

uint32 t addr;

uint32 t data;

/* Python calls this to let us

PyArg ParseTuple(args, "II", &addr, &data);

initialize our module */

// part of basic op.h which call the SV

PyMODINIT FUNC

mem write(addr, data);

PyInit CModule(void)

return Py BuildValue("");

}

return PyModule Create(&moduledef);

/* This is a wrapper function for C function "mem read". */

static PyObject* py mem read(PyObject* self, PyObject* args)

uint32 t return val;

uint32 t addr;

PyArg ParseTuple(args, "I", &addr);

// part of basic op.h which call the SV

return val = mem read(addr);

return Py BuildValue("I", return val);

}

/* Bind Python function names to our C functions */

static PyMethodDef CModule methods[] = {

{"mem_write", py_mem_write, METH_VARARGS},

{"mem read", py mem read, METH VARARGS},

{NULL, NULL}

```

# **Byproduct**

Pre-Silicon Test suite developed is still valid ...!!!

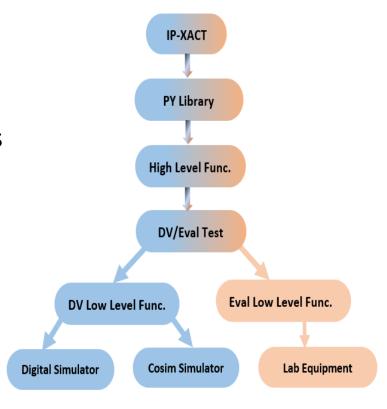

### Framework Overview

- Most of the framework auto dumped form YODA through custom script

- Test cases / functions are reused across all the stage of product development

## Sample test Case

```

Extending Python

from CModule import *

from chips import Util

import Bench

import time

def main py():

print ("You passed this Python program from C! Congratulations!")

8

9

dut = Bench.chips.ADAR690x()

10

# Initialize the PLL

dut.ADC ADPLL.adcpll_fast_init_gen(80e6, 0, 1, 500e3)

11

Function declared In C

12

13

delay ns(1000)

14

15

dut.MISC.MISC FILTER CTRL.FILTER DECIM RATIO = 0x20

16

17

dut.MISC.MISC FILTER CTRL.FILTER OUTPUT BITWIDTH = 0x1

Register Write

18

dut.dev reg update()

19

20

## Read the register and compare with excepted data

21

dut.comms.read expect(Util.Address(dut.MISC.MISC SCRATCHPAD 0), 0x30, 0x04)

22

Register Read

23

## Memory Write

24

dut.comms.write((DCCM STRADDR+0x500), 0x12345678, 0x04)

test.py

## Memory Read

27

read data = dut.comms.read((DCCM STRADDR+0x500), 0x04)

28

if(read data != 0x87654321):

Memory Wr/Rd

29

read data = dut.comms.read((DCCM STRADDR+0x500), 0x04)

print (read data)

31

32

#force the signal

33

force digital("'DIGITAL TOP.muxout in",0x01)

34

#wait for expected value on specificed signal

35

wait state ("GPIO[1]",1,10)

36

#release the signal

Force/Wait/Release

release("`DIGITAL TOP.muxout in")

37

38

39

#generate a random value

40

random data = gen random data(1,10)

dut.MISC.MISC_SCRATCHPAD_1.SCRATCHPAD_1 = random_data

41

42

dut.dev_reg_update()

43

44

#Same function can be used for all instand of AFE.RX

45

for RX name, AFE name in [['RX0','AFE0'],['RX1','AFE1'],['RX2','AFE2'],['RX3','AFE3']];

46

RX = Util.get subsystems by instance name(dut,RX name)

47

AFE = Util.get subsystems by instance name(dut, AFE name)

DESIGN AND VERIFICATION

48

RX.channel init()

49

AFE.afe channel init()

19

50

51

return 0

```

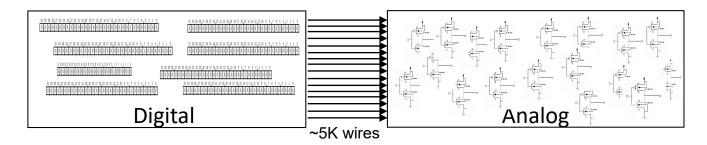

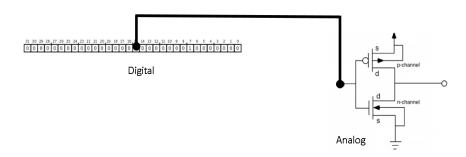

## **Extended Solution**

Automated Checks for the connectivity from digital register bits to the relevant analog nodes in mixed signal simulation.

## **Extended Solution**

### Cont...

```

import sys

from CModule import *

from chips import Util

import Bench

import time

def main py():

8

9

dut = Bench.chips.ADAR690x()

10

11

comment ("Testing afe0 adc bias ctrl0.adc dac23 ncs ctrl")

12

# local hier[] = "<digimmic.die.rx section.rxchannel0.afe>adc dac23 ncs ctrl";

13

signal="<DIGIMMIC.DIE.RX SECTION.RXCHANNELO.AFE>ADC DAC23 NCS CTRL"

14

comment ("signal="+str(signal)) # FOUND HIERARCHY OF AFEO.ADC BIAS CTRLO.ADC DAC23 NCS CTRL

15

# Bus check

16

for i in range(2):

17

dut.AFE0.ADC_BIAS_CTRL0.ADC_DAC23_NCS_CTRL = 0X1 << i; dut.dev_reg_update();</pre>

18

dut.comms.read expect(Util.Address(dut.AFE0.ADC BIAS CTRL0), 0x1<<(i+24),0x04);</pre>

19

probe bus expect(signal, 0x1 << i);</pre>

20

21

dut.AFE0.ADC BIAS CTRL0.ADC DAC23 NCS CTRL = 0X0; dut.dev reg update();

dut.comms.read expect(Util.Address(dut.AFE0.ADC BIAS CTRL0), 0x0,0x04);

23

probe bus expect(signal, 0x0);

24

25

comment("Testing afe0 adc bias ctrl0.adc amp3 stgl bias")

26

# local hier[] = "<digimmic.die.rx section.rxchannel0.afe>adc amp3 stgl bias";

27

signal="<DIGIMMIC.DIE.RX SECTION.RXCHANNELO.AFE>ADC AMP3 STG1 BIAS"

comment ("signal="+str(signal)) # FOUND HIERARCHY OF AFEO.ADC BIAS CTRL0.ADC AMP3 STG1 BIAS

28

29

# Bus check

30

for i in range(2):

31

dut.AFE0.ADC_BIAS_CTRL0.ADC_AMP3_STG1_BIAS = 0X1 << i; dut.dev_reg_update();</pre>

32

dut.comms.read expect(Util.Address(dut.AFE0.ADC BIAS CTRL0), 0x1<<(i+8),0x04);</pre>

33

probe bus expect(signal, 0xl << i);</pre>

34

35

dut.AFE0.ADC BIAS CTRL0.ADC AMP3 STG1 BIAS = 0X0; dut.dev reg update();

dut.comms.read expect(Util.Address(dut.AFE0.ADC BIAS CTRL0), 0x0,0x04);

36

37

probe bus expect(signal, 0x0);

38

39

return 0

```

## Other benefits

- Functions and test re-use across digital and mixed signal simulation.

- Enables the verification infrastructure of complex data-paths present in the system

- Using power of Python packages like numpy to compute FFTs etc.

- Enabled system boot-up infrastructure with minimal effort.

- Enabled designers to get involved in test development.

- Accelerating debug, evaluation and demo creation.

### Results

- Eval and Apps support

- Easy debug of configurations issues from Evaluation and Applications

- Tester support

- UltrFlex tester was used which has a Visual Basic (VB) Front End and all the chip configurations that were developed in Py/C were translated as VB code with minimal effort.