## Trends in Functional Verification: *A 2016 Industry Study*

## Invited Talk

## Harry D Foster

Chief Scientist Verification Mentor Graphics Corp

February 28, 2017

# LIES, DAMN LIES, AND STATISTICS

## **Design Size by Projects**

20%

## ~31% of designs over 80M gates ~20% of designs over 500M gates

## **Study Background**

Worldwide study

- North America, India/China, Japan, Rest of World

Sample frame consisted of 1738 participants

8% smaller than our 2014 study (1886)

3.3x larger than our 2012 study

9.4x larger than the 2004 Collett International study

Confidence interval 95%

— ±2.36% Margin of Error

## Design Productivity Grew 5 Orders of Magnitude Since 1985

1,000,000,000,000,000 100,000,000,000,000 10,000,000,000,000 1,000,000,000,000 100,000,000,000 10,000,000,000 Quantity 1,000,000,000 100,000,000 10,000,000 1,000,000 100,000 10,000 1992 1993 1992 1991 1999 2002 2003 2005 2001 2009 J. Ser 10<sup>80</sup> 2013 Transistors Produced — Total Electronic Engineers

Source: Technology Research Group – EDA Database, 1986, EDA TAM, 1989 & Gartner/Dataquest 2005 Seat Count Report, Gary Smith EDA, 2013 Seat Count Analysis, VLSI Research, 2013 - Transistors Produced Analysis

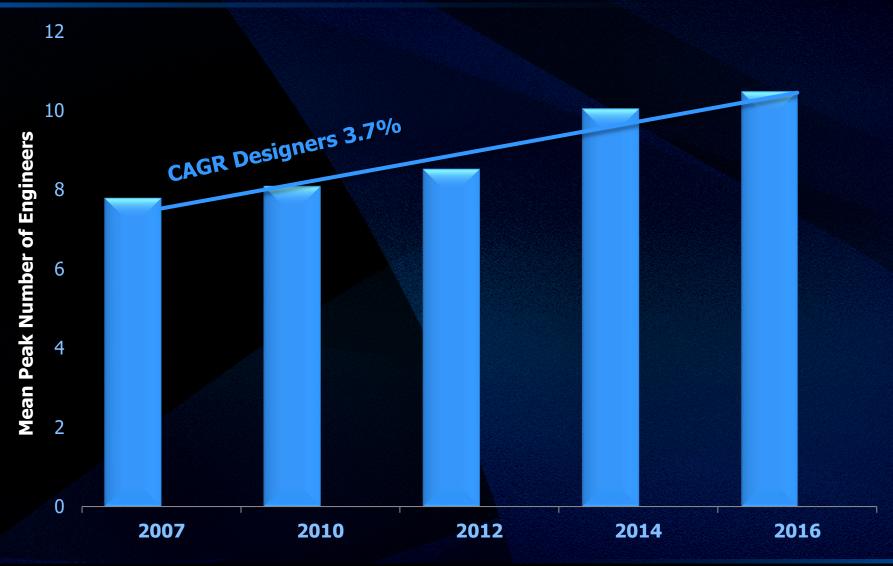

## **Demand for Design Engineers Grows Slowly**

### **Demand for Verification Engineers 3X Designers**

# RISING VERIFICATION COMPLEXITY

## **Emergence of New Verification Requirements**

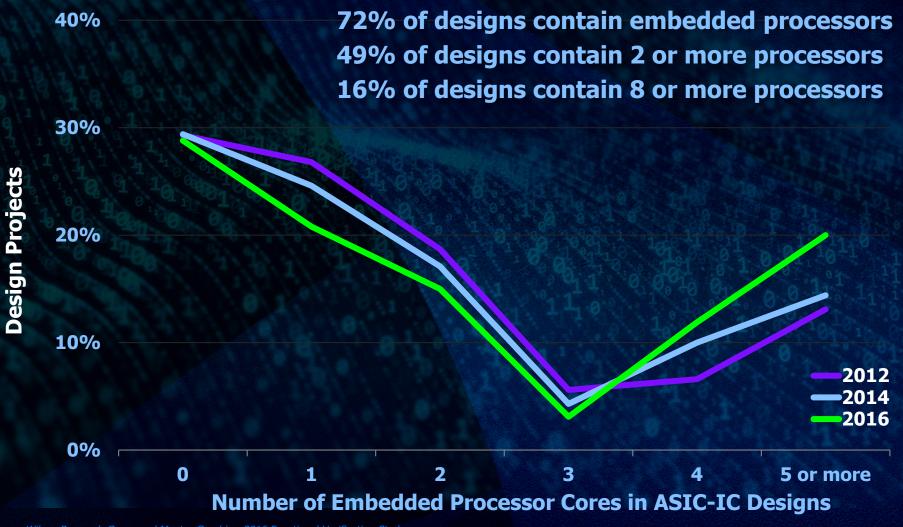

## It's an SoC World

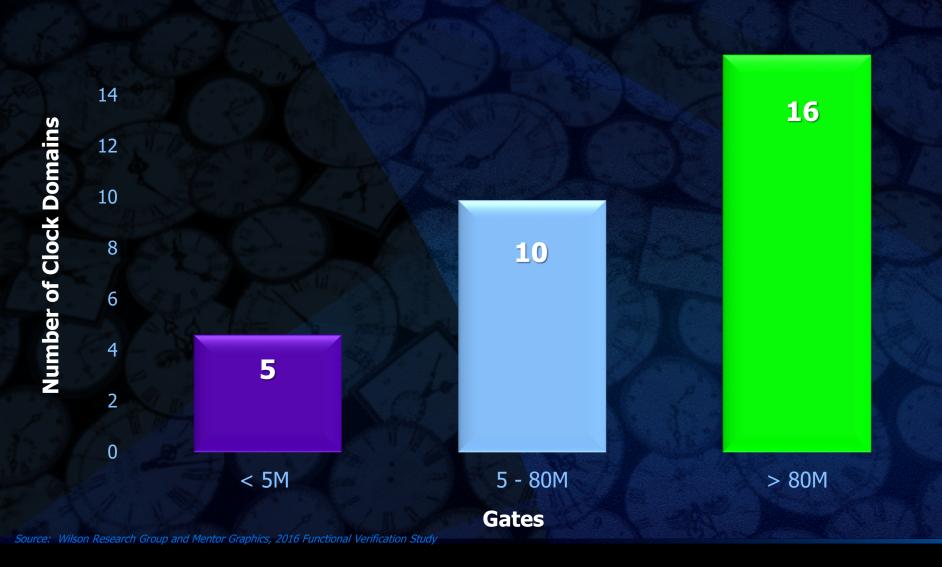

## Number of Clock Domains Increases with Design Size

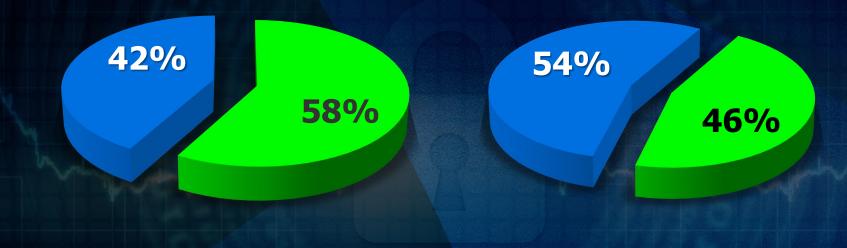

### **Designs Projects Implementing Security Features**

#### **ASIC/IC Projects**

**FPGA Projects**

Security Features

No Security Features

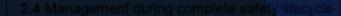

## **Projects Working on Safety Critical Design** 56% 54% 46% 44% **ASIC/IC Projects FPGA Projects** Safety Critical Design DO-254, ISO26262, IEC60601, IEC61508, etc. Not Safety Critical

Source: Wilson Research Group and Mentor Graphics, 2016 Functional Verification Study

12 Harry Fector, DVCon February 201

13 Harry Foster, DVCon February 2017

8.12 Overall quality management

8.13 Qualification of software tools

8.14 Qualification of software libraries

# IMPACT OF RISING COMPLEXITY

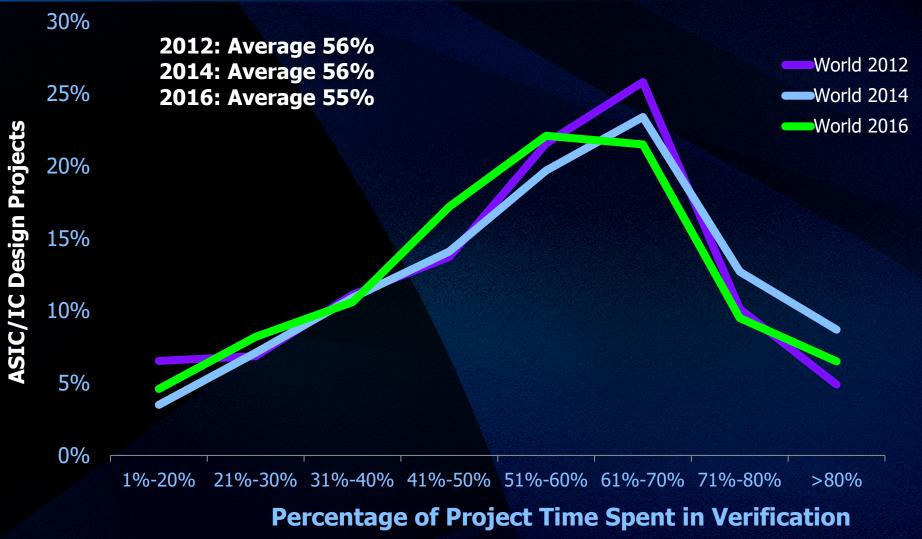

## **Verification Project Time**

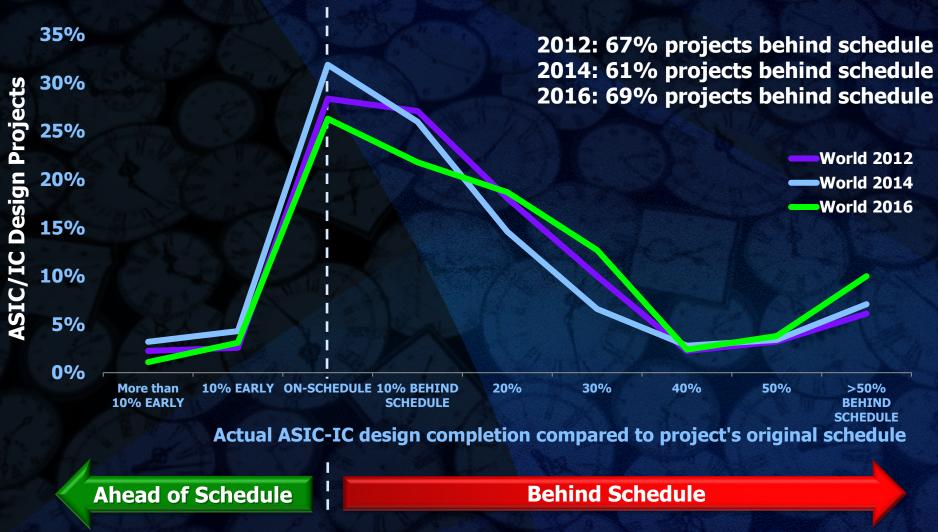

## **Project Completion to Original Schedule**

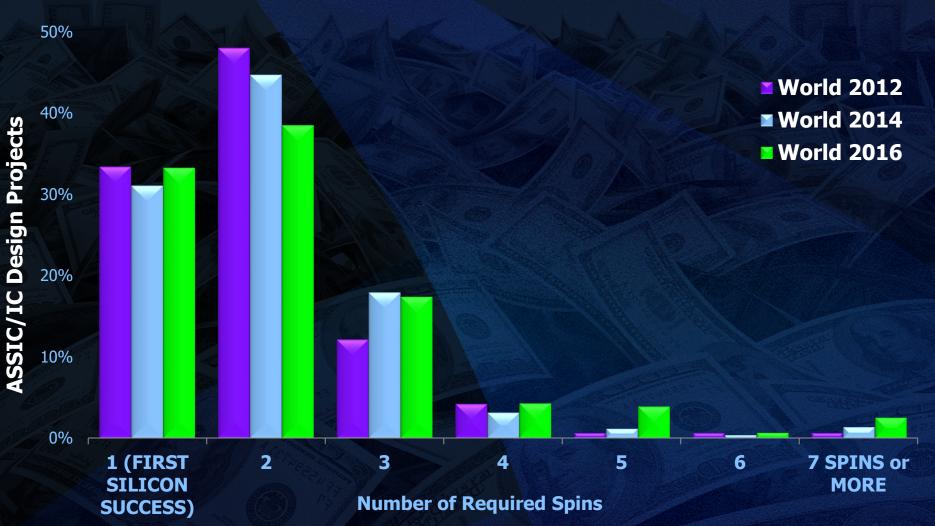

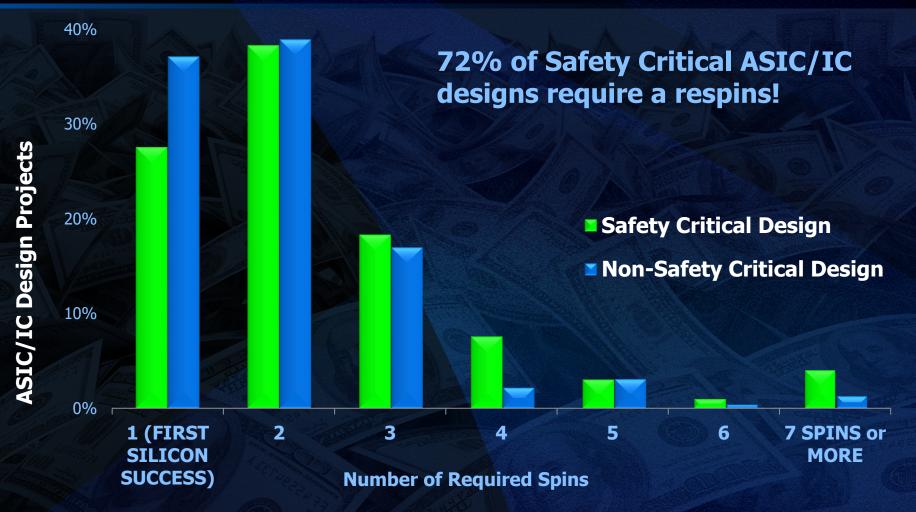

## **Number of Required Spins Before Production**

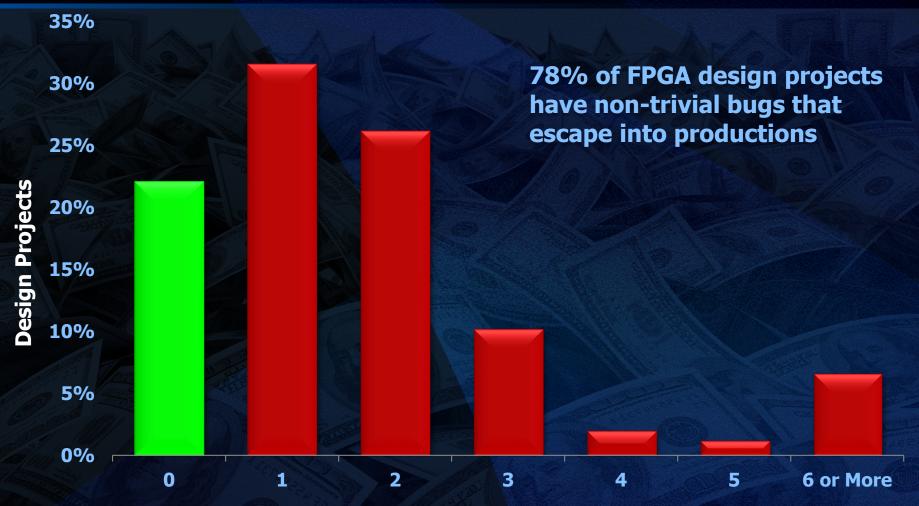

## **Number of FPGA Bug Escapes to Production**

#### **2016 FPGA Non-Trivial Bug Escapes to Production**

## **Flaws Contributing to Respins**

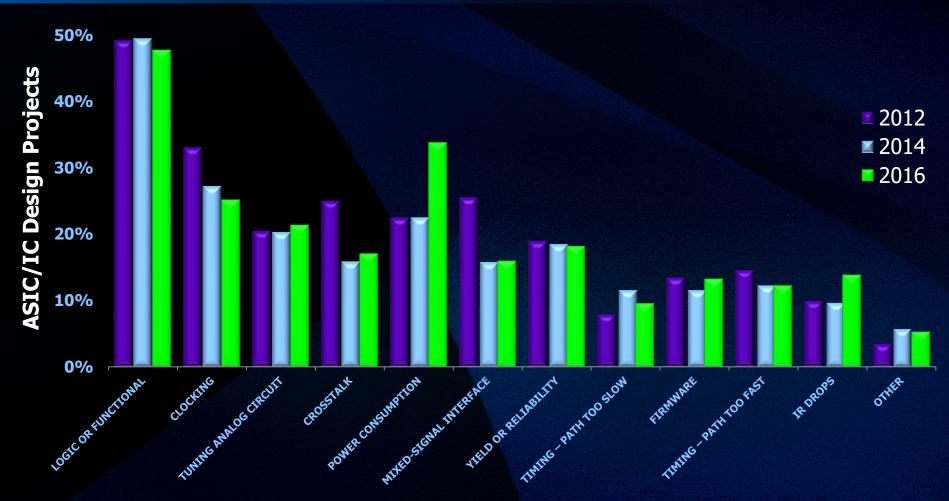

#### **Trends in Types of Flaws Resulting in Respins**

\* Multiple answers possible

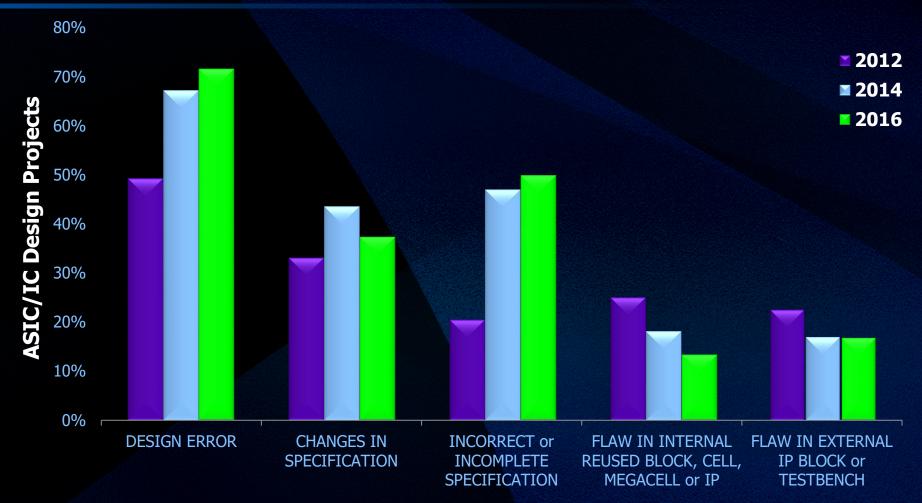

## **Root Cause of Functional Flaws**

#### **Root Cause of Functional Flaws**

# Projects Working on Safety Critical Design

Safety management during development

## **Required Spins for Safety Critical Designs**

#### DO-254, ISO26262, IEC60601, IEC61508, etc.

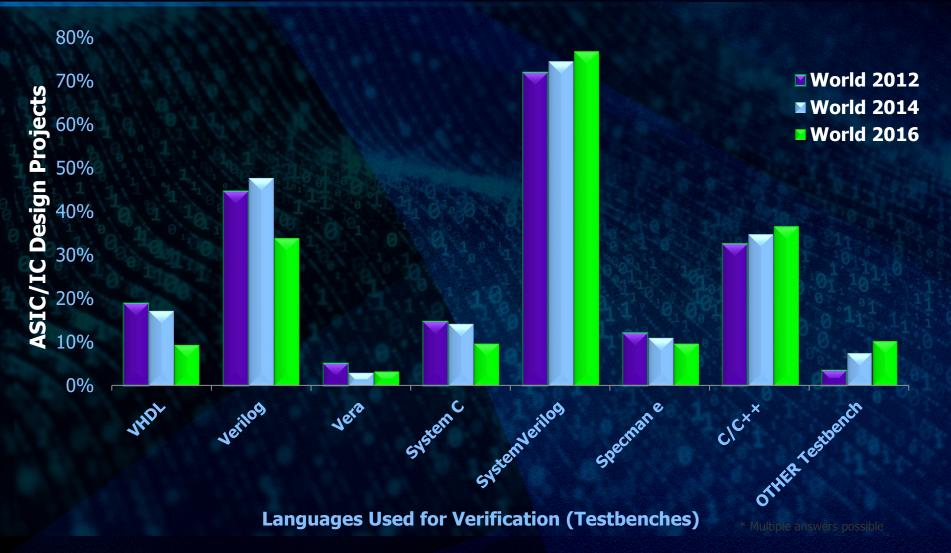

## LANGUAGES & METHODOLOGIES

## **Verification Language Adoption Trends**

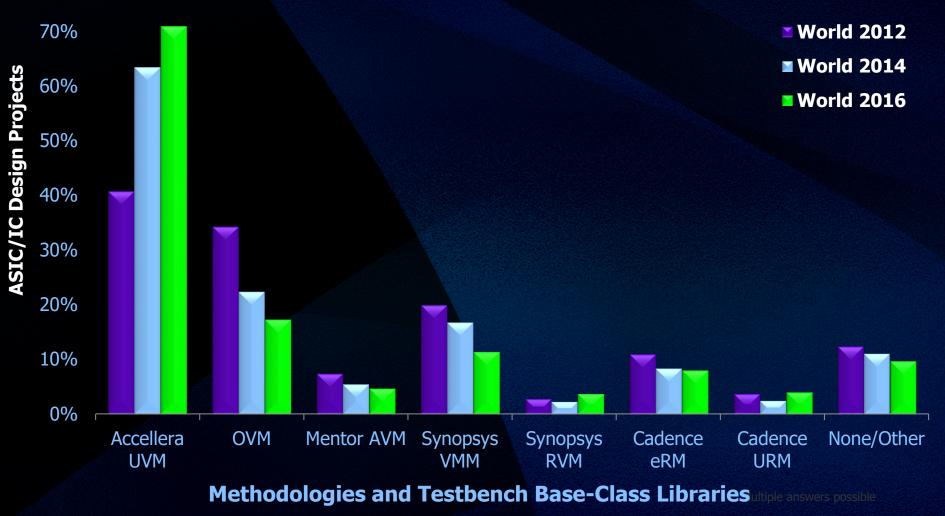

## **Testbench Methodology Adoption Trends**

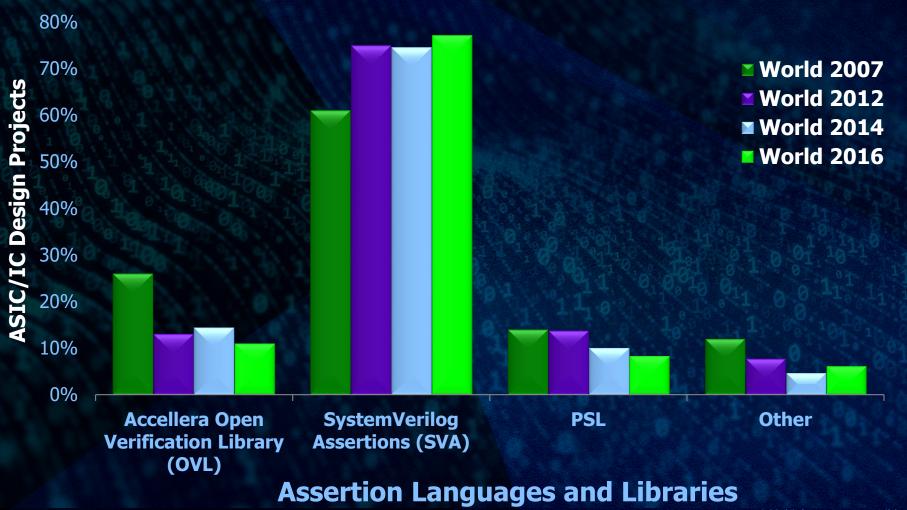

## **Assertion Language Adoption**

Source: Wilson Research Group and Mentor Graphics, 2016 Functional Verification Study

\* Multiple answers possible

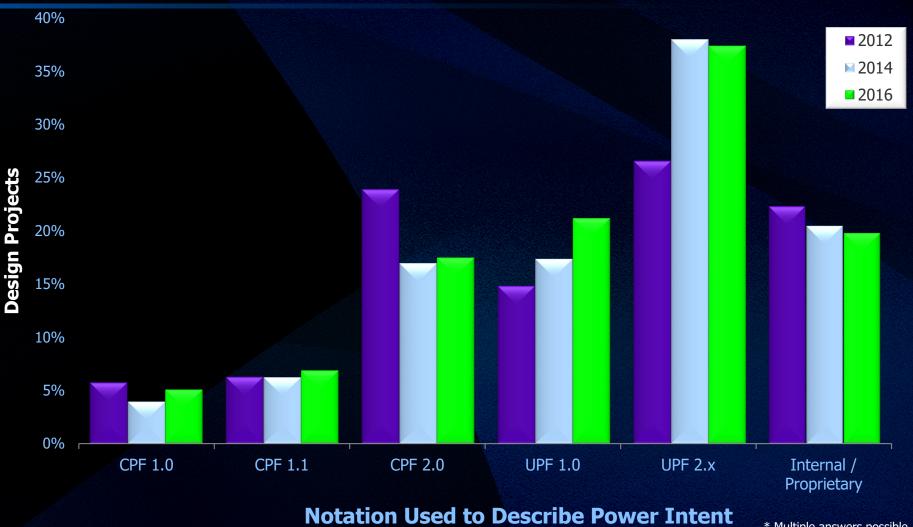

## **Power Intent Standards Trends**

\* Multiple answers possible

## VERIFICATION ADOPTION TRENDS

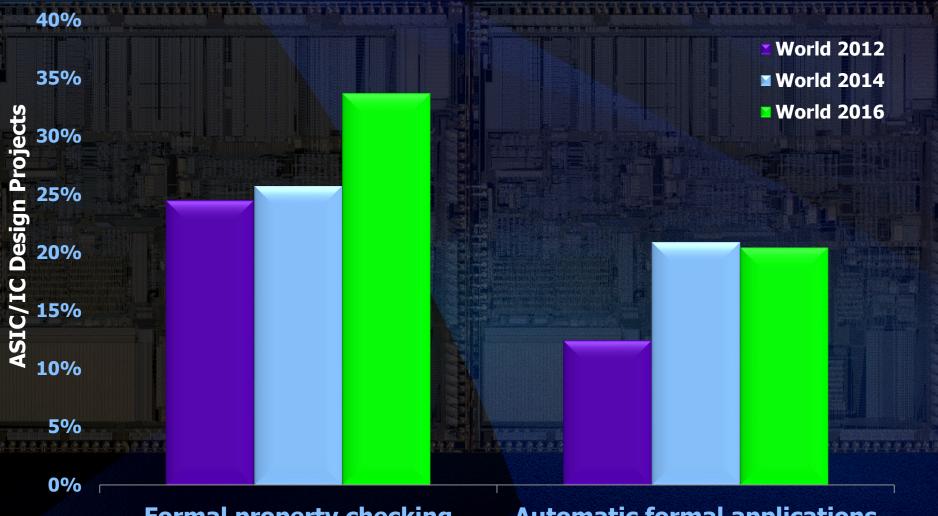

## **Formal Technology Adoption Trends**

#### Formal property checking

Source: Wilson Research Group and Mentor Graphics, 2016 Functional Verification Study

#### **Automatic formal applications**

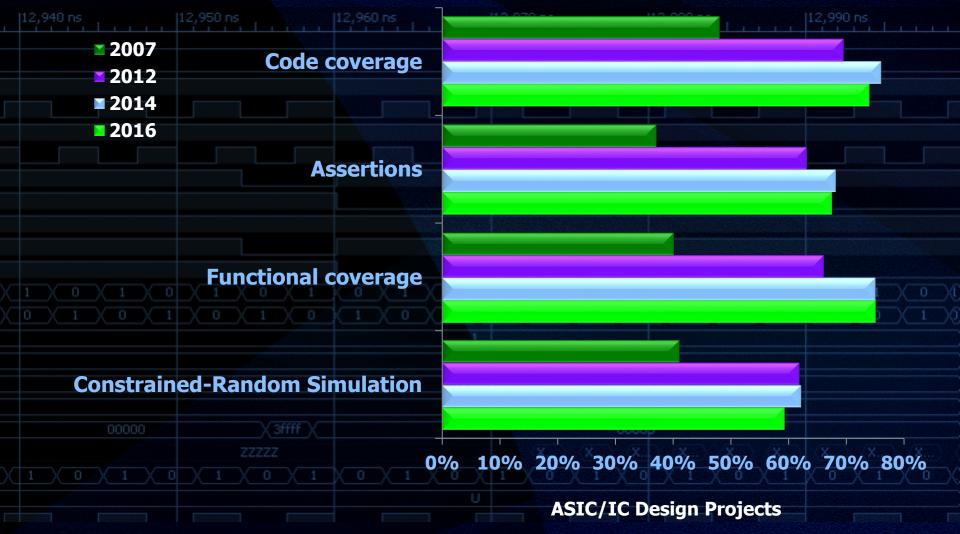

## **Dynamic Verification Adoption Trends**

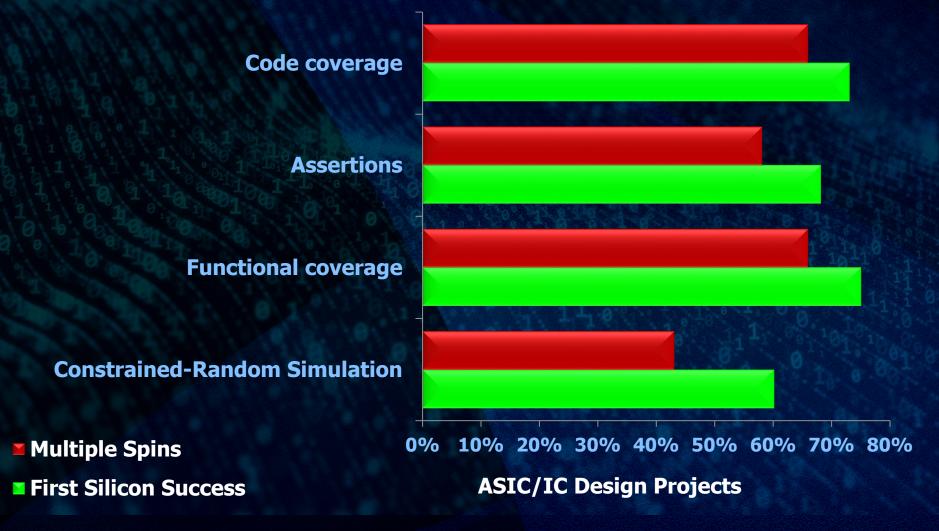

# Comparing required spins, and project maturity in adopting various verification techniques.

# CLOSING THE VERIFICATION GAP

## **Closing the Verification Productivity Gap**

## Common Methodology

### Acceleration

### Automation

### Abstraction

### Summary

- The design productivity gap has been closed through the adoption of advanced automation and reuse methodology

- What about the verification gap?

- The industry has matured its verification processes rapidly due to rising complexity

- Closing the verification productivity gap will require...

- The adoption of a common methodology, more reuse (VIP), acceleration, raising the abstraction level when possible, and automating verification to ease adoption and broaden usage

## **Additional Resources**

Paper accompany this talk in the DVCon proceedings

See my blog for additional details related to this study

— http://go.mentor.com/4Qa1S

Includes both ASIC/IC and FPGA findings

www.mentor.com