# TLM modeling and simulation for NAND Flash and Solid State Drive systems

Tim Kogel, Victor Reyes - Synopsys

#### Agenda

- Introduction to NAND Flash storage

- Solid State Drive challenges

- Virtual Prototyping

- SSD Reference VDK overview

- Summary

#### Introduction

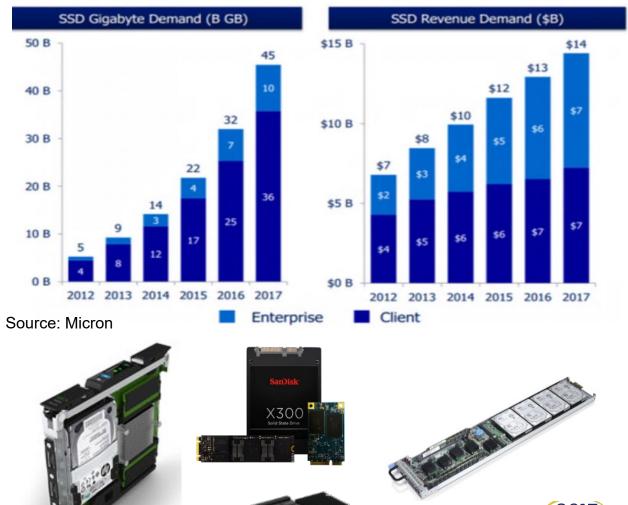

#### • Growing demand for Solid State Drives in Enterprise and Client markets

- Time to market is shortening

- NAND Flash is the technology of choice

- SSD is non-volatile storage that can be electrically erased and reprogrammed

- + High durability (vs. hard disks)

- + Fast access times (similar to DRAM)

- Finite number of writes to a block after which it wears out

SSD TAM

3

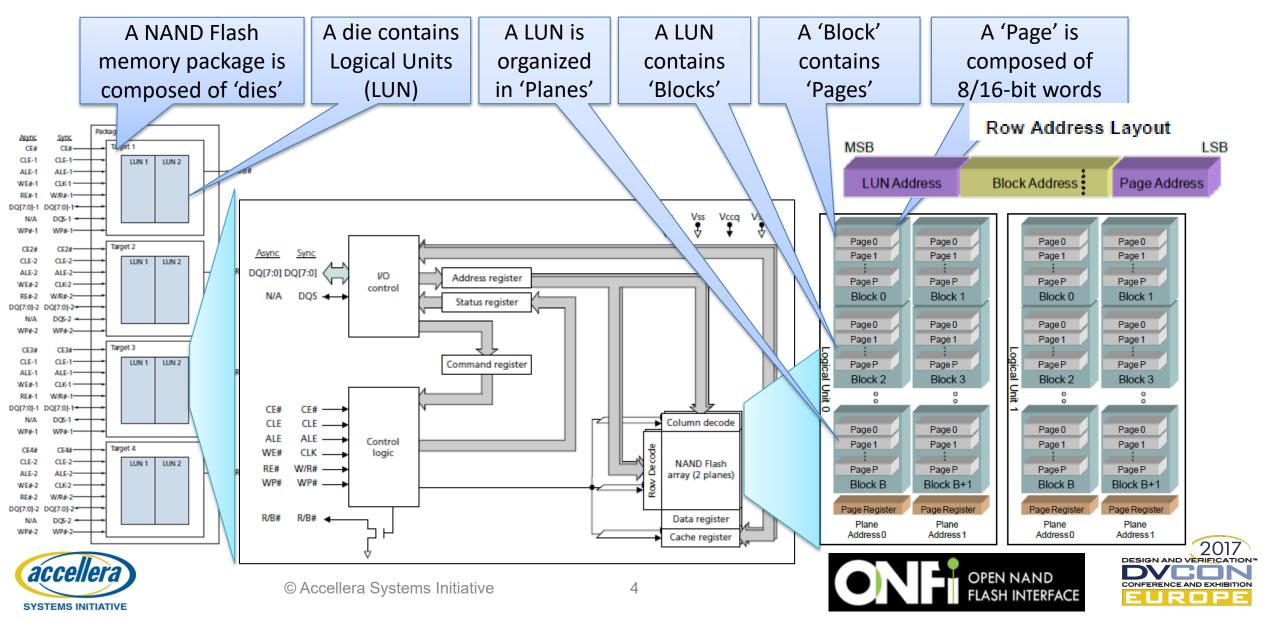

#### NAND Flash memory organization

#### **ONFI** protocol

- Open NAND Flash Interface Specification

- www.onfi.org

- 34 standardized ONFI commands (composed of cycles)

- 1 or 2 command cycles

- 0, 1, 3 or 5 address cycles

- Variable data read/write cycles

| Mandatory<br>Commands | Optional<br>Commands           |                      |  |

|-----------------------|--------------------------------|----------------------|--|

| Read                  | Multi-plane                    | Change Row Address   |  |

| Change Read Column    | Copyback Read                  | Volume Select        |  |

| Block Erase           | Change Read Column<br>Enhanced | ODT Configure        |  |

| Read Status           | Read Cache Random              | Read Unique ID       |  |

| Page Program          | Read Cache Sequential          | Get Features         |  |

| Change Write Column   | Read Cache End                 | Set Features         |  |

| Read ID               | Multi-plane                    | LUN Get Features     |  |

| Read Parameter Page   | Read Status Enhanced           | LUN Set Features     |  |

| Reset                 | Multi-plane                    | ZQ Calibration Short |  |

|                       | Page Cache Program             | ZQ Calibration Long  |  |

|                       | Copyback Program               | Reset LUN            |  |

|                       | Multi-plane                    | Synchronous Reset    |  |

|                       | Small Data Move                |                      |  |

DESIGN AND VERIEI

#### **SSD CHALLENGES**

#### NAND flash limitations

- Block erasure

- Erasure is always at a block level

- Memory wear

- NAND flash memory wears out, typically after 100k to 1M program/erase cycles

- Wear leveling balances write operations among blocks to avoid loss of capacity

- Read disturb

- Frequent reads between erases may change content of nearby cells

- The block's content must copied over to another location and original block erased

### System complexity

- Performance

- Dominated by controller latency and memory interface speeds

- Parallel NAND operations are required to scale bandwidth and hide latencies

- Fast host interfaces such PCIe (NVMe) are required

- Reliability

- Improved through ECC and overprovisioning

- Security

- Encryption

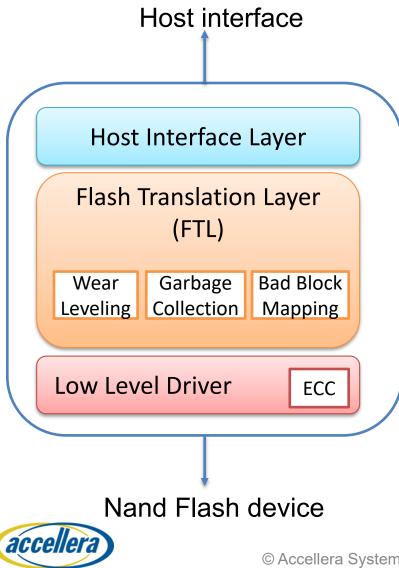

### Firmware complexity

SYSTEMS INITIATIVE

- SSD controllers are embedded processors executing ۲ firmware-level software functions

- Bad block mapping

- Read and write caching

- Encryption

- Error detection and correction via Error-correcting code (ECC)

- Garbage collection

- Read scrubbing and read disturb management

- Wear leveling

- Flexible to support evolving algorithms and interface standards •

- Optimized to provide highest performance

#### VIRTUAL PROTOTYPING

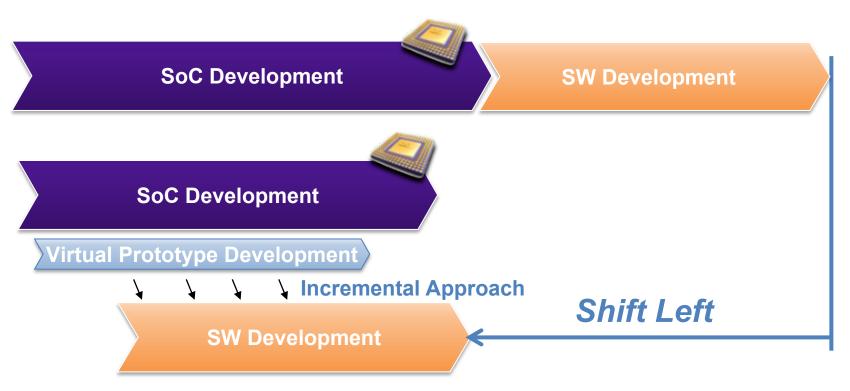

#### Why do Virtual Prototyping?

- Break Dependencies on RTL Availability (by using Transaction Level Models)

- Agile Software Development in Lock Step with Virtual Prototype Development

ESIGN AND VER

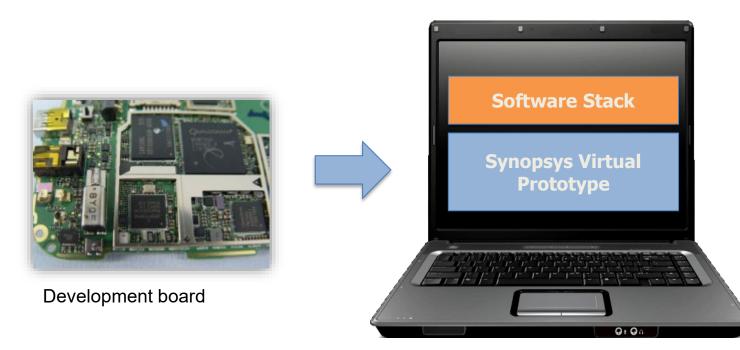

# Virtualizer Development Kits (VDKs)

- Software Development Kits that use a Virtual Prototype as a target

- VDK's are fully functional models of the system executing target code (SW / FW)

**Early Availability Easier Deployment Better SW Development Productivity** • Visibility Control and repeatability

- Fault Injection support

- Scriptable

# Benefits and opportunities for SSD

- Mitigate risk

- Try new software, architectures and components before starting implementation

- Early firmware development

- Develop, integrate and test controller firmware before silicon

- Customer enablement

- Share VDK based Software development platform with device maker

- Improve reliability

- Use fault injection capabilities to ensure robustness of firmware

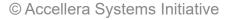

#### **SSD REFERENCE VDK OVERVIEW**

### Methodology reference kits

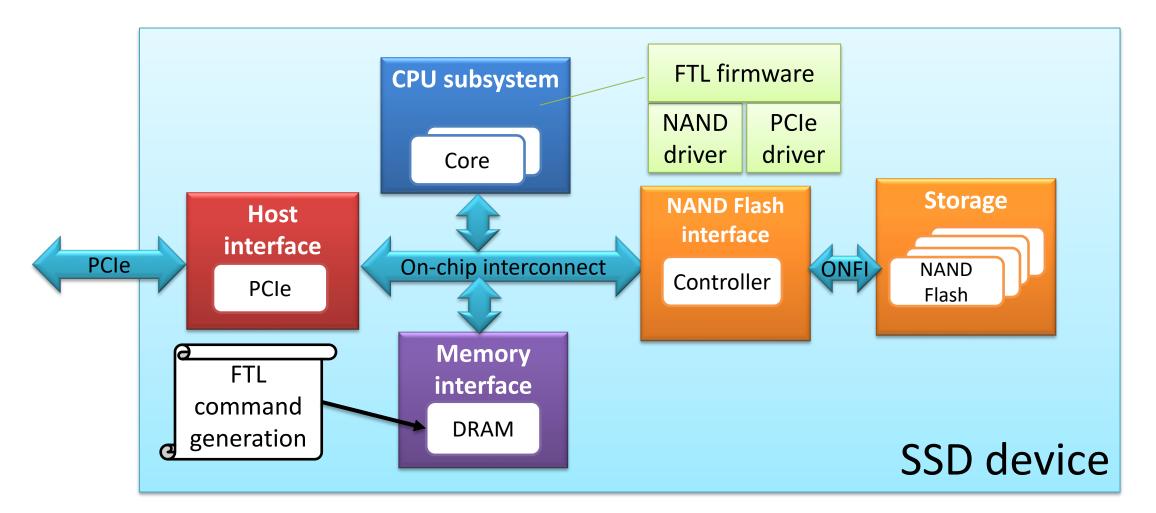

#### SSD Reference VDK Block Diagram

2017

DESIGN AND VERIFICATION

ONFERENCE AND EXHIBITION

### SSD Reference VDK Design

- Virtualizer Studio based VDK

- Easy reconfiguration of CPU subsystem

- Any number and types of cores

- Automatic connectivity

- Largest library of TLM models for interface IP

- DesignWare PCIe, USB3, SATA

- ONFI compliant configurable TLM models

- NAND Flash controller, including software driver

- NAND Flash memories with configurable number of LUN, planes, blocks, pages, etc.

- Script based FTL command generation with Python or TCL

#### SSD Reference VDK in Virtualizer Studio

| VDK System Browser Build: success                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                 |                                                                 |          |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------|--|--|--|--|--|

| Design Hierarchy 1 a to TestPlatformONFI                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                 |                                                                 |          |  |  |  |  |  |

| C C 🕈 ଟ 🛛                                                                                                                                                                                                                                   | 🗱 SpecFlow 📄 VDK Settings 🖶 VDK Packaging 🛋 Librar                                                                                                                                                                                                                                                                                                                              | ry Manager 🛿 🛱 Interfaces 🗱 Parameters 🍥 Docum                  | entation |  |  |  |  |  |

| type filter text  TestPlatformONFI  SVSREGS SVSCLK SYSRST RAM DRAM DRAM DRAM DRAM Properiphs Periphs Periphs Periphs Periphs NandFlashController NandFlashController NandTarget_0 NandTarget_1 NandTarget_2 NandTarget_3 HostIF PCIe_2_0_EP | It SpecFlow  WDK Settings  VDK Packaging  Library Tables  Itype filter text ✓ Image: CCL.PVBUS_M - /CPU_SS/CPU/CCI MandFlashController.axi_initiator - /NandFlashS PCIe_2_0_EP.BusMaster - /HostIF/PCIe_2_0_EP ✓ Interrupt Table Interrupt Table GIC.IRQS - /CPU_SS/CPU/GIC ✓ Reset Tree SYSRST.RST - /SYSRST ✓ Clock Tree SYSCLK.CLK - /SYSCLK ✓ ONFI Network Image: ONFI_NW_1 | Add New Entry  No table selected  Name:  Start:  Start:  Start: |          |  |  |  |  |  |

| IO_PCIe_2_0_RC_stub<br>Extend design using SpecFlow                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                 |                                                                 |          |  |  |  |  |  |

20

DESIGN AND VERIFIC

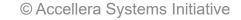

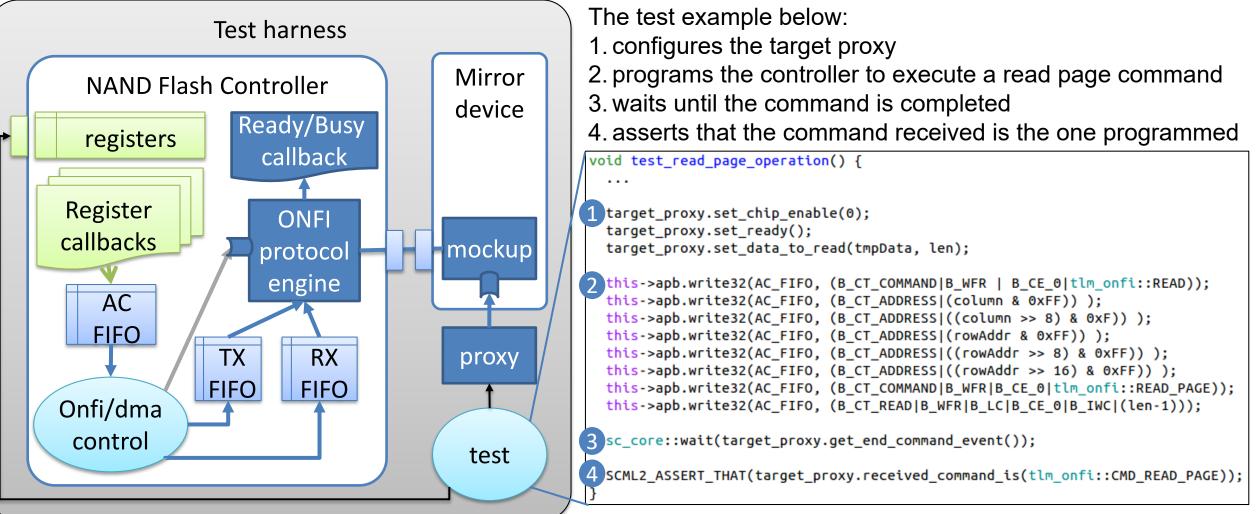

# NAND Flash Modeling Approach

- Separate Controller from Target devices

- Explicitly model the NAND Flash interface at the TLM level

- Provide reusable building blocks that encapsulate the NAND Flash protocol details

- Protocol engine(s) can be share across models

- Verify once, reuse many times

- Include best practices for simulation speed using callbacks and analysis instrumentation

- Include solution for model unit-testing

- Based on reusable objects and TLM Creator unit testing framework

- File based implementation to deal with high density storage

- Encapsulated as a reusable 'Logical Unit' object with debug and analysis instrumentation

- Highly configurable

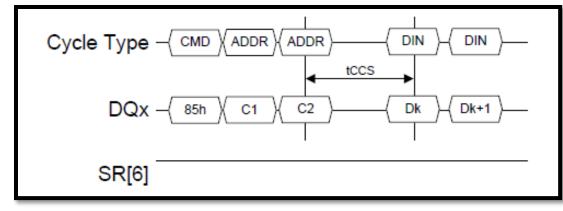

### **ONFI** protocol TLM Modeling

Protocol engine object allows different levels of timing and accuracy on the interface:

- Single transfer with overall time (fastest)

- Separate transfers for command, address and data (more accurate)

Protocol engine object decodes ONFI commands and triggers callbacks Logical Unit object models the storage

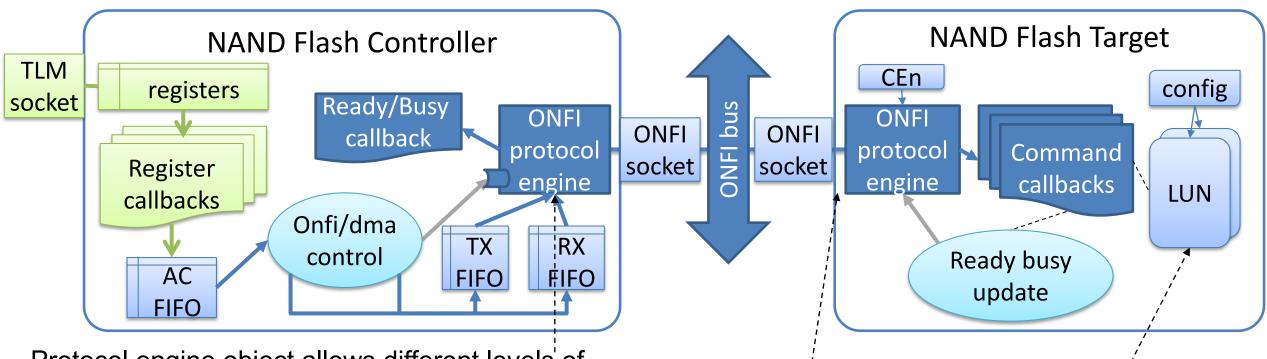

## Unit-Testing infrastructure

- Automated execution and reporting

- SystemC aware assertions

SCML2\_ASSERT\_THAT (condition);

SCML2\_ASSERT\_THAT(socket.read32(ADDRESS).equals(value); SCML2\_ASSERT\_THAT(pin.equals(value)); SCML2\_ASSERT\_THAT(pin.equals(value).after\_ms(amount)); SCML2\_ASSERT\_THAT(pin.equals(value).after\_ns(amount)); SCML2\_ASSERT\_THAT(socket.read32(ADDR).equals(val).after\_cycles(amount, CLK)); SCML2\_ASSERT\_THAT(socket.read32(ADDR).equals(val).within\_ms(amount)); SCML2\_ASSERT\_THAT(socket.read32(ADDR).equals(val).within\_ms(amount));

DESIGN AND VERIFICATION\*\*

### **ONFI Unit-Testing example**

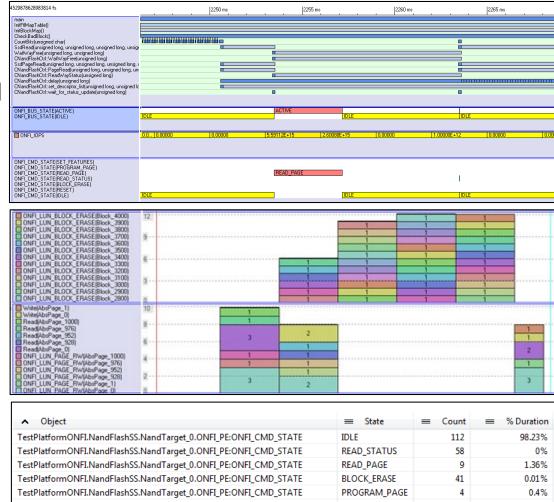

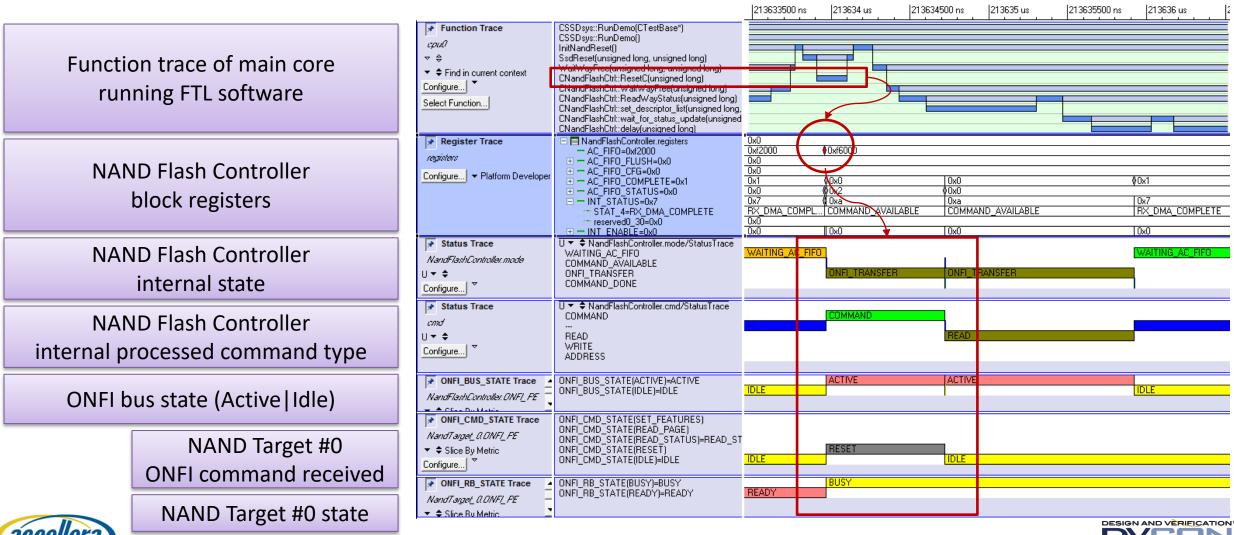

# SSD Reference VDK Capabilities

- Execute, debug and test full SSD software stacks

- Debug with full visibility and correlation on software and hardware events

- Automated testing for a large number of scenarios

- Analyze software statistics and utilization

- Analyze ONFI metrics

- Utilization of the NAND Flash controller

- Number and type of ONFI commands per memory

- Per block, number of erase operation

- Per page, number of read and program operation

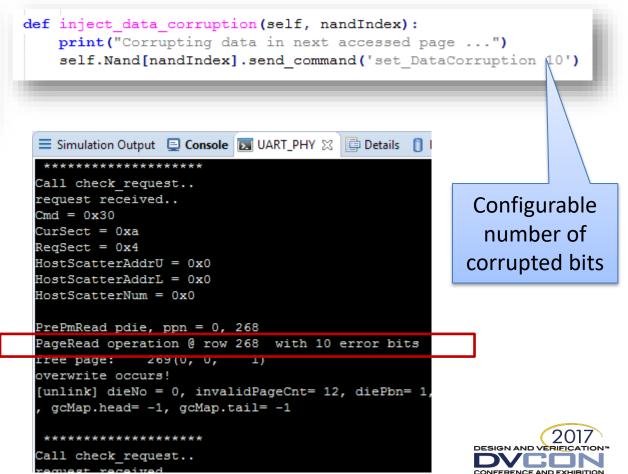

- Configure and inject errors

- Factory defect mapping and dynamic data corruption

2017

DESIGN AND VERIFICATION

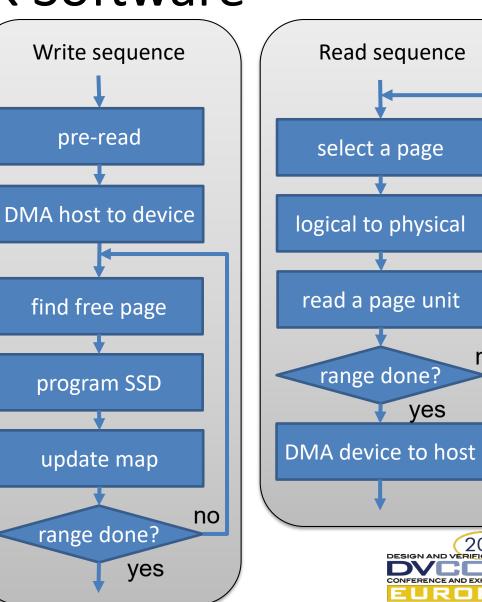

# SSD Reference VDK Software

- SW based on the "Cosmos OpenSSD platform"

- <u>http://www.openssd-project.org</u>

- Page-level mapping

- Emulates the functionality of an HDD

- Every logical page is mapped to a physical page

- Redirect each write request from the host to an empty area already erased

- Garbage collection

- Reclaim new free blocks for future write requests

- Greedy algorithm: victim block is selected to minimize search time

- NAND Controller driver

- Provides basic commands: block erase, read page, program page, read status, etc.

- Provide data corruption fault checking

no

# Hardware / Software analysis

Scenario: NAND Flash Controller driver performing a reset command

© Accellera Systems Initiative

CONFERENCE AND EXHIBITION

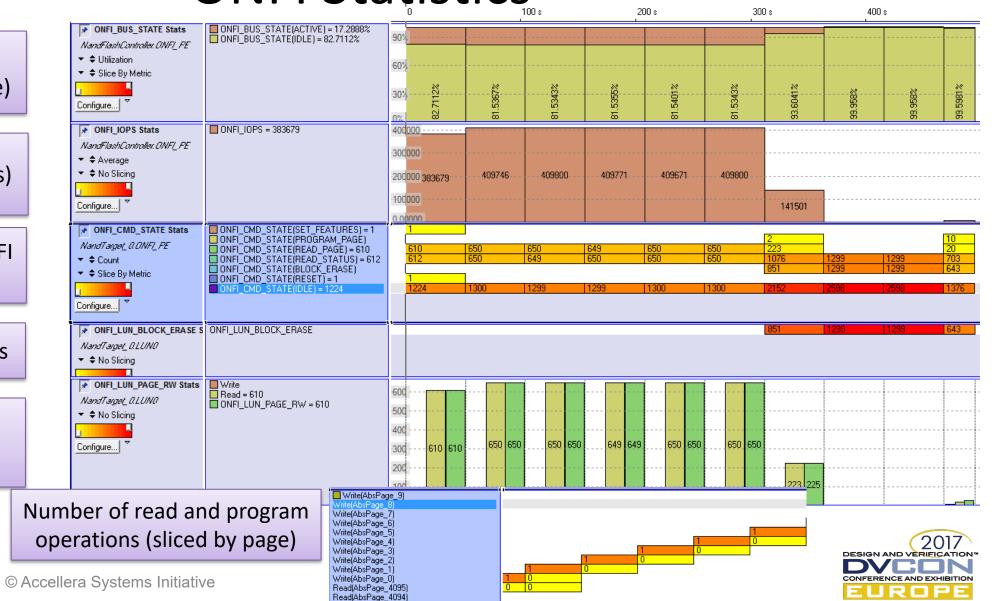

#### **ONFI Statistics**

ONFI bus utilization in percentage (Active / Idle)

IOPS (cycles per seconds)

Number and type of ONFI commands per target

Number of erased blocks

Number of read and program operations

# Factory Defects and Error injection

#### Factory defect mapping (scriptable)

| <pre>def set_factory_settings(self):     print("Initializing Factory Settings")</pre> |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| <pre>for i in range(len(self.Nand)):</pre>                                            |  |  |  |  |  |  |  |

| <pre>self.Nand[i].send command('set BadBlockMark 0')</pre>                            |  |  |  |  |  |  |  |

|                                                                                       |  |  |  |  |  |  |  |

| <pre>self.Nand[i].send_command('set_FactoryInvalidBlock 0 50')</pre>                  |  |  |  |  |  |  |  |

| <pre>self.Nand[i].send_command('set_FactoryInvalidBlock 0 367')</pre>                 |  |  |  |  |  |  |  |

| <pre>self.Nand[i].send_command('set_FactoryInvalidBlock 0 1112')</pre>                |  |  |  |  |  |  |  |

| <pre>self.Nand[i].send command('set FactoryInvalidBlock 0 4091')</pre>                |  |  |  |  |  |  |  |

|                                                                                       |  |  |  |  |  |  |  |

| 🚍 Simulation Output 📮 Console 📑 Details 🗻 Memory 🔽 UART_PHY 🔀                         |  |  |  |  |  |  |  |

|                                                                                       |  |  |  |  |  |  |  |

| Running Test: CorePeripherals : SSD_system : RunDemo                                  |  |  |  |  |  |  |  |

| PAGE_MAP_ADDR : 8c000000                                                              |  |  |  |  |  |  |  |

| [ ssd page map initialized. ]                                                         |  |  |  |  |  |  |  |

| [ checking bad blocks. ]                                                              |  |  |  |  |  |  |  |

| Bad block is detected on: Ch 0 Way 0 Block 50                                         |  |  |  |  |  |  |  |

| Bad block is detected on: Ch 0 Way 1 Block 50                                         |  |  |  |  |  |  |  |

| Bad block is detected on: Ch 0 Way 2 Block 50                                         |  |  |  |  |  |  |  |

| Bad block is detected on: Ch 0 Way 3 Block 50                                         |  |  |  |  |  |  |  |

| Bad block is detected on: Ch 0 Way 0 Block 367                                        |  |  |  |  |  |  |  |

| Bad block is detected on: Ch 0 Way 1 Block 367                                        |  |  |  |  |  |  |  |

| Bad block is detected on: Ch 0 Way 2 Block 367                                        |  |  |  |  |  |  |  |

| Bad block is detected on: Ch 0 Way 3 Block 367                                        |  |  |  |  |  |  |  |

| Bad block is detected on: Ch 0 Way 0 Block 1112                                       |  |  |  |  |  |  |  |

| Bad block is detected on: Ch 0 Way 1 Block 1112                                       |  |  |  |  |  |  |  |

| Bad block is detected on: Ch 0 Way 2 Block 1112                                       |  |  |  |  |  |  |  |

| Bad block is detected on: Ch 0 Way 3 Block 1112                                       |  |  |  |  |  |  |  |

| Bad block is detected on: Ch 0 Way 0 Block 4091                                       |  |  |  |  |  |  |  |

| Bad block is detected on: Ch 0 Way 1 Block 4091                                       |  |  |  |  |  |  |  |

| Bad block is detected on: Ch 0 Way 2 Block 4091                                       |  |  |  |  |  |  |  |

| Bad block is detected on: Ch 0 Way 3 Block 4091                                       |  |  |  |  |  |  |  |

| [ Bad block Marks are saved. ]                                                        |  |  |  |  |  |  |  |

| [ Erase all sdd blocks. ]                                                             |  |  |  |  |  |  |  |

|                                                                                       |  |  |  |  |  |  |  |

#### Inject data corruption (scriptable)

27

# Error injection analysis

|                                                                                                                    | _                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 495295 r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ns                                 | 495300 ms                                                              |

|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------------------------------------------|

| Software routines checks<br>and clears the ECC fields<br>(assuming data integrity is<br>recovered by ECC hardware) | <ul> <li>Function Trace</li> <li>cpcd2</li> <li>♦     <li>Find in current context     <li>Configure</li> <li>Select Function</li> </li></li></ul> | PrePmRead[_HOST_CMD*, unsigned long]<br>SsdRead(unsigned long, unsigned long, unsigned<br>WaitWayFree(unsigned long, unsigned long)<br>CNandFlashCtrt::WaitWayFree(unsigned long)<br>SsdPageRead(unsigned long, unsigned long, unsigned long, unsigned long, unsigned long, unsigned long, unsigned long)<br>CNandFlashCtrt::PageRead(unsigned long, unsigned long)<br>CNandFlashCtrt::ReadWayStatus(unsigned long)<br>CNandFlashCtrt::deav(unsigned long)<br>CNandFlashCtrt::deav(unsigned long)<br>CNandFlashCtrt::set_descriptor_list(unsigned long)<br>CNandFlashCtrt::set_descriptor_list(unsigned long)<br>CNandFlashCtrt::checkECC()<br>CNandFlashCtrt::clearECC() |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                    |                                                                        |

| Error is exposed to the<br>Software through the<br>controller registers<br>(ECC_ERROR_LAST)                        | Image: Register Trace       nagrintary       Configure       ▼ Platform Developer                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x7         \$0xa         \$0x7           0x0         \$0x0         0x0           0x0         0x0         0x0           0x0         0x0         0x1           0x0         0x14         0x3f           0xff         0xff         0xff           0xff         0x0         0x14           0x9f         0xff         0xff           0xff         0x0         0x0           0xff         0x0         0x0           0x0         0x0         0x0           0x0         0x0         0x0           0x0         0x0         0x0 |                                    | 0x0<br>0x0                                                             |

| Next Read Page operation<br>triggers ECC error<br>(detected by the NAND<br>Flash Controller)                       | ▼ ♦ Slice By Metric                                                                                                                               | ONFI_CMD_STATE(SET_FEATURES)=SET_FE/<br>ONFI_CMD_STATE(PROGRAM_PAGE)=PROGF<br>ONFI_CMD_STATE(READ_PAGE)=READ_PAGE<br>ONFI_CMD_STATE(READ_STATUS)=READ_ST<br>ONFI_CMD_STATE(BLOCK_ERASE)=BLOCK_EI<br>ONFI_CMD_STATE(RESET)=RESET<br>ONFI_CMD_STATE(IDLE)=IDLE                                                                                                                                                                                                                                                                                                                                                                                                              | READ_PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                    | I<br>I<br>IDLE                                                         |

| SYSTEMS INITIATIVE                                                                                                 | ccellera Systems In                                                                                                                               | itiative 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ta corruption on arget (scripting) | 2017<br>DESIGN AND VERIFICATION<br>CONFERENCE AND EXHIBITION<br>EUROPE |

#### **SUMMARY**

# Summary

- SSD market is growing rapidly

- Use Virtual Prototyping to manage SSD development risks and challenges

- Software complexity

- ightarrow start firmware development months before hardware

- Time to market  $\rightarrow$  enable customers early across the supply chain

- Performance optimization  $\rightarrow$  analyze hardware/software interactions and trend

- Data reliability  $\rightarrow$  validate many (error) scenarios with regression testing

- The SSD Reference VDK is the best starting point to engage!

- Ready out of the box with configurable models and example software

- Easy to customize and match an specific customer design

- Great analysis and scripting capabilities

#### References

- "Overview of the NAND Flash High-Speed Interfacing and Controller Architecture", Nina Mitiukhina, IEE 5008 Memory Systems Final Report 0060805

- "Open NAND Flash Interface Specification, revision 4.0", 2014, <u>www.onfi.org</u>

- "03 NAND Basics: Understanding the Technology Behind Your SSD", <u>http://www.samsung.com/it/business-images/resource/white-</u> <u>paper/2014/01/Samsung SSD WhitePaper Final PDF 130724d-0.pdf</u>

- "NAND Flash 101: An Introduction to NAND Flash and How to Desing It In to Your Next Product", TN-29-19, <u>www.micron.com</u>

- "A Comparative Study of Flash Storage Technologies for Embedded Devices", 2015, <u>www.datalight.com</u>

# Thank You! Questions?

tim.kogel@synopsys.com

victor.reyes@synopsys.com