### Introduction

Setting up an effective UVM-based verification environment can be challenging due to various reasons. This paper discusses an approach that can be used to improve controllability and scalability of tests while maximizing the effect of constrained randomness and reusability in any complex UVM-based verification environment. This paper also discusses the advantages and challenges of using this approach in the verification of an xHCI-based USB 3.0 host controller

The proposed approach is to have multiple runtime switches, termed as "verif\_modes", corresponding to every design feature. Each verif\_mode enables a sequence or a set of sequences to create the scenarios required to verify the design feature and also optionally enables checks related to the feature. The verification environment uses verif\_modes to hierarchichally manage the real work sequences. The verif\_modes can be enabled to test directed scenarios or concurrently with other verif\_modes to create interleaved constrained random scenarios

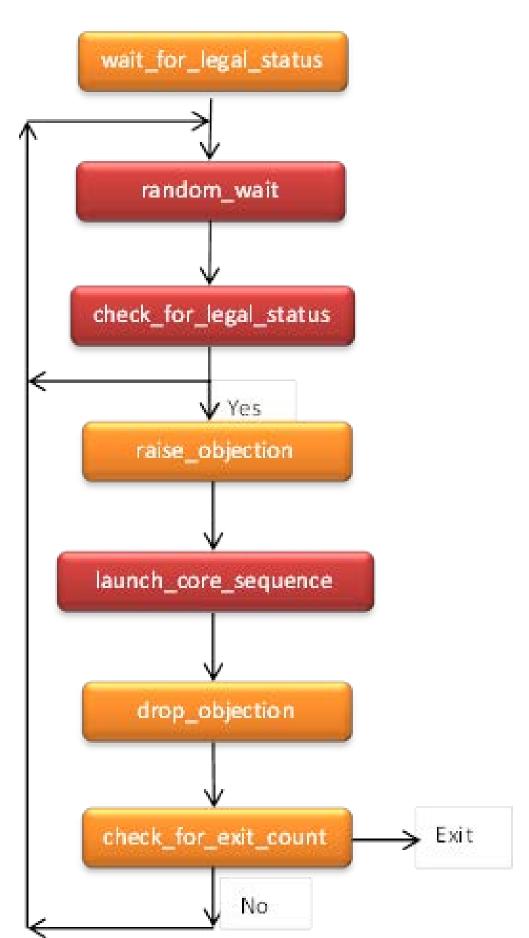

#### General VERIF\_MODE Flow Diagram

The core\_sequence, which exercises the minimal iteration of the identified scenario, needs to be implemented. The verif\_mode sequence following the above generic flow diagram needs to be implemented. Using bench\_status from the mointor, every verif\_mode sequence waits for some legal state during which it can exercise the scenario. The sequence waits for a random time that helps in creating corner cases. The sequence then again checks for a legal condition for exercising the verif\_mode. The verif\_mode sequence then launches the core\_sequence. The verif\_mode sequence could, optionally, raise/drop an objection before/after running the core\_sequence. After running the core\_sequence, the verif\_mode sequence could either repeat the iteration depending on the intended number of times the verif\_mode needs to be exercised in the test.

# Taming a Complex UVM Environment Manjunath Shetty, Ramamurthy Gorti **Broadcom Corporation**

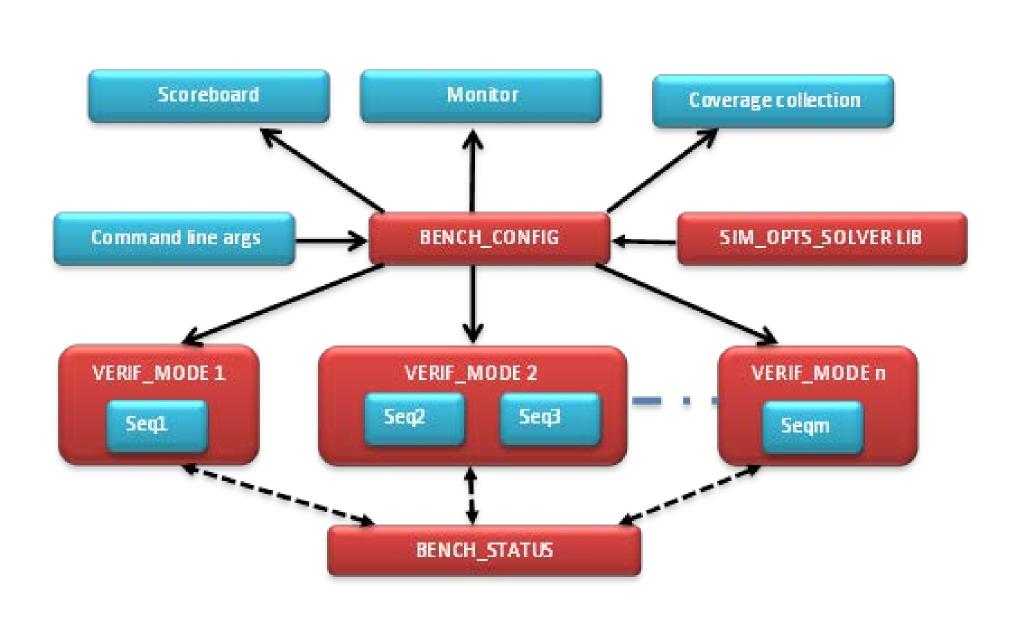

# Verification Environment Block Diagram using VERIF\_MODES

A singleton class called "bench\_config" is used to control verif\_modes. The bench\_config class provides a centralized way to control all of the simulation options and their usage throughout the environment. Each verif\_mode in bench\_config class can be configured using command line options or using "sim\_opts\_solver" class. The uvm\_cmdline\_processor class can be used to set each verif\_mode to desired values from simulation options provided by the user. For an automated way of controlling the verif\_modes, the "sim\_opts\_solver" class is used. The sim\_opts\_solver class consists of constraints to configure all the verif\_modes in different combinations to create interesting legal corner cases and to take care of any spatial and/or temporal dependencies. One can have a library of such sim\_opts\_solvers targeting single/multiple features in the design while enabling or disabling other background verif\_modes. The sim\_opts\_solver also provides a way to deal with mutually exclusive and dependent verif\_modes

Any specific verif\_mode could also be set from simulation options using uvm\_cmdline\_processor. The verif\_mode configured using command line option takes precedence over randomized value from sim\_opts\_solver class. This also provides the option of disabling scenarios when needed, either due to a known design issue or when a verif\_mode sequence itself has issues

Above figure also shows the usage of the "bench\_status" class. This is a data structure maintained in monitor and is used by all verif\_mode sequences to check and update the status of the bench and DUT at any point in time during the run\_phase of the test. Each verif\_mode uses this during check\_for\_legal\_status and also updates it according the verif\_mode during the running of core\_sequence

Monitor can optionally maintain a data structure for each verif\_mode indicating the number of times the expected scenario was hit. This can be used during the check\_phase() of the test to make sure all the intended scenarios were hit during the test, at least once. It can also be used during the report\_phase() to print statistics of various verif\_modes enabled in the test and the number of times each scenario was hit during the test

# Template use cases of VERIF\_MODES:

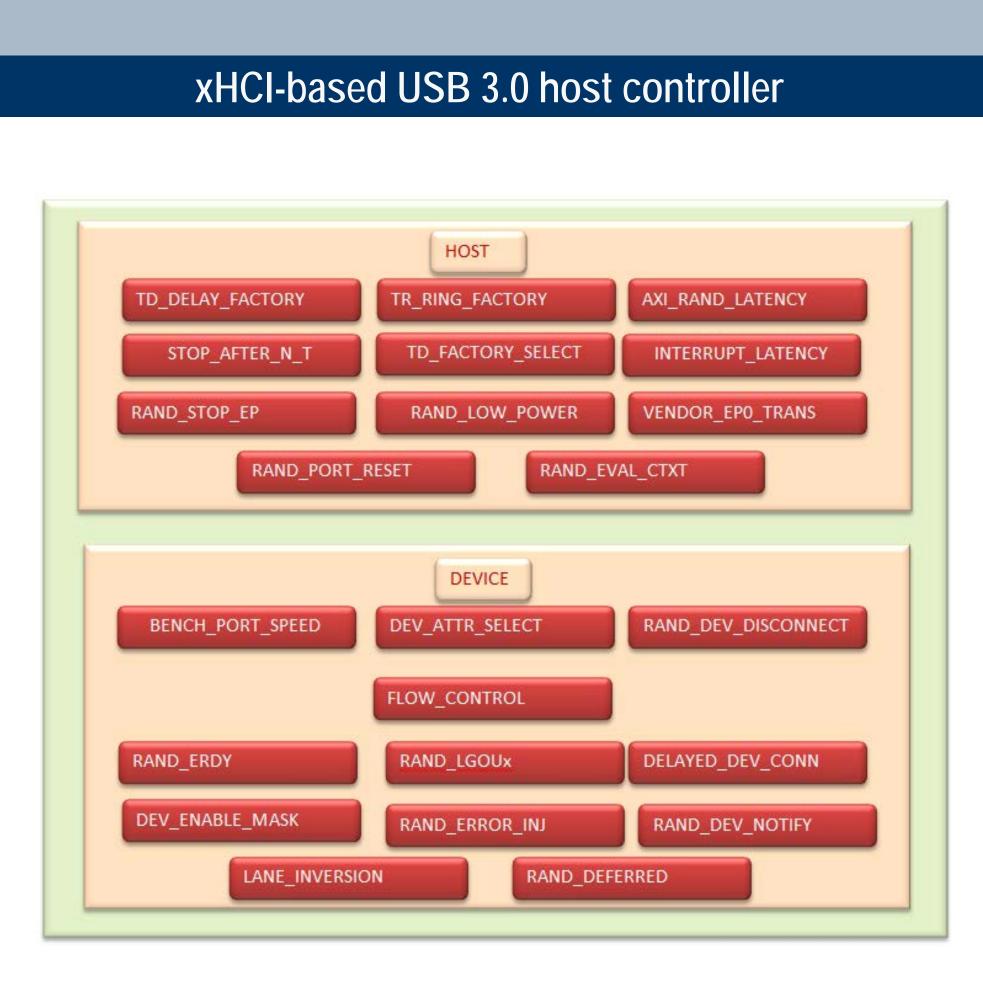

**General verif\_modes**: These are the verif\_modes that are needed for all tests. Most of these are used to pass a particular runtime argument to the bench. **Controlling the speed**: BENCH\_PORT\_SPEED and RANDOM\_SPEED\_SELECT\_INCLUDE Controlling the device model configuration: DEVICE\_ATTRIBUTE\_LIBRARY\_SELECT Controlling the quantity of traffic: DMVC\_STOP\_AFTER\_N\_TDS\_PER\_EP. **Controlling the type of traffic:** TD\_FACTORY, TD\_FACTORY\_LIBRARY\_SELECT, ENQUEUE\_TD\_DELAY\_FACTORY and TR\_RING\_FACTORY\_RANDOM\_SELECT Controlling external latencies: INT\_LATENCY\_RANDOM\_SELECT and AXI\_SLAVE\_CFG\_RANDOM\_SELECT

**Special features verif\_modes**: These are the verif\_modes identified from the specification targeting a specific scenario and needs a sequence implemented as per Figure 1. **Device disconnect**: NUM\_DISCONNECT\_CONNECT.

**Port Reset**: NUM\_PORT\_RESET and PORT\_RESET\_TYPE **Stopping the endpoints**: ISSUE\_RAND\_STOP\_EP\_CMD. Flow control on the endpoints: FLOW\_CONTROL\_BUFFER.

Low power modes: ENABLE\_FAST\_U1\_ENTRY and ENABLE\_FAST\_U2\_ENTRY.

| Backg<br>identif<br>the tes<br>mostly<br>simple<br>power<br>De     |

|--------------------------------------------------------------------|

| De<br>De                                                           |

| Ро                                                                 |

| Ve                                                                 |

| Со                                                                 |

| Err                                                                |

| LN<br>De                                                           |

| Ev                                                                 |

| La<br>De                                                           |

|                                                                    |

| The pr<br>xHCI-k<br>increm<br>protoc<br>has pr<br>over 3<br>and we |

|                                                                    |

| Manj<br>Sr St<br>shett                                             |

**Ramamurthy Gorti** Sr Manager rgorti@broadcom.com

ground activity verif\_modes: These verif\_modes are ified from the specification to create random activities in est to help create legal corner-case scenarios. These are y light on sequence implementation and exercise e design features, but when enabled together, are rful in creating corner cases. evice issuing ERDYs: ENABLE\_RAND\_ERDY and ISSUE\_MULTI\_DUMMY\_ERDY evice issuing LGO\_Ux:. RAND\_DEVICE\_TX\_LGOU1 and RAND\_DEVICE\_TX\_LGOU2. elayed device connection: RAND\_DELAYED\_DEVICE\_CONNECT. orts with no device connected: DEVICE\_ENABLE\_MASK. endor Endpoint0 transfers: ENABLE\_BACKGROUND\_EP0\_TRAFFIC ontrol transfers with address=0:. GET\_DESC\_BEFORE\_ADDR\_DEV. ror injection: ENABLE\_RANDOM\_ERROR\_INJECTION. **MP packets:** RAND\_PORTPM\_WRITE\_BACK evice notification packets: ISSUE\_RAND\_DEV\_NOTIFY valuate context command: ISSUE\_RAND\_EVALUATE\_CONTEXT ane Inversion: INVERT\_LANE\_POLARITY eferred packets: ENABLE\_DEFERRED\_MODE

### Conclusion

roposed approach has been very effective in verifying an based Host Controller. It facilitated modular verification of nental design/test-bench enhancements such as Streams col, Broadcom PHY, and USB2.0 support. This approach roven to be of very high quality and has managed to catch 300 RTL and corner cases, many of which were obscure ould not easily have been hit with a simpler test bench

## Contact information

junath Shetty taff Engineer shetty@broadcom.com