## SystemRDL to PSS BASIC TO PRO

Anupam Bakshi

Amanjyot Kaur

# Agenda

- Introduction

- Components

- Field

- Register

- Register File

- Address Map

- Memory

- Signals

- Address Allocation

- Enumerations

- Parameters

- Structures

- Property Assignment

- Special Register

- Interrupt

- Counters

- Verification Constructs

- HDL PATH

- Constraint

- Structural Testing

- Perl preprocessor

- SystemRDL Usage Methodology

- SystemRDL Editor

- Introduction to Portable Standard Stimulus (PSS)

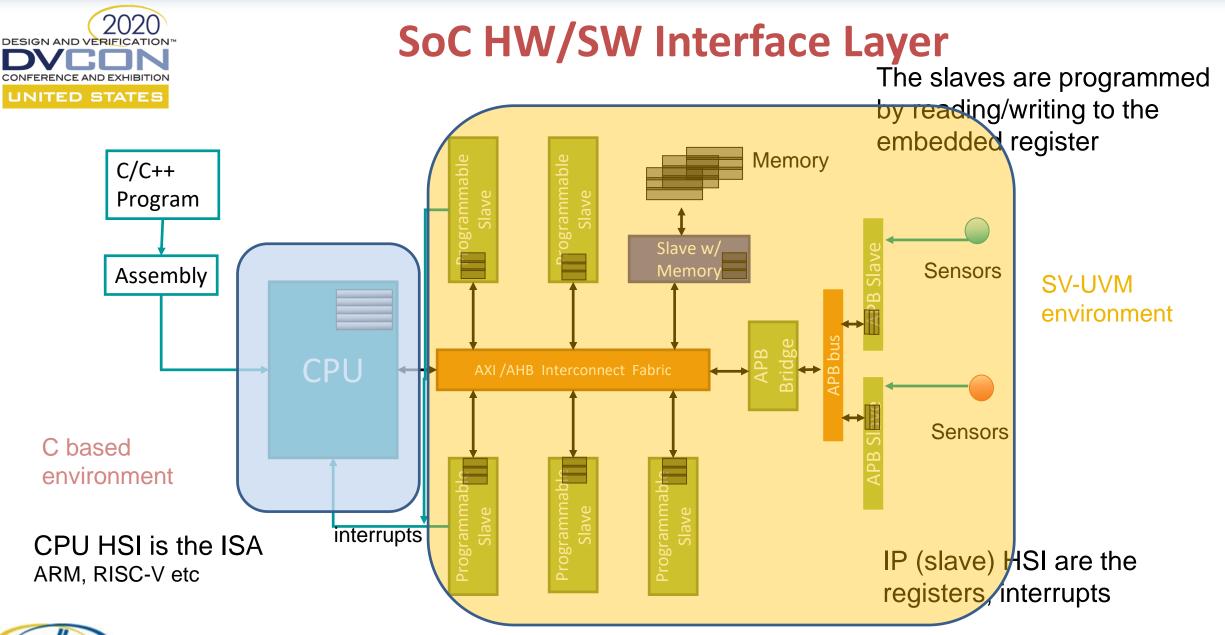

- SoC HW/SW Interface Layer (HSI)

- Example Sequence with HSI

- Introduction to Sequences

- Problems faced with sequences

- Proposed Solution

- ISS+PSS tool flow example: WISHBONE DMA

- Conclusion

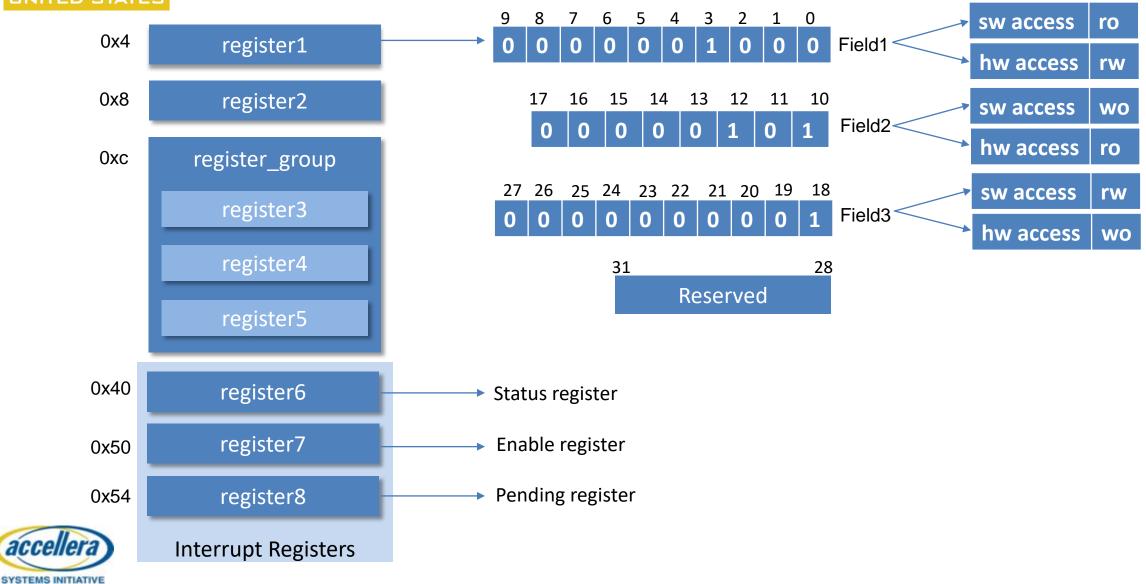

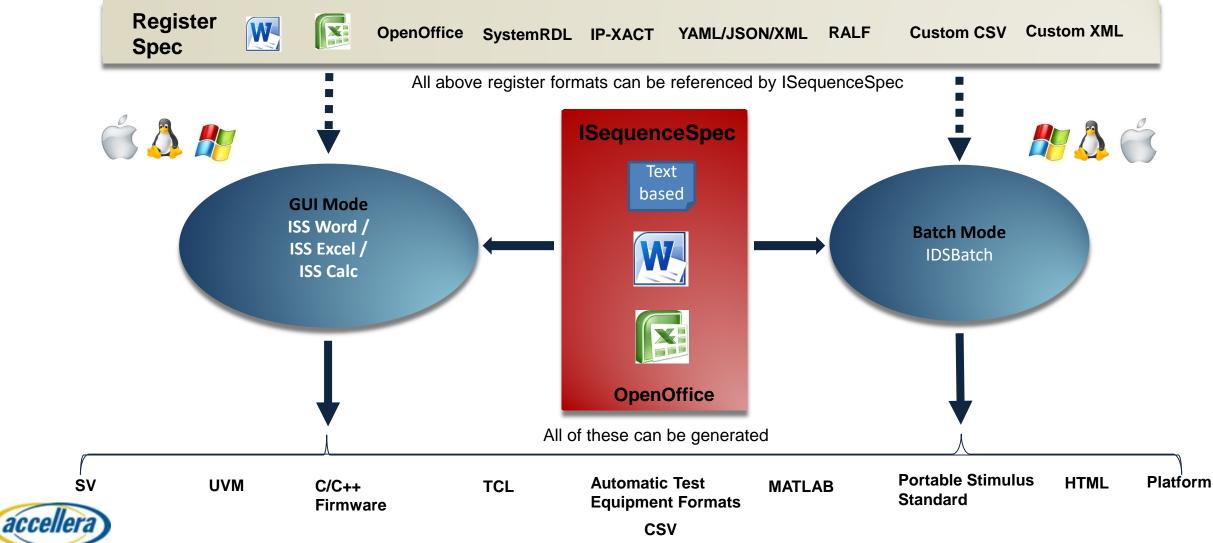

Register map in **SystemRDL**

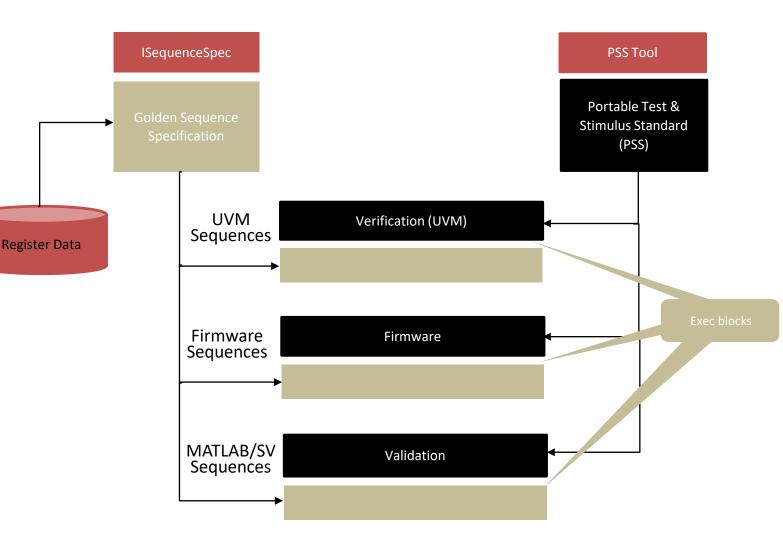

## **SystemRDL to PSS**

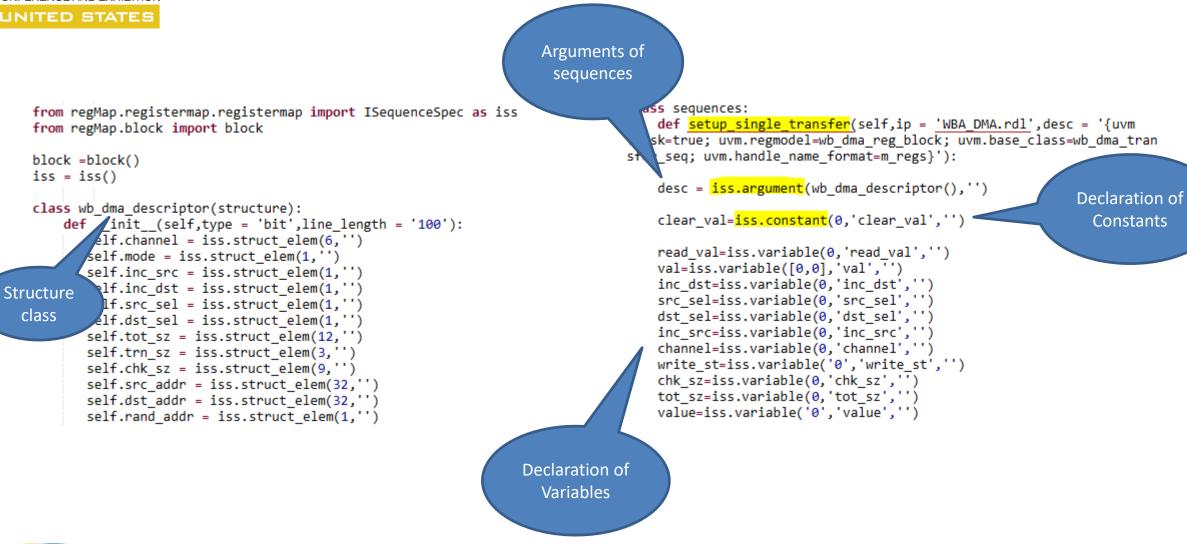

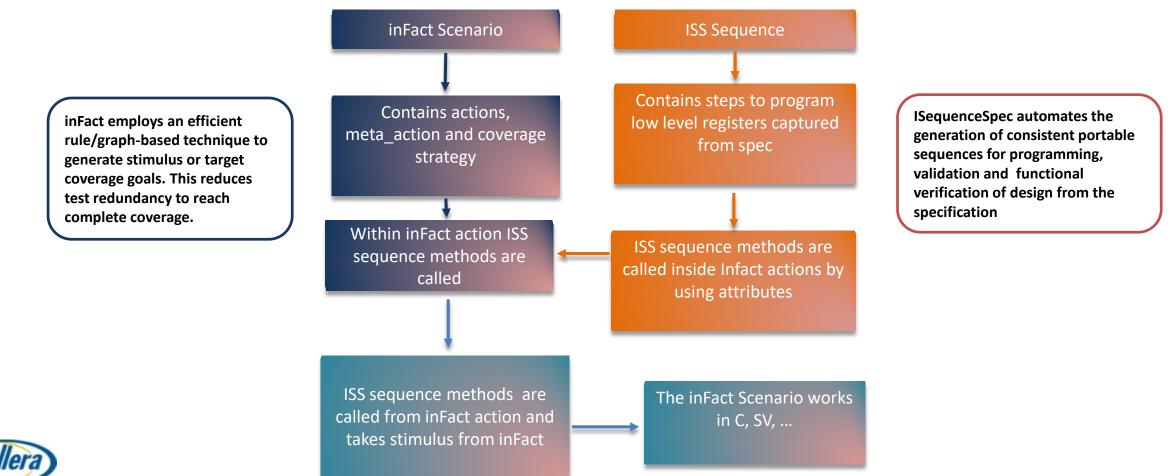

# ISequence

Uses register map to write sequences on it

Generate implementation level sequences on various platforms

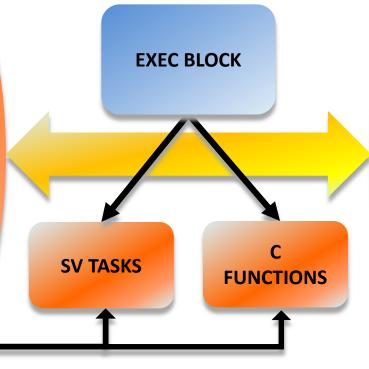

Generated exec blocks can be directly used in PSS

## **PSS Tool**

Create high-level scenarios

Low-level sequences handled by exec blocks

Synthesize the tests/scenarios

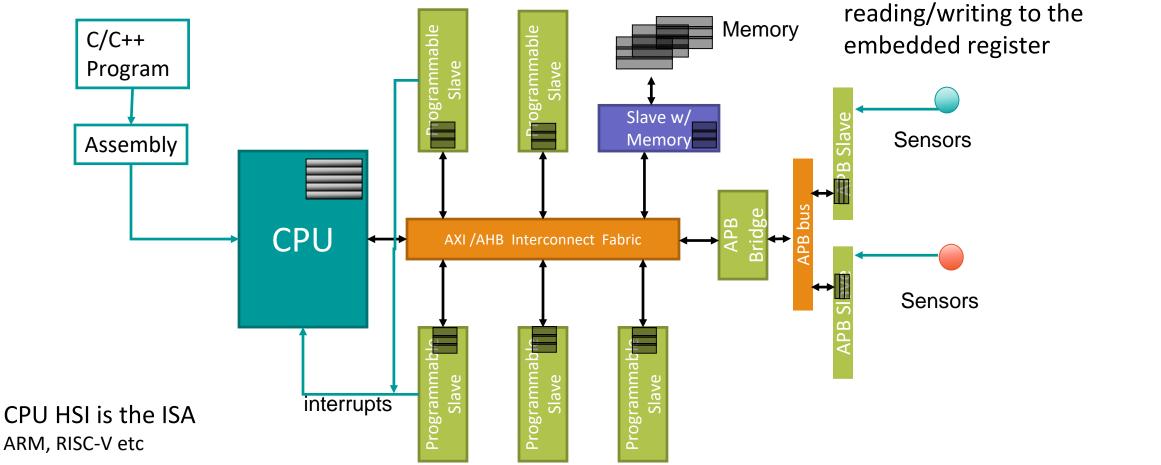

# **CPU & IP Hardware Software Interface**

The slaves are programmed by

# SystemRDL Importance and History

- An embedded system consists of Hardware and Software components.

- SystemRDL is a textual representation of Hardware-Software interface consisting of addressable registers, interrupts, counters etc.

- History

- Created at Cisco, released as Accellera 1.0 standard.

- Version 2.0 released in Jan 2018

- Added Verification constructs, parameterization, data types etc.

- Reference:

https://www.accellera.org/images/downloads/standards/systemrdl/SystemRDL 2.0 Jan2018.pdf

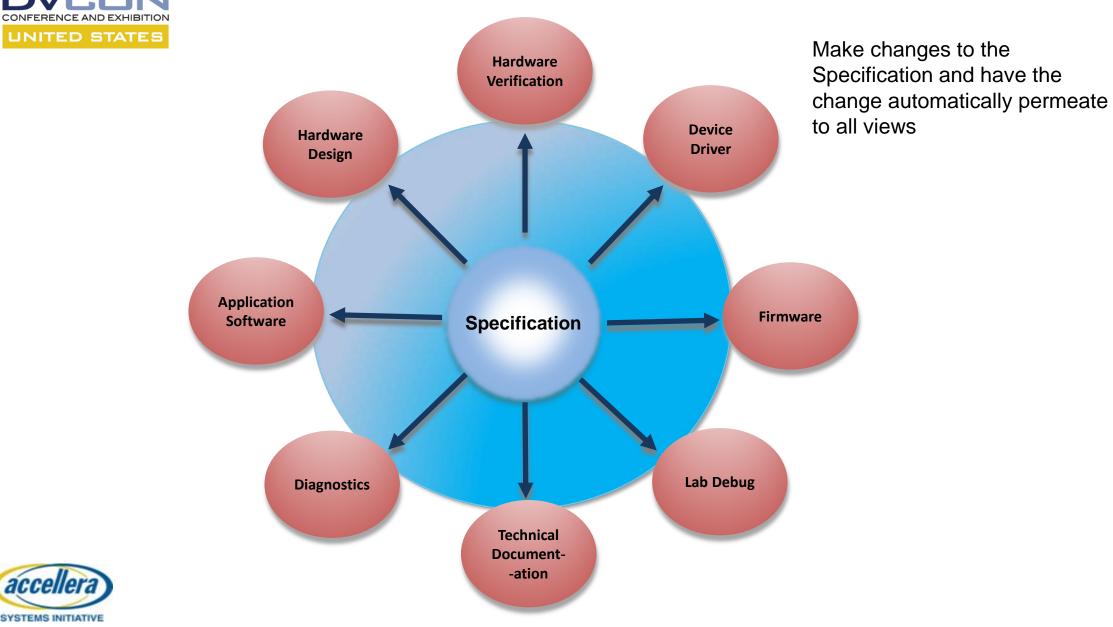

- Support specification centric flow, automatically generate

- RTL bus interface

- Verification model

- C header and API

Documentation

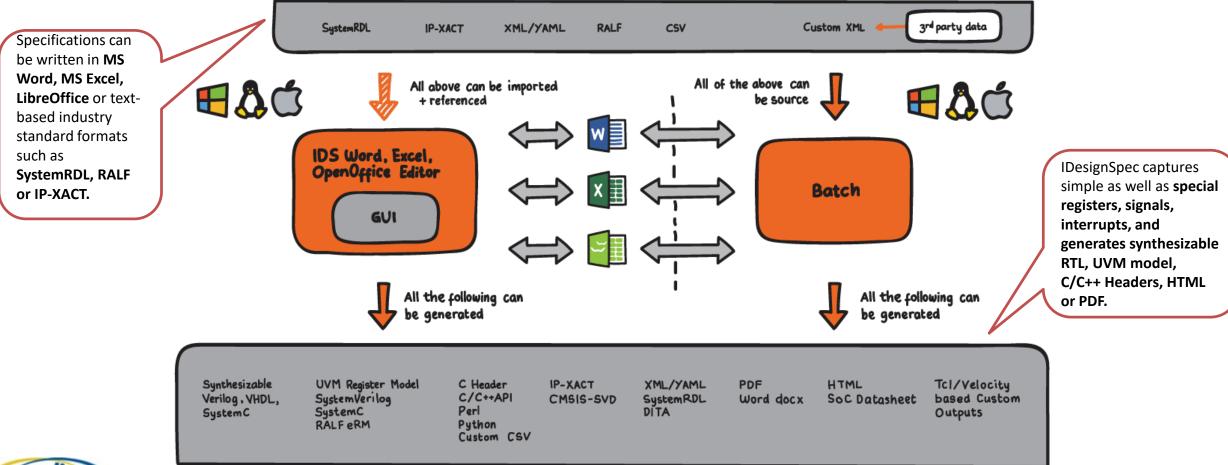

## IDesignSpec<sup>™</sup> – Centralize Register Design/Verification from a Golden Specification

**IDesignSpec™** helps IP/SoC Design architects and engineers to create an executable specification for registers and automatically generate output for SW and HW teams.

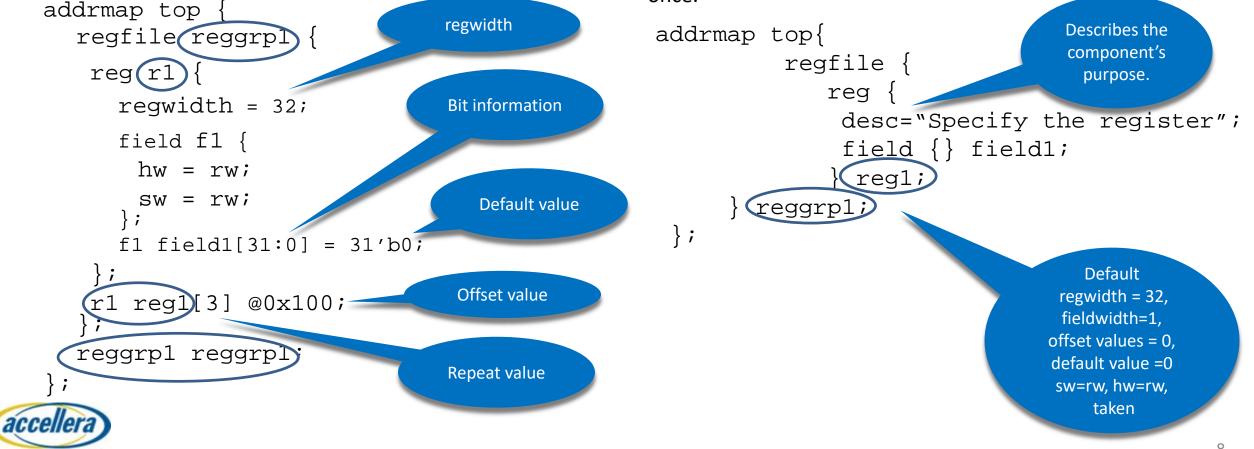

## Example

SYSTEMS INITIATIVE

# **Defining Components**

### **Definitive definition :**

In definitive definition we instantiate the component in a separate statement. It is suitable for reuse.

### Anonymous definition:

In Anonymous definition we instantiate the component in the same statement. It is suitable for components that are used once.

# **Field**

The **field** component is the lowest-level structural component, it stores the bit information of a register.

## **Definitive field definition:**

**field** [#(field parameter instance [, field\_parameter\_instance]\*)] field\_instance\_element [, field instance element]\*;

e.g. field f { };

#### f f1: Anonymous field definition:

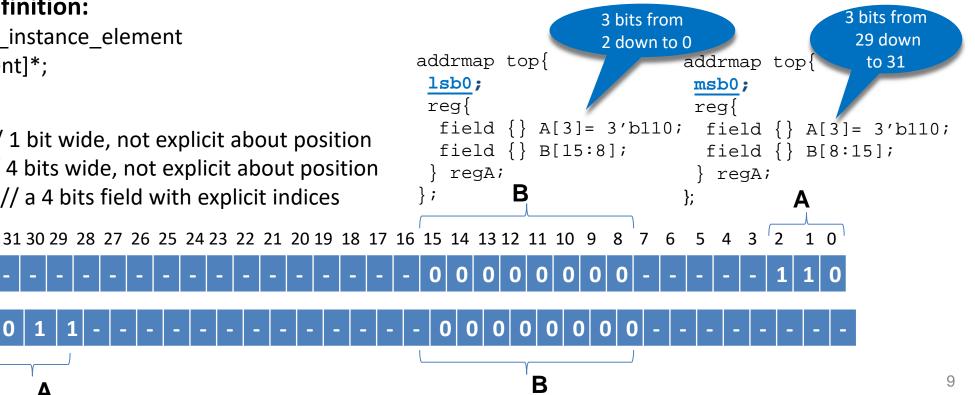

Lsb0

Msb0

**field** {field body} field instance element [,field instance element]\*; e.g. field { } f1, f2; e.g.

field { } single bit field; // 1 bit wide, not explicit about position field { } somefield[4]; // 4 bits wide, not explicit about position field { } somefield[3:0]; // a 4 bits field with explicit indices

## **Field ordering in registers**

| Field ordering in registers | Syntax                               |

|-----------------------------|--------------------------------------|

| lsb0                        | field_type field_instance [high:low] |

| msb0                        | field_type field_instance [low:high] |

# **Software Access Properties**

| Properties  | Description                                                                                                                                                      | Dynamic |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| rclr        | Clear on read                                                                                                                                                    | Yes     |

| rset        | Set on read                                                                                                                                                      | Yes     |

| onread      | Read side-effect                                                                                                                                                 | Yes     |

| woset       | Write one to set                                                                                                                                                 | Yes     |

| woclr       | Write one to clear                                                                                                                                               | Yes     |

| onwrite     | Write function                                                                                                                                                   | Yes     |

| swwe        | Software write-enable active high                                                                                                                                | Yes     |

| swwel       | Software write-enable active low                                                                                                                                 | Yes     |

| swmod       | Assert when field is modified by software (written or read with a set or clear side effect)                                                                      | Yes     |

| swacc       | Assert when field is software accessed                                                                                                                           | Yes     |

| singlepulse | The field asserts for one cycle when<br>written 1 and then clears back to 0 on<br>the next cycle. This creates a single-cycle<br>pulse on the hardware interface | Yes     |

```

reg register1{

field {} fld1,fld2;

field {

hw = rw;

sw = rw;

onread = rclr;

onwrite = woset;

swacc;

} fld3;

field {

hw = r;

sw = w;

singlepulse;

} fld4;

};

addrmap myAmap{

register1 reg1;

reg1.fld1 -> swwel = true;

reg1.fld2 -> swmod = true;

};

```

accei

SYSTEMS INITIATIVE

## **Hardware Access Properties**

| Property       | Description                                                                                                                            | Dynamic |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------|---------|

| we             | Write-enable (active high)                                                                                                             | Yes     |

| wel            | Write-enable (active low)                                                                                                              | Yes     |

| anded          | Logical AND of all bits in field                                                                                                       | Yes     |

| ored           | Logical OR of all bits in field                                                                                                        | Yes     |

| xored          | Logical XOR of all bits in field                                                                                                       | Yes     |

| fieldwidt<br>h | Determines the width of all instances of the field. This<br>number shall be a numeric. The default value of fieldwidth<br>is undefined | Yes     |

| hwclr          | Hardware clear. This field need not be declared as hardware-writable                                                                   | Yes     |

| hwset          | Hardware set. This field need not be declared as hardware-writable                                                                     | Yes     |

| hwenable       | Determines which bits may be updated after any write enables. Bits that are set to 1 will be updated                                   | Yes     |

| hwmask         | Determines which bits may be updated after any write enables. Bits that are set to 1 will not be updated                               | Yes     |

```

reg register1{

field {

fieldwidth = 5;

}fld1,fld2,fld3;

field {}fld4;

field {}fld5;

```

#### };

addrmap myAmap{

register1 reg1,reg2;

reg1.fld1 -> we = true;

reg1.fld2 -> wel = true;

reg1.fld3 -> anded = true;

reg2.fld1 -> hwenable =

reg1.fld1;

};

11

# Register

A register is defined as a set of one or more SystemRDL field instances that are atomically accessible by software at a given address.

### **Definitive register definition**

[external] reg\_name [#(parameter\_instance [, parameter\_instance]\*)]

reg\_instance\_element [, reg\_instance\_element]\*;

### Anonymous register definition

reg {[reg\_body]}

[external] reg\_instance\_element [, reg\_instance\_element]\*;

Register Instantiation into three forms:

| Register<br>Instantiation<br>forms | Description                                                                                                                                                                                      |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| internal                           | all register logic is created by the SystemRDL compiler for the instantiation (the default form)                                                                                                 |

| external                           | the register/memory is implemented by the designer and the interface is inferred from instantiation                                                                                              |

| alias                              | Alias registers are used where designers want to allow<br>alternate software access to registers. SystemRDL allows<br>designers to specify alias registers for internal or external<br>registers |

req req1 { field { hw=w; sw=rw; field1; reg some\_intr { field { hw=w; sw=rw; onwrite = woclr; } field2; addrmap foo { some intr event1; external reg1 reg1; alias event1 some\_intr event1\_for\_dv; };

## **Register Properties**

| Properties  | Description                                                                                                                                  | Dynamic |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------|

| regwidth    | Specifies the bit-width of the register (power of two)                                                                                       | No      |

| accesswidth | Specifies the minimum software access<br>width (power of two) operation that may be<br>performed on the register                             | Yes     |

| errextbus   | The associated external register has error input                                                                                             | No      |

| intr        | Represents the inclusive OR of all the<br>interrupt bits in a register after any field<br>enable and/or field mask logic has been<br>applied | No      |

| shared      | Defines a register as being shared in different address maps                                                                                 | No      |

RDL:

addrmap top {

reg reg1{

errextbus = true;

regwidth = 32;

field {

hw = rw;

sw = rw;

} fld;

};

external reg1 reg1 @0x0;

};

# **Memory Component**

A *memory* is an array of storage consisting of a number of entries of a given bit width. The physical memory implementation is technology dependent and memories shall be **external**.

### **Definitive memory definition**

external mem\_name [#(parameter\_instance [, parameter\_instance]\*)]

mem\_instance\_element [, mem\_instance\_element]\*;

### Anonymous memory definition

mem {[mem\_body]} external mem\_instance\_element [,

mem\_instance\_element]\*;

| Properties | Description                                 | Dynamic |

|------------|---------------------------------------------|---------|

| mementries | The number of memory entries                | No      |

| memwidth   | The memory entry bit width                  | No      |

| SW         | Programmer's ability to read/write a memory | Yes     |

## RDL

```

mem fixed_mem #(longint unsigned

word_size = 32, longint unsigned

memory_size = word_size * 4096) {

mementries = memory_size/word_size ;

memwidth = word_size ;

};

```

# **Register File Components**

- > A register file is as a logical grouping of one or more register and register file instances.

- The only difference between the register file component (regfile) and the addrmap component is an addrmap defines an RTL implementation boundary where the regfile does not.

### **Definitive Register File Definition**

[external | internal] regfile\_name [#(parameter\_instance [, parameter\_instance]\*)]

regfile\_instance\_element [, regfile\_instance\_element]\*;

## **Anonymous Register File Definition**

regfile {[regfile\_body]}

[external | internal] regfile\_instance\_element [, regfile\_instance\_element]\*;

| Properties   | Description                                                                        | Dynamic |

|--------------|------------------------------------------------------------------------------------|---------|

| alignment    | Specifies alignment of all instantiated components in the associated register file | No      |

| sharedextbus | Forces all external registers to share a common bus                                | No      |

| errextbus    | For an external regfile, the associated regfile has an error input                 | No      |

```

regfile fifo_rfile {

reg {field {} a;} a;

reg {field {} a;} b;

};

regfile top_regfile {

external fifo_rfile fifo_a;

external fifo_rfile fifo_b[64];

sharedextbus;

};

addrmap top{

top_regfile top_regfile;

```

};

accellera systems initiative

# Addrmap

- An address component map (addrmap) contains registers, register files, memories, and/or other address maps and assigns a virtual address or final addresses.

- Specifies RTL module boundary

## **Definitive Definition**

component new\_component\_name [#(parameter\_definition [, parameter\_definition]\*)]

{[component\_body]} [instance\_element [, instance\_element]\*];

Anonymous Definition

component {[component\_body]} instance\_element [, instance\_element]\*;

| Properties   | Description                                                                                                   | Dynamic |

|--------------|---------------------------------------------------------------------------------------------------------------|---------|

| alignment    | Alignment of all instantiated components in the address map                                                   | No      |

| sharedextbus | Forces all external registers to share a common bus                                                           | No      |

| errextbus    | The associated addrmap instance has an error input                                                            | No      |

| littleendian | Uses little-endian architecture in the address map                                                            | Yes     |

| addressing   | Controls how addresses are computed in an address map                                                         | No      |

| rsvdset      | The read value of all fields not explicitly defined is set to 1 if rsvdset is True; otherwise, it is set to 0 | No      |

| rsvdsetx     | The read value of all fields not explicitly defined is unknown if rsvd-setX is True                           | No      |

| msb0         | Specifies register bit-fields in an address map are defined as 0:N versus N:0                                 | No      |

| lsb0         | Specifies register bit-fields in an address map are defined as N:0 versus N:0                                 | No      |

accellera systems initiative

## Addrmap - Contd..

addrmap top{ errextbus; rsvdset; reg reg1 { field { } fld1[31:20]; field { } fld2[7:5]; }; reg reg2 { field { } fld1[32]; }; reg1 reg1 @0x0; external reg2 reg2 @0x4; };

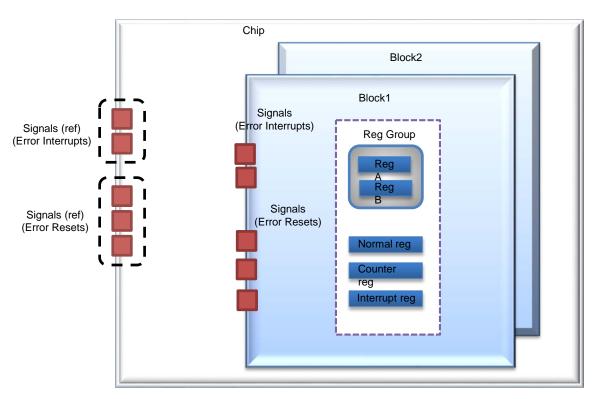

# **Signals**

- "Signals" creates ports, at the block or chip level, and connect certain internal design signals to the external world.

- User can choose what gets connected to these signals and where these signals are used in the generated RTL using properties

| Keyword     | Description                                                                                                                           | Dynamic |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------|---------|

| signalwidth | Width of the signal                                                                                                                   | No      |

| sync        | Synchronous to the clock of the component                                                                                             | Yes     |

| async       | Asynchronous to the clock of the component                                                                                            | Yes     |

| cpuif_reset | Default signal to use for resetting the software interface logic. This parameter only controls the CPU interface of a generated slave | Yes     |

| field_reset | Default signal to use for resetting field<br>implementations                                                                          | Yes     |

| active low  | Signal is active low (state of 0 means ON)                                                                                            | Yes     |

| active high | Signal is active high (state of 1 means ON)                                                                                           | Yes     |

| resetsignal | Reference to the signal used to reset the field                                                                                       | Yes     |

```

addrmap top {

signal{activelow;async;field_reset;} pci_soft_reset;

signal{async;activelow;cpuif_reset;} pci_hard_reset;

reg PCIE_REG_BIST {

reqwidth = 8;

field {

hw = rw;

sw = r;

fieldwidth = 4i

} cplCode [3:0];

field {

hw = rw;

sw = rw;

fieldwidth = 1;

resetsignal = pci_hard_reset;

} capable [7:7]=0;

};

PCIE REG BIST PCIE REG BIST @0x0;

};

```

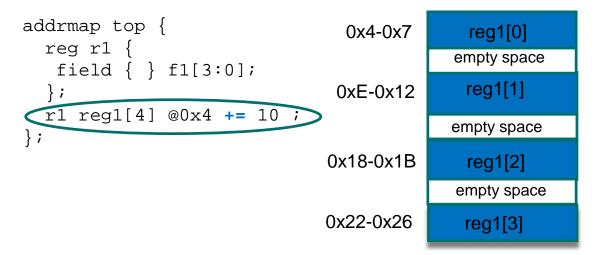

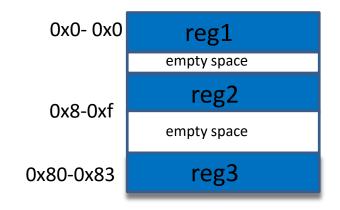

## **Instance address allocation**

## **Instance Alignment**

## **Addressing Modes**

#### **Address allocation operators**

- a) @ expression : Specifies the address for the component instance.

- b) += expression : Specifies the address stride when instantiating an array of components (controls the spacing of the components).

- c) %= expression : Specifies the alignment of the next address when instantiating a component (controls the alignment of the components).

#### **Addressing Modes:**

- *a) Compact* : Specifies the components are packed tightly together while still being aligned to the accesswidth parameter

- **b) Regalign** : Specifies the components are packed so each component's start address is a multiple of its size

- *c) fullalign* : The assigning of addresses is similar regalign, except for arrays.

# Offset (@)

addrmap top {

reg r1 {

field { } f1[3:0];

};

r1 reg1[4]

@0x4;

};

| 0x4  | reg1[0] |  |

|------|---------|--|

| 0x8  | reg1[1] |  |

| 0xB  | reg1[2] |  |

| 0x10 | reg1[3] |  |

# Stride (+=)

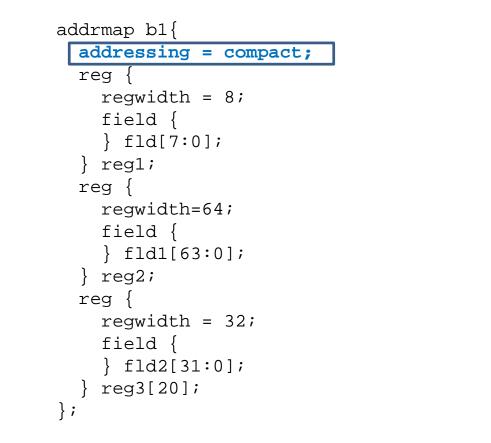

## Compact

It specifies the components are packed tightly together.

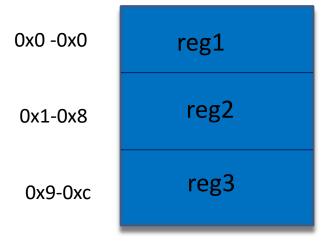

# Regalign

It specifies the components are packed so each component's start address is a multiple of its size

```

addrmap b1{

addressing = regalign;

reg {

regwidth = 8;

field {

} fld[7:0];

} reg1;

reg {

regwidth=64;

field {

} fld1[63:0];

} reg2;

reg {

regwidth = 32;

field {

} fld2[31:0];

} reg3[20];

};

```

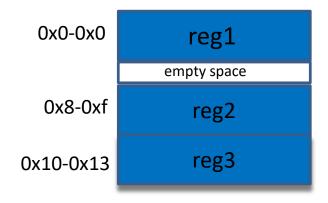

# Fullalign

- The assigning of addresses is similar regalign, except for arrays.

- The alignment value for the first element in an array is the size in bytes of the whole array (i.e., the size of an array element multiplied by the number of elements), rounded up to nearest power of two.

| addrmap b1{                              |

|------------------------------------------|

| addressing = fullalign;                  |

| reg {                                    |

| regwidth = 8;                            |

| field {                                  |

| } fld[7:0];                              |

| } reg1;                                  |

| reg {                                    |

| regwidth=64;                             |

| field {                                  |

| } fld1[63:0];                            |

| } reg2;                                  |

| reg {                                    |

| regwidth = 32;                           |

| field {                                  |

| } fld2[31:0];                            |

| } reg3(20];                              |

| }; · · · · · · · · · · · · · · · · · · · |

# **Enumerations**

It encloses a set of constant named integral values into the enumeration's scope

Syntax: An enum component definition appears as follows.

enum enum\_name { encoding; [encoding;]\* };

Enumerator references shall be prefixed with their enumerated type name and two colons (::), e.g., MyEnumeration::MyValue.

| Keyword | Description                                                                      | Dynamic |

|---------|----------------------------------------------------------------------------------|---------|

| enum    | It encloses a set of constant named integral values into the enumeration's scope | no      |

| encode  | Binds an enumeration to a field.                                                 | Yes     |

```

enum Enum1 {

VAL1 = 3'h0;

VAL2 = 3'h1;

};

enum Enum2 {

VAL11 = 3'h0;

VAL22 = 3'h1;

VAL33 = 3'h2;

};

property MyUDP { component = addrmap ; type = Enum1; }

addrmap top {

reg some_reg { field { } a[3] ; } ;

addrmap {

MyUDP = Enum1::VAL1 ; // Allowed

some_reg regA ;

regA.a -> reset = Enum1::VAL2 + Enum2::VAL33;

submap1 ;

addrmap {

req {

field {

hwclr=longint'(Enum1::VAL1) ==

longint'(Enum2::VAL11);

b;

other_shared_reg ;

submap2 ;

25

```

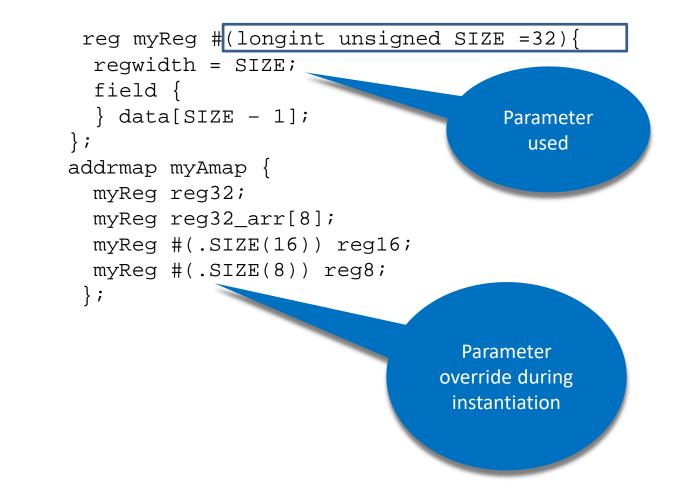

# **Defining component parameters**

All definitive component types, except enumerations and constraints, may be parameterized using Verilog-style parameters.

## Struct

struct configIP { **Syntax:** A **struct** definition appears as follows. boolean Reg1\_is\_present; [abstract] struct struct name [: base struct name] boolean Reg2\_is\_present; }; {{member\_type member\_name;}\*}; struct configTop { configIP IP1; configIP IP2; **Deriving structures** }; addrmap ip #(configTop t){ A struct declaration may *derive* from another struct by req r1 { specifying the base **struct**'s name after a colon (:), ispresent = t.IP1.Reg1\_is\_present; field {}f1; }; struct base\_struct { reg r2{ bit foo ; ispresent = t.IP2.Reg2\_is\_present; }; field {}f1; }; struct derived\_struct : base\_struct { r1 r1; longint unsigned bar ; r2 r2; }; }; addrmap top { struct final\_struct : derived\_struct { ip #(.t(configTop'{IP1:configIP'{Reg1\_is\_present:true}}, // final\_struct's members are foo, bar, and baz. IP2:configIP'{Reg2\_is\_present:false} } ) ) ip1; string baz ; ip #(.t( configTop'{IP1:configIP'{Reg1\_is\_present:false}, }; IP2:configIP'{Reg2 is present:true} } ) ) ip2; };

### Dynamic Assignment

• When a property is assigned after the component is instantiated, the assignment itself is referred to as a *dynamic assignment*.

### Syntax:

```

instance_name ->

property_name [= value]

```

## Property Assignment

A specific property shall only be set once per scope.

Syntax:

property\_name[=expression];

## Default Property

#### Assignment

A specific property default value shall only be set once per scope.

#### **Syntax**

default property\_name [= value];

## SystemRDL Default Value for Property type

• Property takes its default value

| property_name [= value];                                                                                   |                                                                                                              |                                                                                                                          | rog                                                                                     |

|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| <pre>reg {   default name ="def   name";   field f_type {     name = "other name";   };   f_type f1;</pre> | <pre>reg {   default name ="def   name";   field f_type {     name = "other name";     };   f_type f1;</pre> | <pre>reg {     default name ="def     name";     field f_type {         name = "other name";     };     f type f1;</pre> | <pre>reg {   default name ="def   name";   field f_type {    name = "other name";</pre> |

| <pre>fl_cype fif fl-&gt;name = "Dynamic Assignment"; } some_reg;</pre>                                     | <pre>fl_cype fif<br/>fl-&gt;name = "Dynamic<br/>Assignment";<br/>} some_reg;</pre>                           | <pre>f_type f1;<br/>f1-&gt;name = "Dynamic<br/>Assignment";<br/>} some_reg;</pre>                                        | <pre>f_type f1;<br/>f1-&gt;name = "Dynamic<br/>Assignment";<br/>} some_reg;</pre>       |

**Property Assignment**

## Interrupt

Interrupt is a signal generated and sent to the processor by hardware or software indicating an event that

needs attention

| Keyword    | Description                                                                                                                                              |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| intr       | Interrupt, part of interrupt logic for a register                                                                                                        |  |

| posedge    | Interrupt when next goes from low to high                                                                                                                |  |

| negedge    | Interrupt when next goes from high to low                                                                                                                |  |

| bothedge   | Interrupt when next changes value                                                                                                                        |  |

| level      | Interrupt while the next value is asserted and maintained (the default)                                                                                  |  |

| nonsticky  | Defines a non-sticky (hierarchical) interrupt (not locked)                                                                                               |  |

| enable     | Defines an interrupt enable; i.e., which bits in an interrupt field are used to assert an interrupt                                                      |  |

| mask       | Defines an interrupt mask ; i.e., which bits in an interrupt field are not used to assert an interrupt                                                   |  |

| haltenable | Defines a halt enable (the inverse of haltmask); i.e.,<br>which bits in an interrupt field are set to de-assert the<br>halt out.                         |  |

| haltmask   | Defines a halt mask (the inverse of haltenable); i.e.,<br>which bits in an interrupt field are set to assert the halt<br>out                             |  |

| sticky     | Defines the entire field as sticky; i.e., the value of the associated interrupt field shall be locked until cleared by software (write or clear on read) |  |

```

addrmap block_name {

reg Status1 {

regwidth = 32;

field {

reg Mask1 {

hw = rw;

sw = rw;

onread = r;

onwrite = woclr;

intr;

} Fld[31:0] = 32'h0;

reg Status2 {

};

regwidth = 32;

field {

hw = rw;

sw = rw;

Mask1

onread = r;

onwrite = woclr;

intr;

;

} Fld[31:0] = 32'h0;

reg Enable1 {

regwidth = 32;

field {

```

```

regwidth = 32;

field {

hw = rw;

sw = rw;

onread = r;

onwrite = w;

} Fld[31:0] = 32'h0;

Status1 Status1 @0x0000;

Status2 Status2 @0x0004;

Enable1 Enable1 @0x0008;

Mask1

@0x000C;

Status1.Fld -> enable = Enable1.Fld;

Status2.Fld -> mask = Mask1.Fld;

```

29

};

};

hw = rw;sw = rw; onread = r;onwrite = w;

} Fld[31:0] = 32'h0;

## Counter

SYSTEMS INITIATIVE

• A *counter* is a special purpose field which can be incremented or decremented by constants or dynamically specified values.

| Keyword       | Description                                                                        |

|---------------|------------------------------------------------------------------------------------|

| counter       | Field implemented as a counter.                                                    |

| incrvalue     | Increment counter by specified value.                                              |

| decrvalue     | Decrement counter by specified value.                                              |

| incrsaturate  | Indicates the counter saturates in the incrementing direction.                     |

| decrsaturate  | Indicates the counter saturates in the decrementing direction.                     |

| Incrthreshold | Indicates the counter has a threshold in the incrementing direction.               |

| decrthreshold | Indicates the counter has a threshold in the decrementing direction.               |

| decrwidth     | Width of the interface to hardware to control decrementing the counter externally. |

| incrwidth     | Width of the interface to hardware to control incrementing the counter externally. |

| threshold     | This is an alias of incrthreshold.                                                 |

| saturate      | This is an alias of incrsaturate.                                                  |

| underflow     | Underflow signal asserted when counter underflows or wraps.                        |

| overflow      | Overflow signal asserted when counter overflows or wraps.                          |

| incr          | The counter increment is controlled by another component or signal (active high).  |

| a decr        | The counter decrement is controlled by another component or signal (active high).  |

```

addrmap block_name {

reg incr_reg {

reqwidth = 32;

field {

hw = na;

sw = rw;

counter;

incrvalue = 2;

incrsaturate = 15;

incrthreshold = 10;

} Fld[31:0] = 32'h0;

};

reg decr_reg {

regwidth = 32;

field {

hw = na;

sw = rw;

counter;

decrvalue = 2i

decrthreshold = 10;

decrsaturate = 5;

} Fld[31:0] = 32'h0;

};

incr_reg incr_reg @0x0000;

decr_reg decr_reg @0x0004;

};

```

30

## **HDL PATH**

By specifying an HDL path, the verification environment can have direct access to memory, register, and field implementation nets in a Design Under Test (DUT).

An hdl\_path\_slice or hdl\_path\_gate\_slice can be put on a field or mem component. It can be used when the corresponding

RTL or gate-level netlist is not contiguous.

### Syntax:

hdl\_path = "path"; hdl\_path\_gate = "path"; hdl\_path\_slice = '{"path" [, "path"]\*}; hdl\_path\_gate\_slice = '{"path" [, "path"]\*};

| Property            | Description                                                     | Dynamic |

|---------------------|-----------------------------------------------------------------|---------|

| hdl_path            | Assigns the RTL hdl_path for an addrmap, reg, or regfile        | Yes     |

| hdl_path_slice      | Assigns a list of RTL hdl_path for a field or<br>mem            | Yes     |

| hdl_path_gate       | Assigns the gate-level hdl_path for an addrmap, reg, or regfile | Yes     |

| hdl_path_gate_slice | Assigns a list of gate-level hdl_path for a field or mem        | Yes     |

```

addrmap blk def #(string ext hdl path = "ext block"){

hdl path = "int block" ;

req {

hdl_path = { ext_hdl_path, ".externl_reg" } ;

field {

hdl path slice = '{ "field1" } ;

} f1 ;

} external external_reg ;

req {

hdl_path = "int_reg" ;

field {

hdl_path_slice = '{ "field1" } ;

} f1 ;

internal req ;

addrmap top {

hdl path = "TOP" ;

blk_def #( .ext_hdl_path("ext_block0")) int_block0 ;

int_block0 -> hdl_path = "int0" ;

blk_def #( .ext_hdl_path("ext_block1")) int_block1 ;

int block1 -> hdl path = "int1" ;

};

```

## Constraint

A *constraint* is a value-based condition on one or more components; e.g., constraint-driven test generation allows users to automatically generate tests for functional verification.

### **Definitive definition**

**constraint** constraint component name {[constraint body]}; constraint\_component\_name constraint\_inst;

### Anonymous definition

**constraint {**[*constraint body*]} constraint\_component\_name;

| Property           | Description                                                          | Dynamic |

|--------------------|----------------------------------------------------------------------|---------|

| constraint_disable | Specifies whether to disable (true)<br>or enable (false) constraints | Yes     |

```

constraint max_value { this < 256; };</pre>

enum color {

red = 0 { desc = " color red ";};

qreen = 1 { desc = " color green ";};

};

reg register1 {

field {

} limit[0:2]= 0;

field {

max value max1;

} f1[3:9]= 3;

field {

encode=color;

constraint{this inside{color::red,color::green};}rg1;

} f2[10:31];

addrmap constraint_component_example {

register1 reg1;

register1 reg2;

req2.f2.rq1->constraint disable = true;

};

```

32

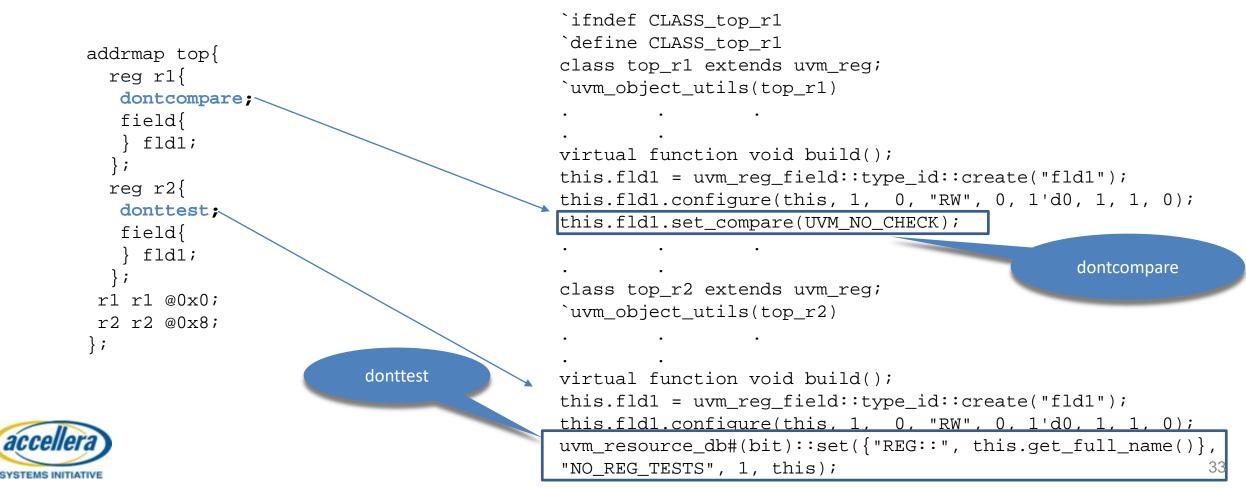

# **Structural Testing**

1) dontcompare : This is testing property indicates the components read data shall be discarded and not compared against expected results.

2) donttest : This testing property indicates the component is not included in structural testing.

# SystemRDL with Embedded Perl

- Perl snippets shall begin with <% and be terminated by %>; between these markers any valid Perl syntax may be used.

- Any SystemRDL code outside of the Perl snippet markers is equivalent to the Perl print 'RDL code' and the resulting code is printed directly to the postprocessed output.

- <%=\$VARIABLE%> (no whitespace is allowed) is equivalent to the Perl print \$VARIABLE.

- The resulting Perl code is interpreted, and the result is sent to the traditional Verilog-style preprocessor.

| Directive | Defining standard | Description                |

|-----------|-------------------|----------------------------|

| `define   | SystemVerilog     | Text macro definition      |

| `if       | Verilog           | Conditional compilation    |

| `else     | Verilog           | Conditional compilation    |

| `elsif    | Verilog           | Conditional compilation    |

| `endif    | Verilog           | Conditional compilation    |

| `ifdef    | Verilog           | Conditional compilation    |

| `ifndef   | Verilog           | Conditional compilation    |

| `include  | Verilog           | File inclusion             |

| `line     | Verilog           | Source filename and number |

| `undef    | Verilog           | Undefine text macro        |

```

reg myReg {

myField data0 [1:0];

myField data2 [3:2];

myField data4 [5:4];

};

```

addrmap BlockA {

# **Including Multiple File**

addrmap BlockB {

reg RegB1 {

field {

};

hw = rw;

sw = rw;

addrmap BlockC { name = "BlockC Address Map"; name = "BlockB Address Map"; reg RegCl { reqwidth = 32;desc = "I am register B1."; field { regwidth = 32;hw = rw;sw = rw;} FC1[31:0] = 32'h0; } FB1[31:0] = 32'h0; };

### **IDSBatch Output:**

| 17-Sep-19 | 05:54 PM < | DIR>          |                            |

|-----------|------------|---------------|----------------------------|

| 17-Sep-19 | 05:54 PM < | DIR>          |                            |

| 17-Sep-19 | 05:54 PM   | 15,481        | BlockA.v                   |

| 17-Sep-19 | 05:54 PM   | 10,525        | BlockB.v                   |

| 17-Sep-19 | 05:54 PM   | 10,510        | BlockC.v                   |

| 17-Sep-19 | 05:54 PM   | 10,202        | ids_top_amba_aggregation.v |

| 17-Sep-19 | 05:54 PM   | 9,855         | top.v                      |

|           | 5 File(s)  | 56,57         | 73 bytes                   |

|           | 2 Dir(s)   | 334,284,574,7 | 720 bytes free             |

|           |            |               |                            |

req ReqA1 { reqwidth = 32;field { hw = rw;sw = rw;

name = "BlockA Address Map";

```

desc = "Hi I am field of register A";

} FA1[31:0] = 32'h0;

```

```

`include "BlockA.rdl"

`include "BlockB.rdl"

`include "BlockC.rdl"

```

```

addrmap top {

name = "top Address Map";

```

BlockA BlockA @0x000; BlockB BlockB @0x500; BlockC BlockC @0x1000; };

## **SystemRDL** Editor

- SystemRDL editor is available as a part of IDS-NG

- User can write input SystemRDL file in the editor

- Keywords are highlighted which makes effective code visibility

- Auto completion of components is also possible (e.g. bracket, semicolon completion)

- The tool indicates syntax error for every line, simultaneously, while writing the spec

- The tool also provides keyword hinting, and it can also hint to the component names used within the file during instantiation or dynamic assignment.

- At the end, the entire input file can be checked for compilation and syntax errors

- Suggestions for error resolution are also provided

- User can check and generate the input file as well from the tool

- Evaluation Request : <u>support@agnisys.com</u>

### **SystemRDL** Editor – Contd..

|                   | ty display_name {type= strin                                                                                 | g ; component = addrmap reg ;}                                                                                            | ;        |  |

|-------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------|--|

| addrmap           | <pre>b dbg_regs { me = "dbg registers.";</pre>                                                               |                                                                                                                           |          |  |

| des               | <pre>sc = "dbg registers.";</pre>                                                                            |                                                                                                                           |          |  |

| displa            | ay_name = "dbg_regs_%d";                                                                                     |                                                                                                                           |          |  |

| reg               | t up pogl                                                                                                    |                                                                                                                           |          |  |

| Tet               | g wr_reg{<br>regwidth = 32;                                                                                  |                                                                                                                           |          |  |

|                   | default hw=r;                                                                                                |                                                                                                                           |          |  |

|                   | default sw=rw;                                                                                               |                                                                                                                           |          |  |

| •                 | field{                                                                                                       |                                                                                                                           |          |  |

|                   | hw=r;<br>sw=rw;                                                                                              |                                                                                                                           |          |  |

|                   |                                                                                                              |                                                                                                                           |          |  |

|                   | $WR_REG[31:0] = 0;$                                                                                          |                                                                                                                           |          |  |

|                   | }WR_REG[31:0] = 0;<br>};                                                                                     |                                                                                                                           |          |  |

|                   | };                                                                                                           |                                                                                                                           |          |  |

|                   | };<br>_regc0_wr                                                                                              | reg0 @0x0000000;                                                                                                          |          |  |

| c0<br>ali         | <pre>}; _reg c0_wr_ wr_reg0-&gt;rt1_reg_enb=false; ias c0_wr_reg0 wr_reg c1_wr_</pre>                        |                                                                                                                           |          |  |

| c0<br>ali         | };<br>_reg c0_wr_<br>_wr_reg0->rtl_reg_enb=false;                                                            |                                                                                                                           |          |  |

| c0<br>ali         | <pre>}; _reg c0_wrwr_reg0-&gt;rt1_reg_enb=false; ias c0_wr_reg0 wr_reg c1_wrreg.</pre>                       | reg0 @0x00001000;                                                                                                         | <u></u>  |  |

| c0_<br>ali<br>wr_ | <pre>}; _reg c0_wr_ wr_reg0-&gt;rt1_reg_enb=false; las c0_wr_reg0 wr_reg c1_wr_ reg.</pre>                   | reg0 @0x00001000;<br>[keyworc] property<br>[keyworc]                                                                      |          |  |

| c0<br>ali         | <pre>}; _reg c0_wrwr_reg0-&gt;rtl_reg_enb=false; ias c0_wr_reg0 wr_reg c1_wrreg.</pre>                       | reg0 @0x00001000;<br>[keyword]<br>[keyword]<br>[keyword]                                                                  |          |  |

| c0_<br>ali<br>wr_ | <pre>}; _reg c0_wr_ wr_reg0-&gt;rtl_reg_enb=false; ias c0_wr_reg0 wr_reg c1_wr_ reg. </pre>                  | reg0 @0x00001000;<br>[keyworc]<br>[keyworc]<br>[keyworc]<br>[keyworc]<br>[keyworc]                                        |          |  |

| c0_<br>ali<br>wr_ | <pre>};<br/>_reg c0_wr_<br/>_wr_reg0-&gt;rtl_reg_enb=false;<br/>ias c0_wr_reg0 wr_reg c1_wr_<br/>_reg.</pre> | reg0 @0x00001000;<br>[keyword<br>[keyword<br>[keyword<br>[keyword<br>[keyword<br>[keyword                                 |          |  |

| c0_<br>ali<br>wr_ | <pre>};<br/>_reg c0_wr_<br/>wr_reg0-&gt;rt1_reg_enb=false;<br/>ias c0_wr_reg0 wr_reg c1_wr_<br/>_reg.</pre>  | reg0 @0x00001000;<br>[keyworc<br>[keyworc<br>[keyworc<br>[keyworc<br>[keyworc<br>[keyworc<br>[keyworc<br>[keyworc         |          |  |

| c0_<br>ali<br>wr_ | <pre>}; _reg c0_wr_ wr_reg0-&gt;rtl_reg_enb=false; ias c0_wr_reg0 wr_reg c1_wrreg.</pre>                     | reg0 @0x00001000;<br>[keyworc]<br>[keyworc]<br>[keyworc]<br>[keyworc]<br>[keyworc]<br>[keyworc]<br>[keyworc]<br>[keyworc] | <u>.</u> |  |

| c0_<br>ali<br>wr_ | <pre>};<br/>_reg c0_wr_<br/>wr_reg0-&gt;rt1_reg_enb=false;<br/>ias c0_wr_reg0 wr_reg c1_wr_<br/>_reg.</pre>  | reg0 @0x00001000;<br>[keyworc<br>[keyworc<br>[keyworc<br>[keyworc<br>[keyworc<br>[keyworc<br>[keyworc<br>[keyworc         | <u>-</u> |  |

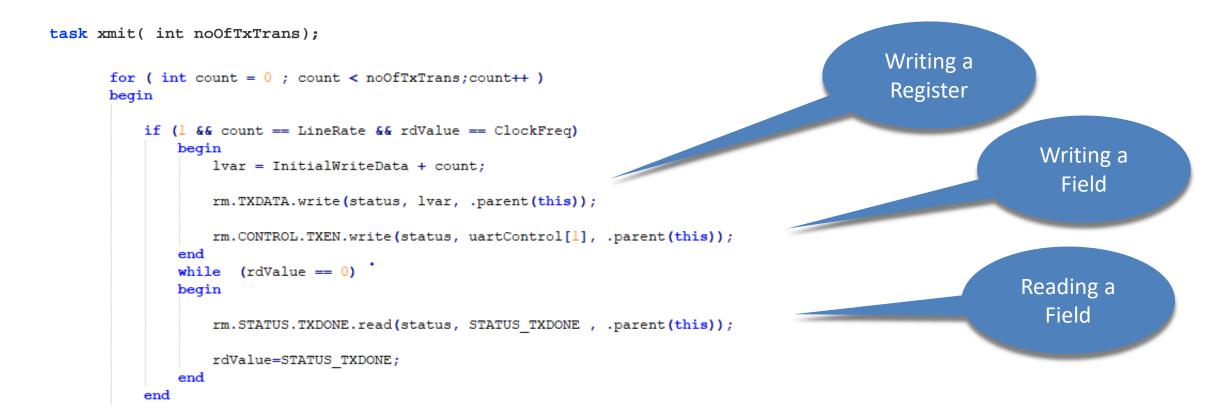

# **Example Sequence with HSI**

As an example, the code below is a SV task that is manually coded by the user. It shows that HSI is a critical part of a sequence to achieve a certain behavior in the target device.

## **Introduction to Sequences**

- Sequences are built on registers, memories, pins

- Sequences contain

- Register / Field Writes

- Register / Field Reads

- Pin Manipulation Commands

- Wait / Function calls, sub sequence calls

- Information about Registers/Memories can be in any format

- IP-XACT

- SystemRDL

- Word / Excel

- Text files

# **The Problem:**

### How to write sequences once, run anywhere?

- Designer Creates HW design with a certain sequence

- Verification engineer reads from a spec or from designer's mind and creates SV/UVM sequences

- Firmware engineer repeats step 2 but this time in his own environment typically C/C++

- Lap debug may have a C based environment or even TCL/Python based environment

- Repeat the process for validation

Why repeat the same algorithm over and over again in the various stages of the development?

# **Proposed Solution**

### **Create a Golden Spec for Implementation-Level Sequences and Auto-Generate the Code**

- Capturing the golden specification for sequences will need the following capabilities:

- Control flow

- High level of abstraction devoid of implementation detail

- Access to hierarchical register data for SoC, Subsystem and IPs

- Access to pins, signals and interfaces

- High level execution of arbitrary transactions

- Deal with timing differently based on the target

- Hierarchy of sequence and base address of the DUT

# **Specification Driven Development**

2020

DESIGN AND VERIFICATION

SYSTEMS INITIATIVE

## **ISequenceSpec™** Suite

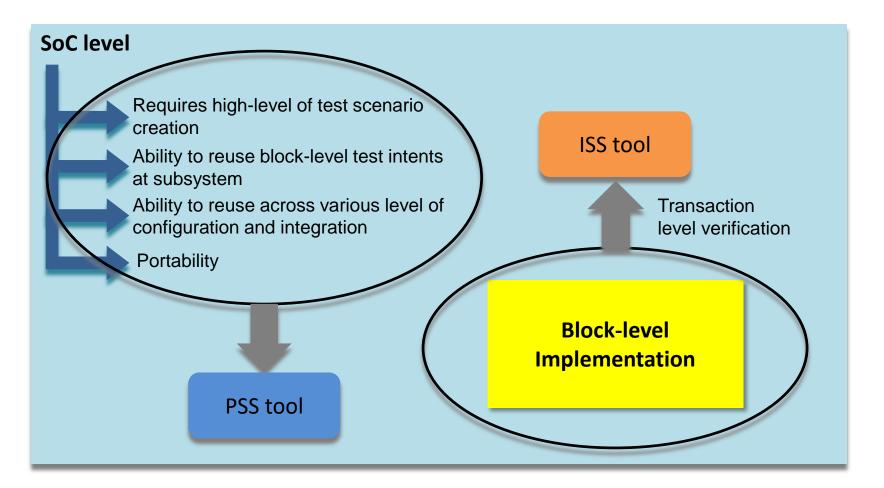

# **Portable Stimulus Standard**

- PSS helps automate the testing process, thereby reducing the time to generate complex use-case scenarios

- It can generate tests, 10x faster than hand coding

- Portability from IP to sub-system to SoC level, including hardware-aware software can be achieved

## **Portable Stimulus Standard – Contd..**

# Portable Stimulus Standard – Contd..

• PSS 1.0 Standard was released in June 2018

#### 1.1 Purpose

The Portable Test and Stimulus Standard defines a specification for creating a single representation of stimulus and test scenarios, usable by a variety of users across different levels of integration under different configurations, enabling the generation of different implementations of a scenario that run on a variety of execution platforms, including, but not necessarily limited to, simulation, emulation, FPGA prototyping, and post-Silicon. With this standard, users can specify a set of behaviors once, from which multiple implementations may be derived.

- Powerful concepts of PSS: Abstraction and Reuse

- PSS is useful for high-level test scenario creation

- Modeling Data flow

- Modeling Behavior

- Constraints, Randomization, Coverage

- Actions are a key abstraction unit can model the scenarios and include exec blocks

- The implementation-level tests are handled by "exec blocks"

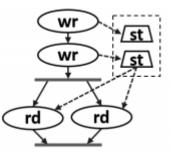

# **PSS Data Flow Object Types**

- **Buffers**: A buffer represents persistent data that can be written (output by a producing action) and may be read (input) by any number of consuming actions.

- **Streams**: The stream flow object type represents transient data shared between actions. The semantics of the stream flow object requires that the producing and consuming actions execute in parallel (i.e., both activities shall begin execution when the same preceding action(s) complete.

- **States**: The state flow object represents the state of some element in the DUT or test environment at a given time. Multiple actions may read or write the state object, but only one write action may execute at a time.

- **Data Object Pools**: Data flow objects are grouped into pools, which can be used to limit the set of actions that can communicate using objects of a given type. For buffer and stream types, the pool will contain the number of objects of the given type needed to support the communication between actions sharing the pool. For state objects, the pool will only contain a single object of the state type at any given time.

c. States

accellera

SYSTEMS INITIATIVE

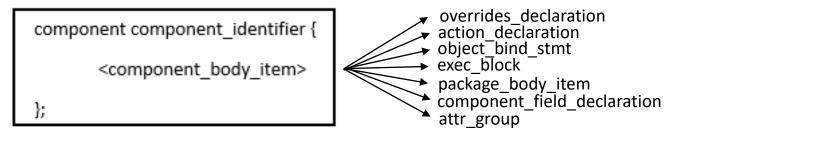

# **PSS Language Constructs**

• **Component**: A structural entity, defined per type and instantiated under other components.

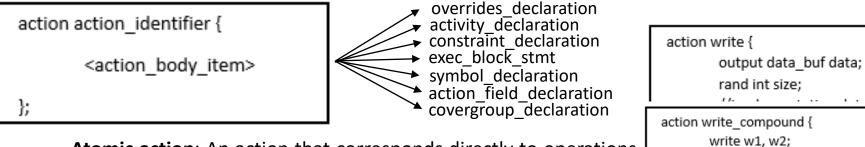

• Action: An element of behavior.

- <u>Atomic action</u>: An action that corresponds directly to operations of the underlying system under test (SUT) and test environment.

- <u>Compound action</u>: An action which is defined in terms of one or more sub-actions.

- Activity: An abstract, partial specification of a scenario that is used in a compound action to determine the high-level intent and leaves all other details open.

ls

activity{

w1; w2;

# **PSS Language Constructs – Contd..**

• **Exec block**: Specifies the mapping of PSS scenario entities to its non-PSS implementation.

| exec exec_kind_identifier {       |

|-----------------------------------|

| <exec_body_stmt></exec_body_stmt> |

| };                                |

exec\_kind\_identifier:

pre\_solve post\_solve body header declaration run\_start run\_end

init

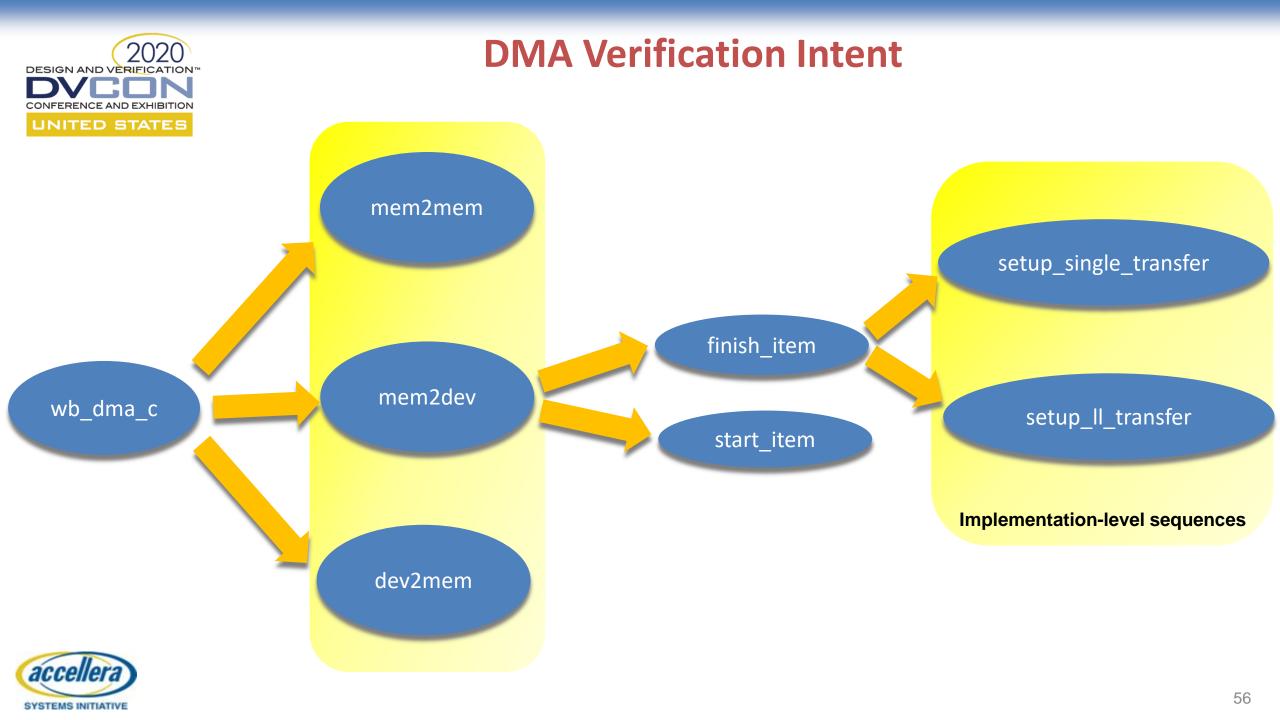

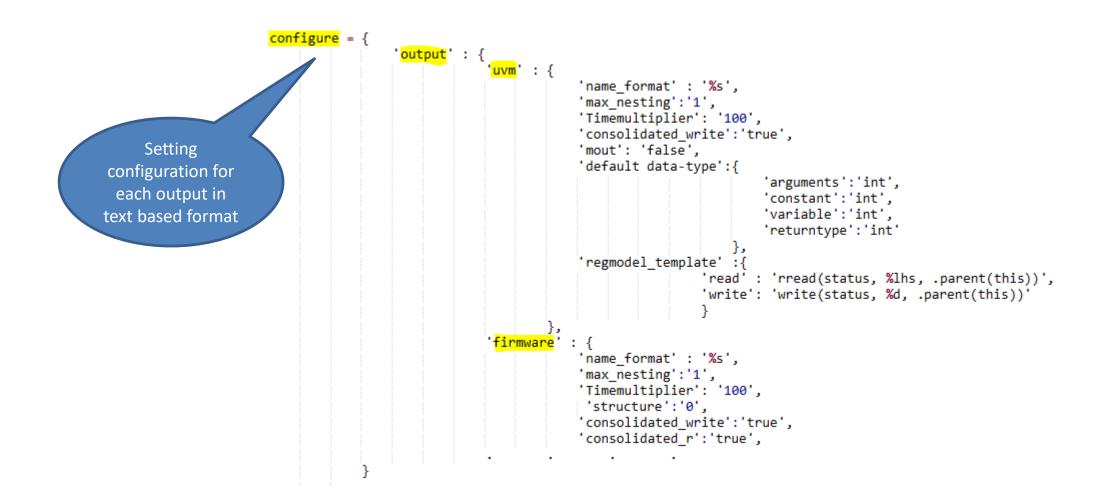

# **ISequenceSpec** + PSS Proposed Tool Flow

- Capture sequences in pseudo-code in the golden spec (spreadsheet or text)

- Generate sequences in multiple formats (C, System Verilog, UVM)

- PSS tool user creates the test scenarios and calls the exec blocks generated by ISS

- PSS tool user synthesizes the tests/scenarios and generates the required files for the target platform

### WISHBONE DMA

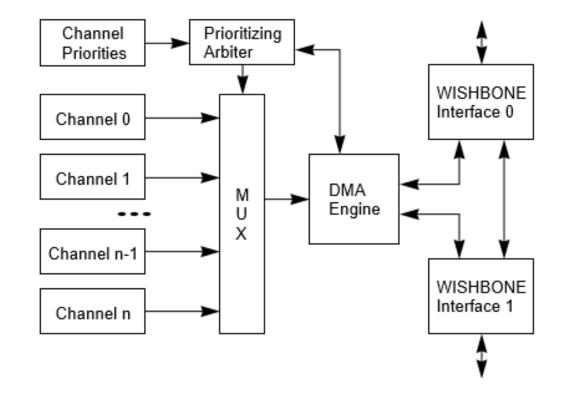

- WISHBONE DMA has been contributed by OpenCores. This core provides DMA transfers between two WISHBONE interfaces. Transfers can also be performed on the same WISHBONE interface.

- Following block diagram depicts the DMA Engine and its functional blocks.

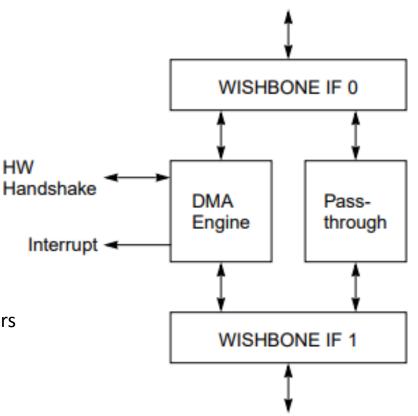

### WISHBONE DMA – Contd..

- It consists of 3 building blocks:

- 2 WISHBONE interfaces

- DMA Engine

- Pass-through logic

- WISHBONE interface :

- DMA Bridge/Core has two master and slave capable WISHBONE interfaces.

- Both interfaces are WISHBONE SoC bus specification Rev. B compliant.

- This implementation implements a 32-bit bus width.

- DMA Engine:

- The DMA engine is a up to 31 channel DMA engine that supports transfers between the two interfaces as well as transfers on the same interface.

- Each channel can be programmed to have a different priority.

- Pass-through logic:

- This block performs the bridging operation between the two WISHBONE interfaces.

- It includes a two entry deep write buffer in each direction. The write buffer can be disabled if desired.

### WISHBONE DMA – Contd..

- This implementation is designed to work with two WISHBONE interfaces running at the same clock.

- The WISBONE specification and additional information about WISHBONE SoC can be found at: <a href="http://www.opencores.org/wishbone/">http://www.opencores.org/wishbone/</a>

- The Main features of the DMA/Bridge are:

- Up to 31 DMA Channels

- 2, 4 or 8 priority levels

- Linked List Descriptors Support

- Circular Buffer Support

- FIFO buffer support

- Hardware handshake support

### **DMA Register Map**

addrmap ch {

reg csr {

field {

field {

hw = r;

sw = r;

hw = r;

SW = r;

.

regwidth = 32;

}; };

reg SZ {

field {

hw = rw;

sw = rw;

field {

hw = rw;

sw = rw;

.

csr csr @0x000; SZ SZ @0x004; A0 A0 @0x008; AM0 AM0 @0x00C; A1 A1 @0x010; AM1 AM1 @0x014; DESC DESC @0x018;

}; .

};

name = "ch Address Map";

} I CHK DONE[22:22] = 1'h0;

} I DONE[21:21] = 1'h0;

} CHK SZ[24:16] = 9'h0;

} TOT SZ[11:0] = 12'h0;

.

regwidth = 32;

UNITED STATES

| <pre>addrmap wb_dma_reg_block {     name = "wb_dma_reg_block Address Map";</pre>                                            |

|-----------------------------------------------------------------------------------------------------------------------------|

| <pre>reg CSR {     regwidth = 32;     field {         hw = rw;         sw = rw;         } PAUSE[0:0] = 1'h0; };</pre>       |

| <pre>reg int_msk_a {     regwidth = 32;     field {         hw = r;         sw = rw;         } MASK[30:0] = 31'h0; };</pre> |

| <pre>reg int_msk_b {     regwidth = 32;     field {         hw = r;         sw = rw;         } MASK[30:0] = 31'h0; };</pre> |

CSR CSR @0x000; int\_msk\_a int\_msk\_a @0x004; int\_msk\_b int\_msk\_b @0x008; int\_src\_a int\_src\_a @0x00C; int\_src\_b int\_src\_b @0x010; ch ch[32] @0x014; };

55

## **Descriptors in DMA**

|             | <pre>class wb_dma_descriptor extends uvm_sequence_item;</pre> |                      |  |  |

|-------------|---------------------------------------------------------------|----------------------|--|--|

|             | <pre>`uvm_object_utils(wb_dma_descriptor)</pre>               |                      |  |  |

|             | rand bit[5:0]                                                 | channel;             |  |  |

|             | rand bit                                                      | mode;                |  |  |

|             | rand bit                                                      | inc_src;             |  |  |

|             | rand bit                                                      | inc_dst;             |  |  |

|             | rand bit                                                      | <pre>src_sel;</pre>  |  |  |

|             | rand bit                                                      | dst_sel;             |  |  |

| Descriptors | rand bit[11:0]                                                | tot_sz;              |  |  |

|             | <pre>rand bit[2:0]</pre>                                      | trn_sz;              |  |  |

| for DMA 🚽   | rand bit[8:0]                                                 | chk_sz;              |  |  |

|             | <pre>rand bit[31:0]</pre>                                     | <pre>src_addr;</pre> |  |  |

|             | <pre>rand bit[31:0]</pre>                                     | dst_addr;            |  |  |

|             | bit                                                           | rand_addr;           |  |  |

|             | <pre>constraint trn_sz_c</pre>                                |                      |  |  |

|             | trn_sz inside {1                                              | , 2, 4};             |  |  |

|             | }                                                             |                      |  |  |

|             | <pre>constraint addr_incr</pre>                               | _c {                 |  |  |

|             | inc_src    inc_d                                              | st;                  |  |  |

|             | }                                                             |                      |  |  |

|             | <pre>constraint channel_c</pre>                               | {                    |  |  |

|             | channel inside {                                              | [0:7]};              |  |  |

|             | }                                                             |                      |  |  |

|             | <pre>constraint tot_sz_c</pre>                                | {                    |  |  |

|             | <pre>tot_sz &gt; 0;</pre>                                     |                      |  |  |

|             | }                                                             |                      |  |  |

|             | <pre>constraint chk_sz_c</pre>                                | (                    |  |  |

|             | $chk_sz > 0;$                                                 |                      |  |  |

|             | }                                                             |                      |  |  |

|             | constraint rand_addr                                          | _c {                 |  |  |

|             | (rand_addr == 0)                                              | -> src_addr == 0;    |  |  |

|             | (rand_addr == 0)                                              | -> dst_addr == 0;    |  |  |

|             | }                                                             |                      |  |  |

|             | endclass                                                      |                      |  |  |

PSS component

containing actions

**PSS code**

component wb\_dma\_c {

import pvm\_types\_pkg::\*;

action wb\_dma\_a {

// The channel this transfer runs on

rand bit[3] channel;

// Total transfers to perform

rand bit[16] tot\_sz;

```

// Bytes to transfer at a time (1, 2, 4)

rand bit[4] in [1,2,4] trn_sz;

```

```

action mem2mem_a : wb_dma_a {

input data_mem_b dat_i;

output data_mem_b dat_o;

constraint {

```

```

dat_i.sz == dat_o.sz;

}

```

```

action mem2dev_a : wb_dma_a {

input data_mem_b dat_i;

output data_ref_mem_s dev_dat_o;

constraint {

```

```

dat_i.sz == dev_dat_o.sz;

}

```

```

action dev2mem_a : wb_dma_a {

input data_mem_b dat_o;

output data_ref_mem_s dev_dat_i;

```

```

constraint {

dat_o.sz == dev_dat_i.sz;

}

```

SYSTEMS INITIATIVE

PSS action blocks containing the Exec Block

```

"exec" blocks

generated by

ISequenceSpec

containing SV

tasks.

```

```

extend action wb_dma_c::mem2mem_a {

```

```

exec body {

mem2mem(channel, dat_i.addr, dat_o.addr, tot_sz, trn_sz);

```

```

exec body SV = """

mem2mem({{channel}}, {{dat_i.addr}}, {{dat_o.addr}}, {{tot_sz}}, {{trn_sz}});

""";

exec body C = """

mem2mem({{channel}}, {{dat_i.addr}}, {{dat_o.addr}}, {{tot_sz}}, {{trn_sz}});

""";

```

```

extend action wb_dma_c::dev2mem_a {

exec body {

dev2mem(channel, dev_dat_i.addr, dat_o.addr, tot_sz, trn_sz);

dev2mem(channel, dev_dat_i.addr, dat_o.addr, tot_sz, trn_sz);

```

```

exec body SV = """

dev2mem({{channel}}, {{dev_dat_i.addr}}, {{dat_o.addr}}, {{tot_sz}},

{{trn_sz}});

""";

exec body C = """

dev2mem({{channel}}, {{dev_dat_i.addr}}, {{dat_o.addr}}, {{tot_sz}},

{{trn_sz}});

""";

```

### PSS code – Contd..

} cg; } }

UNITED STATES

```

component wb_dma_par4_xfer_c {

enum xfer_type_e {

mem2mem,

mem2dev,

dev2mem

action xfer a {

rand bit[3]

channel;

rand xfer type e

xt;

wb dma c::mem2mem a

m2m;

wb dma c::dev2mem a

d2m;

wb dma c::mem2dev a

m2d;

dma helper c::gendata a

gd;

dma_helper_c::checkdata a

cd;

dma helper c::dev sink a

dsi;

dma helper c::dev src a

dsr;

constraint channel c {

m2m.channel == channel;

m2d.channel == channel;

d2m.channel == channel;

activity {

match (xt) {

[mem2mem]: {gd ; m2m; cd; }

[dev2mem]: {

parallel { d2m; dsr; }

cd;

[mem2dev]: {

ad;

parallel { m2d; dsi; }

1

```

```

action scenario_top_a {

action wb dma par4 xfer c::xfer type e xt 1, xt 2, xt 3, xt 4;

action bit[3]

ch 1, ch 2, ch 3, ch 4;

xfer_a x1, x2, x3, x4;

constraint channel unique c {

unique {x1.channel, x2.channel, x3.channel, x4.channel};

1

activity {

repeat (40) {

xt 1; xt 2; xt 3; xt 4;

ch 1; ch 2; ch 3; ch 4;

parallel {

xl;

x2:

x3;

x4;

}}}

constraint xt cov c {

xt 1 == x1.xt; ch 1 == x1.channel;

xt 2 == x2.xt; ch 2 == x2.channel;

xt 3 == x3.xt; ch 3 == x3.channel;

xt 4 == x4.xt; ch 4 == x4.channel;}

covergroup {

xtl cp : coverpoint xt l; // Transfer type for xl

xt2_cp : coverpoint xt_2;

xt3_cp : coverpoint xt_3;

xt4 cp : coverpoint xt 4;

cl_cp : coverpoint ch_1; // Channel for xl

c2_cp : coverpoint ch_2;

c3 cp : coverpoint ch 3;

c4_cp : coverpoint ch_4;

xt_c_l_cross : cross xtl_cp, cl_cp;

xt_c_2_cross : cross xt2_cp, c2_cp;

xt_c_3_cross : cross xt3_cp, c3_cp;

xt_c_4_cross : cross xt4_cp, c4_cp;

```

### **DMA sequences**

task mem2mem( bit[31:0] channel, bit[31:0] src, bit[31:0] dst, bit[31:0] tot sz, bit[31:0] trn sz); wb dma descriptor desc = wb dma descriptor:: type id::create(); \$display("--> mem2mem"); desc.mode = 0;desc.inc src = 1; desc.inc dst = 1; desc.src sel = 0; desc.dst sel = 1; desc.tot sz = tot sz; desc.trn\_sz = trn\_sz; desc.chk sz = 16;desc.src\_addr = src; desc.dst addr = dst; start\_item(desc); finish item(desc); \$display("<-- mem2mem");</pre>

endtask

task dev2mem( bit[31:0] channel, bit[31:0] src, bit[31:0] dst, bit[31:0] tot\_sz, bit[31:0] trn sz); wb dma descriptor desc = wb dma descriptor:: type id::create(); \$display("--> dev2mem"); desc.mode = 0;desc.inc src = 0;desc.inc dst = 1; desc.src sel = 0;desc.dst sel = 1; desc.tot\_sz = tot\_sz; desc.trn sz = trn sz; desc.chk sz = 16;desc.src addr = src; desc.dst addr = dst; start item(desc);

finish\_item(desc);

\$display("<-- dev2mem");

endtask</pre>

| task <mark>mem2dev</mark> ( |                               |

|-----------------------------|-------------------------------|

| bit[31:0]                   | channel,                      |

| bit[31:0]                   | src,                          |

| bit[31:0]                   | dst,                          |

| bit[31:0]                   | tot_sz,                       |

| bit[31:0]                   | trn_sz);                      |

| wb_dma_descript             | or desc = wb_dma_descriptor:: |

| type_id::create             | 0 :                           |

| \$display("> m              | em2dev");                     |

| <pre>desc.mode = 0;</pre>   |                               |

| desc.inc_src =              | 0;                            |

| desc.inc_dst =              | 1;                            |

| desc.src_sel =              | 0;                            |

| <pre>desc.dst_sel =</pre>   | 1;                            |

| desc.tot_sz = t             | ot_sz;                        |

| desc.trn_sz = t             | rn_sz;                        |

| desc.chk_sz = 1             | 6;                            |

| desc.src_addr =             | src;                          |

| desc.dst_addr =             | dst;                          |

|                             |                               |

| <pre>start_item(desc</pre>  | );                            |

| finish_item(des             | c);                           |

\$display("<-- mem2dev");</pre>

endtask

accellera systems initiative

DESIGN AND VERIFICATION"

UNITED STATES

### DMA sequences- Contd..

endtask

```

virtual task finish item(

input uvm sequence item item,

input int set priority=-1);

uvm reg data t value;

uvm status e status;

wb dma descriptor desc;

wb dma 11 descriptor 11 desc;

wb_dma_ch ch;

addresses[$];

bit[31:0]

if (!$cast(desc, item)) begin

`uvm fatal(get name(), "Failed to cast item to

wb dma descriptor");

end

$display("--> Finish Item: channel=%0d", desc.channel);

m reg sem.get(1);

// Setup appropriate channel

ch = m_regs.ch[desc.channel];

if ($cast(ll desc, desc)) begin

setup ll transfer(ll desc, addresses);

end else begin

setup single transfer(desc, addresses);

end

m reg_sem.put(1);

$display(" SRC ADDR='h%08h", desc.src_addr);

$display(" DST ADDR='h%08h", desc.dst addr);

$display(" SRC IFC=%0d", desc.src_sel);

$display(" DST IFC=%0d", desc.dst sel);

// Now, wait completion

```

```

repeat(1000) begin

#10us;

m reg sem.get(1);

ch.CSR.read(status, value);

m_reg_sem.put(1);

if (value[11]) begin

$display("== DONE CSR='h%08h ==", value);

if (m_done_ap != null) begin

m done ap.write(desc);

end

break;

end

end

m_reg_sem.get(1);

ch.CSR.read(status, value);

if (!value[11]) begin

'uvm fatal(get name(), "DMA transfer failed to

terminate");

end

ch.CSR.read(status, value);

value[0] = 0;

ch.CSR.write(status, value);

m reg sem.put(1);

foreach (addresses[i]) begin

m mem mgr.free(addresses[i]);

end

addresses = {};

$display("<-- Finish Item %0d", desc.channel);</pre>

```

### **Capture Sequences in Golden Spec**

### **Capture Sequences in Golden Spec – Contd..**

## **Capture Sequences in Golden Spec – Contd..**

Steps of

sequences

iss.read(desc.channel,write st,'') iss.read(ch[write st].CSR,value,'' iss.write(value,value & 0xFFFFFFFE, iss.write(ch[write st].CSR, value, iss.read(ch[write st].A0,value,'' iss.read(ch[write st].A1,value,''] iss.write(ch[write st].A0,desc.src addr,'') iss.write(ch[write st].A1,desc.dst addr,'') iss.write(ch[write st].AM0,0xFFFFFFFC,'') iss.write(ch[write st].AM1,0xFFFFFFC,'') iss.read(ch[write st].SZ,value,'') iss.write(value,value & 0xFE00C000,'') iss.write(val[0], '(desc.trn sz == 4)?0:(desc.trn sz==2)?0:1',' iss.write(val[1],'(desc.trn sz == 4)?0:(desc.trn sz==2)?1:0', iss.write(val[0], val[0]<<12,'')</pre> iss.write(val[1], val[1] << 13, '') iss.write(chk sz, desc.chk sz<<16 , '')</pre> iss.write(tot sz, desc.tot sz) iss.write(read val, tot sz|chk sz|val[1]|val[0],'') iss.write(value, read val | value,'') iss.write(ch[write st].SZ,value,'') iss.read(ch[write st].CSR,value,'') iss.write(value, value & 0xFFFE1EE0,'') iss.write(channel, desc.channel<<13,'')</pre> iss.write(src sel, desc.src sel<<2,'')</pre> iss.write(inc src, desc.inc src<<4,'''</pre> iss.write(dst Sel, desc.dst sel<<1,''</pre> iss.write(inc dst, desc.inc dst<<3,'')</pre> iss.write(read val, channel|src sel|dst sel|inc dst|0x1|0x100|0x1 0000 [inc src,'') iss.write(value, value | read val, '') self.write analysis port(desc) iss.write(ch[write st].CSR, value)

### **Generated Sequences in the Target Format**

#### UNITED STATES value=ch Al ; task wb dma transfer seq::setup single transfer ( rm.ch[write st].A0.write(status, desc.src addr ); rm.ch[write st].Al.write(status, desc.dst addr ); wb dma descriptor desc rm.ch[write\_st].AMO.write(status, 'hFFFFFFFC); ); rm.ch[write st].AMl.write(status, 'hFFFFFFFC); uvm status e status; rm.ch[write st].SZ.read(status, ch SZ ); wb dma reg block rm = m regs ; const int clear\_val = 0 ; value=ch SZ ; bit [31:0]read val = 0 ; value = value & 'hFE00C000 ; lvar = desc.trn sz==4 ? 0 : (desc.trn sz==2 ? 0 : 1); bit [2:0]chnl = 0; val[0]=lvar; bit val[2] = {0,0} ; lvar = desc.trn sz==4 ? 0 : (desc.trn sz==2 ? 1 : 0); int write st = 0 ; val[1]=lvar; int value = 0 ; ead val = {1'b0,1'b0,1'b0,1'b0,1'b0,1'b0,desc.chk sz,1'b0,1'b0,val[1], int lvar; UVM [0],desc.tot sz}; uvm reg data t ch A0 ; uvm reg\_data\_t ch\_A1 ; r = read val | value; generated ue=lvar; uvm reg data t ch SZ ; uvm\_reg\_data\_t ch\_CSR ; ch[write st].SZ.write(status, value); sequences .ch[write st].CSR.read(status, ch CSR ); if (rm == null) begin 'uvm error("wb dma reg block block", "No register model s value=ch CSR ; sequence on, you should specify regmodel by using property value = value & 'hFFFE1EE0 ; in the sequence") chnl = desc.channel ; return; 1'b0,1'b0,1'b1,chn1,1'b0,1'b0,1'b0,1'b1,1'b0,1'b0,1'b0,desc.inc src,desc. end inc\_dst,desc.src\_sel,desc.dst sel,l'bl}; write st=desc.channel; lvar = value | read val; rm.ch[write st].CSR.read(status, ch CSR ); value=ch CSR ; value=lvar: lvar = value & 'hfffffffe: `uvm info("ISS", \$sformatf("== DMA Transfer %0d ==/n SRC: 'h%08h (%0d) inc=%0d/n DST: 'h%08h (%0d) inc=%0d/n SZ: %0d/n value=lvar; ", desc.channel, desc.src addr, desc.src sel, desc.inc src, desc.dst addr, desc.dst sel, desc. rm.ch[write st].CSR.write(status, value); rm.ch[write\_st].A0.read(status, ch\_A0 ); inc dst, desc.tot sz), UVM LOW); write analyis port(desc); value=ch A0 ; rm.ch[write\_st].Al.read(status, ch\_Al ); rm.ch[write st].CSR.write(status, value);

# Portability and connection to implementation level sequences

```

extend action wb_dma_c :: mem2mem_a {

exec body SV = """

mem2mem({{channel}}, {{dat_i.addr}}, {{dat_o.addr}}, {{tot_sz}}, {{trn_sz}});

""";

}

```

```

extend action wb_dma_c :: mem2mem_a {

exec body C = """

mem2mem({{channel}}, {{dat_i.addr}}, {{dat_o.addr}}, {{tot_sz}}, {{trn_sz}});

""";

}

```

### **Generated PSS code**

### **Creation of high-level test scenario**

68

|                    | // Register sequence with UVM factory                                                                            | 白      | <pre>function void registeraut();</pre>                                                |

|--------------------|------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------|

|                    | <pre>`uvm_object_utils(wb_dma_par4_seq)</pre>                                                                    | T.     | // Action tasks                                                                        |

|                    | typedef class functor;                                                                                           |        | <pre>virtual task actionTask(int id);</pre>                                            |

|                    | typedef class pcCallBack;                                                                                        | T.     | // Signed meta action tasks                                                            |

|                    | <pre>typedef class covergroup_action_wb_dma_par4_xfer_c_scenario_top_a_cg;</pre>                                 | L.     | virtual task signedMetaActionTask(                                                     |

|                    | // pss_exec class                                                                                                | T.     | // Unsigned meta action tasks                                                          |

| 由                  | <pre>class pss_exec;</pre>                                                                                       | L.     | virtual task unsignedMetaActionTask(                                                   |

|                    | // pss_exec_block class                                                                                          | T.     | // Unsigned meta action import functions                                               |

| 由                  | <pre>class pss_exec_block extends pss_exec;</pre>                                                                |        | <pre>virtual function longint unsigned unsignedMetaActionImportFunction(int id);</pre> |

|                    | // Execute PSS exec bodies in sequence                                                                           | T.     | // Trace entry function                                                                |

| 由                  | <pre>class pss_exec_seq extends pss_exec;</pre>                                                                  | L.     | virtual function void infact_trace_entry(int unsigned id);                             |

|                    | // Execute PSS exec bodies in parallel                                                                           | T.     | // Trace exit function                                                                 |

| 由                  | <pre>class pss_exec_par extends pss_exec;</pre>                                                                  | L.     | virtual function void infact_trace_exit(int unsigned id);                              |

|                    | // pss_exec_thread class                                                                                         | ۲.     | <pre>// Returns the cumulative coverage report of all coverages</pre>                  |

| 由                  | <pre>class pss_exec_thread;</pre>                                                                                | L.     | function string getCoverageReport();                                                   |

| 由                  | // fields of class wb_dma_par4_seq                                                                               | ۲.     | <pre>// Returns a true when all the individual coverage goals have been met</pre>      |

|                    | TestEngine m_te;                                                                                                 |        | function bit allCoverageGoalsHaveBeenMet();                                            |

|                    | // Graph name                                                                                                    | T.     | // Callback closure                                                                    |