# System level random verification: How it should be done

Madhusudan Rathi Senior Design Engineer, Analog Devices India

Ashok Chandran Engineering Manager, Analog Devices India

### Agenda

- Introduction

- Constraint development

- Tool performance optimization

- Control and debug

- Guideline for reuse

- Results and summery

acceller

SYSTEMS INITIATIV

### Introduction

- Industry trends

- Trends reveal more general purpose configurable designs.

- Support broader range of applications with the same silicon.

- Increasing number of use-cases and many unknown future applications.

- System level verification

- Typically restricted to connectivity checks between sub-blocks.

- Additionally, use-cases scenario verification using directed test approach.

- Constraint random verification(CRV)

- Widely accepted standard approach for block level verification.

- Helps in exercising known/unknown scenarios.

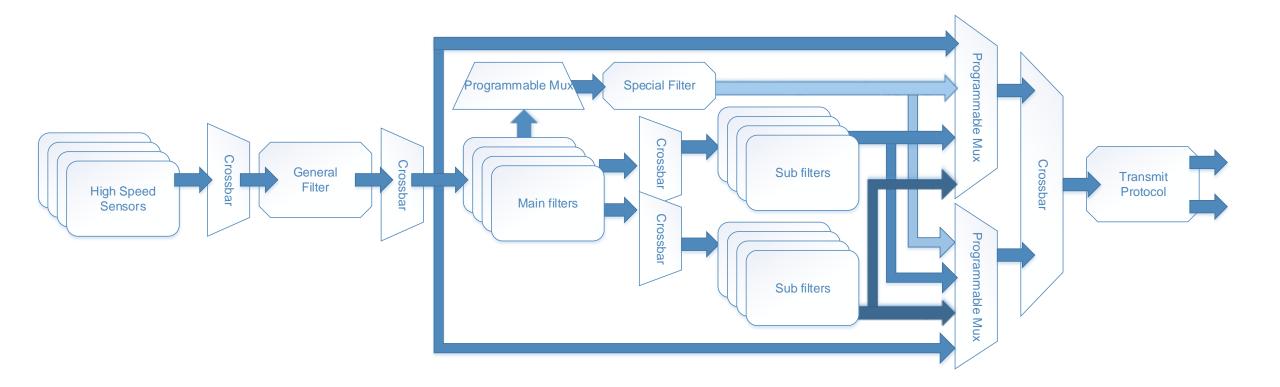

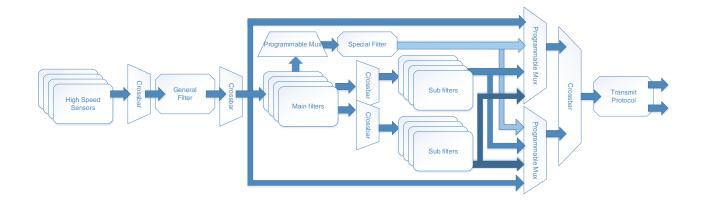

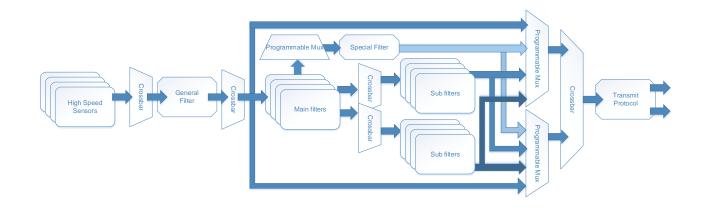

### Design block diagram

~2000 major known use-cases and many more possible usecases for the future.

- ~2000 major known use-cases and many more possible usecases for the future.

- Each use-case results in 10 unique possible combinations of data flow configuration.

- ~2000 major known use-cases and many more possible usecases for the future.

- Each use-case results in 10 unique possible combinations of data flow configuration.

- Each data flow configuration have the 100s of other parameters for randomization.

SYSTEMS INITIATIVE

#### Need for syster random

- ~2000 major known use-cases and many more possible usecases for the future.

- Each use-case results in 10 unique possible combinations of data flow configuration.

- Each data flow configuration have the 100s of other parameters for randomization.

- Required end to end checks for each configuration for signal integrity and deterministic latency.

More than 20,000,000 known design configurations to verify at system level

- For massive number of known use-cases, <u>directed test approach is extremely</u> <u>inefficient</u>.

- Complex data path clocking scheme makes DUT unsuitable for formal runs.

- Require complex properties and huge computation power.

- Signal processing and integrity checks for data path.

- Requirement for gate level simulation to catch synthesis constraints and multicycle issues.

- System level CRV approach is a must for thorough verification.

## Challenges with CRV approach at system level

- Development

- Extensive sets of constraints.

- Require systematic planning.

- Execution

- Huge solution space for constraint solver.

- Significant debug efforts.

- Sign off

- Adaptation to late design changes and new use-cases.

- Appropriate coverage bins for functional coverage.

## Challenges with CRV approach at system level

- Development

- Extensive sets of constraints.

- Require systematic planning.

- Execution

- Huge solution space for constraint solver.

- Significant debug efforts.

- Sign off

- Adaptation to late design changes and new use-cases.

- Appropriate coverage bins for functional coverage.

### Agenda

Introduction

#### Constraint development

- Tool performance optimization

- Control and debug

- Guideline for reuse

- Result and summery

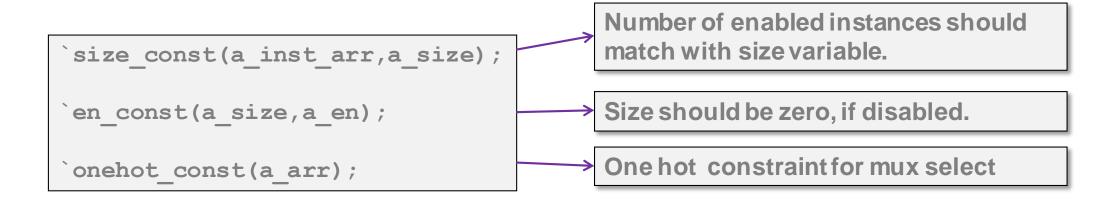

### Use of constraint macros

`size\_const(a\_inst\_arr,a\_size);

`en\_const(a\_size,a\_en);

`onehot\_const(a\_arr);

Number of enabled instances should match with size variable.

Size should be zero, if disabled.

**One hot constraint for mux select**

### Use of constraint macros

- Platform approach for uniformity in coding.

- Avoid typo and copy paste errors.

- Easy to update and audit.

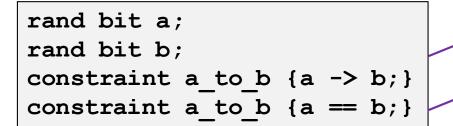

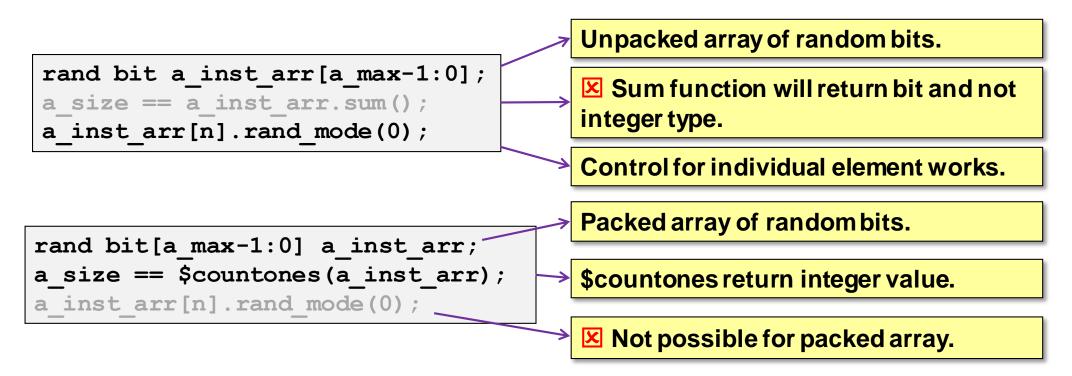

#### Recognize SV language limitations

Logical equivalent to (!a)|b

Logical equivalent to (ab) (!a!b)

| а | b | a -> b | a == b |

|---|---|--------|--------|

| 0 | 0 | True   | True   |

| 0 | 1 | True   | False  |

| 1 | 0 | False  | False  |

| 1 | 1 | True   | True   |

#### Recognize SV language limitations

Understanding of language limitation will enable reduction of global development and debug time.

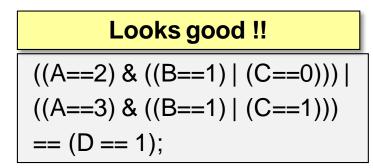

### Avoid ambiguous constraints

### Avoid ambiguous constraints

D

- Are you able find the difference between the two?

- X | Y == Z means (X | Y ) == Z or X | (Y == Z)

- Both are correct and interpretation depends on tool.

- Can we debug such issues quickly?

- Eliminate ambiguities with proper brackets as per intends.

| X | Y | Ζ | ( X   Y ) == Z | X   (Y == Z) |

|---|---|---|----------------|--------------|

| 0 | 0 | 0 | True           | True         |

| 0 | 0 | 1 | False          | False        |

| 0 | 1 | 0 | False          | False        |

| 0 | 1 | 1 | True           | True         |

| 1 | 0 | 0 | False          | True         |

| 1 | 0 | 1 | True           | True         |

| 1 | 1 | 0 | False          | False        |

| 1 | 1 | 1 | True           | True         |

### Agenda

- Introduction

- Constraint development

#### Tool performance optimization

- Control and debug

- Guideline for reuse

- Result and summery

### System level constraint issues

- Large solution space for system will consume significant computation power.

- 100s of parameter to randomize.

- Inter blocks dependencies for valid combinations.

- Like number of monitors depend on sensors count.

- Implementation complexity/trade off driven design constraints.

- Ex. Max. data rate at filter input.

- Frequency planning for valid outputs.

- Depends on input bands and mixers.

### **Divide and conquer**

- Partition of randomization based on functionalities and dependencies.

- Protocol and external interaction (transmit lanes, lane rates...).

- Data path, crossbar and muxes (number of filters, data source & destination...).

- Frequency planning for system (input bands, mixer frequencies...).

- Non data path parameters (GPIOs, interrupts...).

- Implementation details

- Individual, layered transactions for each partition.

- » Used layered approach for reuse.

- Transactions are randomized and passed to rest of transactions.

- » System sequence will order randomization among transaction and share as required.

- Result

- See ~30 times performance improvement.

- Help in debug for randomization failures.

Easy to update and maintain.

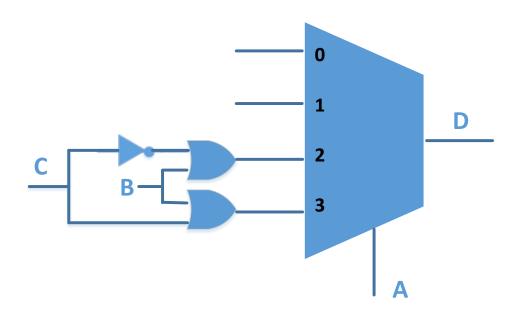

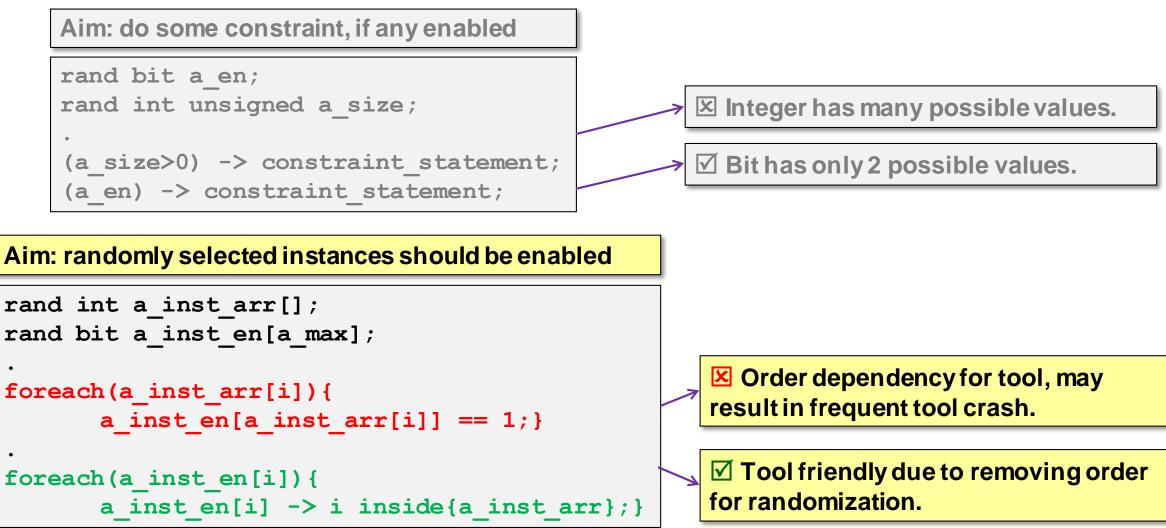

# Understanding the solution space with examples

Aim: do some constraint, if any enabled

rand bit a\_en;

rand int unsigned a size;

(a\_size>0) -> constraint\_statement; (a en) -> constraint statement; Integer has many possible values.

Bit has only 2 possible values.

# Understanding the solution space with examples

# Optimizing for the solver performance

- Recommendations

- Split system randomization in multiple steps.

- Search for possibilities in solution spaces reduction.

- Avoid indirect dependencies by rewriting constraints.

- Provide guidance to solver for order of randomization.

- Tools may have optimization for standard constraint statements.

- Redundant constraints may also help in performance improvement.

### Solution space (not the number of constraints) determines randomization time for the tool.

### Agenda

- Introduction

- Constraint development

- Tool performance optimization

#### Control and debug

- Guideline for reuse

- Result and summery

## Run-time control over constraints

- Problem

- Multiple request for the specific use-case scenarios during the project.

- Separate test for each request will be overkill.

- Require control over random variables and constraint blocks.

- Solution

- Enable or disable randomization in pre randomization phase.

- Use \$plusargs based run-time options and uvm\_config\_db to receive commands.

- Sample commands: +set\_sensor\_mode=1 +set\_main\_filter\_size=2 +set\_bypass\_path

- Ease to update and native method to provide support for various commands.

- Use macro defines for uniformity in run-time options.

- Separate constraint blocks for commonly required cases.

# Run-time control over constraints

- Run-time options based control became savior.

- Used by architecture, design, verification and silicon eval teams.

- Used for development, verification, mix signal cosim, coverage closure, power analysis, silicon debug and use-cases run.

- Result

- Help in serving many requested use-cases without writing alternative tests.

- Save compile time for each required use-case generation.

- Verification easiness

- Used to narrow down cause for randomization failures.

- Identifying constraints for the required functionality.

- Functional coverage analysis.

### **Functional coverage debug**

- Problem

- Functional coverage holes.

- Indicates given scenario is not covered.

- Cause

- Overly or wrongly constrained conditions and blocks.

- Insignificant runs for functional coverage sampling.

- Strategy to debug

- Use run-time options to force required combination.

- Conflicting constraint failure from tool help in identifying possible constraint issues.

- If no constraint failure means more runs are needed.

# Conflicts and invalid conditions

- Multiple times the bunch of commands result in invalid combinations.

- Result in randomization failure due to conflicting constraints.

- Significant unproductive efforts for various teams to understand and debug such failures.

- Early detection of run-time commands issue

- Error and conflicting conditions are known upfront to developers.

- Put conditional checks for them before randomization.

- Use rand\_mode() return value for identification of run-time options.

- Result in very specific failure message for such conditions.

### Agenda

- Introduction

- Constraint development

- Tool performance optimization

- Control and debug

- Guideline for reuse

- Result and summery

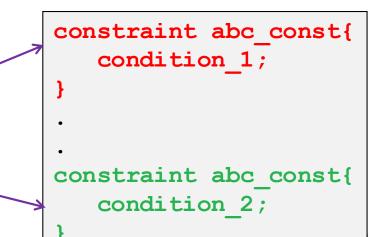

# Constraint reusability concerns

- Identifying constraint for the functionalities in "a sea of constraints".

- Refurbishing constraints for design changes.

- Missing constraint statements and blocks.

- Constraint block override.

- Language supports and useful in few cases.

- » Extended class can override base class constraints.

- Extremely error prone, if not intended.

- Difficult to avoid issue without upfront planning.

constraint block will be fully ignored by tool.

It will override previous constraint block.

### **Guideline for reuse**

| Guideline                                                                             | Improvement                                                                                                                                               |

|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| One constraint block for similar functionalities.                                     | <ul><li>Reduce risk of missing constraints.</li><li>Ease updating of code for design changes.</li></ul>                                                   |

| Name each constrained block using the dependent variables and specific functionality. | <ul><li>Avoid constraint blocks override issue.</li><li>Help in finding</li></ul>                                                                         |

| Ordering the constrained blocks as per order of programming or data flows in design.  | <ul> <li>Mitigate missing constraints issues.</li> <li>Promising way to debug and search constraints.</li> </ul>                                          |

| Use enums and macros instead of hardcoding value                                      | <ul><li>Easy understanding and debug for constraint.</li><li>Require minimum change for spec changes</li></ul>                                            |

| Appropriate comments before constrained blocks and code.                              | <ul> <li>Helps to understand and reuse.</li> <li>Effortless debug for constraint issues.</li> <li>Provide templates for similar functionality.</li> </ul> |

#### Efficiency in finding & understanding

#### $\Rightarrow$ Helps in update & debug

### Agenda

- Introduction

- Constraint development

- Tool performance optimization

- Control and debug

- Guideline for reuse

- Result and Summery

### Results

- Challenges: There are significant challenges in system level randomization and require <u>deep planning and a systematic approach</u> to complete it.

- Quality within time: We have successfully used a system level randomization approach to achieve our verification goals

- Uncovered <u>60+ bugs in system</u> before tape-out.

- We have unearthed many scenarios and design bugs using CRV, which were <u>not</u> <u>thought before</u>.

- Extensive silicon testing did not report any issues.

- **Impact:** Run-time option based use-case scenario generation is extensively used for silicon debug and <u>decreases overall time for silicon bring up</u>.

### Summery

- System level CRV approach provides significant automation to verification process.

- Optimal trade-off between Engineer time vs Computer resources.

Thank You !!

#### Thank you !!

#### **Backup slides**

### System level CRV approach v/s portable stimulus

- Limited advantages

- Due to aggressive schedule and insignificant returns, block level approach is not used in project.

- Other teams (software, silicon eval) were not ready to invest efforts.

- PS was not industry standard and hence had doubt about reusability in subsequent projects.

- Immature tool support.

- A couple of PS tools were evaluated and experienced inadequate results.

- Anticipated various tool issues and time consuming tool debug during project cycle.

- Significant efforts

- PS require significant efforts for team to learn and understand.

- SV is well known and minimum efforts required for team to understand, develop and debug.

- Since we need to code large number of constraints in limited time, native approach is preferred.

Finally we are working to bring up PS setup for the project.

accellera

SYSTEMS INITIATIVE

# Examples for standard constraint statements

Aim: randomly selected instances should be unique and enabled. rand int a inst arr[]; rand bit a inst en[a max]; foreach(a inst arr[i]){ if(a inst en[i]) -> (a inst arr[i] <= a max);</pre> foreach(a inst arr[j]){ if(i!=j) & a\_inst\_en[i] & a\_inst\_en[j]{ a inst arr[i] != a inst arr[j];} Unique(a inst arr); foreach(a inst arr[i]){  $(a inst arr[i] > max) \rightarrow a inst en[i] == 0;$

Complex loops create issue and suffer with tool performance hit.

✓ Tool may have optimization for standard constraint blocks.

# Examples of redundant constraint

Aim: each mux output should have respective one and only one input.

```

rand int a_size,b_size,c_size,d_size;

rand bit a[max],b[max],c[max],d[max];

```

```

foreach(a[i]){

a[i] == (b[i] | c[i] | d[i]);

`onehot_constraint({b[i],c[i],d[i]});

}

```

```

a_size == (b_size + c_size +d_size);

```

Constraints for mux output and only one selection for input.

✓ Redundant constraint on size to help tool.