#### Switch the Gears of the UVM Register Package to cruise through the street named "Register Verification".

Parag Goel Amit Sharma, Varun S, Abhisek Verma Synopsys paragg@synopsys.com amits@synopsys.com svarun@synopsys.com abhiv@synopsys.com

Gaurav Gupta Freescale Semiconductors

gauravG@freescale.com

## **Optimized Register Backdoor Access**

# High simulation performance as no PLI interactions

### Interface with read/write tasks for backdoor

```

endinterface

```

## Modified backdoor class using the interface tasks

/modified backdoor register PRT\_LCK class. class reg\_PRT\_LCK\_bkdr extends

```

uvm_reg_backdoor;

```

virtual host\_regmodel\_intf \_\_reg\_vif;

```

function new(string name);

super.new(name);

// initializing the virtual interface with

// the real interface

uvm_resource_db#

(virtual host_regmodel_intf)::

read_by_name(..., "uvm_reg_bkdr_if",

__reg_vif);

```

endfunction

```

virtual task read(uvm_reg_item rw);

do_pre_read(rw);

```

```

// performing a read access to register

__reg_vif.host_regmodel_PRT_LCK_bkdr_read(rw);

rw.status = UVM_IS_OK;

do_post_read(rw);

endtask

```

No HDL XMR ensures SystemVerilog package-able

endclass

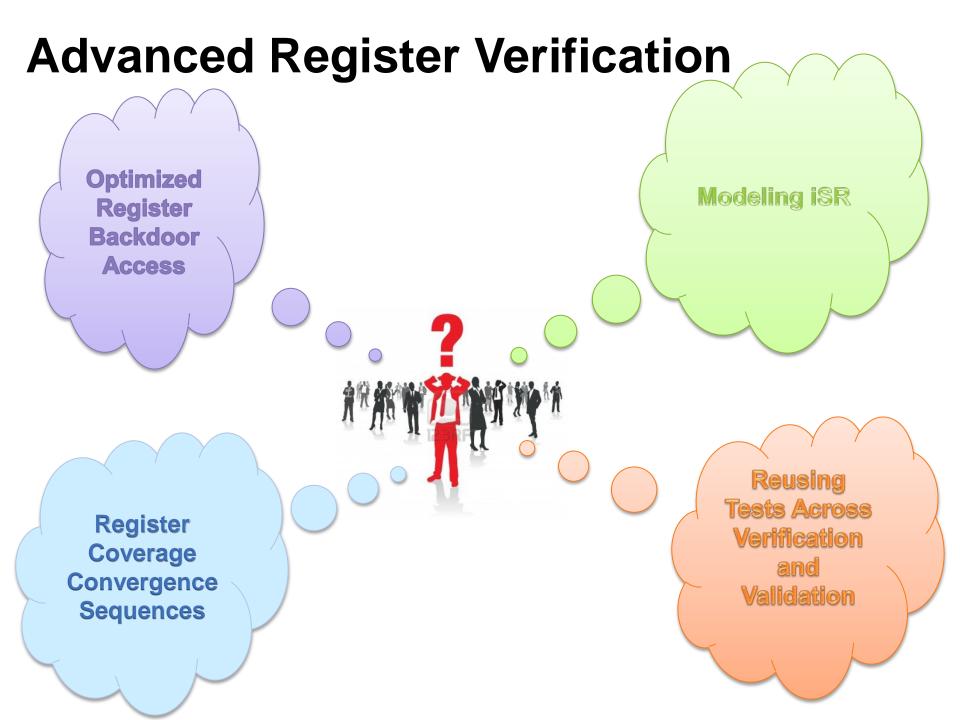

## **UVM REG Coverage**

#### Address map

- Have all address location in the map been accessed?

- Pre-defined sequences covers this.

#### **Bit -level**

- A regressive coverage that covers values for each bit position

- Pre-defined UVM register sequence will cover this too.

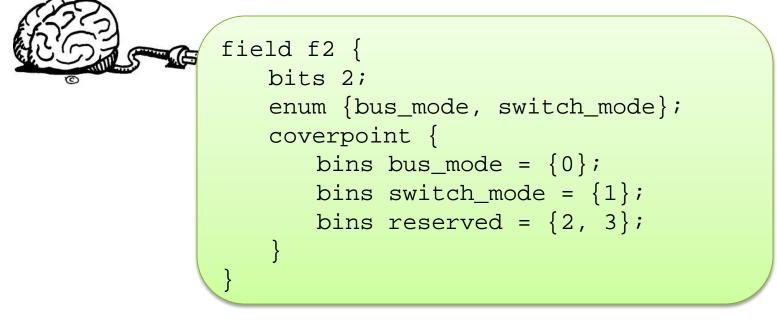

#### Field value

- Configuration value coverage for register fields.

- User written configuration sequences. A bottle neck!

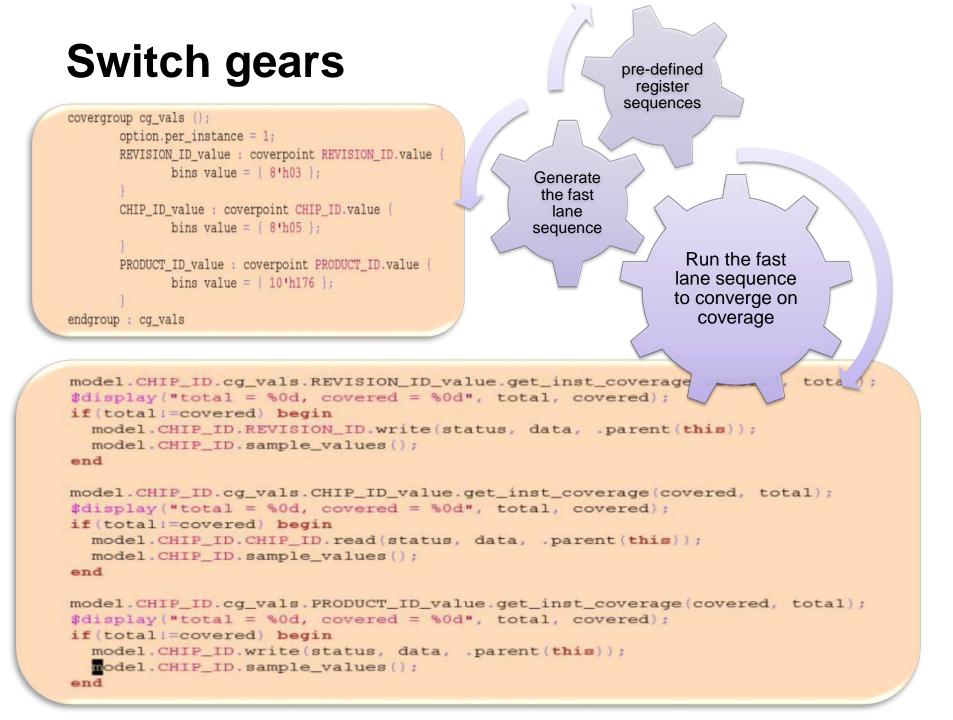

### Why need fast lane sequence?

### Aiding the fast lane sequence

Generate the field coverage models by mapping the respective bins to individual coverpoints. This ensures that more attributes of the model can be queried dynamically through the SV constructs

covergroup cg\_vals ();

option.per instance = 1

R\_ID\_value : coverpoint R\_ID.value {

bins value = { 8'h03 };

endgroup : cg\_vals

Hierarchical model of the coverage architecture enables traversal of the entire coverage model

```

task body();

model.ID.cg_vals.R_ID_value.get_inst_coverage(cov

ered, total);

if(total!=covered) begin

model.ID.R_ID.read(status, data,

.parent(this));

model.ID.sample_values();

end

endtask

```

## Let your register spec do the talking

• Embed configuration information into your register spec

• Enable the model generator to generate configuration sequences to cover all the cases.

## On the Fast Lane

SCORE INST SCORE WEIGHT

99.8

**Fotal groups in report:** 9

92.3

# Coverage After using Fast Lane sequence

| 66.67  | 66.67  | 1 | 100 | test::ral_reg_slave_CHIP_ID::cg_bits  |

|--------|--------|---|-----|---------------------------------------|

| 79.17  | 86.96  | 1 | 100 | test::ral_reg_slave_STATUS::cg_bits   |

| 85.71  | 85.71  | 1 | 100 | test::ral_reg_slave_STATUS::cg_vals   |

| 100.00 | 100.00 | 1 | 100 | test::ral_block_slave::cg_addr        |

| 100.00 | 100.00 | 1 | 100 | test::ral_reg_slave_MASK::cg_vals     |

| 100.00 | 100.00 | 1 | 100 | test::ral_reg_slave_CHIP_ID::cg_vals  |

| 100.00 | 100.00 | 1 | 100 | test::ral_reg_slave_MASK::cg_bits     |

| 100.00 | 100.00 | 1 | 100 | test::ral_reg_slave_COUNTERS::cg_vals |

| 100.00 | 100.00 | 1 | 100 | test::ral reg slave COUNTERS::cg bits |

UVM library provided base sequences were run and coverage was cumulatively collected over these runs.

> Coverage before using Fast Lane sequence

| 0.00  | 0.00   | 1 | 100 | test::ral_reg_slave_STATUS::cg_vals   |

|-------|--------|---|-----|---------------------------------------|

| 0.00  | 0.00   | 1 | 100 | test::ral_reg_slave_MASK::cg_vals     |

| 0.00  | 0.00   | 1 | 100 | test::ral_reg_slave_CHIP_ID::cg_vals  |

| 0.00  | 0.00   | 1 | 100 | test::ral_reg_slave_COUNTERS::cg_vals |

| 66.67 | 66.67  | 1 | 100 | test::ral_reg_slave_CHIP_ID::cg_bits  |

| 79.17 | 86.96  | 1 | 100 | test::ral_reg_slave_STATUS::cg_bits   |

| 00.00 | 100.00 | 1 | 100 | test::ral_block_slave::cg_addr        |

| 00.00 | 100.00 | 1 | 100 | test::ral_reg_slave_MASK::cg_bits     |

| 00.00 | 100.00 | 1 | 100 | test::ral_reg_slave_COUNTERS::cg_bits |

otal Groups Coverage Summary

1

SCORE INST SCORE WEIGHT

Total groups in report: 9

50.01

49.54

This was followed up with the auto-generated sequence which checked for the uncovered points and generated accesses to cover the remaining coverage holes.

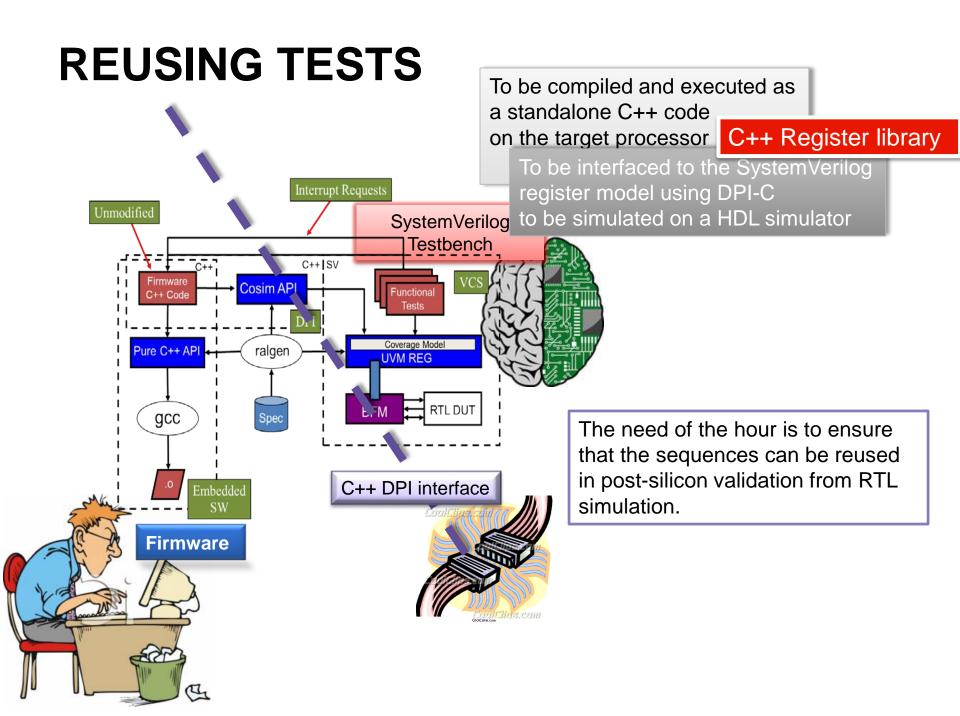

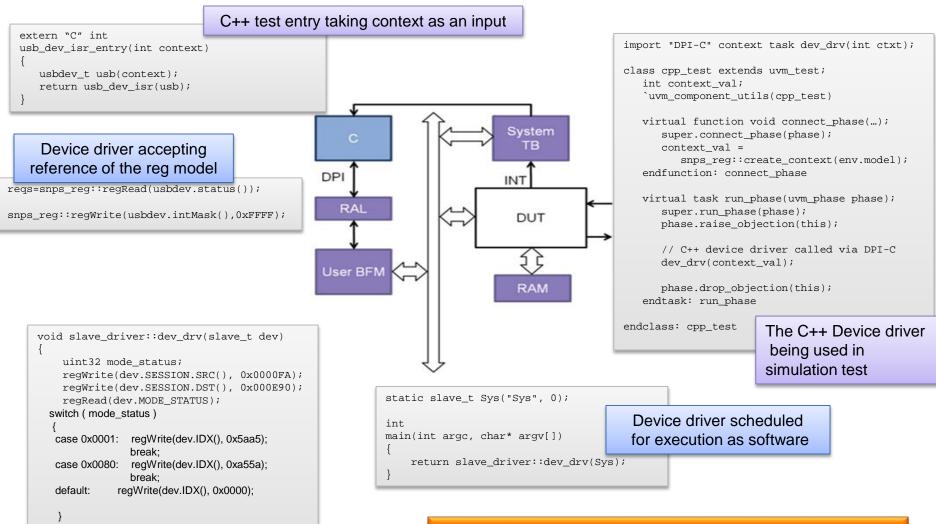

## **REUSING TESTS**

C++ device driver code

};

#### Environment for an interrupt-driven C++ interaction

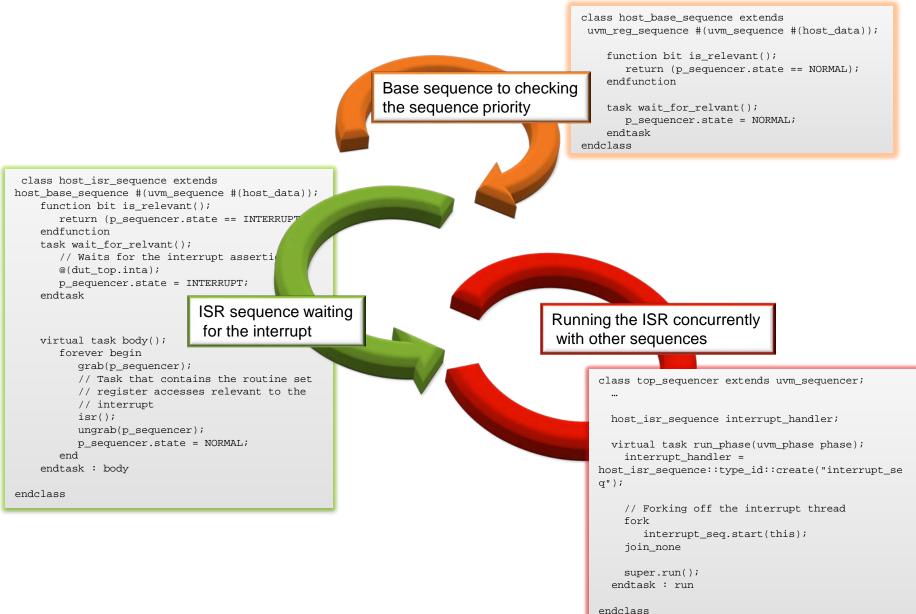

## **MODELING ISR**