# Successive Refinement – An approach to decouple Front-End and Back-end Power Intent

Rohit Kumar Sinha, Intel India, (rohit.kumar.sinha@intel.com)

Abstract—This IEEE 1801 UPF [1] format comes with a limitation that it doesn't entirely support decoupling of front and backend power intent files and as many SoC projects in Intel are marching towards ASIC products on different process technologies, it becomes all the more important for designers to code power intent with the process agnostic approach. Therefore, IEEE 1801-2015 UPF (UPF3.1) [2]has come up with a methodology called Successive refinement that supports Incremental specification. This methodology enables incremental design and verification of the power management architecture, and it is specifically designed to support specification of power management requirements for IP components used in a low power design. This incremental flow accelerates design and verification of the power management architecture using partition methodology wherein the power intent is partitioned into constraints, configuration and implementation. In this paper, we will present the POC for the new methodology Successive refinement implemented on CPUSS in which power intent is specified in a technology independent manner and verified abstractly before implementation

Keywords—IEEE 1801, power, methodology, UPF, implementation, Low Power, SoC.

#### I. INTRODUCTION

Use of IP in SOC's is essential in order to meet time-to-market requirements and leveraging existing technologies efficiently. So, designing the power management mechanism should involve both IP requirements and Soc concerns.

IEEE 1801 UPF follows an implementation-methodology that provides power-management structures and behavior for a design which drives both verification and Implementations steps. There are some problems with this methodology.

In this paper, we will present the new methodology Successive refinement in which power intent is specified in a technology independent manner and verified abstractly before implementation

Following are the Challenges of using Implementation-oriented UPF

- After investing a lot of verification effort to prove that the strategy and UPF file are correct, if the UPF file has to be

modified or re-created after selection of the target process technology, the verification equity built up is lost and the

verification process has to be repeated with associated delays and extra resource costs. so, power aware verification is

often is often postponed until late in the flow

- 2. IP's are re-used either in different soc's, different generation of same soc's or in different target technologies.so, if IP upf contains implementation details, it should be re-generated based on the customer's usage.

Successive Refinement addresses both of these issues. This methodology defines

- 1. How an IP provider can provide upf that specify constraints on the use of an IP component within a system, without knowledge of the characteristics of the system.

- How UPF can be used by the system integrator to specify the logical configuration of power management for the individual IP components used in the system and for the system as a whole. This enables early verification of the power management architecture before any implementation decisions are made.

- how UPF can be used by the system implementer to realize the power intent in the context of a given technology and implementation approach

The concept and methodology come with an idea of adding detailed description of power management in different

files by separating the logical functionality of power management for a system from the technology specific implementation of the system.

#### II. SUCCESSIVE REFINEMENT FLOW AND ITS CHALLENGES

Successive refinement in UPF allows an IP provider to capture the low power constraints inherent in an IP block without predicting a particular configuration. Then any customer who uses that IP can configure the IP, within these constraints, for their particular application without predicating a particular technology specific implementation. The result is a simulatable but technology-independent Golden source against which all technology specific implementations can be verified. In this way the verification of strategies and upf file need not be repeated even if implementation details change.

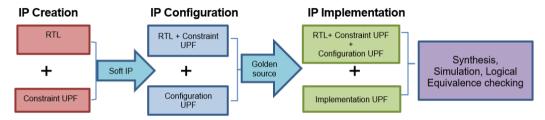

Figure 1 Successive Refinement Flow

#### SUCCESSIVE REFINEMENT ESSENTIALLY PARTITIONS THE UPF INTO THREE CATEGORIES

- A. Constraints UPF: The IP developer creates Constraint UPF. The constraint UPF file should not be replaced or changed by the IP consumer.

- Defines atomic power domains

- Define clamp value for (possible) ISO strategy

- Define retention elements for (possible) strategy

- Fundamental power states are defined without voltage value

**Note**: Retention, Isolation also is not actually specified in the constraint UPF file for an IP component. Implementation of retention, isolation is an implementation choice and is usually left for IP licensees to decide whether they would like to include it in their design. However, it is necessary to specify which state elements must be retained, isolated if the user decides to make use of retention, Isolation in his power management scheme.

1) Defining Atomic Power Domains:

The constraint UPF file defines each power domain that is identified in the specification for the IP component. The option –atomic indicates that this power domain cannot be further partitioned by the IP consumer.

Power domain can be defined as follows

Figure 2.1.1 Atomic power domains in constraint upf

2) Define Isolation Requirements:

Isolation is not actually specified in the constraint UPF file for an IP component. The constraint UPF file should specify the isolation clamp values that must be used if the user decides to shutdown portions of the system as part of this power management scheme.

The command 'set port attributes' is used to define the clamp value requirements:

Figure 2.1.2 Isolation Clamp Values

3) Define retention elements for strategy:

Specify the retention on the state elements if the user decides to make use of retention in his power management scheme. set retention elements retn list <name> -elements [list <Retention elements>]

4) Define power states without voltage value:

Figure 2.1.3 Fundamental power states

For constraint UPF, add\_power\_state should be used to define the fundamental power states of an IP block and its component domains in a technology-independent manner. This implies that power states should be defined without reference to voltage levels. Similarly, constraint UPF should not impose any particular power management approach on the IP consumer, so it should define power states without dictating how power will be controlled.

- B. Maintaining the Integrity of the Specifications

- C. Configuration UPF: The IP consumer adds Configuration UPF describing his system design including how all the IP blocks in the system are configured and power managed.

- Define design ports using create logic port

- Define ISO/RET strategies and how they are controlled

- Update power domain states with logic expressions using add\_power\_state -update

- 1) Define design ports

Add design ports that a design may use to control power management logic using create logic port

Figure 2.2.1 Logic port definition

#### 2.2.2 DEFINE ISO/RET STRATEGIES AND HOW THEY ARE CONTROLLED:

In the configuration file, an isolation strategy must specify clamp values consistent with the specifications in the constraint UPF.

Figure 2.2.2 Isolation Strategy

- 2.3 Implementation UPF: This UPF file is used to provide the implementation details and technology specific information that is needed for the implementation of the design.

- Define supply and network elements for the design

- Defining Power Switches

- Connecting supply nets with supply sets

- Define Supply Voltages in power states

## 2.3.1 DEFINE SUPPLY AND NETWORK ELEMENTS FOR THE DESIGN:

```

______

# Create Supply Port

______

create_supply_port $SOC_VDD_CPU

-direction in

#create_supply_port $SOC_VDD_SRAM

-direction in

create supply port $SOC GROUND

-direction in

------

# Create Supply Net

______

create_supply_net $SOC_VDD_CPU

#create_supply_net $SOC_VDD_SRAM

create_supply_net $SOC_VDD_1V1_TS_CPU

create_supply_net $SOC_VDD_1V8_PLL_A55

```

Figure 2.3.1 Supply nets and Supply ports

## 2.3.2 Defining Power Switches

This methodology requires IPs to no longer create power switches and it's up to the SOC Integrator to handle all the validation

```

______

# Power switchs

set nPWRUPCPU_HAMMER_PDSYS big_little_cluster/CLUSTER/nPWRUPCPU_HAMMER_PDSYS

set nPWRUPCPU_TRICKLE_ACK_PDSYS big_little_cluster/CLUSTER/nPWRUPCPU_TRICKLE_ACK_PDSYS_DSU

set nISOLATECPU_PDSYS big_little_cluster/CLUSTER/nISOLATECPU_PDSYS

create_power_switch ps_PDSYS_main -domain PDSYS \

"VDD SS_${SOC_VDD_CPU}_CLUSTER_GATED.power" \

"TVDD SS_${SOC_VDD_CPU}.power" \

-output_supply_port

-input_supply_port

-control_port

[list NSLEEPIN1 $nPWRUPCPU_HAMMER_PDSYS]

-control_port

[list NSLEEPIN2 $nPWRUPCPU_HAMMER_PDSYS]

on_state

{ on TVDD { NSLEEPIN1 & NSLEEPIN2 }} \

-off_state

{ off

{ !NSLEEPIN1 | !NSLEEPIN2 }}

```

Figure 2.3.2 Power switches

## 2.3.3 Connecting supply nets with supply sets:

The option –update is used to add the names of the supply nets to be connected to functions power, ground of the respective supply set

```

# Create Supply Set

create_supply_set SS_$SOC_VDD_CPU

-update

-function "power $SOC_VDD_CPU"

-function "ground $SOC_GROUND" -function "pwell $SOC_GROUND" -function "nwell $SOC_VDD_CPU"

create_supply_set SS_${SOC_VDD_CPU}_CLUSTER_GATED -update -function "power ${SOC_VDD_CPU}_CLUSTER_GATE

-function "ground $SOC_GROUND" -function "pwell $SOC_GROUND" -function "nwell $SOC_VDD_CPU"

Figure 2.3.3 supply sets

______

# Connect Supply Net

connect_supply_net $SOC_VDD_CPU

-ports $SOC_VDD_CPU

-ports $SOC_VDD_SRAM

#connect_supply_net $SOC_VDD_SRAM

connect supply net $SOC GROUND

-ports $SOC GROUND

connect_supply_net $SOC_VDD_1V1_TS_CPU

-ports $SOC_VDD_1V1_TS_CPU

Figure 2.3.4 supply nets

```

riguic 2.3.4 supply lice

## 2.3.4 Define Supply Voltages in power states

Figure 2.3.5 power states

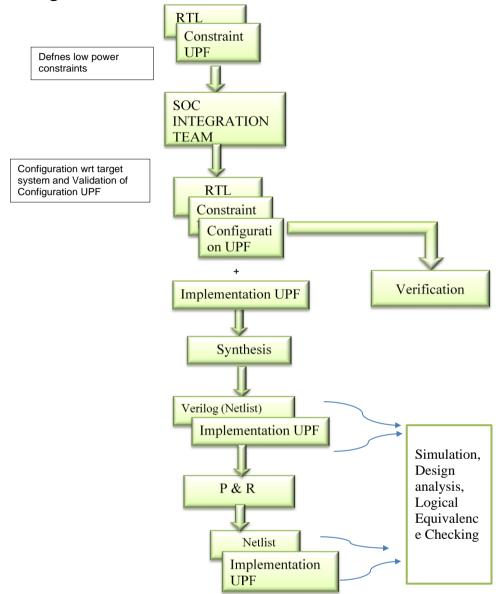

# Flow diagram

Figure 3. Design Low Power Flow Diagram with Successive refinement flow

III. RESULTS- SUCCESSIVE REFINEMENT UPF METHODOLOGY USAGE IN SOC COMPUTE DIE

SOC accepted IP power intent either:

- 1. In process and project agnostic way using "successive refinement" methodology

- 2. Or in aligned with project SD and topology using traditional delivery

Internal IP delivered UPF following the first approach. UPF commands and options were limited by currently supported by all Synopsys and Cadence flow tools. IP level validation was limited by tools as well.

- All layers (including implementation) were required for logic validation and simulation. LRM claims implementation portion only for structural design.

- Only UPF2.1 commands and options are used. E.g., associate\_supply\_set command -handle option was used to connect SOC with IP supplies. UPF \*logic\* commands were not used.

• Updating of power state (add\_power\_state) with -illegal option was not allowed by tools. To avoid conflict between IP and SOC PST last one was disabled after integration for structural design.

SOC used bottom up approach and consumed IP integration wrapper, which included constraint and configuration files. SPA with driver/receiver supply were put to configuration part. Most of configuration IP UPF were not updated by SOC (except removing redundant ISO after disabling internal gated PD). Implementation layer one per SD entity (e.g., partition) was automatically created by SOC. Partition UPF looks schematically:

load IP#1\_wrapper.upf -scope IP#1 load IP#2\_wrapper.upf -scope IP#2

•••

load IP#N\_wrapper.upf -scope IP#N source partition implementation.upf

SOC added automatically inter IP ISO/ELS layers (SOC added ISO between IP, having a logic on gated supply and interface on un-gated was not required). It allowed to simplify most of small IP and produce them with a single power supply. UPF delivery (except one command with clamp value) for the last type of IP was not required.

• IP UPF in "successive refinement" format keeps backward compatibility with traditional way. All layers (including implementation) produce the same traditional UPF: the same content is described by about the same commands are specified in different order and in incremental way.

## IV. SUMMARY

In SoC, we have implemented successive refinement methodology to decouple front-end UPF from BE-UPF and it was successfully accepted. Also, we have piloted it on CPUSS design and work is in progress to scale it to multiple subsystems.

Below are some of the highlights

- A UPF power intent specification for a SoC with multiple IPs having different levels of physical hierarchical implementation and UPF specifications was created

- The UPF specifications for individual IPs were verified for structural checks through static checks and formal methods.

- The power models created for memories and PHY were elegant and re-use of the power model was achieved in the successive refinement process.

- The power intent of hard macros is modelled with power states for the hard macro.

- The higher-level interface of each IP was modelled through port attributes based on UPF interface scenario IP or system level

- Each IP con be verified with the UPF in their block level verification environment and at the top level using the SoC level verification environment.

- The use of UPF for IP block verification, IP *hard macro* implementation, SoC verification and SoC implementation was seamless with no changes to the IP or SoC UPF between processes

## 5 GLANCE TO THE FUTURE

At present not all tools support all the constructs required for Successive Refinement, but it is expected that this issue will go away with time. The IEEE P1801 UPF working group is continuing to refine the definition of UPF in order to support Successive Refinement more effectively. In particular, improvements in power state definition and refinement are being developed for inclusion in the next release of the standard. These improvements should make adoption and use of Successive Refinement even more straightforward than has been described above

## 6 ACKNOWLEDGEMENT

Thanks to HPG management, UPF work group and IOTG Design Team for constantly supporting and providing various technical guidelines

## 7 REFERENCES

- [1] IEEE Std 1801<sup>TM</sup>-2009, "IEEE Standard for Design and Verification of Low-Power Integrated Circuits," 27 March 2009. [Online].

- [2] IEEE Std 1801<sup>TM</sup>-2015, "IEEE Standard for Design and Verification of Low-Power, Energy-Aware Electronic Systems," 5 December 2015. [Online].

- [3] A. Khan, J. Biggs, E. Quigley and E. Marschner, "Successive Refinement: A methodology for incremental specification of power," DVCON, March 2015.