## Static Checking for Correctness of Functional Coverage Models

Wael Mahmoud

- Introduction

- Functional coverage closure problems

- Static enhancements of functional coverage models

- Part A: Enhancements of input/output functional coverage

- Part B: Enhancements of design-centric functional coverage

- Results and conclusion

### Introduction

- Today's designs are getting more bigger and more complex (SoC and ASIC)

- Achieving fully verified SoC is an arduous task.

- Recent industry studies, shows that the average total project time spent in verification was 57%.

- Number of projects that spent more than 80% of time in verification has been increased from the past.

### Motivation

- The intent of verifying "SoC" is to ensure that the design is an accurate representation of the specification.

- Functional coverage provides visibility into the verification process.

- Writing a complete, correct, and concise functional coverage models, that conform design functionality to specs.

- Accelerate functional coverage closure.

- Assist verification teams with techniques to write concise functional coverage models.

- Introduction

- Functional coverage closure problems

- Static enhancements of functional coverage models

- Part A: Enhancements of input/output functional coverage

- Part B: Enhancements of design-centric functional coverage

- Results and conclusion

### Functional coverage closure problems

- Functional coverage closure can't be achieved due to many problems, like:

- 1. Problems with input stimuli, like: incomplete, insufficient, and/or redundant stimuli

- 2. Incorrect implementation of functional coverage model.

- 3. Non-optimized forms of functional coverage.

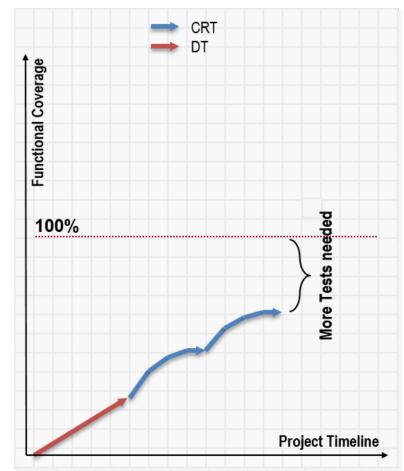

## 1- Incomplete/redundant input stimuli

- Write more directed tests to cover specific corner case scenarios.

- Run test cases multiple times with different random seeds, and hope more interesting scenarios are covered.

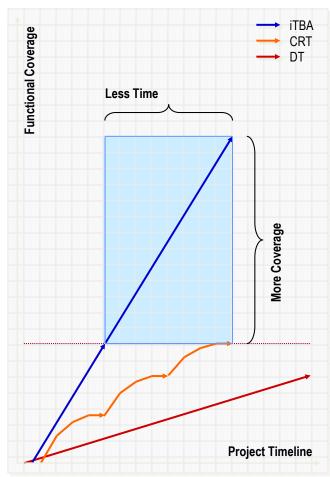

- Alternatively, try out other methodologies (e.g. intelligent test-bench automation "iTBA" tools) when applicable.

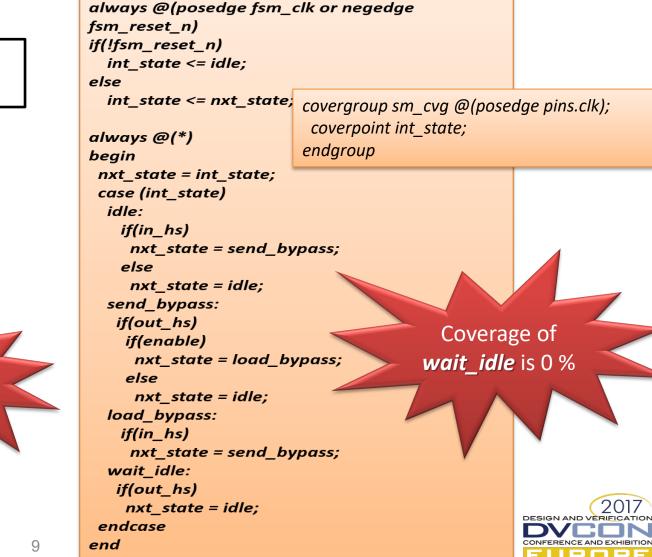

# 2- Incorrect implementation of functional coverage model

- Functional coverage model is contradicting with test-bench's or design's constraints.

- The proposed methodology will shows that there are no possible solutions.

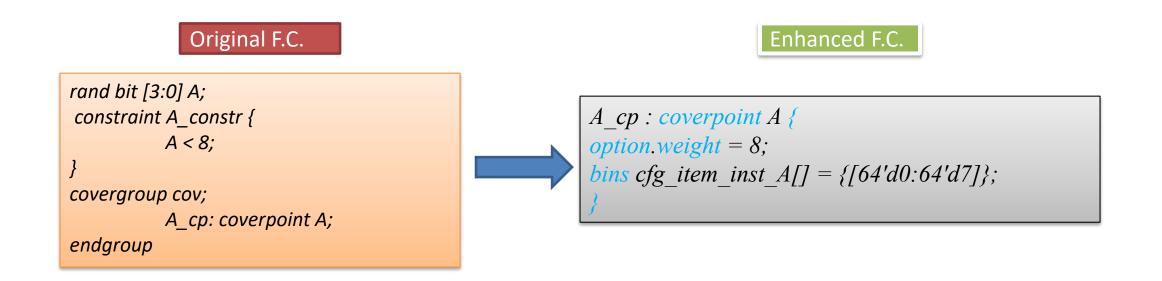

### 3- Non-optimized forms of functional coverage

**Design-centric functional coverage**

Functional coverage model is not written in an optimized form (i.e. it is not considering unreachable bins). Input functional coverage rand bit [3:0] A; constraint A constr { A < 8: Coverage of **A\_cp** is 50 % ... covergroup cov; A cp: coverpoint A; endgroup accellera

© Accellera Systems Initiative

SYSTEMS INITIATIVE

- Introduction

- Functional coverage closure problems

- Static enhancements of functional coverage models

- Part A: Enhancements of input/output functional coverage

- Part B: Enhancements of design-centric functional coverage

- Results and conclusion

### Static enhancements of functional coverage models

This paper proposes a complete framework to enhance functional coverage models of both *"input/output"* and *"design-centric"*

#### <u>"Part A"</u>

Intelligent test-bench automation (iTBA) tool, which internally use constraint solver technologies, is used to enhance "input/output" functional coverage model

#### <u>"Part B"</u>

Formal-based coverage analysis tool, which internally use formal-based analysis, is used to enhance "design-centric" functional coverage model

### Intelligent test-bench automation (iTBA) tools

- iTBA tools achieves input coverage 10-100x faster than random stimulus.

- More than 100x productive than directed test

- It provides an efficient description of stimulus scenarios

- It reduces time spent in writing testbenches

- Mote than 10X efficient than constrained random tests

- No redundant tests

- It helps to find tough corner case bugs easier and earlier

- This paper is using iTBA tool to enhance input/output functional coverage models.

# Part A: Enhancements of input/output functional coverage (1/3)

Import the test-bench into Questa inFact

Questa inFact automatically extracts test-bench's variables, constraints of stimulus class and functional coverage model

Internally solving all variables contributing in functional coverage item against the testbench's constraint

Generate an enhanced functional coverage model

# Part A: Enhancements of input/output functional coverage (2/3)

DESIGN AND VERIF

### Part A: Enhancements of input/output functional coverage (3/3)

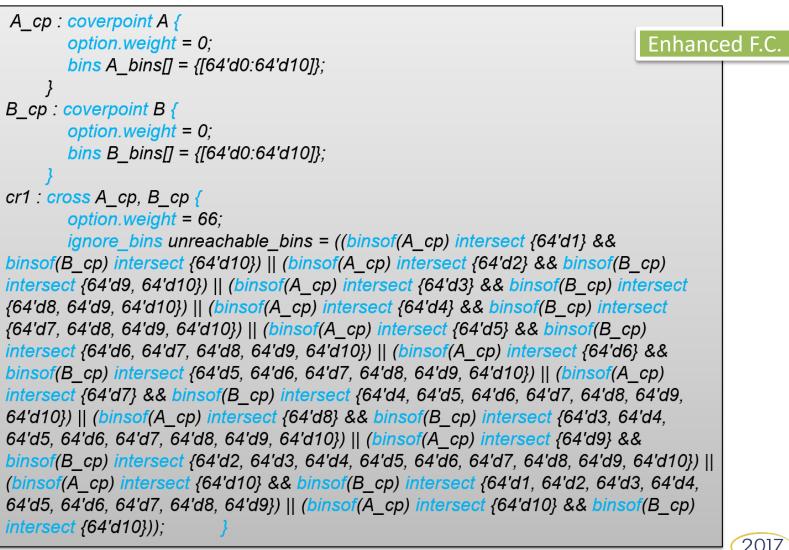

#### Original F.C.

covergroup cov; A\_cp: coverpoint A; B\_cp: coverpoint B; cr1: cross A\_cp, B\_cp; endgroup

DESIGN AND VERIE

- Introduction

- Functional coverage closure problems

- Static enhancements of functional coverage models

- Part A: Enhancements of input/output functional coverage

- Part B: Enhancements of design-centric functional coverage

- Results and conclusion

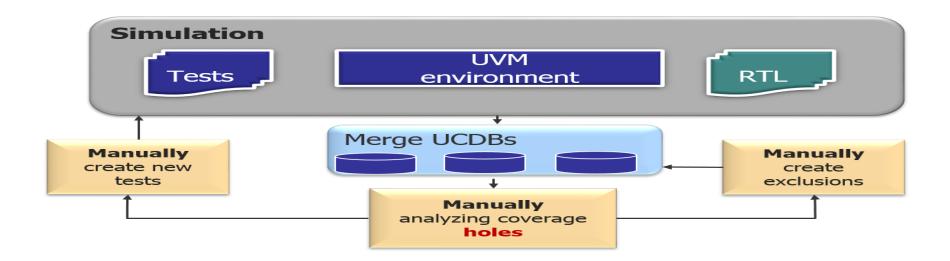

### Manual coverage closure (design-centric)

Manual Coverage Closure challenges

- □ Coverage verification is to verify that coverage goal is achieved in simulation

- Testing all possible scenarios and states are generally so hard

- □ Coverage holes indicate:

- Some blocks, states and transactions in the design are unreachable

- Some coverage items are reachable with complex test scenarios

- □ Huge effort and time are consumed to determine unreachable code and to create complex tests

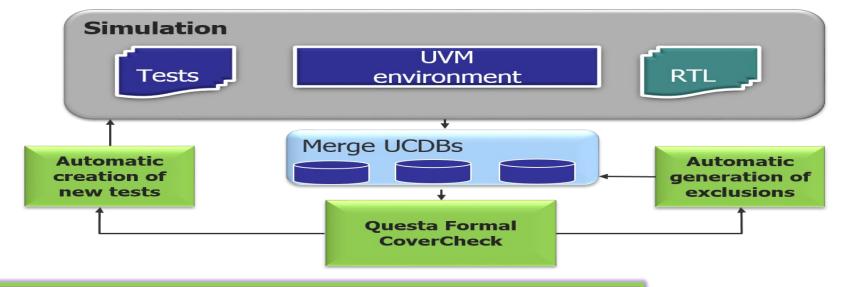

# Coverage closure using formal-based analysis (design-centric)

Formal-based analysis tool for automatic Coverage Closure

- □ Save time that would been spent for manually analyzing coverage holes

- □ CoverCheck provides an automatic solutions for the Coverage Closure challenges

- ✓ Automatically exclude coverage items for unreachable code

- ✓ Automatically generate Witness waveforms for reachable code

□ Customers can easily improve the code and the tests for better coverage metrics

DESIGN AND VERIFICA

NFERENCE AND EXHIBITION

# Part B: Enhancements of design-centric functional coverage

Run Questa CoverCheck on DUT and pass the UCDB generated from a simulation run

Questa CoverCheck automatically analyzes DUT for formal/static reachability using formal-based analysis

Exclusions file is generated with unreachable functional coverage bins, which is applied to simulation UCDB to exclude unreachable functional coverage

DESIGN AND VERIFIC

- Introduction

- Functional coverage closure problems

- Static enhancements of functional coverage models

- Part A: Enhancements of input/output functional coverage

- Part B: Enhancements of design-centric functional coverage

- Results and conclusion

### Results

|   |                                          | Input                     | /Output F.C.                                |                                          |                                                                                      | Design-Ce                                      | ntric F.C.                                      |                        |

|---|------------------------------------------|---------------------------|---------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------|-------------------------------------------------|------------------------|

|   | Coverage item<br>name                    | Туре                      | Coverage results<br>without new<br>approach | Coverage results<br>with new<br>approach | Coverage item name                                                                   | Туре                                           | Coverage results<br>without new<br>approach     | Cov<br>result<br>new a |

|   | up_cvg::upcov<br>_data                   | Cover-<br>point           | 0.7%                                        | 100%                                     | sm_cvg::int_state                                                                    | Cover-<br>point                                | 92.3%                                           | 9                      |

| 2 | up_cvg::upcov<br>_sync                   | Cover-<br>point           | 40%                                         | 100%                                     | sm_cvg::in_hsXint_state                                                              | Cross                                          | 46.1%                                           | 92                     |

|   | up_cvg::up_d<br>elay                     | Cover-                    | 95%                                         | 100%                                     | sm_cvg::out_hsXint_state                                                             | Cross                                          | 46.1%                                           | 10                     |

|   | Clay                                     | point                     |                                             |                                          |                                                                                      |                                                |                                                 |                        |

|   |                                          | point                     |                                             |                                          |                                                                                      |                                                |                                                 |                        |

|   | Coverage iten<br>name                    | n Ty                      | pe Coverage res<br>without no<br>approac    | ew results with<br>n new approach        | Coverage item name                                                                   | Туре                                           | Coverage<br>results without<br>new approach     | r                      |

|   | Coverage item<br>name<br>ethmac_rxtx_sec | n Ty<br>q_c Cove          | without no<br>approact<br>r- 85.9%          | ew results with                          |                                                                                      |                                                | results without<br>new approach                 | resu<br>r<br>apr       |

|   | Coverage iten<br>name                    | n Ty<br>q_c Cove<br>point | r- 85.9%<br>r- 84.4%                        | ew results with<br>n new approach        | Coverage item name<br>HASH0_1_Cvg::BYTE2<br>HASH0_1_Cvg::BYTE3<br>HASH0_1_Cvg::BYTE4 | Type<br>Cover-poin<br>Cover-poin<br>Cover-poin | results without<br>new approach<br>0.7%<br>0.7% | resu<br>r              |

2017 DESIGN AND VERIFICATION\* DVCCONFERENCE AND EXHIBITION

EUROPE

### Functional coverage development become easier

#### **Testbench constraints**

• Automatically exclude unreachable coverage bins, and provide concise forms of F.C., which leverage coverage results

#### **Design conditions**

• Automatically exclude unreachable bins, which leads to improve DUT for better coverage metrics

#### Detect conflicts

• Constraints and original functional coverage conflict can be easily detected

#### Minimize manual mistakes

• Manual writing of exclusion bins is a common source of mistakes

### Conclusion

- Writing complete, correct, and concise functional coverage models to verify the correctness of SoC is a challenging task.

- The proposed methodology uses constraint solvers and formal-based analysis to enhance functional coverage models.

- The proposed methodology is helpful in writing correct and concise functional coverage models.

- The proposed methodology helps verification engineer to start writing functional coverage models, or re-calibrate existing coverage metrics.

- Proposed methodology saves effort and time to determine unreachable code or coverage bins.

### Thank You!

### Any questions?