### Software Driven Test of FPGA Prototype Methods & Use cases

Krzysztof Szczur, Aldec Inc. Radosław Nawrot, Aldec Inc.

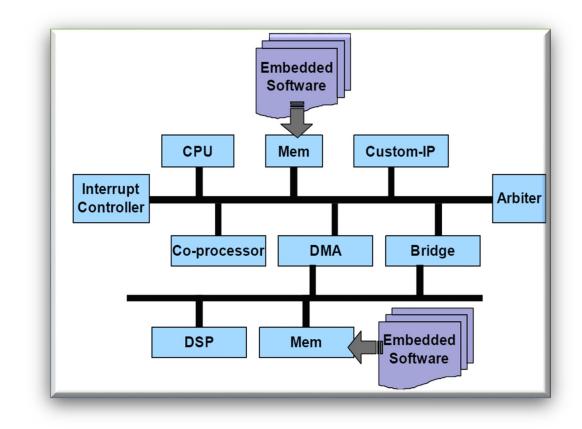

### Motivation - SoC verification challenge

- SoC = Hardware + Software

- both need verification

- software on critical-path (schedule risk)

- Complex architecture

- Hierarchical Network-on-Chip (NoC)

- Corner case hardware/software bugs

- Re-usable IPs: CPU, MEM, DMA, ...

- RTL code not available for FPGA prototyping

- Custom IPs: Co-processors, Function accelerators

- Often need late hardware debugging

# **Tutorial Agenda**

- Software driven v.s. traditional

- FPGA Technology enabling software driven verification

- Embedded software driven testbench application examples with HES-US-440

- Using HES Proto-AXI host interface

- Bare metal approach

- Software driven testbench in simulation

- QEMU co-simulation with Riviera-PRO

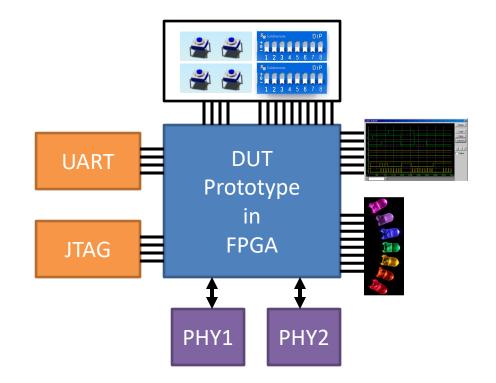

# Traditional Prototyping Bench

- Controllability & Configuration

- Dip switches

- Push buttons

- UART or JTAG ports

- Status & Debug

- LED & Panels

- Logic analyzers

- Live data streams

- PHY components

- Peripheral devices

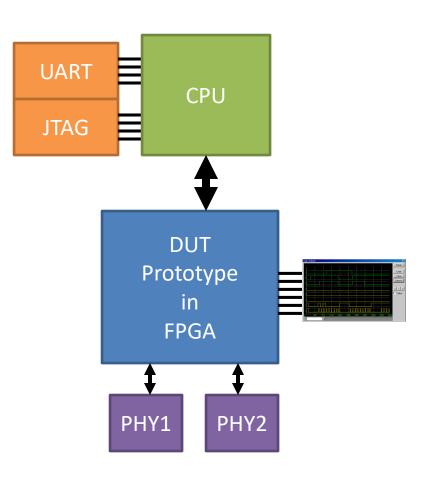

### Software Driven Testbench (SDT)

- Controllability & Configuration

Use CPU

- Status & Debug

- Use CPU

- Logic analyzers (external & on-chip)

- Live data streams

- PHY components

- Peripheral devices

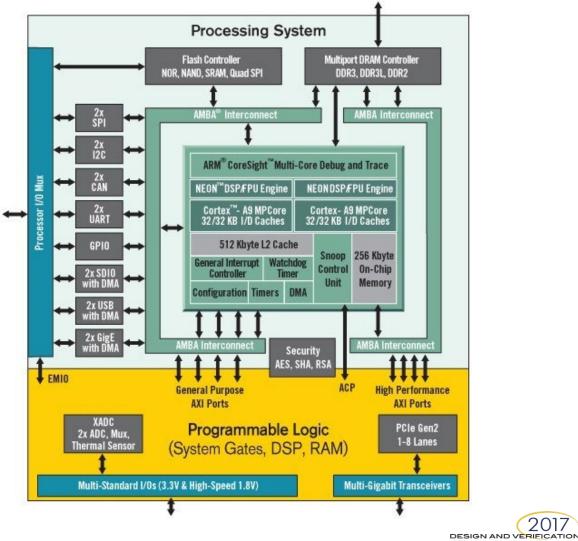

# FPGA Technology Enabling SDT

### Xilinx Zyng and the like...

- Processing System

- ARM Cortex CPU

- Standard I/O peripherals

- Programmable Logic

- Classic FPGA used for:

- More peripherals

- Glue logic & Bridge

2017

ONFERENCE AND EXHIBITION

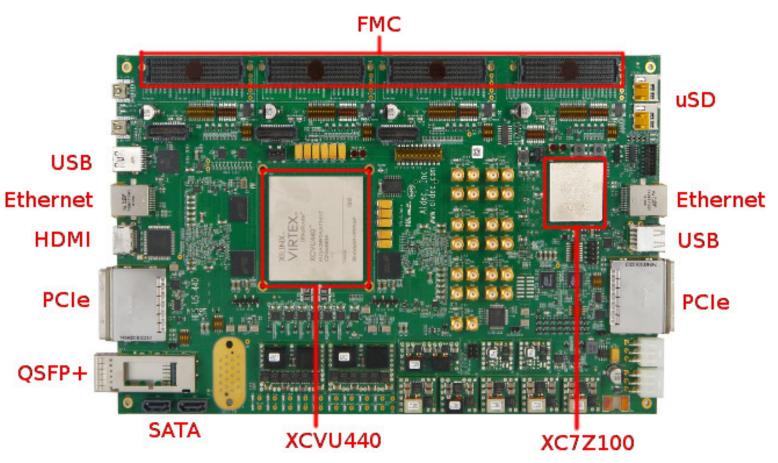

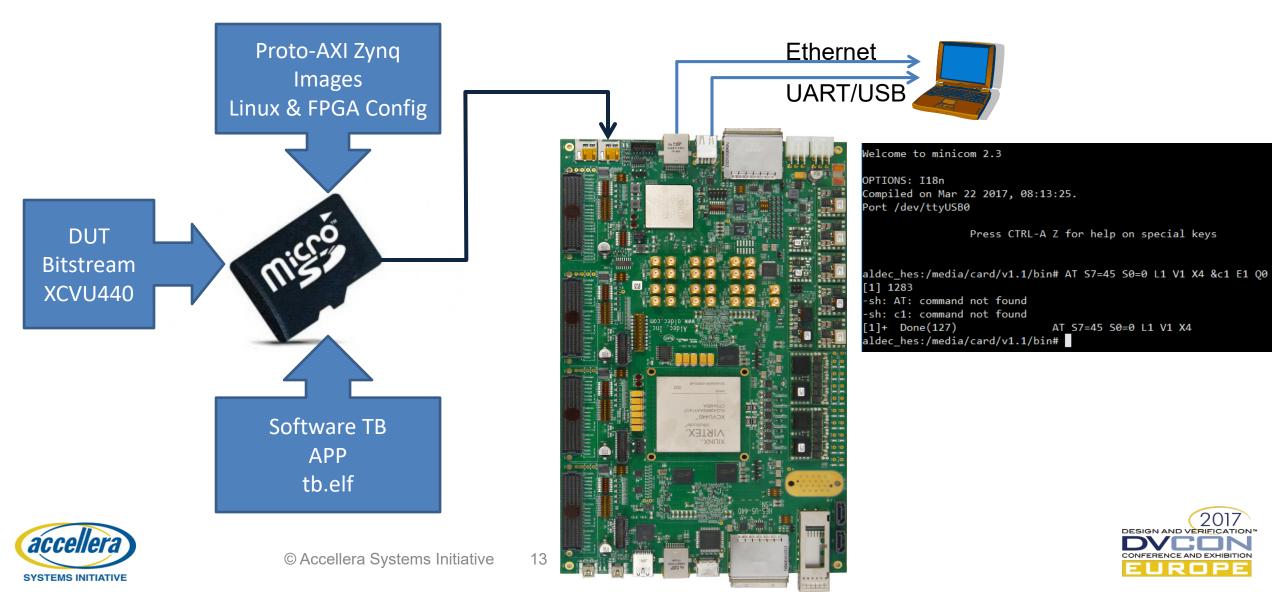

### Aldec HES-US-440

- Main FPGA:

- Virtex UltraScale™ XCVU44

- 26 Million ASIC Gates

- Host FPGA

- Zynq-7000, XC7Z100

- CPU: ARM Cortex A9

- FPGA: Kintex-7

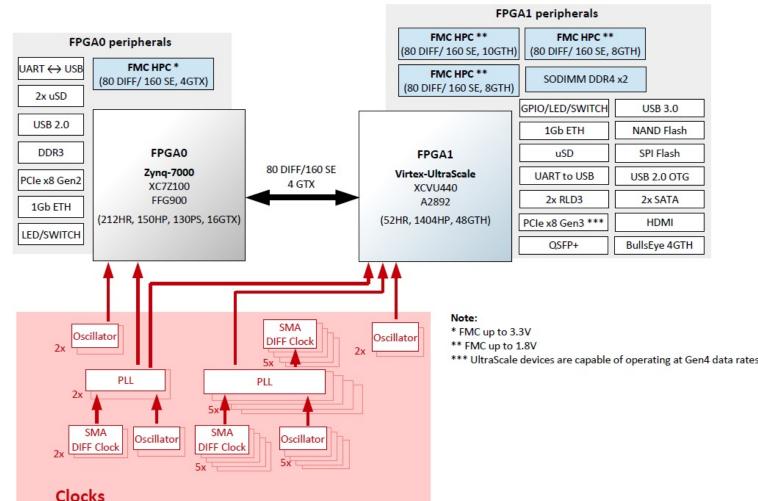

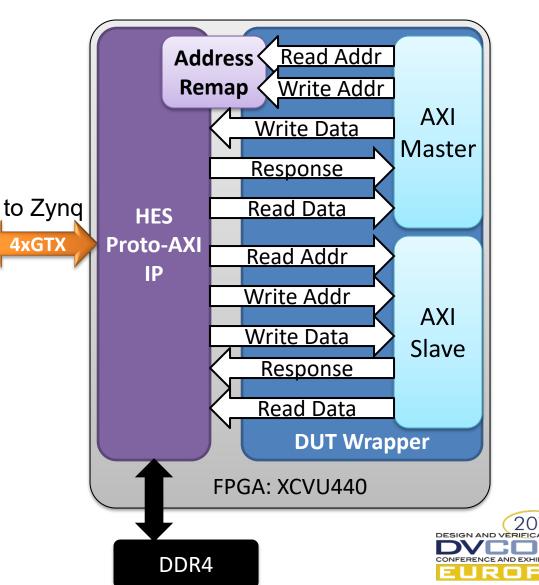

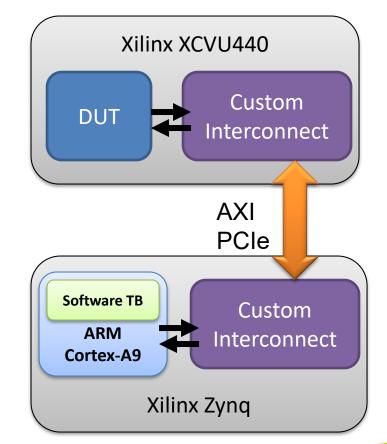

### HES-US-440 Diagram

### • Memory

- DDR4 (64 GB) : 2 x SO-DIMM

- RLDRAM-3 (1152 Mb)

- NAND Flash, SPI Flash

- 2x MircoSD card slots

### • I/O Connectivity

- Inter-FPGA:

- 80 DIFF / 160 SE, 4 GTH

- FMC connectors

- 320 DIFF / 640 SE, 26 GTH

- Peripherals

- PCIe x8 gen3 & gen2

- USB 3.0 & 2.0 & OTG, SATA

- Ethernet 1Gb, QSFP+ 40Gb

- BullsEye

- Clocks

- 7x programmable clock modules

# SDT application examples on HES-US-440

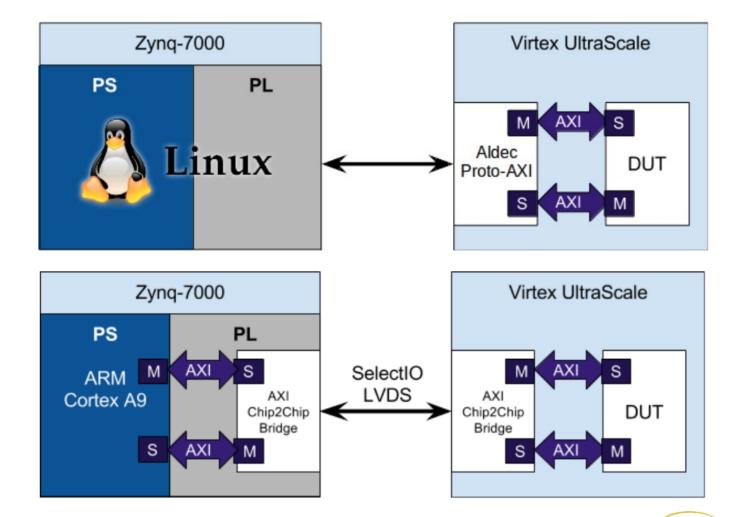

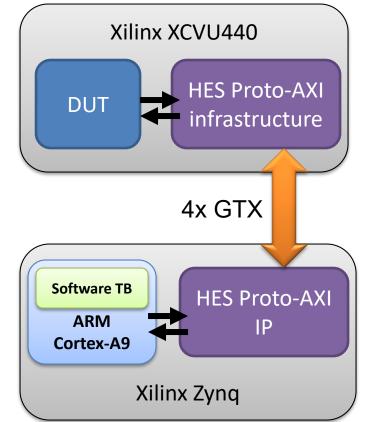

- Case-1: Aldec HES-ProtoAXI

- Zynq image ready to use (PL & PS)

- Use Aldec Proto-AXI IP

- Ready Embedded Linux env.

- Simple Proto-AXI C/C++ API

- Spend all your time to develop SDT

- Case-2: Bare metal / Custom

- Use Xilinx Vivado & SDK

- Create custom C2C bridge in PL

- Create custom SDT in PS

ESIGN AND VERIF

### Use Case-1 with HES Proto-AXI

- 1. Connect DUT to HES Proto-AXI & implement FPGA bitstream

- 2. Develop & build software TB

- 3. Run test

# Step-1: Connecting DUT to HES-Proto-AXI

- Connect HES Proto-AXI

- Use any HDL Editor

- VHDL or Verilog templates available

- Fixed size AXI4 memory mapped interface

- Master interface is optional

- Configure address translation parameters (Address Remapper)

- DUT gets access to on-board DDR4 through HES Proto-AXI

- Compile and implement project in Xilinx Vivado

# Step-2: Developing & building testbench

- Develop testbench as C/C++ code

- Use HES Proto-AXI C API

- #include "hesprotoaxiapi.h"

- Simple, user app level API

- needn't know Zynq or Linux kernel

- Compile and build

- Cross-compilation on host PC

- Use GCC toolchain from Xilinx SDK

- arm-xilinx-linux-gnueabi-g++

```

// AXI write (blocking transaction)

```

| HesProtoAxiTrans HesProt | oAxiWrite(      |

|--------------------------|-----------------|

| HesProtoAxiHandler       | _handler,       |

| HesProtoAxiLocation      | _location,      |

| HesProtoAxiU64           | _address32,     |

| HesProtoAxiBuffer        | _buffer,        |

| HesProtoAxiU64           | _bufferSize32); |

|                          |                 |

- // AXI read (non blocking transaction)

bool HesProtoAxiReadNoCheck(

- HesProtoAxiHandler \_handler, HesProtoAxiLocation \_location, HesProtoAxiU64 \_address32, HesProtoAxiBuffer \_buffer, HesProtoAxiU64 \_bufferSize32);

### // GPI write

```

HesProtoAxiStatus HesProtoAxiWriteGpi(

HesProtoAxiHandler _handler,

HesProtoAxiU16 _value);

```

### // GPIO read

HesProtoAxiStatus HesProtoAxiReadGpio(

12

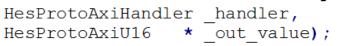

### Step-3: Running Test

### HES Proto-AXI Highlights

Data for HES-US-440

- AMBA AXI4 memory mapped

- 8x Master & Slave interfaces

- Data width: 256, Burst length: 256

- Local clock: 160 MHz

- RAM space: 16GB DDR4 + 64MB RLD

- Customizable address translation

- 16x GPI and GPIO additional lines

- Simple C API

- HES Proto-AXI simulation model available

- Embedded & PC Host modes

ESIGN AND VERIF

### Questions

### Next: Case-2: Bare metal approach

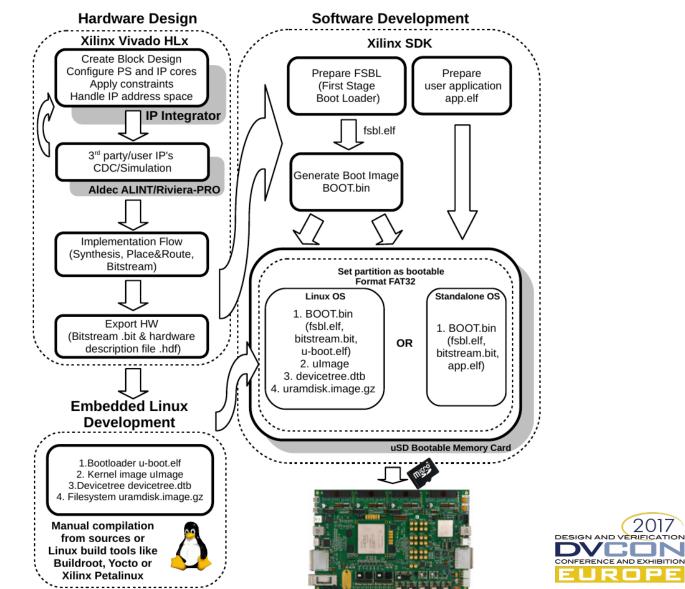

### Use Case-2 – Bare metal approach

- 1. Test controller (Zyng)

- A. Hardware design

- Embedded Linux development Β.

- C. Software development

- 2. Design connectivity (U440)

- A. Custom interconnect

- **FPGA** implementation Β.

2017

© Accellera Systems Initiative

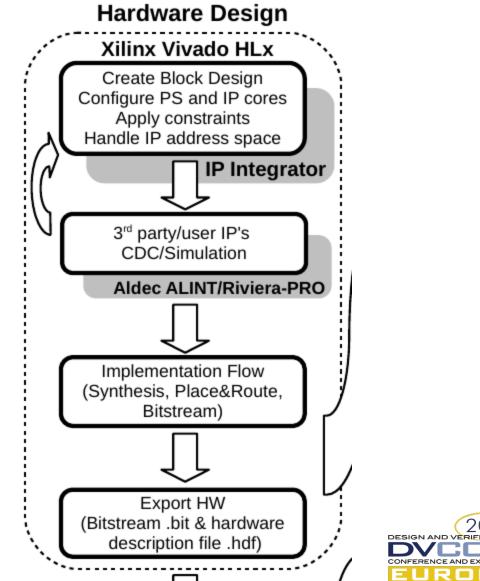

### Step 1.A: Hardware design

- Short path: start with reference design from Aldec

- Customize reference design

- Add your custom chip-2-chip connectivity

- Use Aldec Riviera-PRO with QEMU to verify your changes

- Run Vivado to implement bitfiles and export hardware description

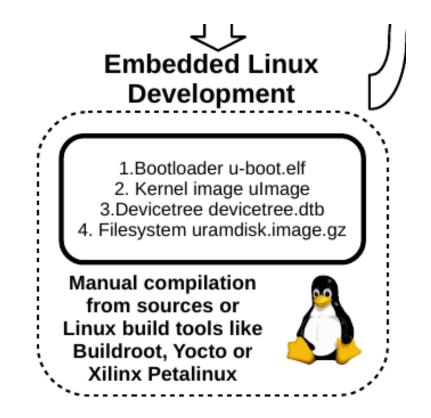

## Step 1.B: Embedded Linux development

- Embedded Linux projects available:

- Yocto

- Petalinux

- Other than Linux:

- Free RTOS

- Bare metal no OS

- Xilinx SDK provides toolchain for such mode

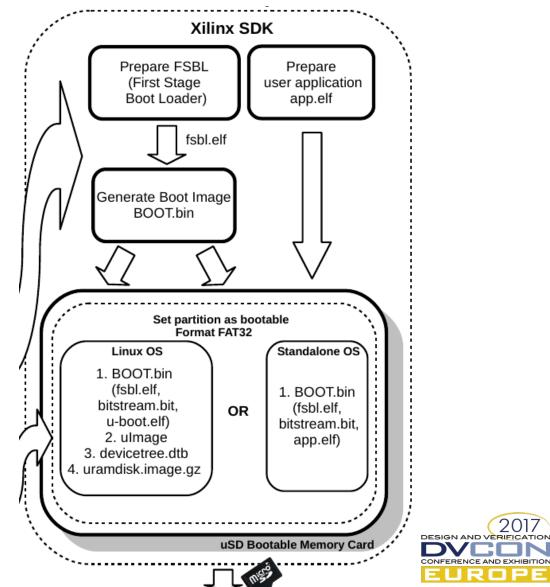

### Step 1.C: Software development

19

- Use Xilinx SDK

- to develop test application

- create bootable Linux image

- Copy files to Micro-SD

- Bitstream for FPGA (PL configuration)

- Bootloader for ARM (PS configuration)

- Linux image & device tree

- User application (app.elf)

$20^{\circ}$

# Step 2: Design connectivity

- Use Xilinx Vivado to implement XCVU440

- Create custom interconnect

- Coupling with one created in Zynq

- Use any standard (AXI, PCIe)

- Use any signaling (LVDS, GTX)

- Connect with the DUT

- Run FPGA implementation

### Questions

### Next: Software driven testbench in simulation: QEMU co-simulation with Riviera-PRO

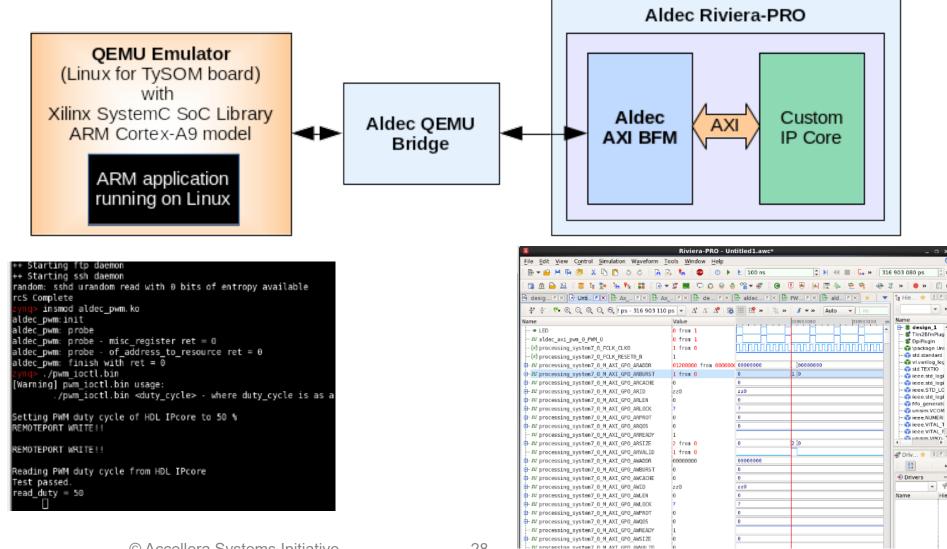

### **QEMU CO-SIMULATION WITH RIVIERA-PRO**

Radosław Nawrot

Software Products Manager, Aldec Inc.

© Accellera Systems Initiative

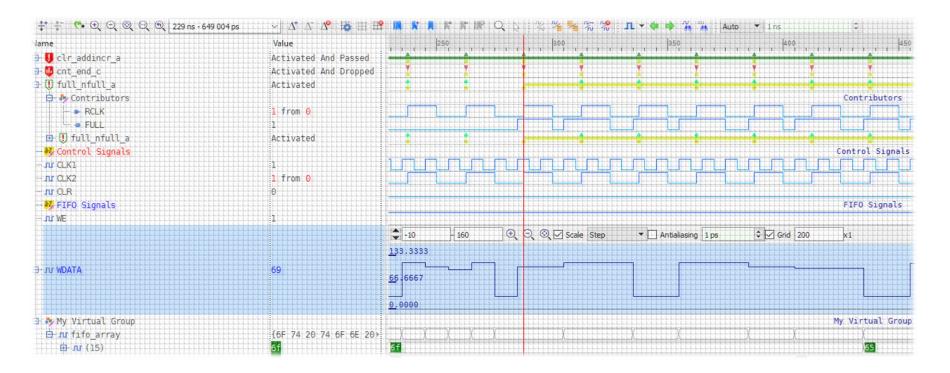

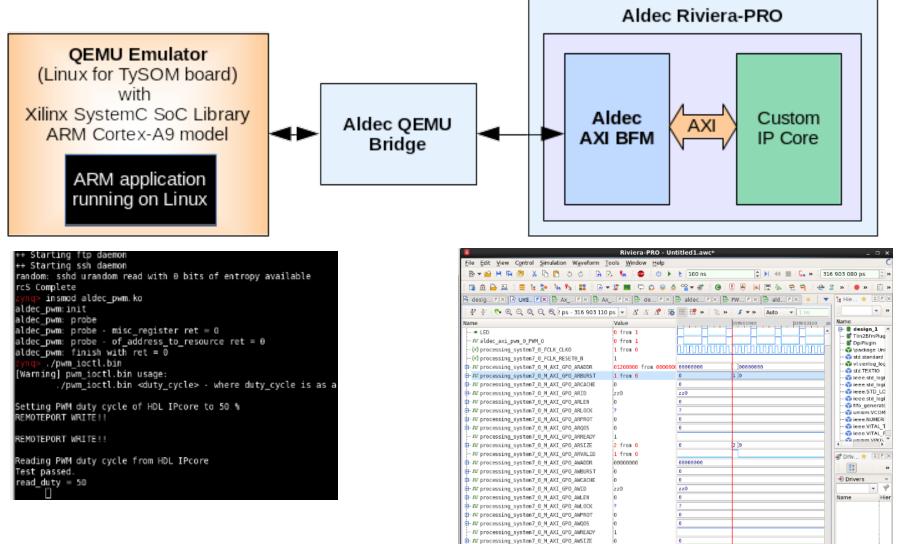

### QEMU co-simulation platform

- Parts of the flow:

- Riviera-PRO Advance Verification Platform

- -Aldec AXI BFM

- -Aldec QEMU Bridge

- -QEMU Emulator

# QEMU co-simulation platform

- Full debug capabilities of RTL IP Core in Riviera-PRO simulator:

- Waveforms

- Hardware Breakpoints

- Hardware steps

- Transaction based verification and debug

- Kernel and driver debug via GDB

- Software Breakpoints

- Variable probing

- Zynq Linux OS ready to use on QEMU without modifications

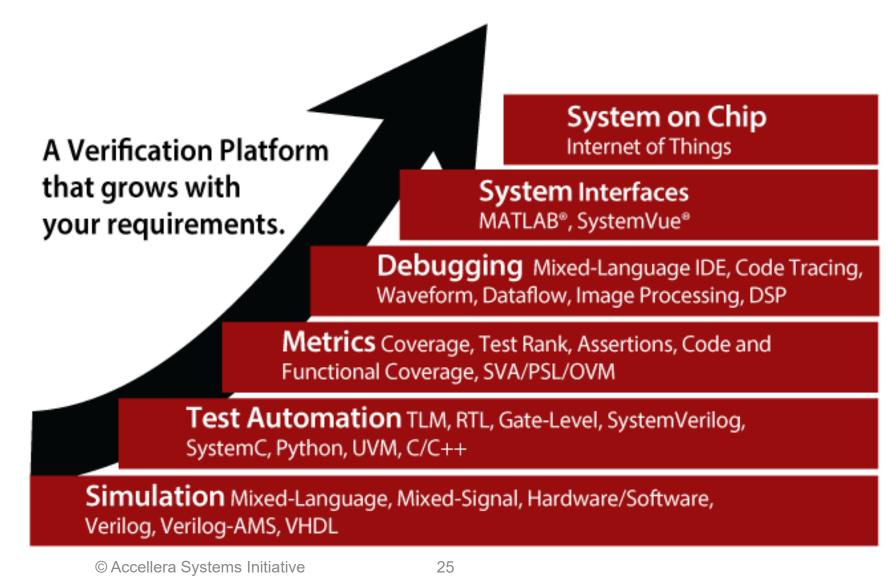

### **Riviera-PRO Verification Platform**

# **Riviera-PRO Highlights**

- High Performance Simulation

- Extensive simulation optimization algorithms

- Support for latest Verification Libraries: UVM, OSVVM , UVVM, CocoTB and more

- Advanced Debugging

- Transaction Level simulation end debug

- Multi-language debug environment (Verilog, VHDL, SystemVerilog, SystemC, Verilog-AMS)

- Support for MATLAB and Simulink

- C/C++ debug environment

- Support for external C/C++ compilers (GCC, Visual C++)

- UVM Toolbox, Graph and Class Viewer

- Code tracing, Waveform, Dataflow, FSM window, Coverage, assertions, memory visualization

- Comprehensive Assertions-Based Verification (SVA and PSL)

- Advanced Code and Functional Coverage

- User-defined test plan linking with coverage database

- Plot Viewer and Image Viewer

ESIGN AND VER

### QEMU – Virtual Platform

- Free and open-source

- Fast emulator

- Supports many machines:

- Xilinx-zynq-a9

- Supports many ARM processors:

- ARM926

- ARM946

- Cortex-A8

- Cortex-A9

- Cortex-A15

- Cortex-A53

- Cortex-A57

### **Riviera-PRO and QEMU**

SYSTEMS INITIATIVE

28

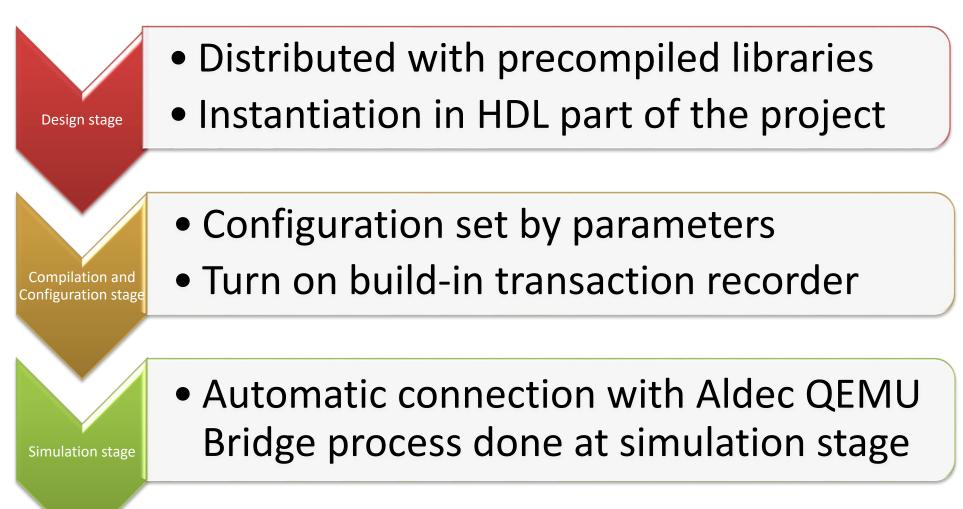

### Aldec AXI BFM usage

### Aldec AXI BFM

- AXI 3 Master

- AXI 3 Slave

- AXI 4 Master

- AXI 4 Slave

- AXI 4 Lite Master

- AXI 4 Lite Slave

- AXI 4 Stream Master

- AXI 4 Stream Slave

| 1 Libraries                         |                   |                                                                 |

|-------------------------------------|-------------------|-----------------------------------------------------------------|

| 0 🔢 🖧 88                            |                   | - <i>S</i>                                                      |

| Name                                | Туре              | Path                                                            |

| 👜 👬 act3_ver (RO)                   |                   | /home/radekn/Aldec/Riviera-PRO-2017.06-x 🔺                      |

| 🕀 👖 aldec (RO)                      |                   | /home/radekn/Aldec/Riviera-PRO-2017.06-x                        |

| 🛱 👖 aldec_axi_bfm_qemu (RO)         |                   | /home/radekn/Aldec/Riviera-PRO-2017.06-x                        |

| 🖅 \$root                            | Module            |                                                                 |

| Ax_Axi3MasterBFM Name: aldec_ax     | _bfm_qemu         |                                                                 |

| 🕼 Ax_Axi3MasterBFM                  | apping            | era-PRO-2017.06-x64/vlib/aldec_axi_bfm_qemu/aldec_axi_bfm_qemu. |

| Ax_Axi3SlaveBFM                     | adekn/Aldec/Rivie | era-PRO-2017.06-x64/viib/aidec_axi_bim_demu/aidec_axi_bim_demu. |

| 🕾 Ax_Axi3SlaveBFMcore               | Module            | /home/radekn/Aldec/Riviera-PRO-2017.06-x                        |

| 🌇 Ax_Axi4LiteMasterBFM              | Top module        | /home/radekn/Aldec/Riviera-PRO-2017.06-x                        |

| 🖅 Ax_Axi4LiteMasterBFMcore          | Module            | /home/radekn/Aldec/Riviera-PRO-2017.06-x                        |

| 🌇 Ax_Axi4LiteSlaveBFM               | Top module        | /home/radekn/Aldec/Riviera-PRO-2017.06-x                        |

| 🖅 Ax_Axi4LiteSlaveBFMcore           | Module            | /home/radekn/Aldec/Riviera-PRO-2017.06-x                        |

| 🌇 Ax Axi4MasterBFM                  | Top module        | /home/radekn/Aldec/Riviera-PRO-2017.06-x                        |

| 🖅 Ax_Axi4MasterBFMcore              | Module            | /home/radekn/Aldec/Riviera-PRO-2017.06-x                        |

| 🌇 Ax_Axi4SlaveBFM                   | Top module        | /home/radekn/Aldec/Riviera-PRO-2017.06-x                        |

| 🖅 Ax Axi4SlaveBFMcore               | Module            | /home/radekn/Aldec/Riviera-PRO-2017.06-x                        |

| 🌇 Ax_Axi4StreamMasterBFM            | Top module        | /home/radekn/Aldec/Riviera-PRO-2017.06-x                        |

| 🖅 Ax_Axi4StreamMasterBFMcore        | Module            | /home/radekn/Aldec/Riviera-PRO-2017.06-x                        |

| 🌇 Ax_Axi4StreamSlaveBFM             | Top module        | /home/radekn/Aldec/Riviera-PRO-2017.06-x                        |

| 🖅 Ax_Axi4StreamSlaveBFMcore         | Module            | /home/radekn/Aldec/Riviera-PRO-2017.06-x                        |

| 🌇 TransactionRecorderAxi3           | Top module        | /home/radekn/Aldec/Riviera-PRO-2017.06-x                        |

| 🥵 TransactionRecorderAxi4           | Top module        | /home/radekn/Aldec/Riviera-PRO-2017.06-x                        |

| 🦝 TransactionRecorderAxi4Lite       | Top module        | /home/radekn/Aldec/Riviera-PRO-2017.06-x                        |

| 🜍 UnitScopePackage_1                | SV Package        | /home/radekn/Aldec/Riviera-PRO-2017.06-x                        |

| 8 protected_512eb4b7af147c73dbdfe0> |                   | /home/radekn/Aldec/Riviera-PRO-2017.06-x                        |

| protected_ef16c1876adf1a8fe7b4971   |                   | /home/radekn/Aldec/Riviera-PRO-2017.06-x                        |

### AXI BFM instance in HDL Code

|       |                                                          | <u>−</u> |   |                                               |                          |                    |     |

|-------|----------------------------------------------------------|----------|---|-----------------------------------------------|--------------------------|--------------------|-----|

| 5     | .AWVALID(processing system7 0 M AXI GP1 AWVALID),        | « ***    |   | Name                                          | Design unit              | Library            |     |

| 6     | .BID(processing system7 0 M AXI GP1 BID),                |          | - | 🚊 書 design 1                                  | design 1                 | xil defaultlib     |     |

| 57    | .BREADY(processing system7 0 M AXI GP1 BREADY),          |          |   | 🖶 書 axi bram ctrl 0                           | design 1 axi bram ctrl   | 0⊩xil defaultlib   |     |

| 8     | .BRESP(processing system7 0 M AXI GP1 BRESP),            |          |   | 🕀 婁 axi bram ctrl 0 bram                      | design 1 axi bram ctrl   | 0⊧xil defaultlib   |     |

| 9     | .BVALID(processing system7 0 M AXI GP1 BVALID),          |          |   | 🕀 🔹 axi cdma 0                                | design 1 axi cdma 0 0(   | d xil defaultlib   |     |

| 0     | .RDATA(processing system7 0 M AXI GP1 RDATA),            |          |   | 🕀 書 axi_mem_intercon_1                        | design 1 axi mem inter   | c⊧xil_defaultlib   |     |

| 1     | .RID(processing system7 0 M AXI GP1 RID),                |          |   | 🕀 書 axi protocol converter 0                  | design 1 axi protocol co | o⊮ xil defaultlib  |     |

| 2     | .RLAST(processing system7 0 M AXI GP1 RLAST),            |          |   | 🕀 🚦 master 0                                  | Ax Axi3MasterBFM         | aldec axi bfm gem  | nu  |

| 3     | .RREADY(processing system7 0 M AXI GP1 RREADY),          |          |   | 🕀 📲 master 1                                  | Ax Axi3MasterBFM         | aldec axi bfm gem  | nu  |

| 4     | .RRESP(processing system7 0 M AXI GP1 RRESP),            |          |   | 🕀 🛊 slave 0                                   | Ax Axi3SlaveBFM          | aldec axi bfm gem  | nu  |

| 5     | .RVALID(processing system7 0 M AXI GP1 RVALID),          |          |   | 🗘 @INITIAL#829_0@                             |                          | xil_defaultlib     |     |

| 6     | .WDATA(processing system7 0 M AXI GP1 WDATA),            |          |   | 🙀 @INITIAL#841_1@                             |                          | xil_defaultlib     |     |

| 7     | .WID(processing system7 0 M AXI GP1 WID),                |          |   | 🖶 📲 gibi                                      | glbl                     | xil_defaultlib     |     |

| 8     | .WLAST(processing system7 0 M AXI GP1 WLAST),            |          |   | 📽 TIm2BfmPlugin                               | TIm2BfmPlugin            | aldec_axi_bfm_qem  | nu  |

| 9     | .WREADY(processing system7 0 M AXI GP1 WREADY),          |          |   | 📽 DpiPlugin                                   | DpiPlugin                | aldec_axi_bfm_qem  | nu  |

| Θ     | .WSTRB(processing system7 0 M AXI GP1 WSTRB),            |          |   | 🛶 🎲 \package UnitScopePackage_1\              | UnitScopePackage_1       | aldec_axi_bfm_qem  | nu  |

| 1     | .WVALID(processing_system7_0_M_AXI_GP1_WVALID)           |          |   | 🌍 std.standard                                | standard                 | std                |     |

| 2 -   | );                                                       |          | : | Name: std.standard                            | verilog_logic            | vl                 |     |

| 3     |                                                          |          |   | Hierarchy Path: sim:/                         | TEXTIO                   | std                |     |

| 4 ▷ 🗐 | Ax Axi3SlaveBFM #(                                       |          |   | 🐨 🕫 Type: Package                             | std_logic_1164           | ieee               |     |

| 5     | DATA BUS WIDTH(64),                                      |          |   | 🐨 🌍 ie Language: VHDL                         | NUMERIC_STD              | ieee               |     |

| 6     | .ADDRESS WIDTH(32),                                      |          |   | a <b>Design Unit:</b> standard ram_ctrl_funcs | axi_bram_ctrl_funcs      | axi_bram_ctrl_v4_0 | _10 |

| 7 -   | .ID WIDTH(12))                                           |          |   | ず ie Library: std                             | std_logic_arith          | ieee               |     |

| 8 😐   | slave 0 <sup>-</sup> (                                   |          |   | 🗝 🧊 unisim.VCOMPONENTS                        | VCOMPONENTS              | unisim             |     |

| 9     | .ACLK(processing system7 0 FCLK CLK0),                   |          |   | 🗝 🌍 ieee.VITAL_Timing                         | VITAL_Timing             | ieee               |     |

| Э     | .ARESETn(processing system7 0 FCLK RESET0 N),            |          |   | 🕆 🌍 ieee.VITAL_Primitives                     | VITAL_Primitives         | ieee               |     |

| 1     | .ARADDR(axi mem intercon 1 M01 AXI ARADDR),              |          |   | 🗝 🎲 unisim.VPKG                               | VPKG                     | unisim             |     |

| 2     | .ARBURST(axi mem intercon 1 M01 AXI ARBURST),            |          |   | 🗝 🌍 ieee.STD_LOGIC_UNSIGNED                   | STD_LOGIC_UNSIGNED       | ieee               |     |

| 3     | .ARCACHE(axi mem intercon 1 M01 AXI ARCACHE),            |          |   | 🗠 🕿 ieee std. Ionic. misc                     | std logic misc           | ieee               |     |

| 4     | .ARID({1'b0,1'b0,1'b0,axi mem intercon 1 M01 AXI ARID}), |          |   | Hierarchy Datasets Classes                    |                          |                    |     |

| 5     | .ARLEN({4'b0,axi mem intercon 1 M01 AXI ARLEN}),         |          |   |                                               |                          |                    |     |

| 6     | .ARLOCK(axi mem intercon 1 M01 AXI ARLOCK),              |          | 1 | Objects                                       |                          |                    |     |

| 7     | .ARPROT(axi_mem_intercon_1_M01_AXI_ARPROT),              |          |   |                                               |                          |                    |     |

| в     | .ARREADY(axi_mem_intercon_1_M01_AXI_ARREADY),            |          | - |                                               |                          |                    |     |

| 9     | .ARSIZE(axi_mem_intercon_1_M01_AXI_ARSIZE),              |          |   | Name                                          |                          | lue                | Ту  |

| Э     | .ARVALID(axi_mem_intercon_1_M01_AXI_ARVALID),            |          |   | I ACLK                                        | 1                        |                    | wi  |

| 1     | .AWADDR(axi_mem_intercon_1_M01_AXI_AWADDR),              |          |   | I ARESETN                                     | 1                        |                    | wi  |

| 2     | .AWBURST(axi_mem_intercon_1_M01_AXI_AWBURST),            |          |   | 🖶 🕨 AWID                                      | z?(                      | )                  | [10 |

20

DESIGN AND VERIFICATION

CONFERENCE AND EXHIBITION

### AXI BFM instance in HDL Code

| <u>W</u> indow | / <u>H</u> elp |                                                                         |            |   |                                           |                       |                |                       |             |        |            |

|----------------|----------------|-------------------------------------------------------------------------|------------|---|-------------------------------------------|-----------------------|----------------|-----------------------|-------------|--------|------------|

| <b>9</b> 88    | <b>500</b>     | 🕐 🕨 🛓 100 ns 🗘 🕨 📢 🔳 🖡 🖧 📮 📫 1 372 ms                                   | ¢ 4        | 2 | 20                                        |                       |                |                       |             |        |            |

| <b>;</b> .     | I 🖓 🗘          | 😔 🕹 😭 🛪 🐨 🔞 I 🛡 I 🕪 🔚 😓 I 🚖 🗣 🐵 🗷 🗵 🔴 🗣 🌒 🗣 🗮                           | //<br>01•A | 1 | , 🖄 🕲 🛑                                   |                       |                |                       |             |        |            |

| 👌 desig        | gn_wrapp       | er_compile.do 🛪 🖾 Untitled1.awc* 🛪 🗋 DpiBridge.so रू 🎼 design_1.v र 🛪 🔹 | •          | L | Hierarchy                                 |                       |                |                       |             |        | ± \$₹      |

| 88             |                | · · · · · · · · · · · · · · · · · · ·                                   | »          |   |                                           |                       |                |                       | •           | 🖗 (.*) | Attributes |

| 682            | 11             | .S AXI HPO WDATA(axi mem intercon 1 MO1 AXI WDATA),                     | «          | Ν | lame                                      | Design unit           |                | Library               |             |        |            |

| 683            | 11             | .S AXI HPO WID({1'b0,1'b0,1'b0,1'b0,axi mem intercon 1 M01 AXI WID})    |            |   | 🕂 書 design_1                              | design_1              |                | xil_defaultlib        |             |        |            |

| 684            | 11             | .S AXI HPO WLAST(axi mem intercon 1 M01 AXI WLAST),                     |            |   | 🖶 🖶 axi_bram_ctrl_0                       | design_1_axi_bram_ct  | rl_0⊧          | xil_defaultlib        | 1           |        |            |

| 685            | 11             | .S AXI HPO WREADY(axi mem intercon 1 M01 AXI WREADY),                   |            |   | 🖶 書 axi_bram_ctrl_0_bram                  | design_1_axi_bram_ct  | rl_0⊧          | xil_defaultlib        |             |        |            |

| 686            | 11             | .S AXI HPO WRISSUECAPI EN(1'b0),                                        |            |   | 🖶 書 axi_cdma_0                            | design_1_axi_cdma_0   | _0(d)          | xil_defaultlib        |             |        |            |

| 687            | 11             | .S AXI HPO WSTRB(axi mem intercon 1 M01 AXI WSTRB),                     |            |   | 🖶 書 axi_mem_intercon_1                    | design_1_axi_mem_in   | terc⊧          | xil_defaultlib        |             |        |            |

| 688            | -77            | .S AXI HPO WVALID(axi mem intercon 1 M01 AXI WVALID));                  |            |   | 🖶 書 axi_protocol_converter_0              | design_1_axi_protocol | co⊮            | xil_defaultlib        |             |        |            |

| 689            | 1              |                                                                         |            |   | 🖶 書 master_0                              | Ax Axi3MasterBFM      | -              | aldec_axi_bfm_qemu    | -           |        |            |

| 690            | /              | /assign processing system7 0 M AXI GP0 WID = 12'b0;                     |            |   | 🕀 書 master 1                              | Ax Axi3MasterBFM      |                | aldec axi bfm qemu    |             |        |            |

|                |                | x Axi3MasterBFM #(                                                      |            |   | 🖶 書 slave 0                               | Ax Axi3SlaveBFM       |                | aldec axi bfm qemu    |             |        |            |

| 692            | Ī              | .DATA BUS WIDTH(32),                                                    |            |   | - 🗘 @INITIAL#829 0@                       | _                     |                | xil_defaultlib        |             |        |            |

| 693            |                | .ADDRESS WIDTH(32),                                                     |            |   |                                           |                       |                | xil defaultlib        |             |        |            |

| 694            | L              | .ID WIDTH(12))                                                          |            |   | 🗄 📲 gibi                                  | glbl                  |                | xil defaultlib        |             |        |            |

|                | E m            | haster 0 (                                                              |            |   | 📽 TIm2BfmPlugin                           | -<br>TIm2BfmPlugin    |                | aldec axi bfm gemu    |             |        |            |

| 696            | ī "            | .ACLK(processing system7 0 FCLK CLK0),                                  |            |   | - PpiPlugin                               | DpiPlugin             |                | aldec axi bfm gemu    |             |        |            |

| 697            |                | .ARESETn(processing_system7_0_FCLK_RESET0_N),                           |            |   | \package UnitScopePackage 1\              | UnitScopePackage 1    |                | aldec axi bfm gemu    |             |        |            |

| 698            |                | .ARADDR(processing_system7 0 M AXI GP0 ARADDR),                         |            |   | std.standard                              | standard              |                | std                   |             |        |            |

| 699            |                | .ARBURST(processing_system7_0_M_AXI_GPO_ARBURST),                       |            |   |                                           | verilog logic         |                | vl                    |             |        |            |

| 700            |                | .ARCACHE(processing_system/ 0 M AXI GPO ARCACHE),                       |            |   | std.TEXTIO                                | TEXTIO                |                | std                   |             |        |            |

| 701            |                | .ARID(processing system7 0 M AXI GP0 ARID),                             |            |   | ieee.std logic 1164                       | std logic 1164        |                | ieee                  |             |        |            |

| 702            |                | .ARLEN(processing_system/_0_H_ARL_OF0_ARLEN),                           |            |   | ieee.NUMERIC STD                          | NUMERIC STD           |                | ieee                  |             |        |            |

| 703            |                | .ARLOCK(processing system7 0 M AXI GP0 ARLOCK),                         |            |   | axi bram ctrl v4 0 10.axi bram ctrl funcs | axi bram ctrl funcs   |                | axi bram ctrl v4 0 10 |             |        |            |

| 704            |                | .ARPROT(processing_system7_0_M_AXI_GP0_ARPROT),                         |            |   | ieee.std logic arith                      | std logic arith       |                | ieee                  |             |        |            |

| 705            |                | .ARREADY(processing_system/ 0 M AXI GPO ARREADY),                       |            |   | unisim.VCOMPONENTS                        | VCOMPONENTS           |                | unisim                |             |        |            |

| 706            |                | .ARSIZE(processing system7 0 M AXI GPO ARSIZE),                         |            |   | ieee.VITAL Timing                         | VITAL Timing          |                | ieee                  |             |        |            |

| 707            |                | .ARVALID(processing_system/ 0 M AXI GPO ARVALID),                       |            |   | ieee.VITAL Primitives                     | VITAL Primitives      |                | ieee                  |             |        |            |

| 708            |                | .AWADDR(processing_system7_0_M_AXI_GPO_AWADDR),                         |            |   | unisim.VPKG                               | VPKG                  |                | unisim                |             |        |            |

| 709            |                | .AWBURST(processing system7 0 M AXI GPO AWBURST),                       |            |   | ieee.STD LOGIC UNSIGNED                   | STD LOGIC UNSIGNED    |                | ieee                  |             |        |            |

| 710            |                |                                                                         |            |   |                                           | std logic misc        |                | ieee                  |             |        |            |

|                |                | .AWCACHE(processing_system7_0_M_AXI_GP0_AWCACHE),                       |            |   | Hierarchy Datasets Classes                |                       |                | ·····                 |             |        |            |

| 711            |                | .AWID(processing_system7_0_M_AXI_GP0_AWID),                             |            | 5 |                                           |                       |                |                       |             |        |            |

| 712            |                | .AWLEN(processing_system7_0_M_AXI_GP0_AWLEN),                           |            |   | • Objects                                 |                       |                |                       |             |        | 📩 ≑ ह      |

| 713            |                | .AWLOCK(processing_system7_0_M_AXI_GP0_AWLOCK),                         |            |   |                                           |                       |                |                       |             |        |            |

| 714            |                | .AWPROT(processing_system7_0_M_AXI_GP0_AWPROT),                         |            |   | I                                         |                       |                |                       | •           | 🌳 (.*) | Attributes |

| 715            |                | .AWREADY(processing_system7_0_M_AXI_GP0_AWREADY),                       | -          | N | Jame                                      |                       | Value          | е Туре                | <u>م</u>    |        |            |

| 716            |                | .AWSIZE(processing_system7_0_M_AXI_GP0_AWSIZE),                         |            |   | anne axi bram ctrl 0 BRAM PORTA ADDR      |                       | No da          |                       | e<br>D]wire |        |            |

| 717            |                | .AWVALID(processing_system7_0_M_AXI_GP0_AWVALID),                       |            |   | axi bram ctrl 0 BRAM PORTA CLK            |                       | No da<br>No da |                       |             |        |            |

| 718            |                | .BID(processing_system7_0_M_AXI_GP0_BID),                               |            |   | axi_bram_ctrl_0_BRAM_PORTA_CLK            |                       | No da<br>No da |                       | 0]wire      |        |            |

| 719            |                | .BREADY(processing_system7_0_M_AXI_GP0_BREADY),                         | Ŧ          |   | Objects Drivers/Readers                   |                       | wo da          | 1.a [31:0             | Jwire       |        |            |

DESIGN AND VERIFICA

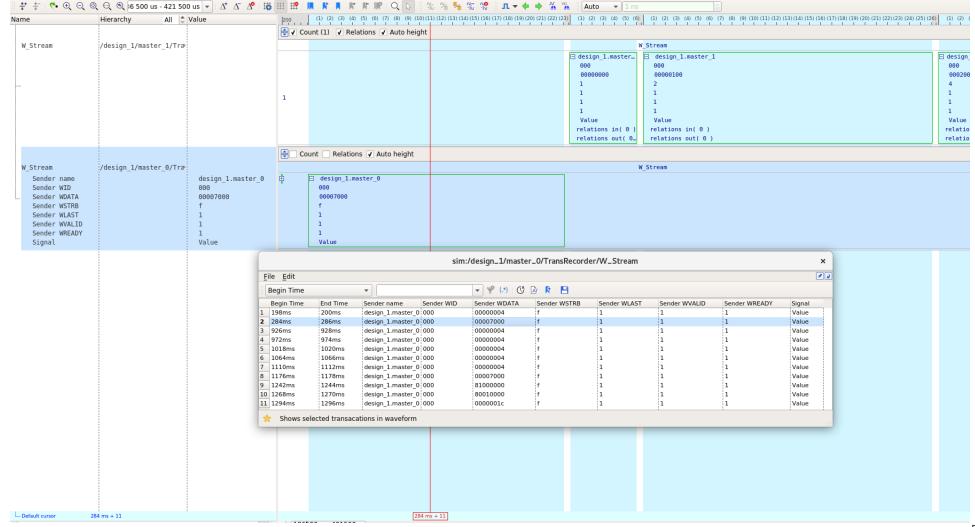

### **Built-in Transaction Recorder**

| 🌛 desigi   | n_wrapper_com 🖲 🗙 📴 Untitled 🖲 🗙 🗋 DpiBri Ə 🗙 🗟 desi Ə 🗙 🔂 Ax_Axi3Slav Ə 🗙 🔶 | •     | Ľ  | Hierarchy                          |                        |                                      |                 |        | 5\$        |

|------------|------------------------------------------------------------------------------|-------|----|------------------------------------|------------------------|--------------------------------------|-----------------|--------|------------|

| 88         | ▼ # # !♥   # # # # !♥ !♥ !♥ !♥ !■ ■ ■ ■ ■ ■ ■                                | »     |    |                                    |                        |                                      | •               | 🌳 (.*) | Attributes |

| 704        | axi_slv_bfm_core.wait_on(phase, count);                                      | « *** |    | lame                               | Design unit            | Library                              |                 |        |            |

| 705        | endtask                                                                      | •     | E  |                                    | design_1               | xil_defaultlib                       |                 |        |            |

| 706        | //////////////////////////////////////                                       |       |    | 🖶 🖶 axi_bram_ctrl_0                | design_1_axi_bram_ctr  |                                      |                 |        |            |

| 707        | `endif                                                                       |       |    |                                    | design_1_axi_bram_ctr  |                                      |                 |        |            |

| 708        |                                                                              |       |    |                                    | design_1_axi_cdma_0_   |                                      |                 |        |            |

| 709        |                                                                              |       |    |                                    | design_1_axi_mem_inte  |                                      |                 |        |            |

|            | `ifdef ALDEC_USE_TRANSACTIONS                                                |       |    |                                    | design_1_axi_protocol_ |                                      |                 |        |            |

| 711        |                                                                              |       |    | 🖶 🖶 master_0                       | Ax_Axi3MasterBFM       | aldec_axi_bfm_qemu                   |                 |        |            |

| 712 🖃      |                                                                              |       |    | 🖶 🛊 master_1                       | Ax_Axi3MasterBFM       | aldec_axi_bfm_qemu                   |                 |        |            |

| 713        | .DATA_BUS_WIDTH(DATA_BUS_WIDTH),                                             |       |    | 🖻 🛊 slave_0                        | Ax_Axi3SlaveBFM        | aldec_axi_bfm_qemu                   |                 |        |            |

| 714        | .ADDRESS_WIDTH(ADDRESS_WIDTH),                                               |       |    | axi_slv_bfm_core                   | Ax_Axi3SlaveBFMcore    | aldec_axi_bfm_qemu                   |                 |        |            |

| 715        | .ID_WIDTH(ID_WIDTH),                                                         |       |    | TransRecorder                      | TransactionRecorderAx  |                                      |                 |        |            |

| 716        | .INSTANCE(\$sformatf("%m")))                                                 |       |    | └──☆ @INITIAL#ini@                 |                        | aldec_axi_bfm_qemu<br>xil defaultlib |                 |        |            |

| 717 Ξ      |                                                                              |       |    | @INITIAL#829_0@<br>@INITIAL#841 1@ |                        | xil_defaultlib                       |                 |        |            |

| 718        | ACLK(ACLK),                                                                  | 11    | Π, |                                    | glbl                   | xil_defaultlib                       |                 |        |            |

| 719        | . ARESETN (ARESETN),                                                         |       |    | Tim2BfmPlugin                      | gibi<br>Tim2BfmPlugin  | aldec axi bfm gemu                   |                 |        |            |

| 720        | . AWID (AWID),                                                               |       |    |                                    | DpiPlugin              | aldec_axi_bfm_gemu                   |                 |        |            |

| 721<br>722 | . AWADDR (AWADDR),                                                           |       |    | package UnitScopePackage 1         | UnitScopePackage 1     | aldec_axi_bfm_qemu                   |                 |        |            |

| 723        | .AWLEN(AWLEN),<br>.AWSIZE(AWSIZE),                                           |       |    | std.standard                       | standard               | std                                  |                 |        |            |

| 723        | .AWBURST(AWBURST).                                                           |       |    | vl.verilog logic                   | verilog logic          | vl                                   |                 |        |            |

| 725        | .AWDORST (AWDORST),                                                          |       |    | std.TEXTIO                         | TEXTIO                 | std                                  |                 |        |            |

| 726        | . AWCACHE ( AWCACHE ) ,                                                      |       |    | ieee.std logic 1164                | std logic 1164         | ieee                                 |                 |        |            |

| 727        | .AWCACHE (AWCACHE),                                                          |       |    | ieee.NUMERIC STD                   | NUMERIC STD            | ieee                                 |                 |        |            |

| 728        | .AWVALID(AWVALID).                                                           |       |    | -                                  | axi bram ctrl funcs    | axi bram ctrl v4 0 1                 | 10              |        |            |

| 729        | . AWREADY (AWREADY) ,                                                        |       |    | ieee.std logic arith               | std_logic_arith        | ieee                                 |                 |        |            |

| 730        | .WID(WID),                                                                   |       |    | unisim.VCOMPONENTS                 | VCOMPONENTS            | unisim                               |                 |        |            |

| 731        | WDATA(WDATA),                                                                |       |    |                                    | VITAL Timing           | ieee                                 |                 |        |            |

| 732        | .wstrb(wstrb),                                                               |       |    | ieee VITAI Primitives              | VITAI Primitives       | ieee                                 |                 |        | 1          |

| 733        | .WLAST(WLAST),                                                               |       |    | Hierarchy Datasets Classes         |                        |                                      |                 |        |            |

| 734        | .WVALID(WVALID),                                                             |       |    |                                    |                        |                                      |                 |        |            |

| 735        | .WREADY (WREADY),                                                            |       | n, | • Objects                          |                        |                                      |                 |        | 📩 ≑        |

| 736        | .BID(BID),                                                                   |       |    |                                    |                        |                                      | -               | 😪 (.*) | Attributes |

| 737        | .BRESP(BRESP),                                                               |       |    | ۰<br>-                             |                        |                                      |                 |        |            |

| 738        | .BVALID(BVALID),                                                             |       | N  | lame                               |                        |                                      | Туре            |        |            |

| 739        | .BREADY(BREADY),                                                             |       |    | ACLK                               | 1                      |                                      | wire            |        |            |

| 740        | .ARID(ARID),                                                                 |       |    | ARESETn                            | 1                      |                                      | wire            |        |            |

| 741        | . ARADDR ( ARADDR ) ,                                                        | -     | E  | 🖶 🕨 AWID                           | z                      | ?0                                   | [ID_WIDTH-1:0]w | ire    |            |

DESIGN AND VERIFIC

### **Riviera-PRO QEMU environment**

| e <u>E</u> dit <u>V</u> iew Control <u>S</u> imulation Wav                |                                |                                              |                         |      |                                                                                                                                                                  |           |                                       |          |

|---------------------------------------------------------------------------|--------------------------------|----------------------------------------------|-------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------|----------|

| x • 🗎 🖪 🖬 🗶 🚺 🖪 🖕 ×                                                       |                                | 120                                          | ≪ ■ Ģ.  ⊑ 219           |      | 🔔 🗘 🍄 👼                                                                                                                                                          |           |                                       |          |

| 5 🟛 🕒 🖳 🍔 🖬 🏞 😘 隆 👪                                                       |                                |                                              |                         | •    | 🗨 🗨 🔍 I 👯 🚓 I 🔬 🛛 🖄 I 🗐                                                                                                                                          |           |                                       |          |

| ilesystem 🔶 🗮 🗮                                                           | design_wrapper_compile.do 💌    | 🗙 🖟 Untitled1.awc* 💽 🗙                       | 🗅 DpiBridge.so 💌 🗙      |      | * 🔻 🖲 1                                                                                                                                                          |           | • • • • • • • • • • • • • • • • • • • | * 🕏 🖱    |

| ≥ = + = 2                                                                 | 🕂 🕂 (*• 🔍 O. 🔍 O. (*)          | - 297 550 231 160 ps 👻 🛆 🗸                   | 5 🕂 🔛 🖽 🖽 🕅             | R R  | N IN 🔍 👌 🐔 🐐 🐐 📶 IL 🔻 🗣 🏹 🦓 IL 🖛 🗭 🦍 Auto 🔹 1 ns                                                                                                                 | uration ^ | <b>+ +</b>                            | - 字 (.*) |

| amples/tools/gemu/zyng demo/pl logic 🕙                                    | Name                           | Hierarchy                                    | All 🚖 Value             | 0    | 50 100 150 200 250 ms                                                                                                                                            | ties ^    | Name                                  |          |

| compile                                                                   | 🖶 🛥 m axi arcache              | /design 1/axi cdma 0                         | 3                       | 3    |                                                                                                                                                                  |           |                                       |          |

| dataset.asdbw                                                             | m axi rready                   | /design_1/axi_cdma_0                         | 0                       |      |                                                                                                                                                                  |           |                                       |          |

| hdl src                                                                   | m axi rvalid                   | /design 1/axi cdma 0                         | 0                       |      |                                                                                                                                                                  |           |                                       |          |

| riviera                                                                   | 🖶 🕨 maxi rdata                 | /design_1/axi_cdma_0                         | XXXXXXXX                | XX   | XXXXX                                                                                                                                                            |           |                                       |          |

| work                                                                      | 🖽 🕨 maxi rresp                 | /design 1/axi cdma 0                         | 0                       | x    | ) <del>0</del>                                                                                                                                                   |           |                                       |          |

| e dataset.asdb                                                            | — ▶ m axi rlast                | /design 1/axi cdma 0                         | х                       |      |                                                                                                                                                                  |           |                                       |          |

| dataset.tmp<br>design wrapper compile.do                                  | ■ m axi awready                | /design 1/axi cdma 0                         | 1                       | 1    |                                                                                                                                                                  |           |                                       |          |

| DpiBridge.so                                                              | m axi awvalid                  | /design 1/axi cdma 0                         | 0                       |      |                                                                                                                                                                  |           |                                       |          |

| library.cfg                                                               | 🗄 🛥 m axi awaddr               | /design 1/axi cdma 0                         | 00000000                | 0.0  | 9000                                                                                                                                                             |           |                                       |          |

| Untitled1.do                                                              | B m axi awlen                  | /design_1/axi_cdma_0                         | 00                      | 00   |                                                                                                                                                                  |           |                                       |          |

|                                                                           | B m axi awsize                 | /design_1/axi_cdma_0                         | 0                       | 0    |                                                                                                                                                                  |           |                                       |          |

|                                                                           | 🖶 🛥 m axi awburst              | /design_1/axi_cdma_0                         | 0                       |      |                                                                                                                                                                  |           |                                       |          |

|                                                                           | er • m_axi_awburst             | /design_1/axi_cdma_0<br>/design_1/axi_cdma_0 | 0                       |      |                                                                                                                                                                  |           |                                       |          |

|                                                                           | Br = m_axi_awprot              | /design 1/axi_cdma_0                         |                         |      |                                                                                                                                                                  |           |                                       |          |

|                                                                           | ■ m_axi_awcache                | /design_1/axi_cdma_0<br>/design 1/axi cdma 0 | 3                       | -    |                                                                                                                                                                  |           |                                       |          |

| gn Manager Filesystem                                                     |                                |                                              | 0                       | -    |                                                                                                                                                                  |           |                                       |          |

|                                                                           | m_axi_wvalid                   | /design_1/axi_cdma_0                         | U<br>XXXXXXXX           |      | 90000                                                                                                                                                            |           |                                       |          |

| ibraries 🔶 🔶 🗮                                                            |                                | /design_1/axi_cdma_0                         |                         | 00   | /F V0 /F                                                                                                                                                         |           |                                       |          |

| ) 🔥 🖧 🏘 📃 👻 🖓                                                             | 🖶 🛥 m_axi_wstrb                | /design_1/axi_cdma_0                         | F                       | 0    | <u>, lt , lt</u>                                                                                                                   |           |                                       |          |

| ne                                                                        | m_axi_wlast                    | /design_1/axi_cdma_0                         | U                       |      |                                                                                                                                                                  |           |                                       |          |

| til vtl dbg (RO)                                                          | m_axi_bready                   | /design_1/axi_cdma_0                         | 1                       |      |                                                                                                                                                                  |           |                                       |          |

| xilinxcorelib (RO)                                                        | — ➡ m_axi_bvalid               | /design_1/axi_cdma_0                         | Θ                       |      |                                                                                                                                                                  |           |                                       |          |

| 🗊 👖 xilinxcorelib_ver (RO)                                                | ⊕ ► m_axi_bresp                | /design_1/axi_cdma_0                         | 0                       | 10   |                                                                                                                                                                  |           |                                       |          |

| 🖳 👖 xp (RO)                                                               | L- Default cursor 219 800 us   |                                              | 10000000                |      | 219 800 us                                                                                                                                                       |           |                                       |          |

| •                                                                         | •                              |                                              |                         | • •  | 0fs - 297550231160ps ► ● ● ● ● Configu                                                                                                                           | ation 🔹 🕨 | 4                                     |          |

| onsole                                                                    |                                |                                              | *                       | × اج | 👷 Transaction Streams                                                                                                                                            |           |                                       | * 🕏      |

| 🔥 🚓 👘 🔇 Errors 🛕 Warnings 🤇                                               | Messages                       |                                              | - 9                     |      | Name Hierarchy                                                                                                                                                   |           |                                       |          |

|                                                                           | - )(                           |                                              |                         |      | start_qemu.sh; bash                                                                                                                                              |           | ×                                     |          |

| # KERNEL: SLP simulation initializ<br># KERNEL: Kernel process initializ  |                                |                                              |                         |      | • *                                                                                                                                                              |           |                                       |          |

| # Allocation: Simulator allocated                                         |                                | 22609 kernel=6627 sdf=0)                     |                         |      | No soundcards found.<br>RAMDISK: gzip image found at block 0                                                                                                     |           |                                       |          |

| # VPI: ALDEC AXI BFM version 1.7.1                                        |                                | 22005 Kernet-002, 341-0,                     |                         |      | EXT4-fs (ram0): couldn't mount as ext3 due to feature incompatibilities                                                                                          |           |                                       |          |

| # KERNEL: ASDB file was created in                                        | location /home/radekn/Aldec/R  | iviera-PR0-2017.06-x64/exa                   | amples/tools/qemu/      |      | EXT4-fs (ram0): warning: mounting unchecked fs, running e2fsck is recommended<br>EXT4-fs warning (device ram0): ext4_update_dynamic_rev:717: updating to rev 1 b |           |                                       |          |

| zynq_demo/pl_logic/dataset.asdb                                           |                                |                                              |                         |      | cause of new feature flag, running e2fsck is recommended                                                                                                         |           |                                       |          |

| <pre># VSIM: 176 object(s) traced.</pre>                                  |                                |                                              |                         |      | EXT4-fs (ram0): mounted filesystem without journal. Opts: (null)<br>VFS: Mounted root (ext4 filesystem) on device 1:0.                                           |           |                                       |          |

| <pre># VSIM: 0 object(s) traced. # WAVEFORM: 8 object(s) inserted t</pre> | a virtual array im avi rdata[A | .71                                          |                         |      | devtmpfs: mounted                                                                                                                                                |           |                                       |          |

| WAVEFORM: 8 object(s) inserted t                                          |                                |                                              |                         |      | Freeing unused kernel memory: 264K (c06e6000 - c0728000)                                                                                                         |           |                                       |          |

| WAVEFORM: 8 object(s) inserted t                                          |                                |                                              |                         |      | Starting rcS<br>++ Mounting filesystem                                                                                                                           |           |                                       |          |

| # WAVEFORM: 8 object(s) inserted t                                        |                                |                                              |                         |      | mount: mounting /dev/mmcblk0p1 on /mnt failed: No such file or directory                                                                                         |           |                                       |          |

| # WAVEFORM: 4 object(s) inserted t                                        |                                |                                              |                         |      | mount: mounting /dev/mmcblk0 on /mnt failed: No such file or directory<br>++ Setting up mdev                                                                     |           |                                       |          |

| <pre># VSIM: 0 object(s) traced.</pre>                                    |                                |                                              |                         |      | ++ Starting telnet daemon                                                                                                                                        |           |                                       |          |

| # KERNEL: Block Memory Generator m                                        |                                |                                              |                         |      | ++ Starting http daemon                                                                                                                                          |           |                                       |          |

| design_1.axi_bram_ctrl_0_bram.inst<br>simulation which will not precisel  | .native_mem_mapped_module.blk_ | mem_gen_v8_3_5_inst is usi                   | ng a pehavioral model f | or   | ++ Starting ftp daemon<br>++ Starting ssh daemon                                                                                                                 |           |                                       |          |

| simulation which will not precisel                                        | y moder memory collision behav | 101.                                         |                         | -    | random: sshd urandom read with 0 bits of entropy available                                                                                                       |           |                                       |          |

|                                                                           |                                |                                              |                         |      | rcS Complete<br>zyng≻ ./dwa_test.bin                                                                                                                             |           |                                       |          |

| onsole Messages                                                           |                                |                                              |                         |      |                                                                                                                                                                  |           |                                       |          |

| onsole Messages                                                           |                                |                                              |                         |      |                                                                                                                                                                  |           |                                       |          |

### Hardware and Software co-sim

| <pre>in per per per per per per per per per per</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ne/rad | dekn/Aldec/Riviera-PRO-2017.06-x64/examples/tools/gemu/zyng_demo/linux_app | × 🗘 🕨 🖛 🔳 🗔        | 🔄 📫 1 372 ms           | a 🤹 😵 👼                                |                     |                        | 88  | ✓ 66 <sup>+</sup> 66 <sup>+</sup> | » ⋟ »         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------|--------------------|------------------------|----------------------------------------|---------------------|------------------------|-----|-----------------------------------|---------------|

| <pre>minute in addition to Array 1 and a first and a first and a first a first</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |                                                                            | 🗖 🖩 🐁 🚊 🖣          | 🐼 I I 🖉 🔴 👫            | 🜒 🜒 🗨 i 👬 👫 i 🐔                        | Ē 🖓 🌐               |                        |     |                                   |               |

| <pre>setime 000 AVP_SIZE block00000<br/>setime 000 AVP_SIZE block00000<br/>fit and DVP_SIZE block00000<br/>fit and DVP_SIZE block00000<br/>fit and DVP_SIZE block000000<br/>fit and DVP_SIZE block000000000<br/>fit and DVP_SIZE block000000000000000000000000000000000000</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |                                                                            |                    | pper compile.do र×     | 🕅 Untitled1.awc* र×                    | DpiBridge.so TX     |                        | 254 |                                   |               |

| <pre>setion BOR_NNLS_SIZE 0.03000000<br/>setion BOR_NNLS_SIZE 0.03000000<br/>setion BOR_NNLS_SIZE 0.03000000<br/>int mainting reg, chart arg(1)<br/>int mainting reg, ch</pre>                                                                                                                                                                                                                                                                                                                                                                                                                |        |                                                                            |                    |                        |                                        |                     |                        |     |                                   |               |

| Set         Marking         Number (Set)         Number (Set)         Number (Set)           1/14ed inter (Set)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |                                                                            |                    | & & & & & & 13         |                                        |                     |                        | 257 |                                   |               |