## SoC Verification Speed – More is Better

Fernanda Braga - Cadence Design Systems, Inc. John Rose - Cadence Design Systems, Inc. William Winkeler - Cadence Design Systems, Inc. Sharon Rosenberg - Cadence Design Systems, Inc. Frank Schirrmeister - Cadence Design Systems, Inc.

- The Need for Speed

- Formal methods to avoid sim cycles

- Coding for max sim speed

- Speeding power + mixed-signal SoC

- Break

- Portable Stimulus for faster verification

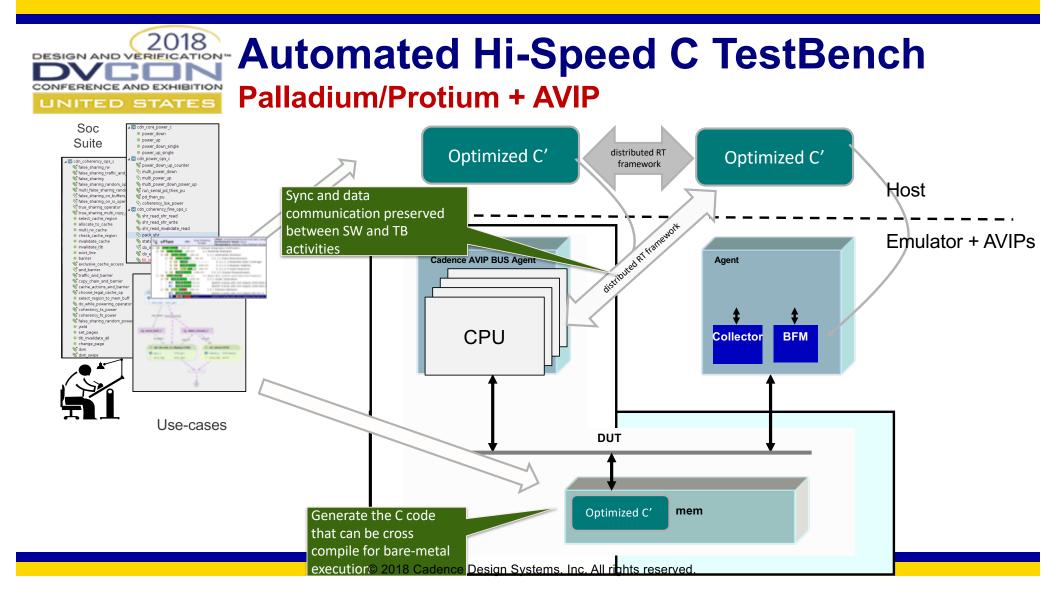

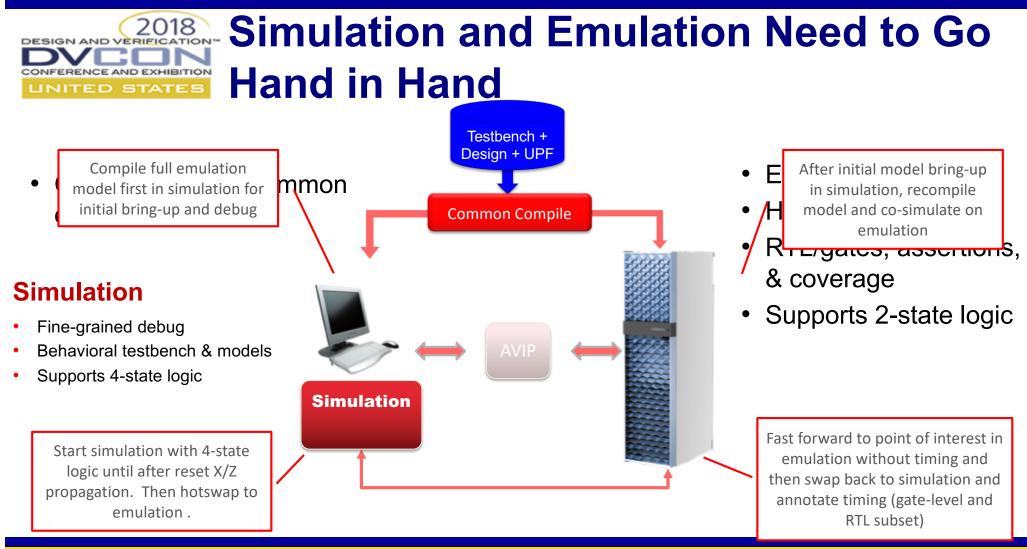

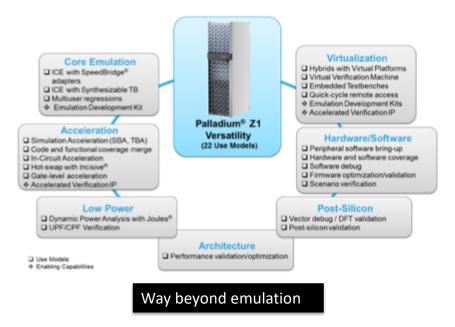

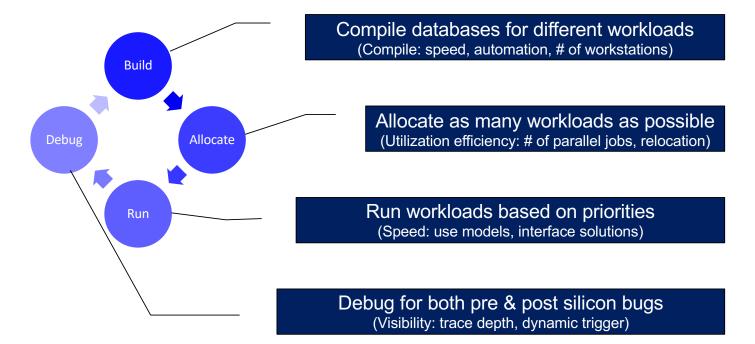

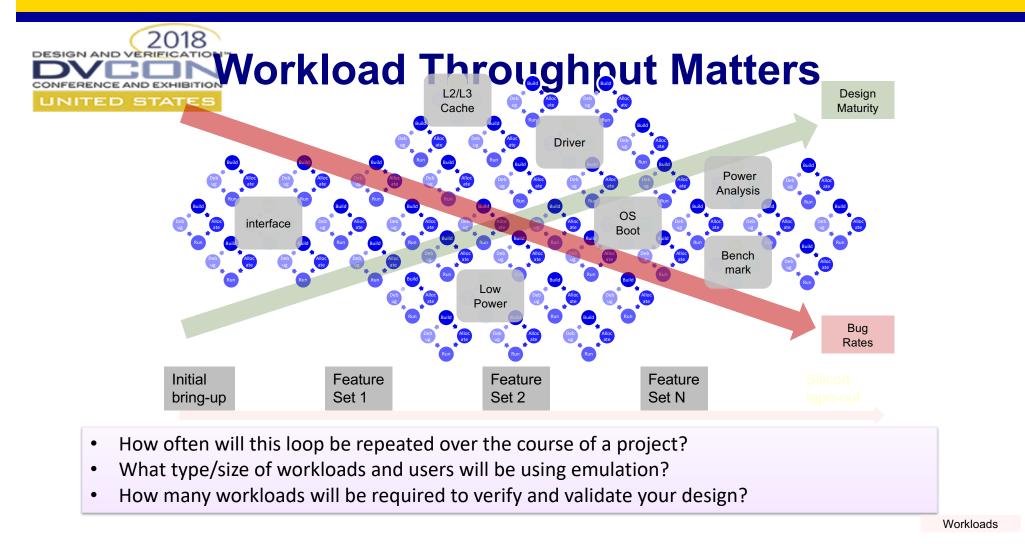

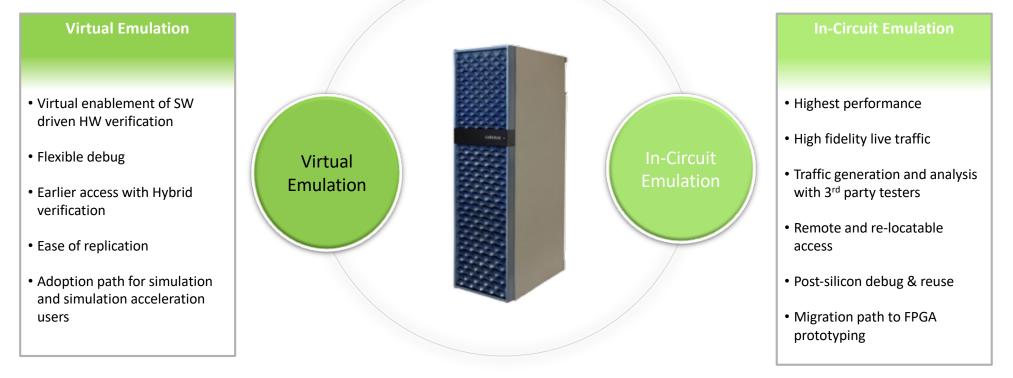

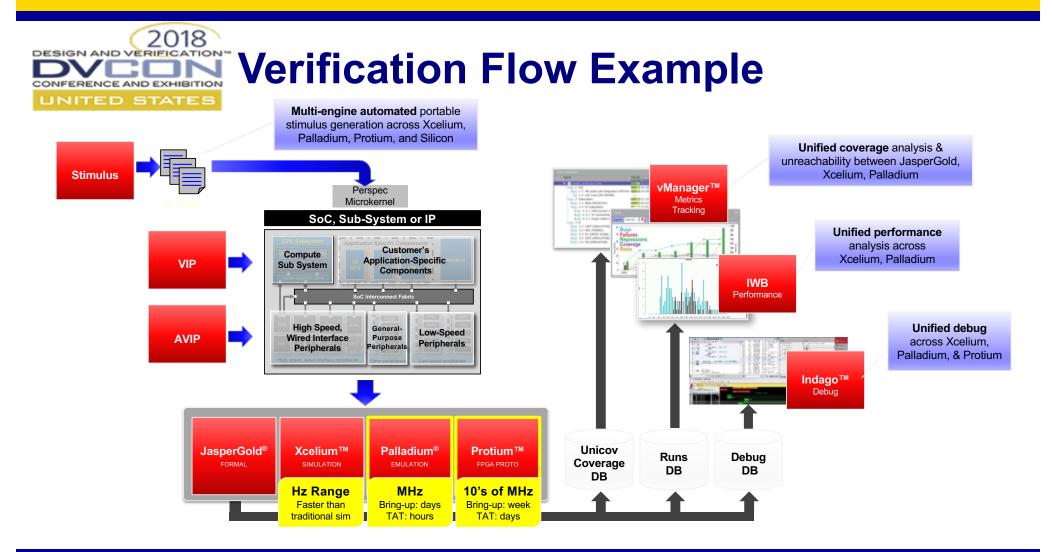

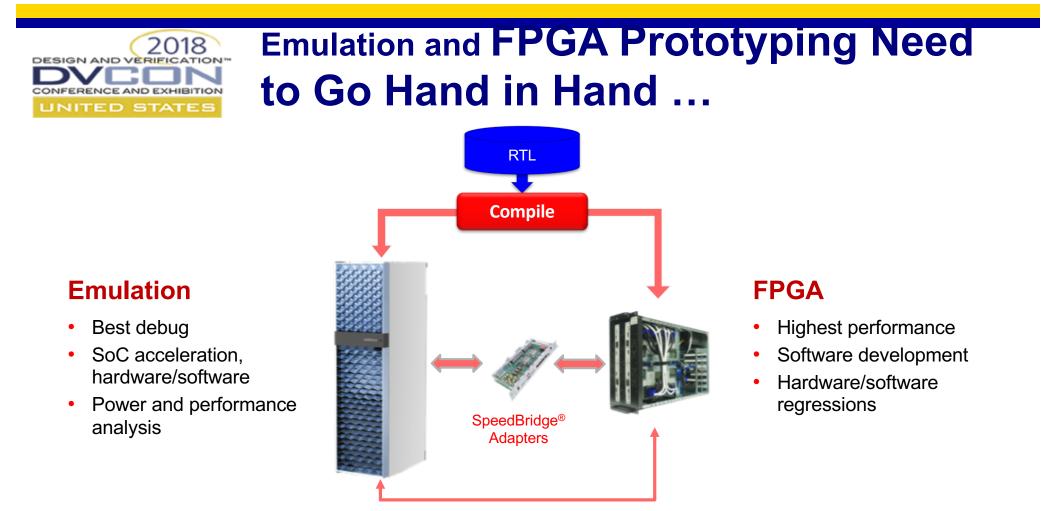

- Applying hardware to speed system verification

- Summary and call to action

© 2018 Cadence Design Systems, Inc. All rights reserved.

Project time

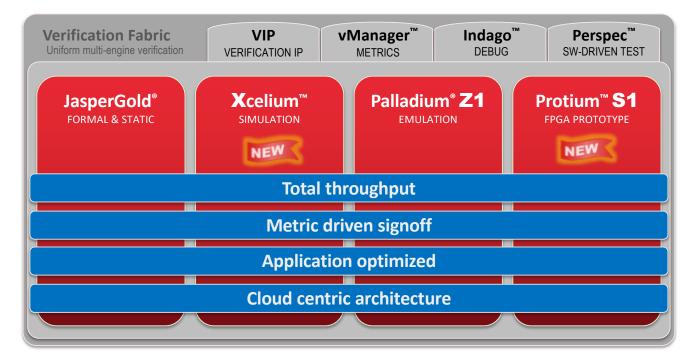

## **Verification Suite**

Technology innovation leadership: Fast, Smart, and Optimized

### • Fast Best-in-class engines

- Smart Flow-driven engine integrations

- Optimized comprehensive solutions

- The Need for Speed

- Formal methods to avoid sim cycles

- Coding for max sim speed

- Speeding power + mixed-signal SoC

- Break

- Portable Stimulus for faster verification

- Applying hardware to speed system verification

- Summary and call to action

-Fernanda Braga

-John Rose

-William Winkeler

-Sharon Rosenberg

-Frank Schirrmeister

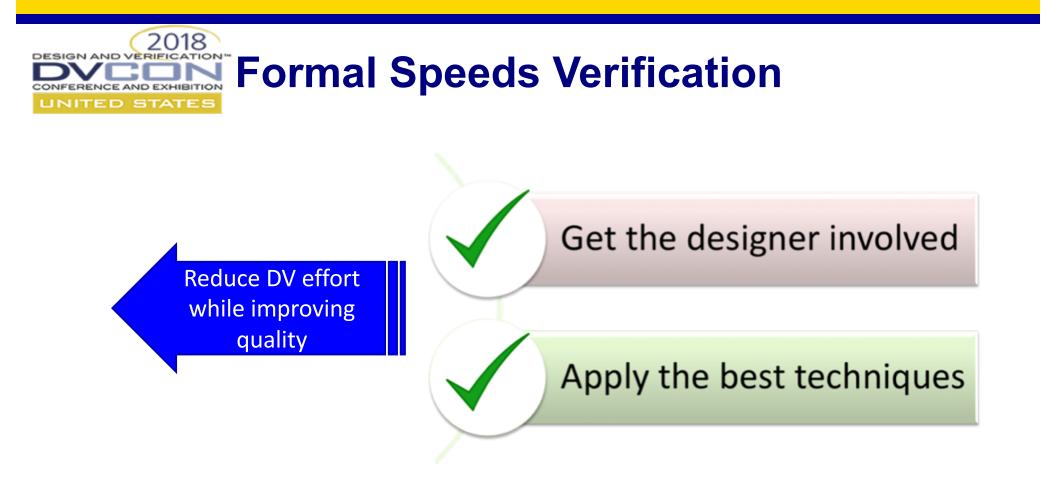

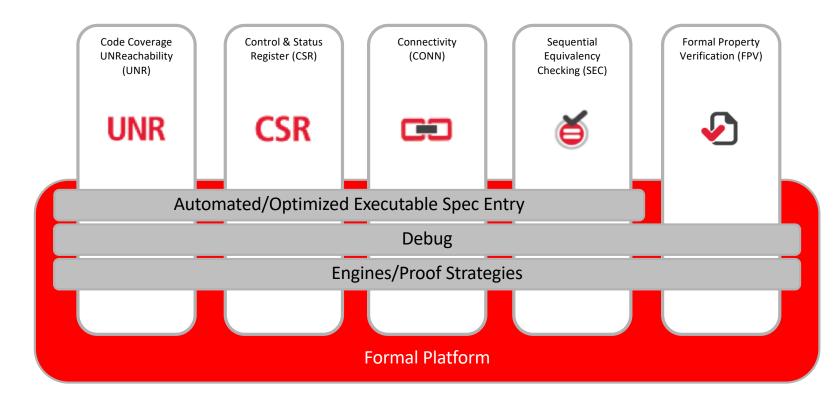

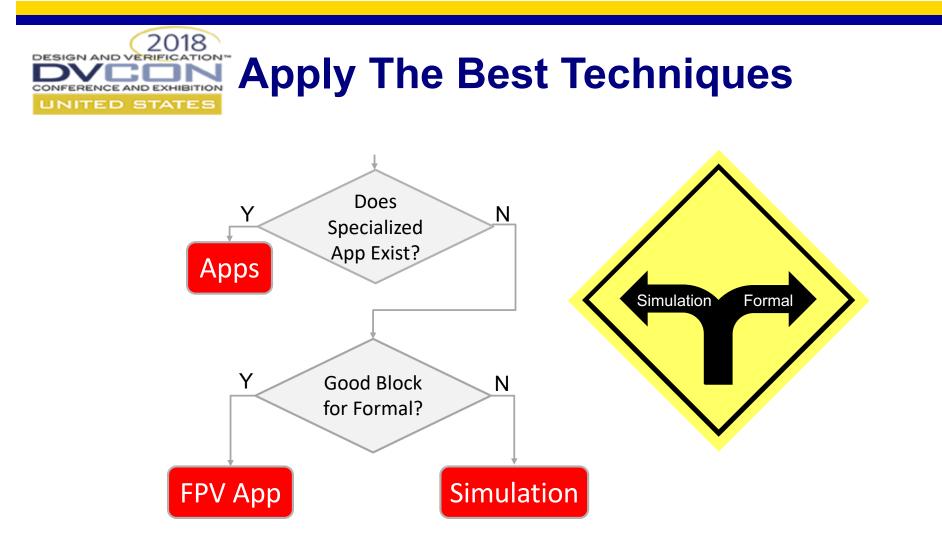

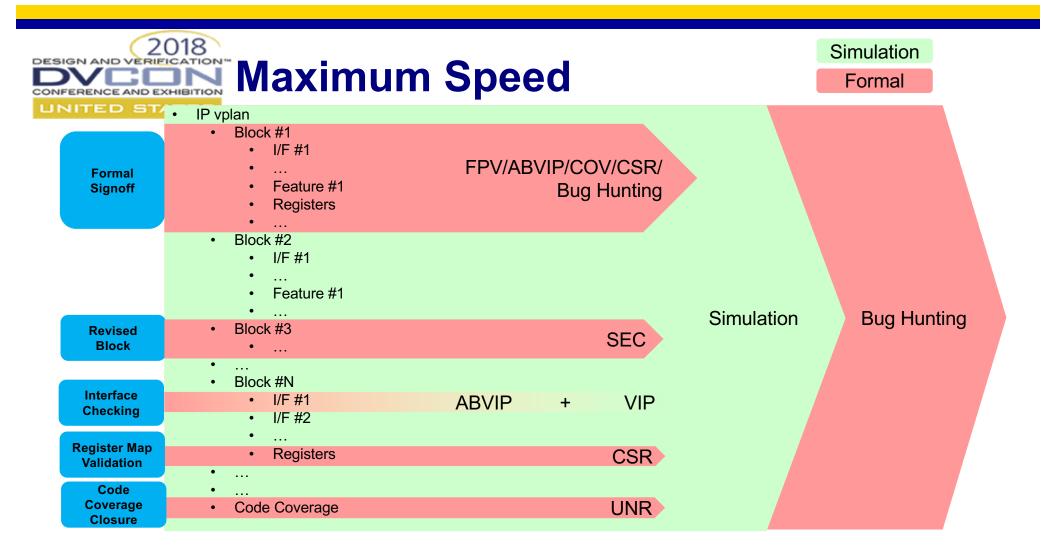

- Overview on how formal can speed up verification process

- Introduce Designer Formal Verification flow

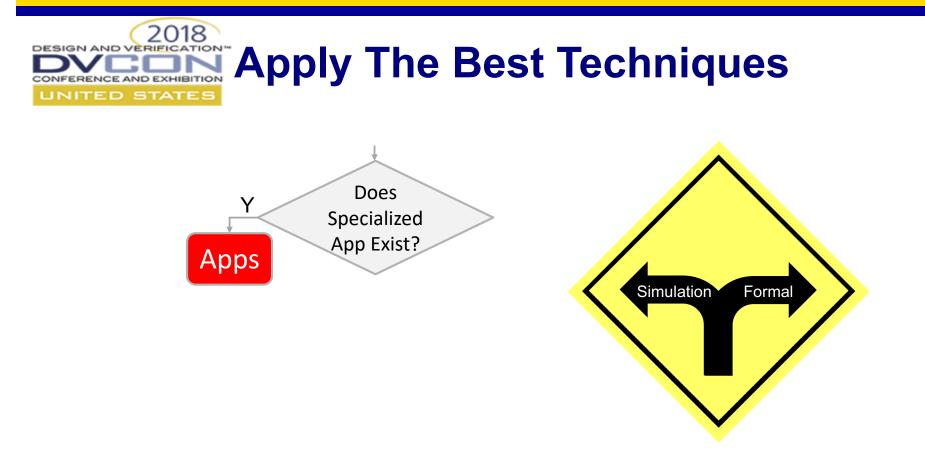

- Discuss when to use formal for maximized productivity

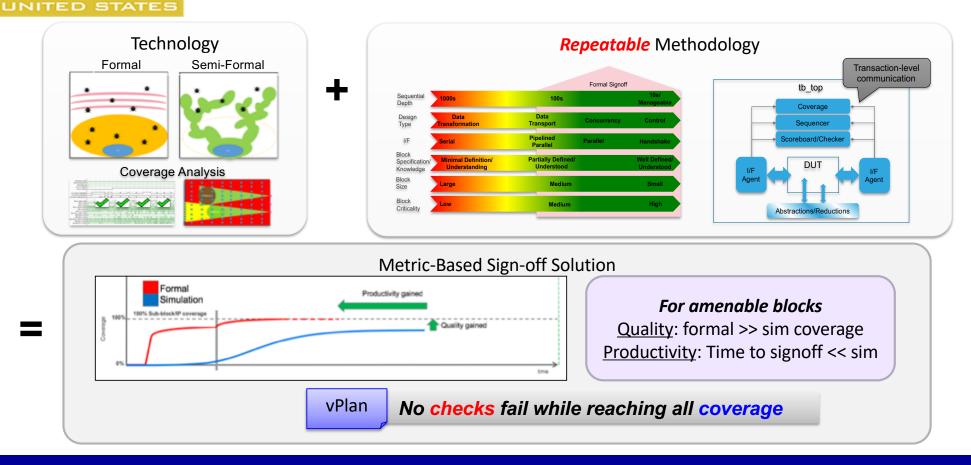

- Introduce methodology to address Formal IP Signoff

For many DV engineers their preferred verification method (simulation) is a hammer and everything looks like a nail

- The reality is

- Many users are already using formal as a sign-off tool for certain blocks and problems

- There are categories of designs which favor simulation and others which favor formal

- Formal, applied to the right designs and problems, can achieve significant productivity and quality gains in the overall verification flow

- Especially when simulation-like rigorous verification planning and coverage closure methodologies are applied

"FV wherever we can, simulate where we must" – Erik Seligman, JUG 2016

3/5/18

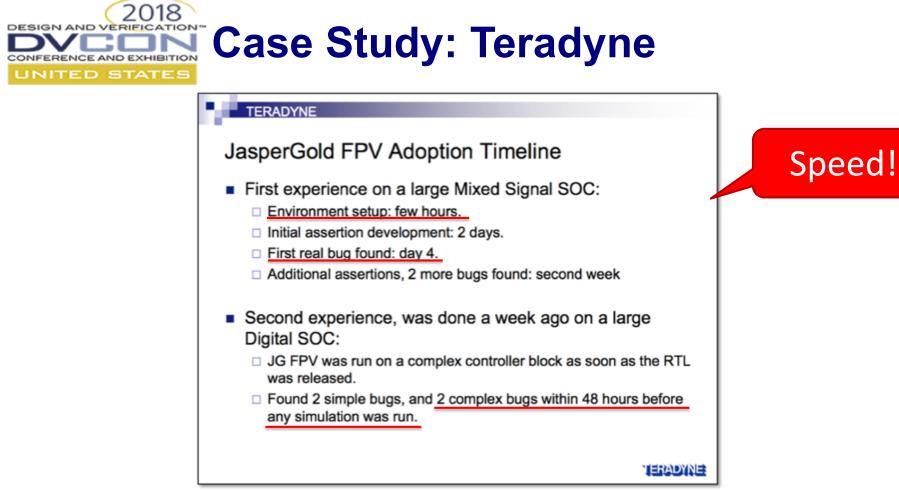

Source: Teradyne presentation at CDNLive Boston, Nov 2017

3/5/18

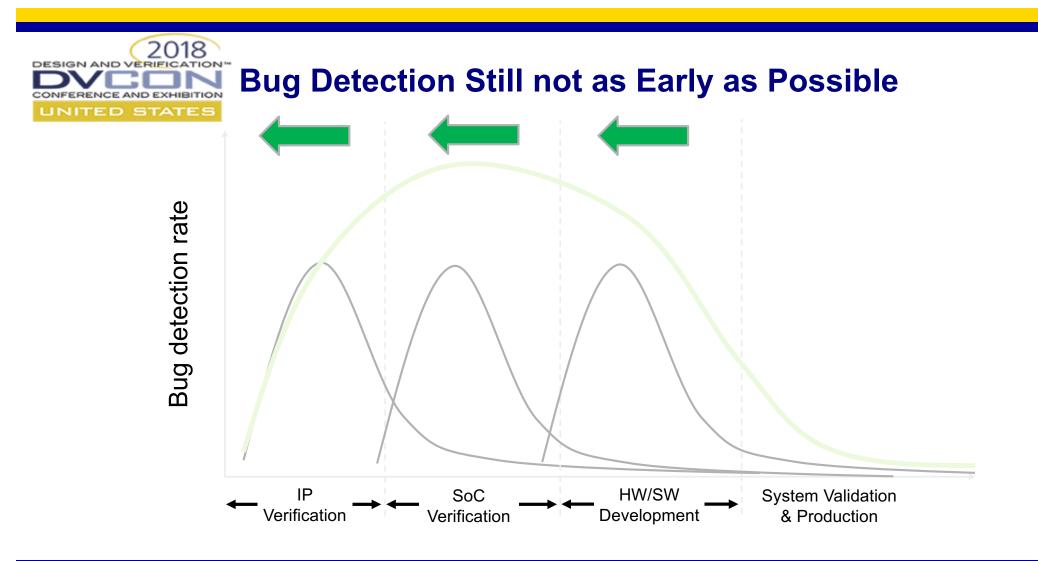

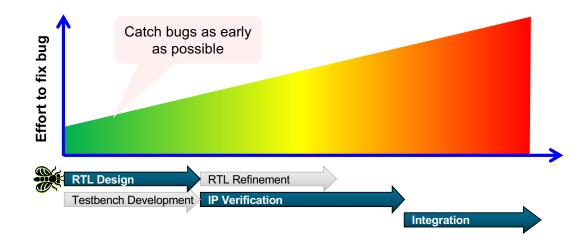

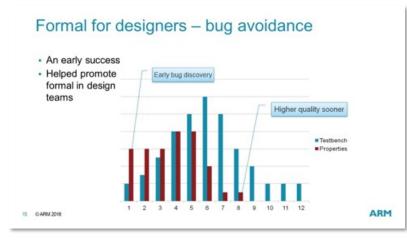

• Effort to fix a bug increases significantly the further into the development cycle

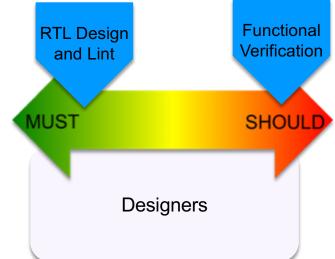

- Managers, verification engineers and even designers all agree that designers *SHOULD* get more involved in verification

- Reality is that RTL design, implementation tasks, etc. MUST get done

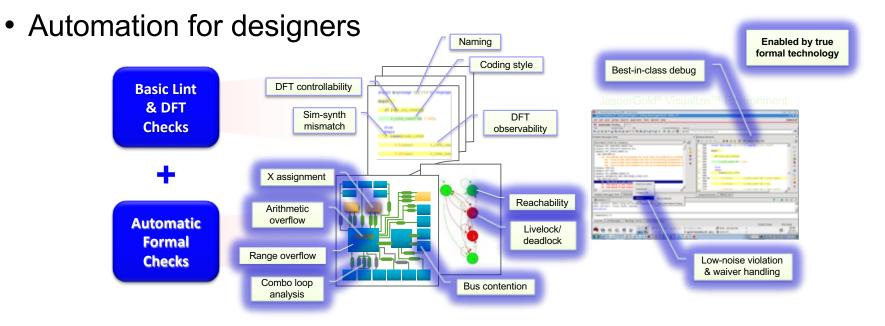

- Conclusion: Only successful way to get designers involved in functional verification is <u>automation</u>

### JasperGold Superlint: CONFERENCE AND EXHIBITION Hand-off Robust Reusable RTL

**Comprehensive functional checks, violation debug &** waiver handling based on best-in-class formal analysis

### • ARM

"We've been using the JasperGold Superlint App at ARM for more than a year, and we've had success with improving RTL signoff and shortening time to market. With the ability to find bugs weeks earlier in the design process, we've reduced late-stage RTL changes, which enables the team to save additional time when we get to the functional verification stage."

Hobson Bullman Vice President and General Manager Technology Services Group, ARM

Source: ARM keynote presentation at Jasper User Group, Nov 2016

3/5/18

3/5/18

### CONFERENCE AND EXHIBITION CONFERENCE AND EXHIBITION UNITED STATES CONFERENCE AND EXHIBITION CONFER

|                                                |                         | uick technology<br>: 5 IPs in 6 r           |                        |                   |                   | <ul> <li>Formal verification ensures better confidence in security features</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------|-------------------------|---------------------------------------------|------------------------|-------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                | IP AAA                  | IP BBB                                      | IP CCC                 | IP DDD            | IP EEE            | implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                | Mature IP, 50 registers | New IP (on-<br>going ), 189<br>registers    | New IP derivative      | New IP derivative | New IP derivative |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| nitial setup<br>formal tb already in<br>blace) | 1h                      | Early verif start                           | 2h                     | 2 wks             | On-going          | <ul> <li>IP-XACT based flow developed &amp; deployed</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RTL bugs                                       | 2, found immediately    | 10                                          | 1 found<br>immediately | 1 found           | On-going          | <ul> <li>Reduces effort needed to deploy register formal verification</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ssues in spec /<br>P-XACT                      | Several found           | Several found<br>before RTL<br>availability | inimediately           | On-going          | On-going          | Less errors, less debug as automation makes sure modeling layer & IP-XACT are<br>in line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Flow ena                                       | bles fast iter          | ations when n                               | ew RTL / spec          | deliveries        |                   | • Next                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                | More exhaus             | stive verification                          | n leading to m         | ore confidenc     | e                 | <ul> <li>Automate generation of a template for the modeling layer</li> <li>How to take benefit from this flow to reduce effort in UVM_REG based verification for the second secon</li></ul> |

|                                                |                         |                                             |                        | for our OTM       | 32 products       | Use of formal coverage & combined coverage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Source: STMicroelectronics presentation at CDNLive 2017

- No need of simulations JG is much faster for these kind of tasks

- <u>1 engineer can cover alone</u> all the connectivity task of a project very fast.

- Short time to write the script for the first time

- Short script for a long task = short task

- Few days of work instead of weeks

- Significantly reduced the effort for connectivity tasks!!!

- Totally re-usable written once and can be used for any other connectivity task

- We used the same script instantly in a <u>completely other project</u>

- Gives also unexpected connections can find hidden bugs

- 3132 connections proven with a button click in our last project using this method

- We <u>found several bugs</u> thanks to JasperGold

Source: DSP Group presentation at CDNLive 2016

3/5/18

• Definition already well established in industry

No checks fail while reaching all coverage

- Signoff is all about confidence

- IMPORTANT: Finding bugs

- CRITICAL: Finding no bugs while reaching a measurable, planned set of coverage

- Required:

- Verification plan specifying checks and coverage to measure progress and define done

- Technology and methodology to achieve signoff

3/5/18

### 2018 DESIGN AND VERIFICATION " **Formal Signoff Summary**

© 2018 Cadence Design Systems, Inc. All rights reserved.

CONFERENCE AND EXHIBITION

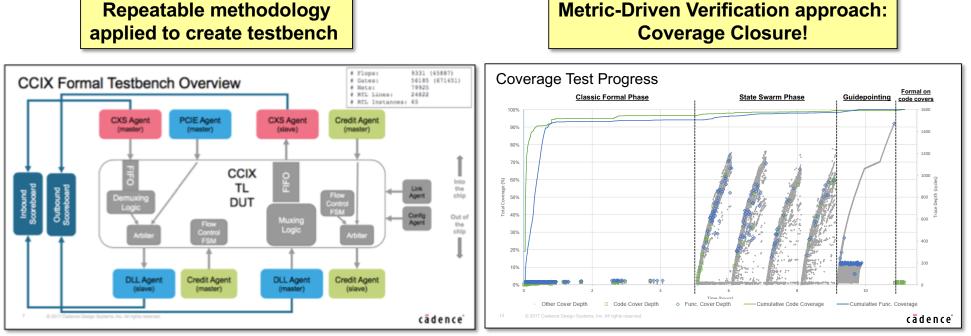

## JUNITED STATES JUG: Coverage-Driven Formal Verification Signoff on CCIX Design

• Partnership with IP Group at Cadence

Source: Cadence IPG presentation at JUG 2017

3/5/18

## JUNITED STATES JUG: Coverage-Driven Formal Verification Signoff on CCIX Design

• Partnership with IP Group at Cadence

| High quality bugs found                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                |                                                                                                     | Formal as viable option for IP signoff in amenable targets                                                                                                                                                                                                                                                                |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Formal                                                                                                                                                                                         | Sim                                                                                                 | Summary                                                                                                                                                                                                                                                                                                                   |  |

| # Assertions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 282                                                                                                                                                                                            |                                                                                                     |                                                                                                                                                                                                                                                                                                                           |  |

| Proof convergence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 61%                                                                                                                                                                                            |                                                                                                     | <ul> <li>No method is perfect!</li> </ul>                                                                                                                                                                                                                                                                                 |  |

| Bugs Found                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 29                                                                                                                                                                                             | Module:                                                                                             | <ul> <li>Formal behind sim in some areas, but ahead in others</li> </ul>                                                                                                                                                                                                                                                  |  |

| # "Exclusive" Bugs<br>Hard for other method to catch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                             | IP: 13<br>6                                                                                         | <ul> <li>Formal is competitive with simulation even on a complex block like CCIX         <ul> <li>Main challenge was that CCIX turned out to have more sequential depth than expected</li> <li>4KB packet length (100+ cycles), max credit update (1000+ cycles), timeout scenarios (1000+ cycles)</li> </ul> </li> </ul> |  |

| Formal Code Coverage:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | WOTR-4.CCH_P057E 1818                                                                                                                                                                          | 1410 1004                                                                                           | <ul> <li>Formal can do meaningful coverage closure         <ul> <li>Extend to end-of-test and incidental checking bring formal closer to sim wrt coverage</li> </ul> </li> </ul>                                                                                                                                          |  |

| □         0 mm_bit loss_bit         33         33         100 00%           □         0 mm_bit loss_bit         34         100 00%         100 00%           □         0 mm_bit loss_bit         100 00%         104         100 00%           □         0 mm_bits_bit         100 00%         1042         100 00%           □         0 mm_bits_bit         100 00%         1042         100 00%           □         0 mm_bits_bit         100 00%         100 00%         100 00%           □         0 mm_bits_bit         100 00%         100 00%         100 00%           □         0 mm_bits_bit         100 00%         100 00%         100 00%           □         0 mm_bits_bit         100 00%         100 00%         100 00%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                |                                                                                                     | <ul> <li>Enhance semi-formal even further         <ul> <li>Critical piece of signoff since it is where sim does a better job</li> </ul> </li> </ul>                                                                                                                                                                       |  |

| D (trans, in, colo, and trans, in, colo, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 51                                                                                                                                                                                             | 53 100.0                                                                                            | <ul> <li>Recommend to sign off with formal if:</li> </ul>                                                                                                                                                                                                                                                                 |  |

| Formal Functional Covera                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                |                                                                                                     | <ul> <li>Design is "formal friendly"</li> </ul>                                                                                                                                                                                                                                                                           |  |

| Constant even thread prev (MPANMC = 110, PO)     Constant, prev (MPANMC = 110, PO)     Constant, previous (packet, decoder trans, packet     Constant, packet, pack | et, bin-rain, packet, bin. 31<br>(, bin-rain, packet, bin. 409<br>d, bin-rain, packet, bin. 308<br>d, bin-rain, packet, bin. 308<br>d, bin-rain, packet, bin. 604<br>r/sink, bin060, COUNT. 25 | 5308 100 0<br>31 100 0<br>409 100 0<br>3438 100 0<br>306 100 0<br>604 100 0<br>25 100 0<br>25 100 0 | <ul> <li>Sequential depth is the most important factor</li> <li>Running simulation one level above target block</li> </ul>                                                                                                                                                                                                |  |

Source: Cadence IPG presentation at JUG 2017

3/5/18

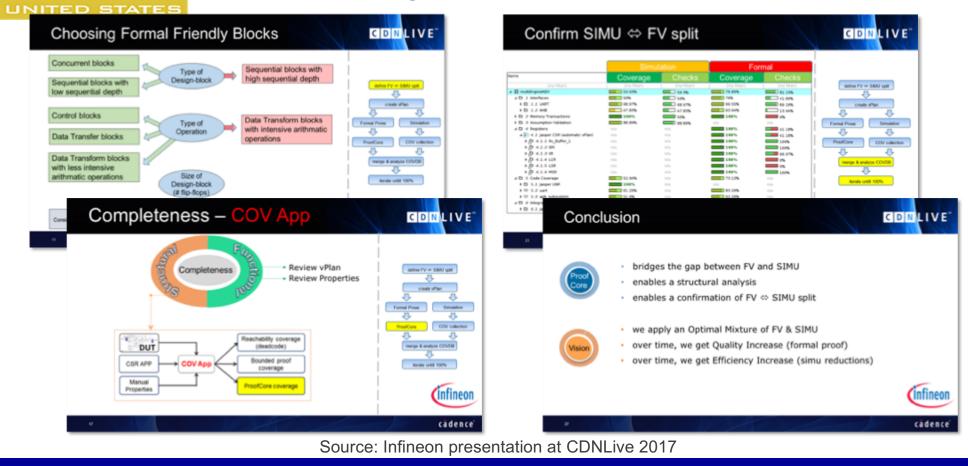

# Conference and exhibition Case Study: Infineon

3/5/18

- The Need for Speed

- Formal methods to avoid sim cycles

- Coding for max sim speed

- Speeding power + mixed-signal SoC

- Break

3/5/18

- Portable Stimulus for faster verification

- Applying hardware to speed system verification

- Summary and call to action

- General SystemVerilog Coding

- Coding for Multi-Core Simulation

- UVM Save / Restart Methodology

- SystemVerilog is BIG (800+ pages)

- Lots of opportunity to improve performance

- Focus today on a few of high-level concepts for making environments faster

- Caching data (results, objects, etc.)

- Focus on efficient algorithms

- Choosing correct data-structures

- What is not being discussed today

- Basic code optimization

- Assertion / Functional coverage coding

- Efficient randomization / constraint creation

- Comprehensive coding guidelines (including these topics and more) available at <u>http://support.cadence.com/</u> -- "Simulation Performance Coding Guidelines for SystemVerilog"

- Examples of when caching is effective

- The same inputs always produce the output

- When the calculation is done often (e.g. every cycle)

- The same inputs will often be repeated over the short term

- The calculation is expensive with respect to other things at the same time

- A class object can be reused

- When consumers of an object will take only what they want (won't keep a reference)

- When the object is heavy to create

- When the object has complex constraints (reuse of constraint construction)

```

function int unsigned hash(string key);

hash = 0;

for(int i=0; i<key.len(); ++i) begin

hash += key[i];

hash += (hash<<10);

hash ^= (hash>>6);

end

hash += (hash<>3);

hash += (hash>>11);

hash += (hash<<15);

endtask

```

What's the problem?

```

function int unsigned hash(string key);

hash = 0;

for(int i=0; i<key.len(); ++i) begin

hash += key[i];

hash += (hash<<10);

hash ^= (hash>>6);

end

hash += (hash<>3);

hash += (hash>>11);

hash += (hash<<15);

endtask

```

Nothing (it is simple and fast), but, it is a linear algorithm so there is a possibility for improvement

```

function int unsigned hash(string key);

static int unsigned cache[string];

//if you need to manage the cache size. Use a static

//array as will be the fastest.

static string aged_list[MAXSIZE];

static int oldest = 0;

// This is the savings if the same key gets used alot

if(cache.exists(key)) return cache[key];

... //normal cache algorithm

// This is the cache overhead.

cache[key] = hash;

cache.delete(aged_lsit[oldest%MAXSIZE]);

aged_list[oldest%MAXSIZE] = key;

++oldest;

endfunction

```

A simple cache may make things faster

```

task mycomp::run(uvm_phase_object phase);

forever begin

@(posedge vif.clk);

if(txstart) begin

local_data = mydata::create("data",this);

data.randomize();

send_recv_data(data); //some time consuming work

$cast(shared_data, local_data.clone()); //copy it

txport.write(shared_data); //send it on

end

end

endtask

```

```

task mycomp::run(uvm_phase_object phase);

forever begin

@(posedge vif.clk);

if(txstart) begin

local_data = mydata::create("data",this);

data.randomize();

send_recv_data(data); //some time consuming work

$cast(shared_data, local_data.clone()); //copy it

txport.write(shared_data); //send it on

end

end

endtask

```

Data is created every time through the loop, but only used locally.

```

task mycomp::run(uvm_phase_object phase);

local_data = mydata::create("data",this);

forever begin

@(posedge vif.clk);

if(txstart) begin

data.randomize();

send_recv_data(data); //some time consuming work

$cast(shared_data, local_data.clone()); //copy it

txport.write(shared_data); //send it on

end

end

endtask

```

Move data creation to only happen once.

- Know the complexity of your algorithm

- Constant (O(1)), logarithmic (O(logn)), linear (O(n)), quadratic (O(n2)) ...

- Watch out for loops in loops

- A loop is O(n)

- A loop inside a loop is O(n2)

- A loop inside a loop inside a loop is O(n3) ...

- Watch out how often you are doing work

- A linear algorithm executed every cycle will likely be problematic

- Watch what you do when operating on larger data sets (higher values of n)

- Can algorithm be changed to be constant or logarithmic?

- Can executions of the algorithm be minimized?

```

input real vin;

output real vout;

real vdata[512];

logic[8:0] ptr;

always@(posedge clk)

ptr<=ptr+1;

real sum;

always@(posedge clk) begin

vdata[ptr] <= vin;

sum=0.0; foreach(vdata[i]) sum+=vdata[i];

vout <= sum/512;

end

```

What's the problem?

```

input real vin;

output real vout;

real vdata[512];

logic[8:0] ptr;

always@(posedge clk)

ptr<=ptr+1;

real sum;

always@(posedge clk) begin

vdata[ptr] <= vin;

sum=0.0; foreach(vdata[i]) sum+=vdata[i];

vout <= sum/512;

end

```

Every edge we sum the array even though only one element changes

```

input real vin;

output real vout;

real vdata[512];

logic[8:0] ptr;

real curr=0.0;

always@(posedge clk)

ptr<=ptr+1;

always@(posedge clk) begin

vdata[ptr] <= vin;

vout <= curr/512;

curr <= curr-vdata[ptr]+vin;

end

```

Better to only do what is required each cycle

- · This is related to memory management and algorithms

- Memory management

- Dynamic data structures (dynamic arrays, queues, associative arrays, classes) have heap management overhead.

- Static arrays and structs are pass by value (no heap management)

- This overhead can be significant depending on how an object is used

- Basic QDA Algorithms

- Search

- Associative arrays are O(logn)

- Everything else is O(n)

- Front/back insertion

- Associative arrays are O(logn)

- Queues are O(1)

- Static and dynamic arrays are O(n) (must be done manually)

- Queues auto-size when needed

- Random insertion

- Associative arrays are O(logn)

- Everything else is O(n)

- General recommendations

- Use associative arrays when searches dominate

- Use queues for most dynamically sizeable random access objects

- Use static arrays anytime it is reasonable

- Use structs instead of classes for tuples (or simple metadata)

```

mydata datain[$];

task mycomp::write(mydata data);

data = data.clone();

datain.push_back(data);

endtask

task mycomp::check(mydata data);

foreach(datain[i]) begin

if(datain[i].unique_id == data.unique_id) begin

do_work(datain[i]);

datain.delete(i);

return;

end

end

do_error(data);

endtask

```

What is the problem with this?

Use an associative array instead Lookup and deletion are O(log(n)) instead of O(n)!

```

2018

DESIGN AND VERIFICATION*

Another Data Structure Example

UNITED STATES

class data;

int aval;

int bval;

What is the problem with this?

int extra;

endclass

data sparse memory[int];

function add elem(int addr, data d);

sparse memory[addr] = d;

endfunction

function data get elem(int addr);

data rval;

if(sparse memory.exists(addr))

rval sparse memory[addr];

else

rval = new;

return rval;

endfunction

```

# **Another data Structure Example**

```

class data;

int aval:

int bval;

int extra;

endclass

data sparse_memory[int];

function add elem(int addr, data d);

sparse memory[addr] = d;

endfunction

function data get elem(int addr);

data rval;

if(sparse memory.exists(addr))

rval sparse memory[addr];

else begin

rval = new;

sparse memory[addr] = rval;

end

return rval;

endfunction

```

There is no need for a class (no polymorphism or any class behaviors)

```

typedef struct packed{

```

```

int aval;

```

int bval;

```

int extra;

```

```

} data;

```

```

data sparse memory[int];

```

```

function add_elem(int addr, data d);

sparse_memory[addr] = d;

endfunction

function data get_elem(int addr);

return sparse_memory[addr];

endfunction

```

#### Change to a struct

- General SystemVerilog Coding

- Coding for Multi-Core Simulation

- UVM Save / Restart Methodology

- Multi-core simulation is similar to hardware acceleration except

- Uses standard servers

- Achieves acceleration by sending concurrent work to separate cores

- Some applications (such as wave dumping) also lend themselves to running in separate cores

- The same coding that works for acceleration works for multi-core

- Synthesizable code

- General guidelines

- Signal level activity should be in synthesizable bfms

- Reduce activity between accelerated and non-accelerated sections maximizes speed up

- Synchronized designs speed up the best but are not required

```

module somemod1 (input clk, ...)

always@(posedge clk)

...//complex expressions and assignments

always@(posedge clk)

...//more complex expressions and assignments

always_comb

...//best is to not have any timing

assign ... //best is to not have any timing

endmodule

```

```

module connector(input clk, ...)

clkgater gl(gclk,clk,cenable)

somemod1(gclk, ...);

othermod(clk, ...);

endmodule

Will attempt to associated

processes with clock or gated

version of clock

```

- What multi-core wants is

- Lots of independent processes active at the same time

```

© 2018 Cadence Design Systems, Inc. All rights reserved.

```

# **Coding for Multi-core Simulation**

```

module behav (myinterface mif, ...)

import vepkg::*;

//some rtl stuff

//some ve stuff

endmodule

```

```

module timedblock(...)

assign #1.1 w1 ----

assign #0.3 w2 = ---

assign #2.6 w3 -----

...

endmodule

```

All happen in different time slots so may not be able to be in parallel if there are interdependency

- What multi-core doesn't want is

- Behavioral code (things it can't synthesize)

- Lots of independent timing (very few events at a given time slot)

- General SystemVerilog Coding

- Coding for Multi-Core Simulation

- UVM Save / Restart Methodology

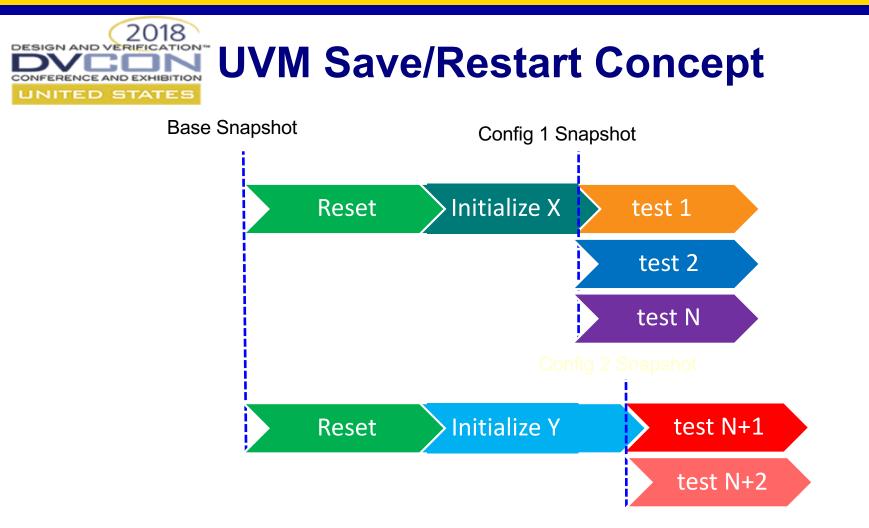

- Test sets tend to do the same initialization work prior to doing test specific work

- Device setup may take as much as 80% of the simulation time

- Treat the device setup as an extension of the build

- Build a base simulation snapshot

- Run the simulation to time N (when device setup is complete)

- Save the simulation snapshot at time N

- Run the test set using the saved simulation snapshot

- Make use of reseeding to run the same tests with different seeds

```

class base_restart_test extends uvm_test;

...

task run(uvm_phase_object phase);

init_seq init_seq = init_seq::type_id::create("init_seq",null);

test_seq seq;

init_seq.start(null, null);

$save(init_seq.get_type_name());

$value$plusags("SEQUENCE=%s",restart_seq_str);

seq = test_seq::type_id::create(restart_seq_str,null);

void'(seq.randomize());

seq.start(seqr, null, -1, 0);

endtask

endtask

```

- Each configuration is a UVM test

+UVM\_TESTNAME=config\_1

- Tests are virtual sequences loaded from command line arg

- +SEQUENCE=testseq

## **Questions?**

3/5/18

- The Need for Speed

- Formal methods to avoid sim cycles

- Coding for max sim speed

- Speeding power + mixed-signal SoC

- Break

3/5/18

- Portable Stimulus for faster verification

- Applying hardware to speed system verification

- Summary and call to action

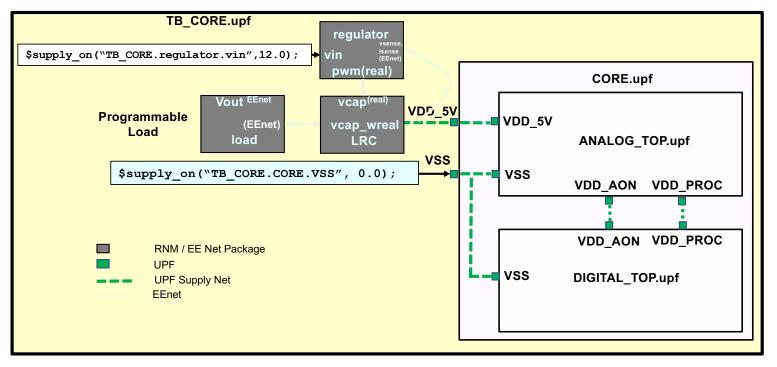

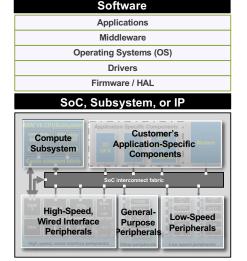

- Discuss verification of mixed signal SoC that is powered by an off-chip regulator driving on-chip supplies

- Processor based design powered by on-chip power supplies

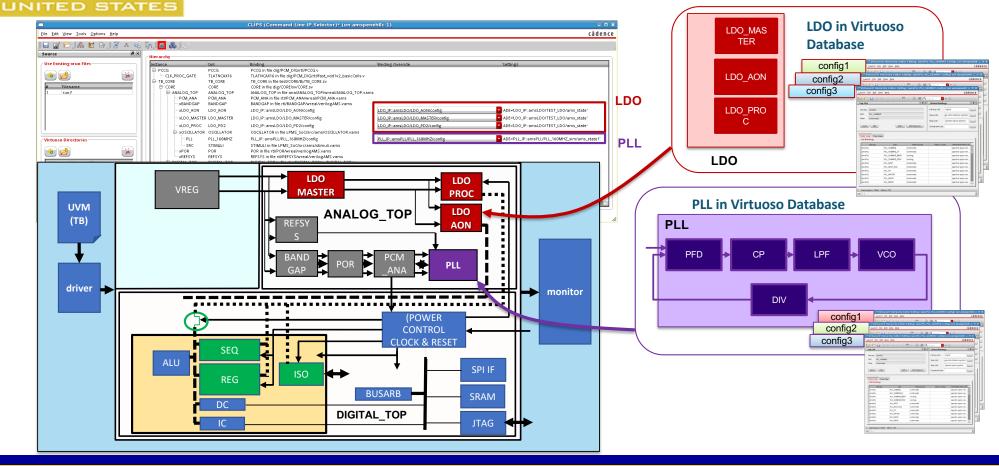

- Verify SPICE, RNM, AMS, Verilog models in the same environment

- All IP developed by Cadence

- Power intent specified in UPF 2.0

- Low Power Mixed Signal simulation run in UVM

- LDO (SPICE) driving UPF Power Supply Network

- Isolation, state retention, power shutoff

- Target Technology Cadence 45 nm GSCLIB045

# 2018 Low Power Basics

| Concept                             | Description                                                                                                                                           |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Domains                       | Group the elements of logic hierarchy that share the same primary power supply                                                                        |

| Supply Ports                        | Provide the supply interface to power domains and switches                                                                                            |

| Supply Nets                         | Connect supply ports                                                                                                                                  |

| Power Switch                        | Based on the value of the power control signal, the Power Switch connects / disconnects the input supply port to the output supply port of the switch |

| HDL Supply Net Control<br>Functions | UPF provides functions which enable the user to drive Supply Ports in low power simulation: supply_on, supply_off, supply_partial_on                  |

| Power Supply Network                | Consists of supply ports, supply nets and power switches and their interconnections                                                                   |

| LDO                                 | Low-dropout regulator. DC/DC converter used for on-chip power supplies                                                                                |

| Concept             | Description                                                                                                                                                                                                                   |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| State Retention     | Allows the contents of registers to be saved prior to power shutoff and recovered<br>when is power is restored<br>Usually performed on key control registers                                                                  |

| Isolation           | Prevents corrupted values from propagating from shutoff power domains to power domains which are powered up                                                                                                                   |

| Power Shutoff (PSO) | Power reduction method where power domains are shutoff. Shutoff can be<br>performed by Power Switch or by turning off the power to the supply ports.<br>Isolation and State Retention are often used in Power Shutoff Domains |

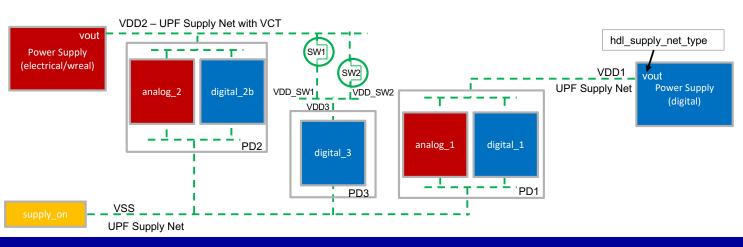

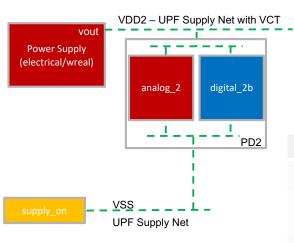

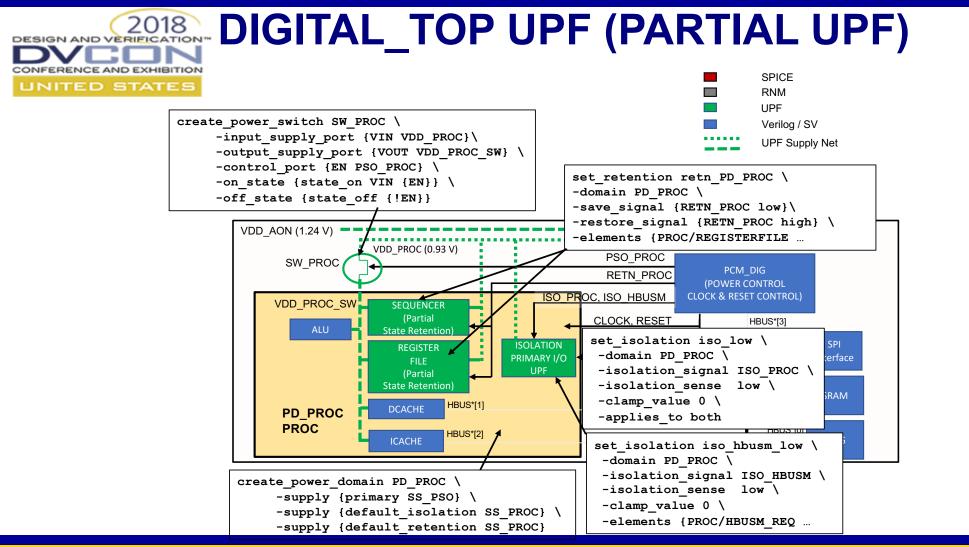

- Most Common

- HDL Supply Net Control Functions (supply\_on)

- UPF Power Switches

- hdl\_supply\_net\_type

- Drive UPF supply nets from HDL models

- UPF Package

SW1, SW2 – UPF Power Switches VDD\_SW1 – UPF Supply Net VDD\_SW2 – UPF Supply Net

VDD3 – UPF Supply Net with Resolution Function

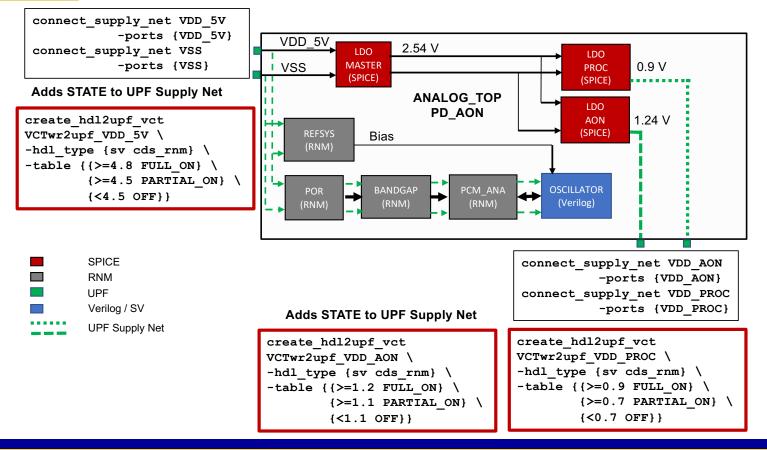

- UPF Supply Nets require a STATE and VOLTAGE

- STATE –

UNDETERMINED,

PARTIAL\_ON,

FULL\_ON, OFF

- wreal / electrical ports provide the VOLTAGE, but no STATE

- Add STATE through VCT (Value Conversion Table)

| <pre>create_supply_net VDD2<br/>create_hdl2upf_vct VCTwr2upf_VDD2 \ -hdl_type {sv cds_rnm} \ -table {{&gt;=4.8 FULL_ON} \ {&gt;=4.5 PARTIAL_ON} \ {&lt;4.5 OFF}}</pre> |                                                 |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--|

|                                                                                                                                                                        |                                                 |  |

| FULL_ON                                                                                                                                                                | Does not cause corruption                       |  |

| PARTIAL_ON                                                                                                                                                             | Enable / Disable corruption through UPF command |  |

| OFF                                                                                                                                                                    | Corrupt                                         |  |

| UNDETERMINED                                                                                                                                                           | Corrupt                                         |  |

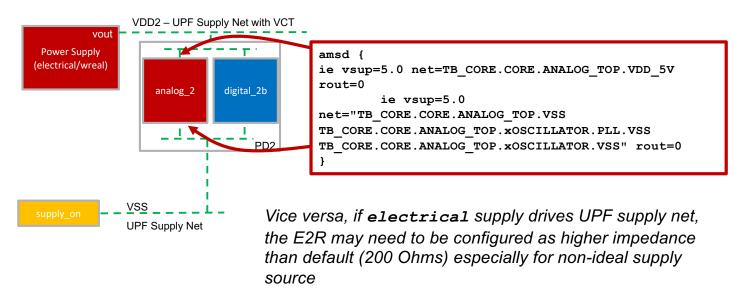

- The VOLTAGE from the UPF supply net is connected to the electrical signal by an internal R2E connect module

- The impedance of the R2E connect module is critical for analog block simulation

### **DESIGN AND VERIFICATION** Block Diagram & Power Architecture

CONFERENCE AND EXHIBITION

UNITED STATES

CORE (PD CORE) **TB\_CORE** VDD 5V 2.54 V LDO LDO MASTER VSS PROC (RNM) (SPICE) (SPICE) 12 V -> 5 V. ANALOG TOP Programmable Load LDO PD\_AON AON RNM / EE Net REFSYS (SPICE) Bias **Off-Chip** SPICE RNM OSCILLATOR UPF BANDGAP PCM ANA (Verilog) (RNM) Verilog / SV **UPF** Supply Net Clock. POR Reset VDD AON (1.24 V) VDD\_PROC (0.93 V) PSO PROC SW PROC PCM\_DIG LPM RETN PROC (POWER CONTROL ISO PROC, ISO HBUSM **CLOCK & RESET CONTROL)** VDD PROC SW SEQUENCER (Partial CLOCK, RESET HBUS\*[3] State Retention HBUS\*[4] ISOLATION Н REGISTER DIGITAL TOP PRIMARY I/O В Interface PD AON 11 (Partial S State Retention) HBUS\*[5] BUSARB SRAM HBUS\*[1] DCACHE PD PROC PROC HBUS\*[0] HBUS\*[2]

© 2018 Cadence Design Systems, Inc. All rights reserved.

| Power State      | Description                                                                                                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Up         | LDO AON powers up, Power On Reset,<br>Clock Enabled, JTAG, BUSARB, PCM_DIG on                                                                                                                                          |

| Load SRAM        | JTAG loads PROC object code<br>LDO_PROC powers up<br>PROC executes instruction thread                                                                                                                                  |

| Power Down PROC  | LPM_ asserted. Cache flush started, clock gated, state saved, isolation enabled.<br>Power Shutoff by Power Switch SW_PROC                                                                                              |

| Power Up<br>PROC | LPM_ released. PROC power on – SW_PROC turned on. Restore state, release state.                                                                                                                                        |

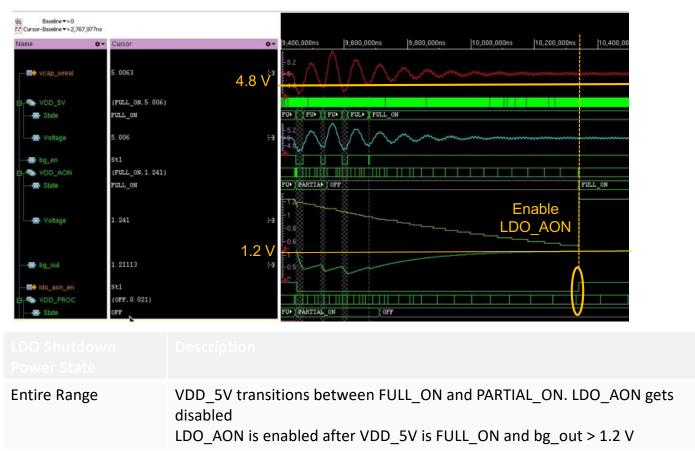

| LDO Shutdown     | Output of VREG is heavily loaded, causing LDO_AON and LDO_PROC to be shutoff.<br>Load is removed, enter Power Up State.<br>After POR, enter into LOAD SRAM state<br>After LOAD SRAM – PROC executes instruction thread |

# **Switch in AMS Design Configuration**

© 2018 Cadence Design Systems, Inc. All rights reserved.

3/5/18

2018 DESIGN AND VERIFICATION"

# DESIGN AND VERIFICATION VDD\_5V TRANSITIONS TO FULL\_ON

1

CONFERENCE AND EXHIBITION

UNITED STATES

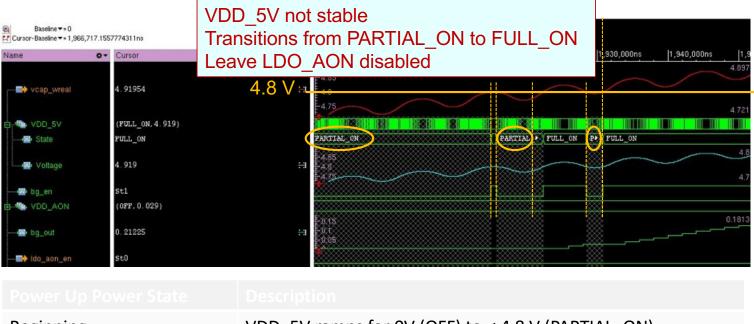

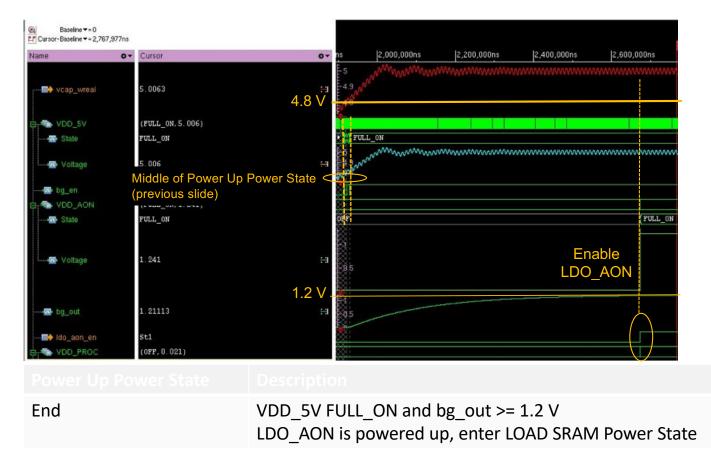

| Beginning | VDD_5V ramps for 0V (OFF) to < 4.8 V (PARTIAL_ON)<br>(PARTIAL_ON -> OFF). Waveform not shown                                                |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Middle    | VDD_5V has multiple transitions between FULL_ON and<br>PARTIAL_ON<br>Disable LDO_AON until VDD_5V is FULL_ON and BANDGAP<br>output >= 1.2 V |

# 2018 VDD 5V TRANSITIONS TO FULL ON

11

CONFERENCE AND EXHIBITION UNITED STATES

# **LDO SHUTDOWN POWER STATE**

• Low Power MS simulation allows user to verify the operation of on-chip power supplies, clock generation, reset, and digital logic concurrently

| Issues Found                            | Description                                                                                                                                                              |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PSN Errors                              | Debugged using SimVision Power Supply Network. Usually found at start of LP verification cycle                                                                           |

| Incorrect parameter setting on POR cell | VREF_LDO parameter was initially set to 2.4 v instead of 4.8 v. Result<br>– LDO_AON turned on too soon produced wrong output voltage.<br>Digital logic did not function. |

| Incorrect registers for state retention | PROC / UPF developers worked together to determine correct registers for state retention strategy                                                                        |