# Simulation Acceleration with ZeBu to Speed IP and Platform Verification

Hillel Miller, Wei-Hua Han – Synopsys

## Agenda

Customer stories and ZeBu simulation acceleration technology overview (45 minutes) – Hillel Miller

AXI example (25 Minutes) – Wei-Hua Han

Q&A (10 Minutes)

#### Customer story one

My simulations, for my design verification environment are very slow, next generation it will be much slower, even 2x will help

We will do anything for 2x

My VP has given me an initiative to achieve 2x

#### Customer story two

- I am developing a graphics core as third party IP vendor

- I need to do power estimation of my graphics core with Manhattan test case

- It takes more than 2 weeks to run the simulation to get power estimation numbers in my SystemVerilog environment

- I want to complete this effort in less than 24 hours

#### Customer story three

- My simulations are very slow

- My Top Level Verification (TLV) environment, uses embedded C test cases running on our DSP core in RTL simulation model. The C test cases are far more successful then standalone UVM environments in finding bugs

- Some of the test cases take weeks to run

#### Customer story four

- I have an IP level UVM environment, with custom UVM VIP. My long test take days to run for number of packets in 10,000's range. My next generation IP will be 2x more complex and expect simulation performance to degrade

- We are missing bugs found by SoC

- My current regression runs on 100 machines

- I need two things

- Run at least 100x faster so that I can match simulation regression running on 100 machines

- Run millions of packets

#### Customer story five

My SoC test cases take days to run. My next generation will run even slower

I have been using Synopsys tools SVT VIP, NLP, SVA, URG, Verdi for as long as can tell

I would like to use the ZeBu emulator under the hood without any changes to speed up my simulations

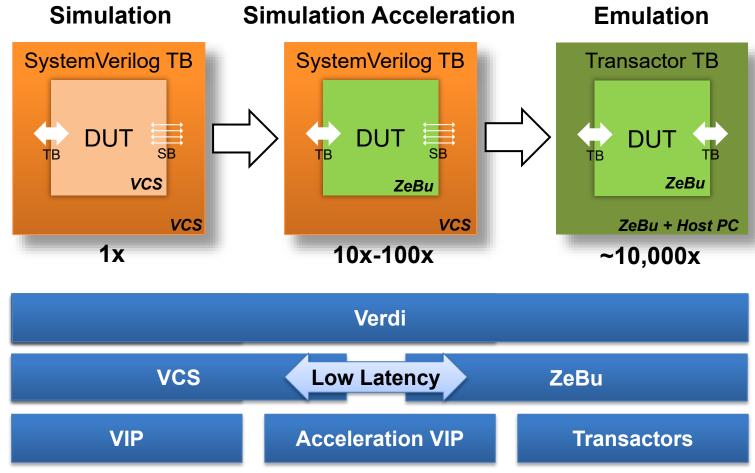

#### Simulation Acceleration with ZeBu

10-100x higher performance

#### **Benefits**

- Native integration with VCS

- Fully automated compile of testbench and design

- Industry leading VCS and ZeBu performance

- Integrated, interactive Verdi debug

- Coexistence of Signal and Transaction-based communication

- Low latency HW/SW interface

- Acceleration VIPs for additional acceleration

## DVC N CONFERENCE AND EXHIBITION UNITED STATES

#### **Continuous Simulation Acceleration**

Ability to incrementally change and mix HW/SW communication capabilities

#### Simulation Acceleration

| Customer Design |                | Acceleration factor | Туре |

|-----------------|----------------|---------------------|------|

| Multimedia      | Sub-System     | 25x                 | TBA  |

|                 | Sub-Systtem    | 80x                 | SBA  |

| Multimedia      | Block          | 18x                 | SBA  |

|                 | SoC            | 14.5x               | SBA  |

| Multimedia      | Sub-System     | 1.5x                | SBA  |

|                 | Sub-System     | 4.8x                | SBA  |

|                 | Sub-System     | 1.5x                | SBA  |

| Processor       | Sub-System     | 6.0x                | SBA  |

|                 | Sub-System     | 8.0x                | SBA  |

| Processor       | CPU Sub-System | 6x                  | SBA  |

| GPU             | Sub-System     | 28x, 64x            | SBA  |

|                 | Sub-System     | 104x, 2091x         | TBA  |

| Networking      | Block          | 62x                 | TBA  |

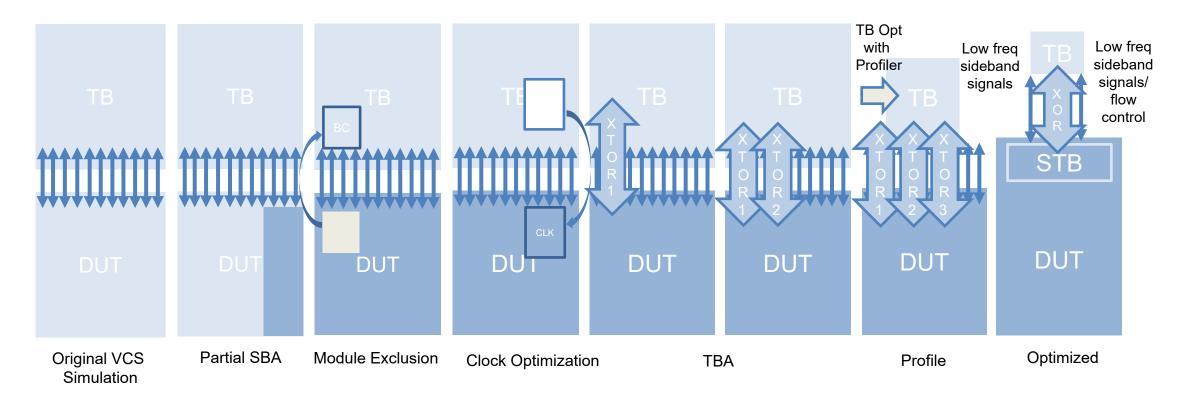

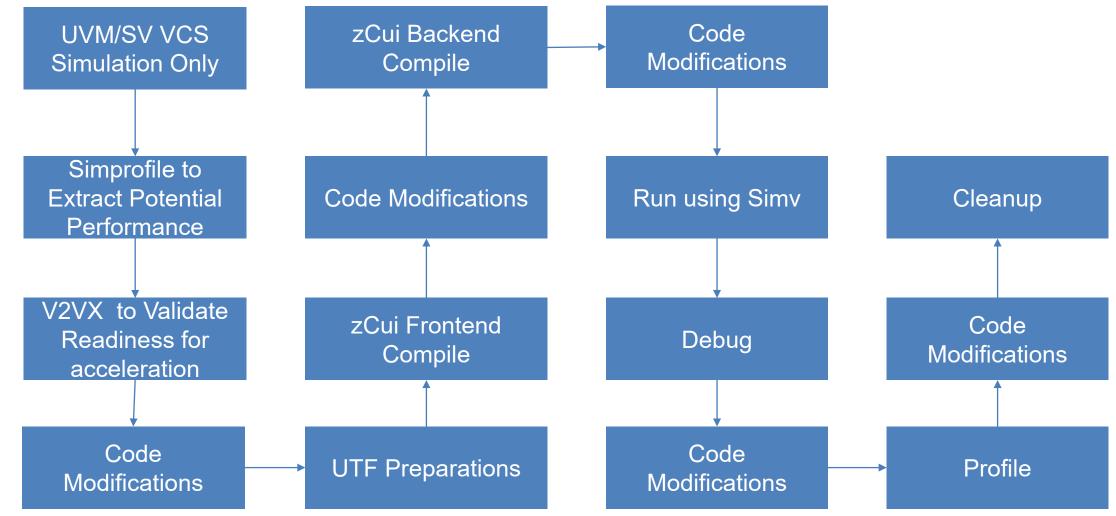

#### Deployment Steps for UVM/SV

#### VCS Options – V2VX mode

- Uses only VCS for both HW and SW compilation. Used for pipe cleaning before moving to ZeBu compile

- VCS Compile option to enable V2VX mode: -Xhwcosimtest=v2vx

- VCS Compile option to specify HW top level instance: Xhdl\_cosim\_dut <hierarchical path to the HW instance> If module

is compiled as a top-level module, then it will be the name of the

module

- Run using existing simv options

- Debug using Verdi

SYSTEMS INITIATIVE

#### UTF Options – V2Z mode

- Uses ZeBu for HW compilation and VCS for SW compilation

- UTF files is a list of commands specifying at a high level how to execute the compile

- ZeBu zCui tool will do the full compile with a UTF file as input and the UTF file pointing to the VCS compile, using the UTF command VcsCommand

- Compile generates a zcui.work directory which is used at runtime to enable VCS to cosimulate will the emulator

- For compile add the following UTF options and VCS compile options:

- UTF command to enable acceleration: simxl –enable true

- UTF command to specify HW top level instance

- simxl\_set\_hwtop -instance <hierarchical path to the HW instance>

- All logic from that instance and below will go into HW. If module is compiled as a top-level module than it will be the name of the module.

- ZCUI compilation GUI is opened using: zCui -u project.utf

- Push the Make Target button in the ZCUI GUI to start the compile process

#### VCS Compile/Runtime – V2Z mode

- VCS additional compile option to generate diagnostic data in current run directory

- -Xhwcosim=diag

- Run using SIMV additional runtime option to point to zcui.work for HW database: +zcui.work=<zcui.work directory generated by zCui>

## Structural Signal Communication

- Signal communication using the following primitive data types for signals:

- wire, wand, wor, tri, etc.

- reg

- logic

- enum

- byte

- integer

- int

- shortint

- longint

- Signed modifier can be applied to any of the above data types.

- Signal communication using the following aggregate data types:

- Packed arrays.

- Unpacked arrays.

- Multi-dimensional arrays.

- Packed structs.

- Unpacked structs.

- -Unions.

- Any composition of the above data types.

- Signal communication using interface ports:

- Interface ports containing signals with any of the above types.

#### Structural Signal Communication: Clocking

```

// Running in ZeBu

module HW(input wire clock, input logic reset);

endmodule

// Running in VCS

interface ift;

logic clock;

logic reset;

assign HW.clock = clock;

assign HW.reset = reset;

clocking cb @(posedge clock);

output clock;

output reset;

endclocking

endinterface

module SW;

ift m if();

Endmodule

```

#### Structural Signal Communication: Datatype

```

typedef struct {

integer source;

integer destination;

} descriptor;

module HW(input wire clock, input logic reset,

input wire descriptor d[100]);

endmodule

interface ift;

descriptor m d[100];

genvar i;

for (i=0; i<100; i++)

assign HW.d[i] = m d[i];

endinterface

module SW;

ift m if();

endmodule

```

## Behavioral Signal Communication

```

module hw(input a);

reg b;

endmodule

module sw;

reg c;

initial

hw.b = c;

endmodule

```

#### Force/Release HW from SW

```

module hw(input a);

reg b;

endmodule

module sw;

reg c;

initial begin

force hw.b = c;

wait(my_event.triggered);

release hw.b

endmodule

```

#### Assertion and Coverage in HW

To enable functional coverage and assertions at compile time, use the following UTF commands:

coverage -enable true // Enables covergroups specified in HW assertion\_synthesis -enable ALL // Enables assertions and coverage properties specified in HW

To activate functional coverage and assertions at runtime, add the following options to the simv command:

```

-simxl=enable dut fcov, enable dut sva

```

Coverage data is generated in the simv.zebu.vdb file.

No special options are required to enable functional coverage and assertions in SW. To merge coverage data from HW with coverage data from SW, use the following URG command:

```

urg -dir simv.vdb simv.zebu.vdb

```

#### Preloading HW memory using SW

```

interface ift;

logic [0:255] mem [4096];

endinterface

module dut;

endmodule

module HW;

ift m if();

dut dut();

endmodule

module SW;

initial

begin

$readmemh("data.hex",

HW.m if.mem);

$writememh("data copy.hex",

HW.m if.mem);

end

endmodule

```

## **Export Subroutine Call**

```

interface ift;

task task1(output o1);

begin

01 = 1;

end

endtask

function integer calculate();

return(0);

endfunction

endinterface

module HW();

ift m if();

endmodule

module SW();

logic a;

initial

begin

HW.m if.task1(a);

$display("A: %d, CALC: %d", a,

HW.m if.calculate());

end

endmodule

```

#### Import Subroutine Call

```

class C;

function void observe(input integer i1);

$display("I: %d", i1);

endfunction

endclass

interface ift;

bit configure done = 0;

C m handle;

function void configure(C handle);

m handle = handle;

configure done = 1;

endfunction

initial begin

wait (configure done == 1);

m handle.observe(4);

end

endinterface

module HW();

ift m if();

endmodule

```

```

module SW();

C c1 = new();

initial

begin

HW.m_if.configure(c1);

end

endmodule

```

#### Moving HW module to SW

- Reasons to moving HW module to SW

- HW module has constructs that are non-synthesizable

- Instance of HW module is being accessed from SW in a non-supported way\

- HW module is causing a compile bottleneck

- Instance of HW module is causing runtime failures

- Add the following VCS option for V2VX flow

```

-Xhdl_cosim_etb <module name>

```

Must be specified for each module that is moved from HW to SW

Add the following UTF command for V2Z flow:

```

simxl move to tb -module {<module name list>}

```

All Modules specified above will execute in SW, using their HW context.

#### Moving clocks from SW to HW

- Reasons for moving clocks from SW to HW

- Clocks toggling in SW increase HW/SW interaction slowing down performance.

- #-delays executing in HW avoid all kinds of issues related to semantics, synchronization, race conditions, etc.

- Changes required to support clocks in HW

- Add new wrapper module that will instantiate the design and clocks.

- Wrapper module will be instantiated instead of DUT and should have same ports as DUT except for clocking ports. All XMRs will need to be updated to add wrapper segment.

- Create clock generator module that will contain implementation of a clock using #-delay. See example below.

- Add following commands to UTF file

```

clock_delay <name of clock generator module> -tolerance auto

clock_config -accuracy 32

```

- // Needed when there is not enough bits to scale all clock frequencies

- Try maintain single timescale throughout the parsed database.

- Validate changes by running representative test cases in simulation only.

#### Guidelines: Time synchronization

- Usage of #-delays in SW

- #-delays should not be used in SW

- Price of usage is very high as HW needs to sync with SW every event clock

- There is a feature in VCS that identifies all #-delays

- Compile option for VCS is: -simprofile.

- Runtime option for SIMV is: -simprofile delay

- Event clock granularity is determined by smallest precision of timescales in HW

- For example, if SW has #1 for timescale 1ns/1ns and HW has timescale 1ns/1fs, then there will be 1, 000, 000 synchronization points.

- Use events that are originated from HW to control synchronization on SW side

#### Guidelines: Time synchronization

- Simplify RTL or SW clocks

- Try keep clocks with whole unit ratio's between clocks

- Complex clocks in SW will slow down simulation significantly

- Do not use decimal point for clock implementations

- Minimize the number of clocks used, eliminate all unnecessary clocks (e.g. test clocks, random delayed clocks, etc)

- For RTL clocks use tolerance feature to reduce number of clock events

- Clock events are synchronization events that are used to determine the next time stamp.

#### Guidelines: Time synchronization

- Simplify usage of timescale

- Do not use decimal point in #-delays which requires needing timescale precision

- Waveform calculation uses timescale finest precision as calculate rate. Finest precision may be an overkill

- Coordinate single usage of timescale directive across the project

- Validate changes to timescale using simulation test case

- Waiting for HW clock cycles on SW side

- Do not call export task to wait for clock cycles

- The same export cannot be called simultaneously during acceleration

- Use an XMR to the clock in the HW side and repeat statement to wait for a finite number of clocks cycles (e.g. repeat @(posedge vif.clock))

SYSTEMS INITIATIVE

#### General Guidelines

- Avoid explicit initialization of memory or registers to Zero

- Many wasted cycles, those elements are initialized to zero by default

- Use +vcs+initreg+random at vcs elaboration time and +vcs+initreg+0 at runtime, for VCS simulation only

- Avoid calling tasks from always block for cycle update of variables.

- Inline the update

- Synthesis doesn't handle this well

- Avoid doing 100k's backdoor to explicit memory addresses or registers from SW

- This is not as fast as VCS simulation

- Updates should be done in HW through Transactors

- May contain a lot of additional overhead in gate count.

- Bring up in the shortest running test available

- Full vision is usually only achievable with a short run

- Identify partial test and run till first point of failure

## General Guidelines (Cont'd)

- Initiate all actions from HW as much as you can.

- Bind transactors to HW that initiate transactions.

- Try to make actions non-time consuming.

- Avoid scheduling on SW side, to reduce SW overhead.

- HW synchronization is better over synchronization in SW.

- Implement transactor as BFM as much as you can

- Runs on HW, needs to be synthesizable and not behavioral code, to achieve maximum performance.

- Use a thin layer of behavioral code.

#### Incremental Compilation

- Incremental compilation is implemented in the simulation acceleration flow

- Xhwcosim=incr\_comp

- VCS detects if the second compilation interface database is subset of previous database

- Avoid new ZeBu compilation

- Examples

- Changes are completely local to testbench

- Removing port connections or SW to HW XMRs from second compilation

- User can force TB only compilation if he is sure there is no change in HW and SW/HW communications

- UTF command: simxl\_tb\_compile\_only -enable true

- Incremental compilation diagnostics

- Xhwcosim=incr\_diag

- "IncrDiag.txt" dumped with info about if TB and DUT communications changed or not

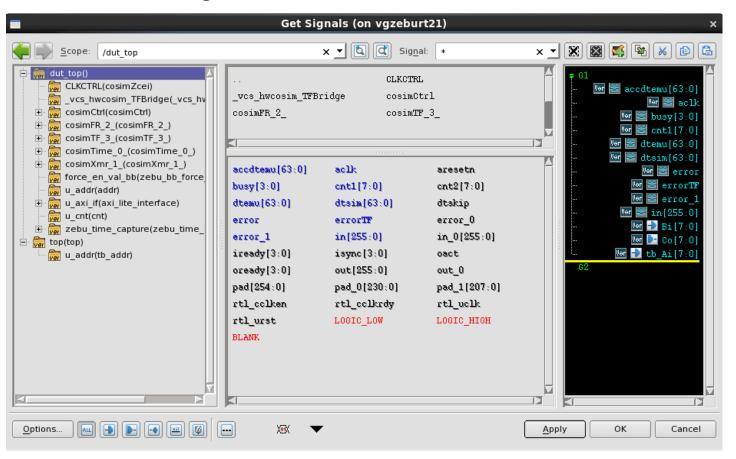

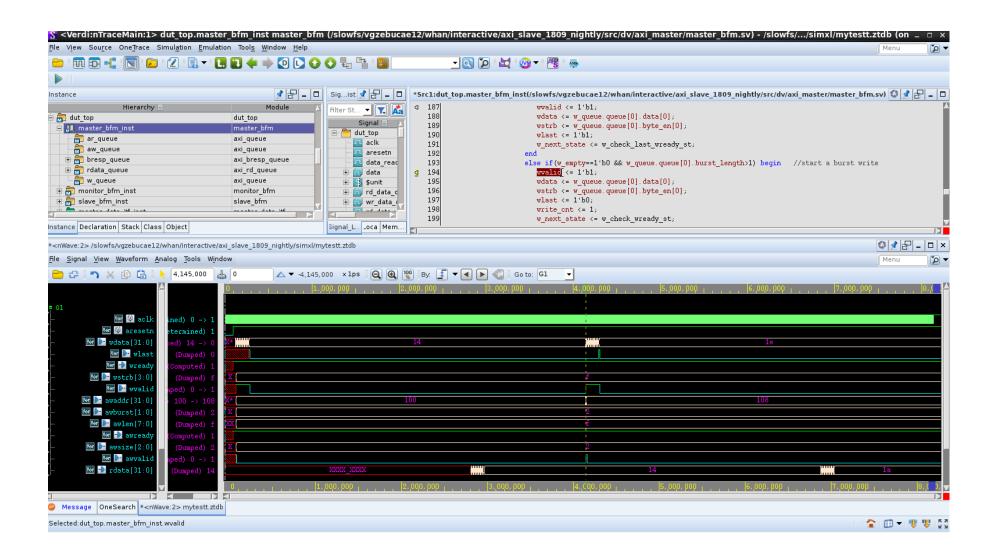

#### INTERACTIVE DEBUG WITH VERDI

SYSTEMS INITIATIVE

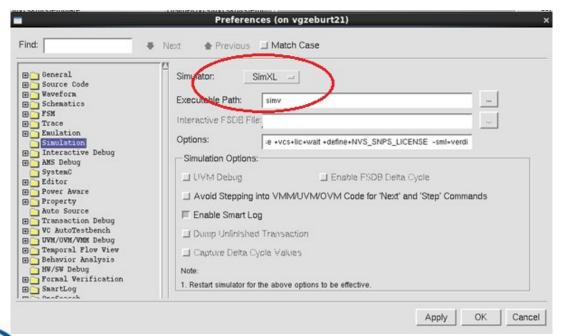

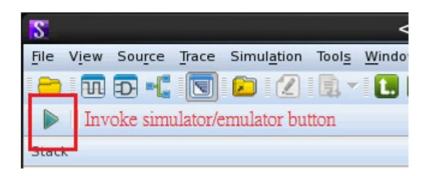

#### Invoking Verdi

#### Invoke simulation acceleration option in Verdi command line

verdi -simBin simv -i -emulation -lca -simXL --root (ztdbHwRoot) -simDelim

+zcui.work=zcui.work/zebu.work +zebu.verbose +vcs+lic+wait

+define+NVS SNPS LICENSE

(Green part is Verdi option; blue part is runtime option; use "-simDelim" to separate them)

Invoke simulation acceleration using preference dialog in Verdi

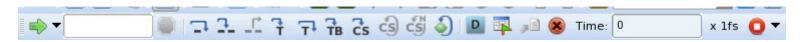

#### Verdi Interactive Debug Toolbar

- Run

- Stop

- Next

- Step in

- Step out

- Step in thread

- Next in thread

- Step in TB

- Step in Constraint Solver

- Restart

- Dump emulation file

- Breakpoint manager

- Go to active file/line

- Quit simulation

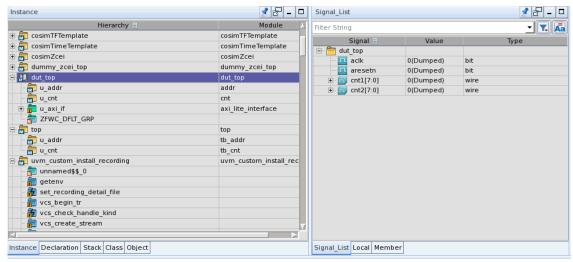

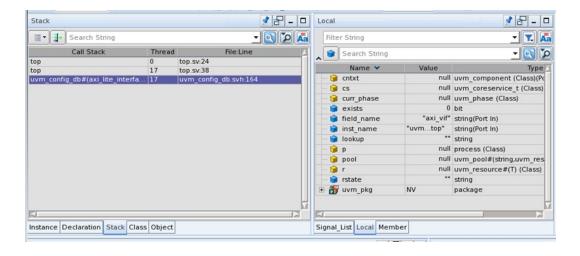

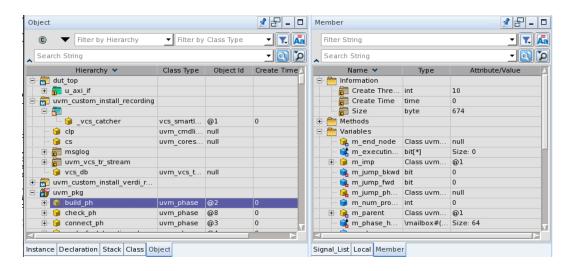

#### Verdi Interactive Debug Views

- Instance/Declaration/Signal List

- Stack/Local

- Class/Object/Member

- Source

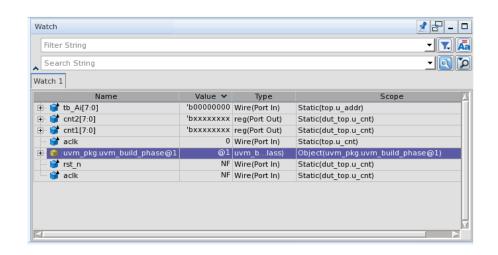

- Watch

- Dump

- Waveform

- Console

## Verdi Interactive Debug Views

#### Verdi Source and Watch

```

*Src1:top(/slowfs/vgverdirnd1/sbchen/simXL/simXL_AXI_lite_UTF/common/hdl/top/top.sv) 🔮 🚀 🚚 🗖

31

wire [7:0] tb_cnt1;

32

wire [7:0] tb_cnt2;

tb addr u addr(.tb Ai(tb cnt1[7:0]), Bi(tb cnt2[7:0]));

tb_cnt u_cnt(.rst_n(tb_aresetn),.aclk(tb_aclk),.cnt1(tb_cnt1[7:0]),.cnt2(tb_cnt2[7:0]))

36

uwm confiq db #(virtual axi lite interface)::set(null, "uwm test top", "axi vif",

dut top.u axi if);

run_test ();

41

$hw_read(dut_top.u_cnt.cnt2);

$hw_read(dut_top.u_cnt.cnt1);

$hw_read(dut_top.u_addr.Co);

$hw_force(dut_top.u_addr.Co);

$hw_force(dut_top.u_cnt.cnt1);

$hw_force(dut_top.u_cnt.cnt2);

tb_aresetn = ~dut_top.aresetn;

$fsdbDumpvars("+fsdbfile+test.fsdb");

initial begin

tb aclk = 1'b0

forever begin

#1000

```

- View HW and SW source code

- Set breakpoint

- Add signal to watch

- Add signal to dump file

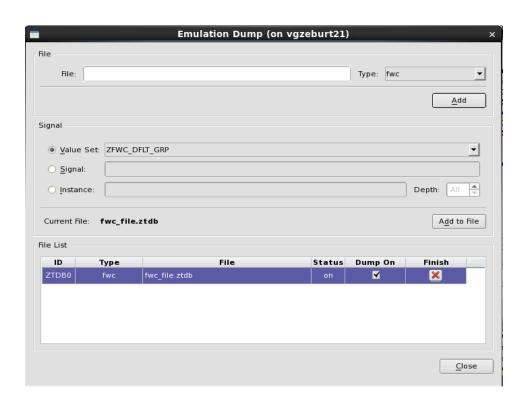

# **Dump Emulation File**

No inter.fsdb dump by default, use emulation dump dialog to dump ztdb file.

- Add emulation Dump file with type

- Add hardware value set into file

- Add software signal/instance into file

- Dump on/off

- Dump close

# Open ZTDB file in Waveform

Unify dumping. HW and SW signals are in one ztdb file

# Open ZTDB file in Waveform (cont'd)

#### Console View

Display simulation acceleration output in console window

```

Console

Rule Time View Tools Window

x1fs 🔳 🕨 🖶 🔁 📵 🔘 100 🔞 Line: 168

▼ 🔯 🌠 🤻 🔻 0

Rule: /M i rule.rc

168 # "libHWAccess 64b"

169 # start time is Thu Sep 27 18:21:50 2018

# Build Date : Sep 27 2018 - 00:39:36

-----System Context-----

12 x bogomips - 5333.21 Intel(R) Xeon(R) CPU

X5650 @ 2.67GHz

173 #

Load: 0.74 3.07 3.20 2/486 1981

174 #

Hostname: vgzeburt21 OS: Linux 2.6.32-696.20.1.el6.x86 64

Total: 24015 MB Free: 18188 MB

176 #

Swap space: 48290 MB Free Swap space: 48274 MB

VmSize: 64 MB VmPeak: 64 MB

178 # Disk Space Total: 1870 GB Available: 201 GB Used: 1669 GB

179 #

Free inodes: 5450945

180 # Stack

Soft Limit

Hard Limit

181 #

Max stack size

unlimited

bytes

-- ZeBu : zServer : The "ZEBU SYSTEM DIR" is set to "/remote/vqinterfaces1/us01zebu config/CONFIG.TD.ZEBU/vqzeburt21".

184 -- ZeBu : zServer : WARNING : Host 'vgzeburt21' is not registered in the file host topology.xml.

185 -- ZeBu: zServer: According to </remote/vginterfaces1/us01zebu config/CONFIG.TD.ZEBU/vgzeburt21/config.dff> file, the 1

186 -- ZeBu : zServer : Looking for a default "designFeatures" file to get the design's features.

187 -- ZeBu : zServer : Looking for a connection (pid 1979 at Thu 27 9 2018 - 18:21:51) ...

188 -- ZeBu : zServer : The PCIe connection through board 0 is free.

189 -- ZeBu: zServer: Get the connection to board 0 at Thu 27 9 2018 - 18:21:51.

190 -- ZeBu : sh : Waiting for the server pid 1979 to register the design.

191 -- ZeBu : zServer : Connection established (host : "vgzeburt21").

192 -- ZeBu : zServer : pid 1992 finished with exit code 0.

193 -- ZeBu : zServer : Initialization (open) of the "ZeBu Server".

194 -- ZeBu : zServer : FPGAs loading will use parallel CPU (5).

195 -- ZeBu : zServer : This 1 unit design will use Unit 0 Module 0.

Verdi>

```

# Debugging/Profiling

- Simulation acceleration uses many Zebu debug methodologies

- zRun can be used to run and dump waveforms and control Zebu normally

- zRun –testbench "./simv <Run\_Time\_Switches>" ...

- Functional Debug using UCLI preferred to zRun

- UCLI for VCS is enhanced to create simulator like interface for Verification Engineers

- The UCLI will provide following functionality

- Dumping waveforms using dynamic\_probe/FWC/QIWC

- Able to force/deposit/watch/get signal in HW.

- Able to set breakpoint on signal change values in HW.

- Dumping/Reading from Zebu Memory.

- Performance Debug

- VCS Profiler to optimize time spend in testbench.

- ./simv -simprofile <other switches>

- profrpt -view time\_all -format all simprofile\_dir/ -dut hw\_top

- profileReport/TimeSummary.txt

- User readable profile file is generated( shows DUT% & other TB components)

- Simulation acceleration profiler

- For SIGNAL acceleration It will be primarily used to find communication overhead.

- It can help identify active channels which can benefit from AVIPs.

# Compiling for Debug (UTF file)

- Enabling UCLI signal control from UTF file

- zforce -rtlname <Zebu\_mapped\_signal>

- This will enable force/release from command line

- zinject -rtlname < Zebu\_mapped\_signal>

- This UTF command will make transformations to enable deposit signal values.

- probe\_signals -type dynamic -rtlname < Zebu\_mapped\_signal>

- This UTF command will allow Reading/Watching signal values in UTF commands.

- Value Sets for QIWC/FWC are defined similar to Zebu Flow

- (\*fwc\*) \$dumpvars(0, hw\_top.DUMP.GRP2);

- (\*qiwc\*) \$dumpvars(0, hw\_top.DUMP.GRP6);

- zSelectProbes

- zSelectProbes is used to select signals for dynamic probing(ReadBack)

- No change from regular Zebu flow

#### **UCLI** Commands

- Simulation acceleration supports TestBench/DUT waveform dumping at same time.(New capability)

- HW Waveforms are captured in ZTDB and Testbench in fsdb file concurrently.

- Verdi provide ways to view the waveforms together with a aligned timestamp.

- dump -file <FILE> -type fwc|dynamic probe -driverClk

- It will create a waveform database directory named <FILE> and also create a test bench side waveform simxl.fsdb inside <FILE>.

- Without –driverClk option, It uses tickClk for sampling.

- dump -add <list\_of\_nids> -fid <FID>

- Add signals into test bench side simxl.fsdb when the given FID is ZTDB FID

- dump -add value set <value set> -fid <FID>

- Add <value\_set> to a given <FID>. Multiple value set can be added

- dump -enable/-disable -fid <FID>

- Enable/Disable dumping

- dump -close <FID>

- Close the Dump file

- dump -flush <FID>

- Flush data to dump file

- dump -load selection

- Loads the zSelectProbes before enabling dump for readback.

# UCLI Commands (cont'd)

- Command: run

- Supports running for relative or absolute time.

- run 20ns

- run –absolute 5us

- Supports running till a HW/SW trigger.

- run –change tb\_signal

- No special compile time directive required

- run –change dut\_signal

- Must be enabled using probe\_signals command.

- Command: show

- show -value tb\_signal

- No special compile time directive required

- show -value hw\_signal

- Must be enabled using probe\_signals command at compile time in UTF file.

# UCLI Commands (cont'd)

- force <sw\_signal> <value>

- No special directive required for forcing SW signal.

- force <hw\_signal> <value>

- HW force must be enabled by "zforce" UTF command.

- release <sw\_signal>

- No special directive required for releasing SW signal.

- release <hw\_signal>

- HW force/release must be enabled by "zforce" UTF command

- force –deposit <sw signal> <value>

- No special directive required for depositing SW signal.

- force –deposit <hw\_signal> <value>

- HW deposit must be enabled by "zinject" UTF command.

# UCLI Commands (cont'd)

- get u\_duv.ctrl -radix b

- Get Signal with –radix b(binary)/d(decimal) or h(hex)

- memory -read|-write -file <fname> [-radix <radix>] [-start start\_address] [-end end\_address]

- Load/write memory values from/to files, or initialize memory with given value

- restart

- Restart tool execution; UCLI will return to time zero

- senv value\_sets

- returns all value sets existing in design compilation.

- senv driver\_clk\_frequency

- returns driver clock frequency in kHz

### Profiler and Translog Dump

- VCS communication profiler

- ./simv -simxl=profile <Other options>

- Enables communication profiling and dumps simxlProfile.txt at the end of test.

- It reports Elapsed Time/Driver Clock Cycles/Active Signals/Memory Read-Write Calls/TimeStamp Synchronization/DPI-Verilog task calls.

- The purpose if to reduce synchronizations between TB-DUT by moving towards a TBA(Transaction Based Acceleration) and identify active interactions.

- Communication overhead in transferring signal/memory values etc.

- Enabling dumping of detailed continuous I/O communication between HW/SW.

- ./simv -simxl=translog, translog\_file:hwlog.txt

TF Id Import Function Call Starts Function path and name **Function** [F] [ImportStart] [id=77] gpu\_test\_pkg::\gpu\_test::write\_memory\_merge ... {address logic Input [63:0] 'h2b89202000000000} ... Type Argument name Direction Value

# Increasing Acceleration Performance

- Usage of HW clock signals in SW can be optimized under the hood to reduce communication overhead.

- When waiting for a fixed number of cycles from many different places.

- For example, usage of 50 difference places in testbench of (repeat (N) @(posedge top.chip.clk))

- Even though communication is at signal level implementation is optimized to communicate when exceeding the repeat count.

- Signals that change infrequently, should be kept at signal communication over communicating them through a code implementation.

- Signals between HW and SW are only communicated when they change their values. Therefore it is worth keeping the communication at signal level and let the tool handle when appropriate to communicate

#### **AXI EXAMPLE**

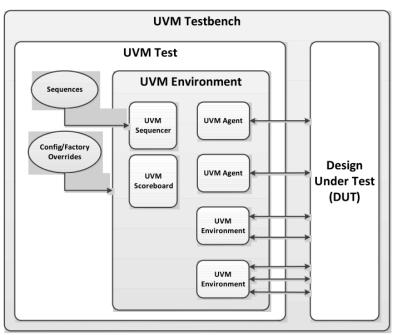

# A Typical UVM Environment

- Signal based connection (through virtual interfaces) in UVM

- Driving and sampling functionalities are usually implemented in bus functional model (BFM) tasks inside drivers or monitors

// The virtual interface used to drive and view HDL signals.

virtual xbus\_if xmi;

// get\_and\_drive

virtual protected task get\_and\_drive();

@(negedge xmi.sig\_reset);

forever begin

@(posedge xmi.sig\_clock);

seq\_item\_port.get\_next\_item(req);

...

xmi.sig\_addr <= trans.addr;

...

xmi.sig\_size <= 2'bz;

...

end

endtask : get\_and\_drive</pre>

class xbus master driver extends uvm driver #(xbus transfer);

Figure 1—Typical UVM Testbench Architecture

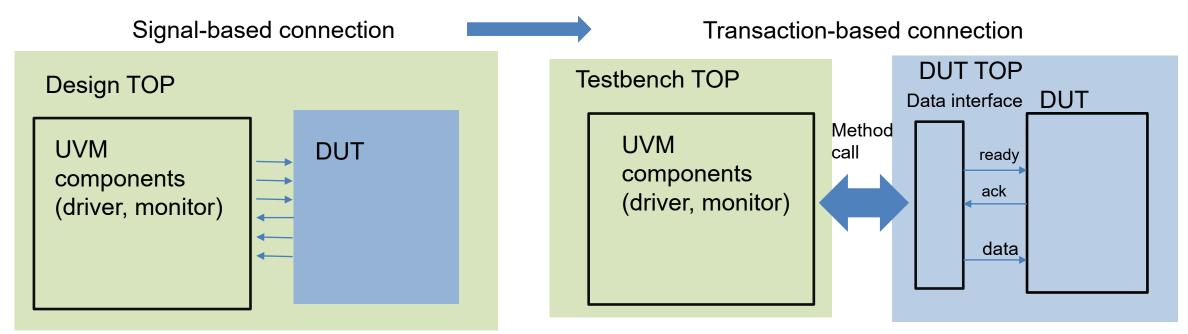

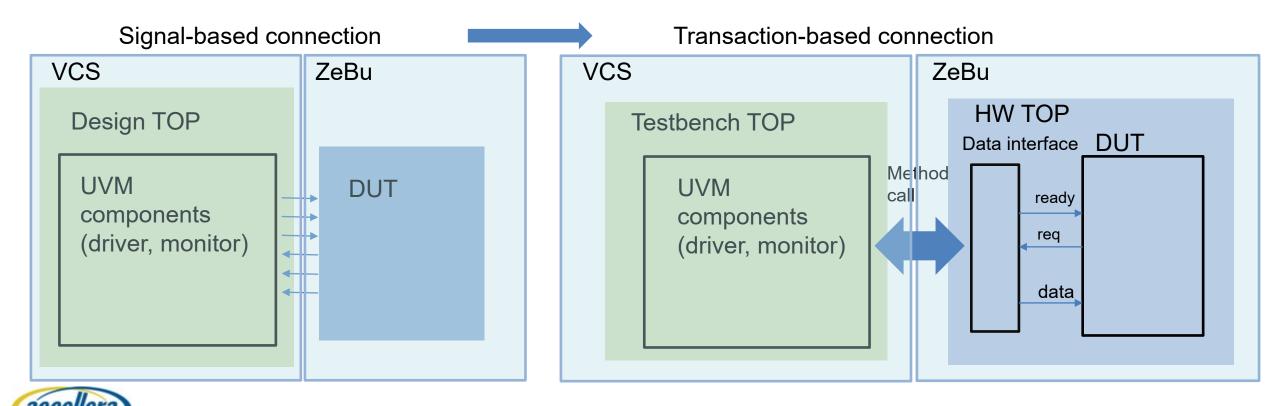

# Moving BFM to Interfaces/Modules

- Isolating transaction generation/post-processing (scoreboards, etc) from transaction driving/sampling

- BFMs can be behavioral level code (for simulation) or RTL code (for synthesis)

- Transactions are passed between testbench and interfaces using the method calls

SYSTEMS INITIATIVE

# Signal-based vs. Transaction-based

- Simulation acceleration supports both usages

- Transaction based connection provides better performance

- Less communication events between simulator and emulator

# Method Call: Export/Import

- Export call

- testbench calls interface through virtual interface

- vif.write(transaction)

- Import call

- interface calls testbench (UVM component) methods through object handle

- master\_handle.get(transaction)

### Data Class: Transaction or Configuration

For objects to be passed between VCS and ZeBu we need to convert them to a struct type.

```

typedef struct {

logic[3:0] in1;

logic[3:0] in2;

logic[4:0] out1;

data s;

class data c;

rand logic[3:0] in1;

rand logic[3:0] in2;

rand logic[4:0] out1;

function void copy to item(input data s data t);

this.in1 = data t.in1;

this.in2 = data t.in2;

this.out1 = data t.out1;

endfunction

function void copy to struct (output data s data t);

data t.in1 = this.in1;

data t.in2 = this.in2;

data t.out1 = this.out1;

endfunction

function void print();

$display($stime,,"in1: %x in2: %x",this.in1,this.in2);

endfunction

endclass

```

- The driver/monitor is running inside

VCS but the object handle will be passed to data interface so data interface can call the driver/monitor method

- import call

# accellera Systems Initiative

#### **Driver/Monitor Class**

```

class mst c;

data c data;

virtual data itf vif;

function void connect();

vif.xtor register(this); //register this xtor to

data interface

endfunction

//data interface will call this task to get a

transaction

task get (output data s data t);

seq item port.get next item(req t);

req t.copy to struct(data t);

endtask

task put (input data s rsp);

data c rsp t;

rsp t.copy to item( rsp);....

seq item port.item done(rsp t);

endtask

endclass

```

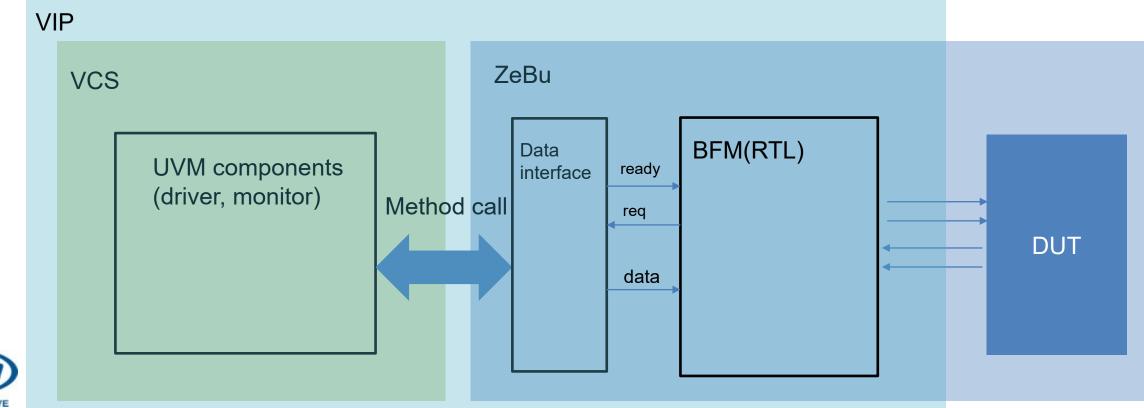

#### Data Interface

- The data interface gets/puts transactions from/to UVM driver/monitor

- As in the typical UVM environment, the driver still pulls transactions from UVM sequence and the monitor still puts the transactions to analysis components

- The interface has other methods for the communication with testbench, for example to register a driver/monitor to this interface instance

- xtor\_register

```

interface data itf(

input logic clk,

input logic reset,

output logic data ready,

output data s data,

input logic data req

mst c mst; //xtor handle

function void xtor register (input mst c

mst t);

mst = mst t;

endfunction

always @(posedge clk) begin

if (reset) begin

data ready <= 1'b0;

next state <= ST GET DATA;</pre>

end

else begin

case (current state)

ST GET DATA:

begin

mst.get(data);

data ready <= 1'b1;</pre>

if (data req) begin

endinterface

```

#### **BFM Module**

- BFM module is a synthesizable module to drive the transaction to DUT or collect the transaction from DUT

- BFM is optional since users can also implement driving/ monitoring methods inside data interface

- Data interface puts/gets the data to/from BFM module

- Same data interface instance will be connected to driver/monitor virtual interface

#### **BFM Module**

```

module mst bfm(

input logic data ready,

output logic data req,

input data s data,

//DUT

itf itf p

always @(posedge itf_p.clk) begin

if (itf p.reset) begin

next state <= ST DRIVE;</pre>

data req <= 1'b0;...

end

else begin

case (current state)

ST DRIVE:

begin

if (data ready) begin //data ready, drive data to DUT

itf p.valid <= 1'b1;</pre>

itf p.in1 <= data.in1;</pre>

itf p.in2 <= data.in2;</pre>

if (itf p.ack) begin //dut ack, get next data

next state <= ST DRIVE;</pre>

```

- UVM driver/monitor BFM tasks are usually implemented with "behavioral code"

- Behavioral Compilation

- Hardware synthesis of behavioral code

```

class xbus master driver extends uvm driver #(xbus transfer);

// The virtual interface used to drive and view HDL signals.

virtual xbus if xmi;

// get and drive

virtual protected task get and drive();

@(negedge xmi.sig reset);

forever begin

@(posedge xmi.sig clock);

seg item port.get next item(reg);

xmi.sig addr <= trans.addr;

xmi.sig size <= 2'bz;

end

endtask: get and drive

```

Initial block and # delay

Bounded and Unbounded loops

```

while (1) begin

@(posedge clk1)

c <= c + 1;

end

for (i=0;i<128;i=i+1) begin

@(posedge clk);

mem[i] = 0;

end</pre>

```

```

bit aclk:

bit aresetn;

initial begin

aresetn = 1'b0;

#5000:

aresetn = 1'b1;

end

initial begin

aclk <= 1'b0:

forever begin

aclk <= 1'b1;

#1000:

aclk <= 1'b0:

#1000:

end

```

- Multiple clocks or edge expressions in the same process

- Wait statement

- Named events

```

always @(posedge clk) begin

a = 0:

@(negedge reset);

a = 1:

@(negedge clk);

a = 2;

end

initial begin

wait(reset==1'b0);

event my event;

initial -> my event;

always begin

@(my_event);

a <= b;

end

```

Clocking blocks

- Fork/Join

- fork/join

- fork/join\_none

- fork/join\_any

```

clocking cb @(posedge aclk);

input aresetn ;

input awaddr ;

endclocking

initial begin

@(cb);

A <= cb.awaddr;

end</pre>

```

```

fork

do_A();

do_B();

join

```

#### AXI 3/4 VIP Environment

- Transaction based connection in a UVM based environment

- UVM testbench (running with VCS)

- Interface and BFM (running with ZeBu)

- UVM drivers/monitors communicate with ZeBu through method call

SYSTEMS INITIATIVE

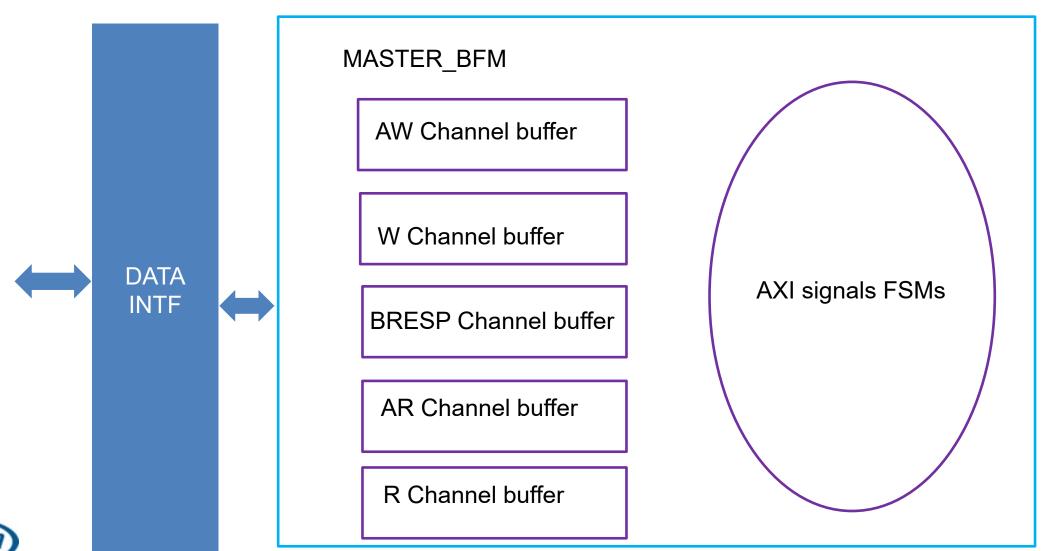

#### **AXI** Master/Monitor

SYSTEMS INITIATIVE

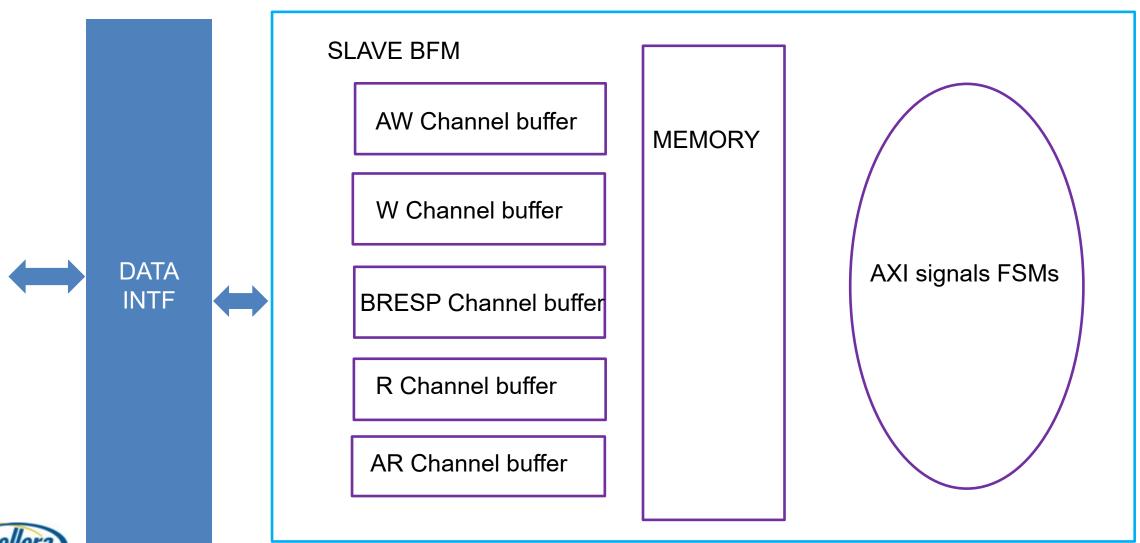

#### **AXI Slave**

#### Data Interfaces

- Get AXI transactions from AXI UVM master component

- Put AXI transactions to AXI UVM slave or monitor components

- When needed, testbench code can also pass the configuration data to data interface through the xtor\_register call

```

//slave data interface

function void xtor register(input axi slave drv slv t, input axi common pkg::slave cfg

slave cfg data );

slv = slv t;

slave cfg data = slave cfg data;

endfunction

always @(posedge clk) begin

if(reset!=0) begin

if (write mem tran in done) slv.put(write mem tran in,0);

end

//master data interface

always @(posedge clk) begin

else begin

if(data req==1'b1) begin

mst.get(data is valid, data new);

```

#### Parameterized Buffer Size

BFM module has a parameter to specify how many outstanding transactions can be processed in parallel

```

module slave bfm #(

parameter bit[3:0] depth=1 //how many transactions can be

processed in same time

endmodulue

module hw top;

slave bfm #(buffer size,...)

slave_bfm_inst(.slave cfg port(slave cfg data),.*);

endmodule

```

# Single and Burst Read/Write Sequence Tasks

```

virtual task read(input bit [`AXI MAX AW-1:0] addr,

output logic [`AXI MAX DW-1:0] data,

output logic [1:0]

rresp,

input

uvm sequencer base seqr,

input bit[(`AXI_ID_WIDTH - 1):1] arid=0,

input int

tr size in bytes =

`AXI MAX DW/8,

input bit[1:0]

burst type = 2'b01,

input

uvm sequence base parent =

null);

virtual task read burst(input bit [`AXI MAX AW-1:0] addr,

output logic [`AXI MAX DW-1:0] data [],

input int

burst length,

output logic [1:0]

rresp [],

input

uvm sequencer base seqr,

input bit[(`AXI ID WIDTH - 1):1] arid=0,

input int

tr size in bytes =

`AXI MAX DW/8,

input bit[1:0]

burst type = 2'b01,

input

uvm sequence base parent

= null);

```

# Single and Burst Read/Write Sequence Tasks

```

virtual task write(input bit [`AXI MAX AW-1:0] addr,

input logic [`AXI MAX DW-1:0] data,

output logic [1:0]

bresp,

input

uvm sequencer base seqr,

input bit[(`AXI ID WIDTH - 1):1] awid=0,

input axi delay vars_struct delay_vars=axi_delay_vars_struct'{default:0},

input int

tr size in bytes = \Delta XI MAX DW/8,

input bit[1:0]

burst type = 2'b01,

input

uvm sequence base parent = null);

virtual task write burst(input bit [`AXI MAX AW-1:0] addr,

input logic [`AXI MAX DW-1:0] data [],

input int

burst length,

output logic [1:0]

bresp,

uvm sequencer base seqr,

input

input bit[(`AXI ID WIDTH - 1):1] awid=0,

input axi delay vars struct delay vars=axi delay vars struct'{default:0},

tr size in bytes = ^{\text{AXI}} MAX DW/8,

input int

burst type = 2'b01,

input bit[1:0]

uvm sequence base parent = null);

input

```

# Write and Read Test Example

```

wr seq = axi master write seq::type id::create("wr seq");

rd seq = axi master read seq::type id::create("rd seq");

//SIMPLE WRITE READ, one byte each transfer

for (int i = 0; i < 16; i++) begin

wr seq.write(32'h00000100+(i*bytelane num), i+1, resp, env.u axi master agt.sqr,1,,1);

end

repeat(30) @(posedge master vif.clk);

for (int i = 0; i < 16; i++) begin

rd seq.read(32'h00000100+(i*bytelane num), rd data single, resp, env.u axi master agt.sqr,1,1);

end

repeat(30) @(posedge master vif.clk);

//BURST WRITE and READ

begin

burst length=5;

wr data = new[burst length];

foreach(wr data[ii]) begin

wr data[ii]=ii+5;

end

wr seq.write burst(32'h1000, wr data, 5,bresp, env.u axi master agt.sqr,1,,2);

repeat(10) @(posedge master vif.clk);

rd seq.read burst(32'h1000, rd data,5, rresp, env.u axi master agt.sqr,1,2);

repeat(10) @(posedge master vif.clk); //unaligned address

wr seq.write burst(32'h1001, wr data, 5,bresp, env.u axi master agt.sqr,1,,2);

repeat(30) @(posedge master vif.clk);

rd seq.read burst(32'h1001, rd data,5, rresp, env.u axi master agt.sqr,1,2);

end

```

# Memory Access Debug Message

AXI slave BFM module puts the received write transaction (both AW channel info and WDATA channel info), received read transaction(AR channel info) and transaction after reading memory (byte enable for each transfer, data read from memory) to AXI slave UVM driver/monitor for the debug purpose.

```

//slave_data_if

always @(posedge clk) begin

if(reset!=0) begin

if (write_mem_tran_in_done) slv.put_transaction(write_mem_tran_in,0);

if (read_mem_tran_in_done) slv.put_transaction(read_mem_tran_in,1);

if (read_mem_tran_out_done) slv.put_transaction(read_mem_tran_out,2);

end

end

//class axi_slave_drv

function void put_transaction(input_axi_seq_item_struct_tran_struct, input_bit[1:0] which_tran);

read_mem_tran_out=axi_seq_item::type_id::create("read_mem_tran_out");

read_mem_tran_out.copy_to_item(tran_struct);

`uvm_info(get_full_name(), $sformatf("%p", read_mem_tran_out), UVM_DEBUG)

endfunction

```

```

UVM_INFO /slowfs/vgzebucae10/whan/MYAXI/0507/myaxi_0628/src/dv/axi_slave/axi_slave_drv.sv(47) @

50315000: uvm_test_top.env.u_axi_slave_agt.drv [uvm_test_top.env.u_axi_slave_agt.drv] ...

m_leaf_name:"read_mem_tran_out"

addr:'he0000150, data:'{'h7, 'hc, 'h11, 'h16, 'h1b} , burst_length:5, burst_type:1,

byte_en:'{'hf, 'hf, 'hf, 'hf, 'hf} , tr_size_in_bytes:4,

```

#### ZeBu Model Instantiation

Hardware top module

```

module hw top();

master data itf

master data itf inst(aclk, aresetn, data ready, data, data req, ...);

master bfm#(buffer size) master bfm inst(data_ready, data, data_req,

wr data valid,..., .*);

slave dut slave(.*);  //AXI signal connections

initial begin

aclk = 1'b0;

forever #5 aclk = \simaclk;

end

initial begin

aresetn = 1'b0;

repeat(10) @(posedge aclk);

aresetn <= 1'b1; //reset deassertion should be synchronous on the

rising edge of aclk

end

endmodule

```

# **AXI Example Capabilities**

- Different burst types, transfer size, burst lengths

- Separate address/control, data and response phases. Separate read and write channels.

- Support for burst-based transactions with only start address issued.

- Write strobe support to enable sparse data transfer on the write data bus

- Narrow transfer support

- Unaligned address access support.

- Ability to issue multiple outstanding transactions.

- Out of order transaction completion support.

- Support for Write data phase before Write address phase (negative AWVALID to WVALID delay)

- Write data and read data interleaving support.

- Configurable write and read interleave depth.

- Slave and Master support fine grain control of response per address or per transaction (OKEY or SLVERR)

# AXI Example Profile

|                    | Time Spent | %time     |

|--------------------|------------|-----------|

| SimXL Elapsed Time | 455.387 s  | 100.0     |

| Test Bench Time    | 438.024 s  | 96.2      |

| Communication Time | 17.363 s   | 3.8       |

| Synchronization    | 0.000 ms   | 0.0/0.0   |

| PIO data packing   | 17.363 s   | 100.0/3.8 |

|                                         | +===================================== | +=====+<br>  %time |

|-----------------------------------------|----------------------------------------|--------------------|

| SimXL Elapsed Time                      | 265.108 s                              | 100.0              |

| Test Bench Time                         | 264.930 s                              | 99.9               |

| Communication Time                      | 177.462 ms                             | 0.1                |

| Synchronization                         | 0.000 ms                               | 0.0/0.0            |

| TF data packing                         | 177.462 ms                             | 100.0/0.1          |

| +====================================== | +========                              | +=====+            |

#### Data Transfer Summary:

| Type         | Total calls | Total data | Average calls | Average data |  |

|--------------|-------------|------------|---------------|--------------|--|

|              |             |            |               |              |  |

| Input        | 14599876    | 3.481 Gb   | 1.106         | 283.152 b    |  |

| Output       | 14341377    | 3.419 Gb   | 1.086         | 278.139 b    |  |

| Force        | 0           | 0 b        | 0.000         | 0.000 b      |  |

| SW->HW call  | 0           | 0 b        | 0.000         | 0.000 b      |  |

| HW->SW call  | 0           | 0 b        | 0.000         | 0.000 b      |  |

| Memory Read  | 0           | 0 b        | 0.000         | 0.000 b      |  |

| Memory Write | 0           | 0 b        | 0.000         | 0.000 b      |  |

Data Transfer Summary:

| Type         | Total calls |       | Total data  | Average calls | Average data |

|--------------|-------------|-------|-------------|---------------|--------------|

| -            |             | -   - |             | -             | -            |

| Input        | 0           |       | 0 b         | 0.000         | 0.000 b      |

| Output       | 0           |       | 0 b         | 0.000         | 0.000 b      |

| Force        | 0           |       | 0 b         | 0.000         | 0.000 b      |

| SW->HW call  | 3           |       | 290 b       | 0.000         | 0.000 b      |

| HW->SW call  | 600090      |       | 1001.699 Mb | 0.045         | 79.573 b     |

| Memory Read  | 0           |       | 0 b         | 0.000         | 0.000 b      |

| Memory Write | 0           |       | 0 b         | 0.000         | 0.000 b      |

SBA

TBA

# **AXI Example Profile**

Other profile information

```

Instance Name: dut_top.master_data_itf_inst

| Total Calls|Direction| Input Size | Output Size | Task ID | Task/Func name

200000 | HW->SW | 96 b | 1.616 Kb | 1 | axi_master_pkg::^Gxi_master_drv::get_req *

99998 | HW->SW | 1.709 Kb | 0 b | 5 | axi_master_pkg::^Gxi_master_drv::put_tran * 99998 | HW->SW | 1.709 Kb | 0 b | 6 | axi_master_pkg::^Gxi_master_drv::put_tran *

97 | HW->SW | 96 b | 1.616 Kb | 0 | axi_master_pkg::^Gxi_master_drv::get_req *

1 | HW->SW | 96 b | 1.616 Kb |

3 | axi master pkg::^Gxi master drv::get reg *

1 | SW->HW | 64 b | 32 b |

7 | this.vif.xtor_register

0 | HW->SW | 96 b | 1.616 Kb |

2 | axi_master_pkg::^Gxi_master_drv::get_reg *

0 | HW->SW | 96 b | 1.616 Kb |

4 | axi_master_pkg::^Gxi_master_drv::get_reg *

Details of signal changes:

Total Changes | Width | ID | Signal name

|-----

Inputs:

1 b | 1 | dut_top.bfm_top_inst.aclk

200001 |1.614 Kb | 3 | dut_top.bfm_top_inst.data_in_bits

3 | 1 b | 4 | dut_top.bfm_top_inst.data_ready

2 | 1 b | 2 | dut_top.bfm_top_inst.aresetn

2 b | 16 | dut_top.bfm_top_inst.slave_cfq_data_bits

```

# Summary

- Simulation acceleration provides flow for VCS users to take advantage of ZeBu for accelerating their UVM regressions

- VCS supports signal-based and transaction-based acceleration

- By moving UVM driver/monitor BFM tasks to interfaces/modules we can setup a UVM-based emulation friendly environment