#### SimpleLink™ MCU Platform: IP-XACT to UVM Register Model -Standardizing IP and SoC Register Verification

#### "UVM is a perfect start"

Jasminka Pasagic(j-pasagic@ti.com)Frank Donner(f-donner@ti.com)

## Contents

- Abbreviations and Common Terms

- Platform Project and Challenges

- Why changing from manual to automation?

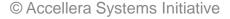

- Flow

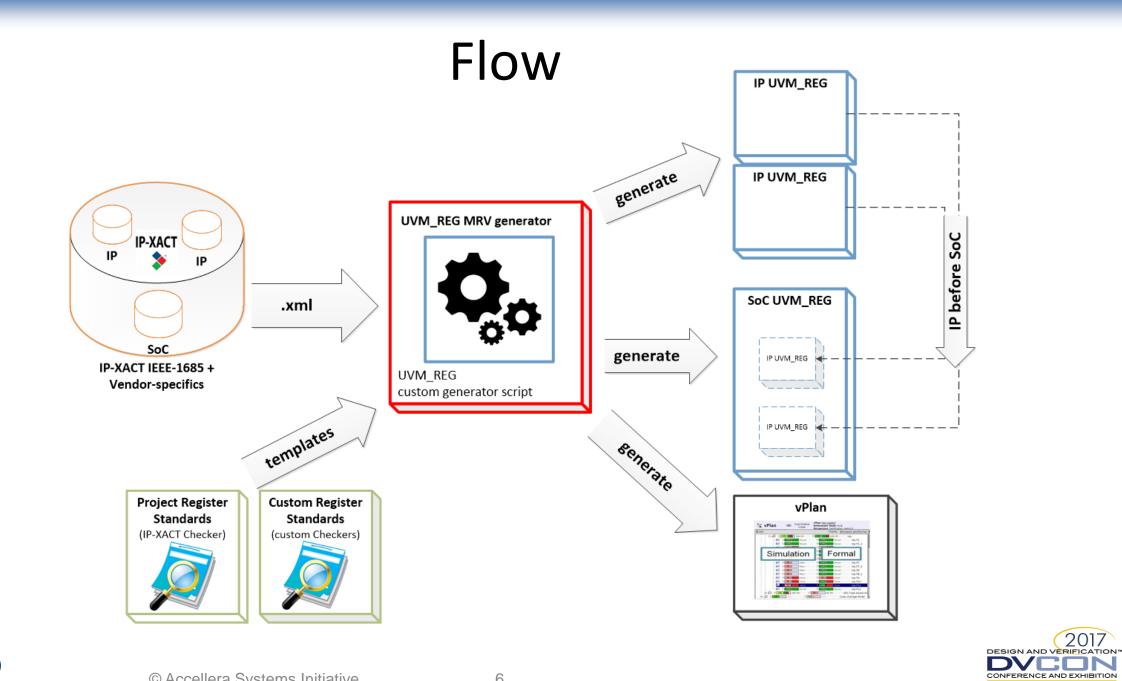

- Register Requirements

- UVM Register Model Updates

- Effort Savings UVM\_REG Time Reduction Comparison

- Conclusions

- Further Work

#### Abbreviations and Common Terms

| SoC        | System on Chip                                                 |

|------------|----------------------------------------------------------------|

| IP         | Intellectual Property                                          |

| MRV        | Memory Register Verification                                   |

| UVM        | Universal Verification Methodology                             |

|            |                                                                |

| GIT        | means <i>unpleasant person</i> in <u>British English</u> slang |

| DesignSync | Data Management tool                                           |

DESIGN AND VE

#### **Platform Project and Challenges**

Multi-site project High amount of reuse and standardization High amount of automation Planning and execution to be shared Automotive

#### Why changing from manual to automation?

Ensure specification and verification data consistency and accuracy

Reduce time spent in developing register verification

Use industry standards: IP-XACT register description UVM register generators UVM RAL

(indirect registers, lock, shadow, alias, alternate register, interrupts, counters, FIFOs, wider registers, atomic registers, register arrays, etc.)

accelle

SYSTEMS INITIATIVE

EUROPE

DESIGN AND VERIFICATIO

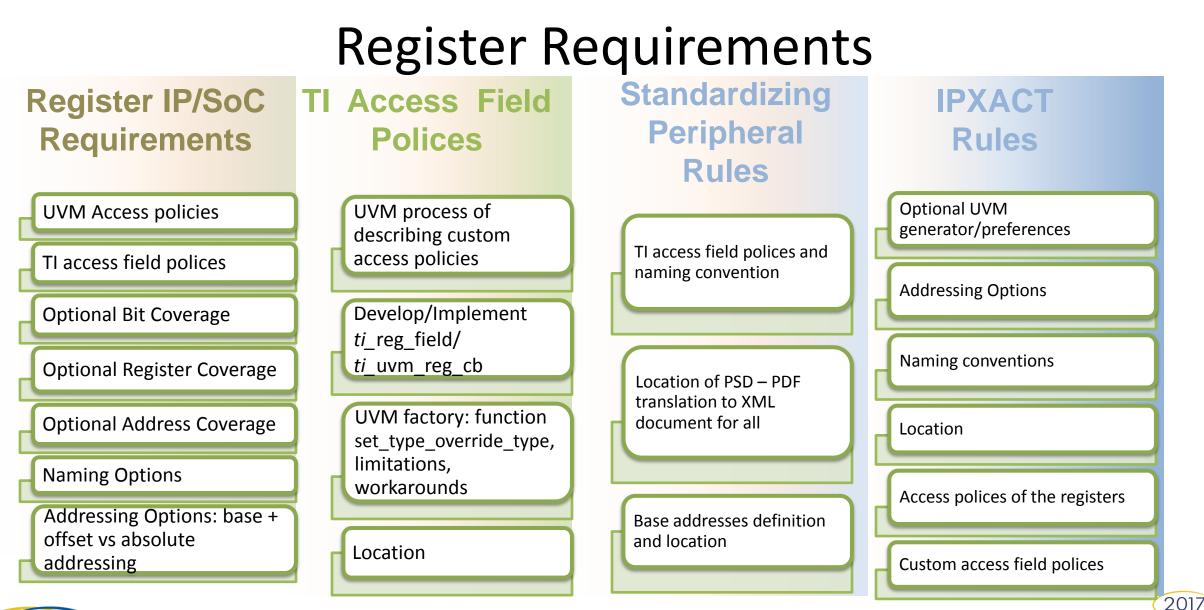

#### **UVM Register Model Updates**

SYSTEMS INITIATIVE

## **Effort Savings**

| <b>Manual</b><br>Always   | <b>Generation</b><br>Effort 1 <sup>st</sup> time | <b>Generation</b><br>Effort 2 <sup>nd</sup> time | <b>Generation</b><br>3 <sup>rd</sup> time | Generation+Manual<br>2 <sup>nd</sup> time |

|---------------------------|--------------------------------------------------|--------------------------------------------------|-------------------------------------------|-------------------------------------------|

| UVM_REG manual<br>written | Input preparation                                | Input preparation                                |                                           |                                           |

| WORK                      | Generation scripts                               | Generation scripts                               | LUOR M                                    |                                           |

|                           | Output update                                    |                                                  |                                           |                                           |

2017 DESIGN AND VERIFICATION

CONFERENCE AND EXHIBITION

EUROPE

DVC

## Conclusions

#### Manually developed UVM register Model

- □ labor intensive task

- introduces range of potential problems and flaws

- difficult to maintain specification change cycles

- □ difficult to add central changes

- error prone

#### Automated/Semi-Automated UVM REGISTER Model

- ✓ ensures specification consistency

- ✓ standardizing inputs and outputs allows data reproducibility, reusability and allows cross industry convergence (eg. if you stay within IEEE 1685 standard but internal reuse of custom register is supported)

- ✓ faster cycle time to simulateable register framework

DESIGN AND VERI

$\checkmark$  incremental development

## Further Work

- □ SoC register model testing

- Update loops: tool versions

- Optimization of simulation time

- Checkers improvement for generator and TI register access polices

- Capture speed factor from manually to automated or semi-automated register model generation for our project

- UVM factory type override limitations and workarounds

- □ Auto generation of register verification plan

#### Thank you!!

#### Questions ??

#### BACKUP

## What is UVM\_REG? What is IP-XACT?

#### What is UVM\_REG?

UVM\_REG is an abstract SystemVerilog model for registers and memories from the DUT. It is built using the UVM methodology.

Ramp-up on UVM\_REG model by reading :

- Verification Academy's Registers : <u>https://verificationacademy.com/cookbook/registers</u>

- Advanced features of the UVM Register model: <u>http://www.verilab.com/files/litterick\_register\_final\_1.pdf</u>

#### What is IP-XACT?

IEEE 1685, "Standard for IP-XACT, Standard Structure for Packaging, Integrating and Re-Using IP Within Tool-Flows," describes an XML Schema for meta-data documenting Intellectual Property (IP) used in the development, implementation and verification of electronic systems and an Application Programming Interface (API) to provide tool access to the meta-data.

# What to consider for selecting generator?

- 1. Scalability designs may include large numbers of registers and scalability is an important consideration.

- 2. Support for a standard input format

- 3. Ability to replace the generator as needed

- 4. Debug-ability and self-checking of the generated code

# Examples of industry UVM register model generators?

- Cadence <u>iregGen</u> is a native IPXACT to UVM generator (supports registers as well as memories, wide range of registers such as immediate, fifo, shared and more, and automatically creates functional coverage)

- 2. Magillem UVM Generator

- 3. Synopsis genSys

- 4. AgniSys

## UVM Custom Field Access Policy Example

class zeroToSet\_cbs extends uvm\_reg\_cbs; `uvm\_object\_utils(zeroToSet\_cbs)

class zeroToSet\_reg\_field extends uvm\_reg\_field;

`uvm\_object\_utils(uvm\_reg\_field\_ext)

© Accellera Systems Initiative

local static bit m\_rwos = define\_access("RWOS");

//Cunstructor

function new(string name = "zeroToSet\_reg\_field");

super.new(name);

endfunction

endclass

class <IP/SoC>\_reg extends uvm\_reg;

`uvm\_object\_utils(zts)

rand uvm\_reg\_field field1; rand zeroToSet\_reg\_field field2;

//Cunstructor

function new(string name = "<IP/SoC>\_reg");

super.new(name);

endfunction

virtual function void build(); field1 = uvm\_reg\_field::type\_id::create("field1"); field2 = zeroToSet\_reg\_field::type\_id::create("field2");

field1.configure(this, 16, 16, "RW", 0, 0, 1, 1, 0); field2.configure(this, 16, 0, "RWOS", 0, 0, 1, 1, 0);

// register callback

zeroToSet\_cb field2\_cbs = new("rwos\_cbs");

uvm\_reg\_field\_cb::add(field2, rwos\_cbs);

endfunction

endclass