# Scalable Multi-Domain Multi-Variant Reset Management in Complex Verification IPs

Kaustubh Kumar, Verification Architect, SiliConch Systems, Bengaluru, India (k.kaustubh@siliconch.com)

Munnangi Sirisha, Verification Architect, SiliConch Systems, Bengaluru, India (sirisha.munnangi@siliconch.com)

Lokesh Kumar, Verification Lead, SiliConch Systems, Bengaluru, India (lokesh@siliconch.com)

*Abstract*— Reset Modeling in verification IPs is a crucial part of functional verification and its complexity increases with the architecture complexity. Reset testing might vary from resetting the complete environment (global reset) to resetting only a set of components (domain-specific reset) in the environment. With the growing complexity of protocols and design features, multiple variations of resets and other power-related features need to be tested and modeled in verification IPs as well. A standardized, scalable and protocol-independent approach is needed to handle all the possible complex scenarios to achieve a well synchronized reset across the testbench. This paper will present our technique of standardizing the reset management by deploying a centralized UVM-based Reset Handler which handles and manages all the possible reset conditions at both levels, global as well domain specific. This paper will also present the extensibility of the proposed technique to handling different kinds of reset using the proposed Reset Handler.

Keywords—reset management; domain-specific resets; reset variations; reset master-slave relationship; asynchronous reset handling

#### I. INTRODUCTION

A major requirement in Verification IPs (VIPs) is to handle dynamic resets, targeted to a certain set of VIP components or to the entire VIP. Modeling resets in the verification IPs is a crucial part of functional verification and its complexity increases with the architecture complexity. Reset testing might vary from resetting the complete environment (global reset) to resetting only a set of components (domain-specific reset) in the environment. With the growing complexity of protocols and design features, multiple variations of resets and other power-related features need to be tested and modeled in verification IPs as well.

This paper presents a scalable, protocol independent and a centralized way to handle reset assertion and execution throughout the VIP. This standardization is achieved by deploying a centralized UVM-based reset\_handler component which handles the reset assertion conditions and invokes the concerned VIP entities to execute the reset operation. Some of the reset-based scenarios common in VIPs, that are expected to be handled by reset handler, are mentioned below:

1) **VIP Initial Reset/Global VIP Reset:** Initial reset of VIP components is required to put the logical threads/variables/interfaces in their reset state. This initialization step may happen at simulation time 0 or any non-zero time instant as well to introduce reset delay randomization. Again, based on protocol/scenario requirements, entire VIP environment might be required to undergo reset operation dynamically/asynchronously.

2) **Domain-specific Reset:** Based on the protocol under verification, only a subset of all the VIP components might be required to undergo reset operation at any time instant. These subsets of VIP components constrained to undergo reset together, form a reset-domain.

3) **Modes/Variants of Reset:** VIP might be required to undergo different varieties of reset operations, for example, "COLD" and "WARM" resets. The VIP components undergoing the reset operation in this case may expect an input about the mode of reset in order to execute the operation differently, as per protocol requirements.

Apart from "reset" functionality alone, reset\_handler functionality can be extended to execute operations such as disable, clock gating, clock un-gating, etc.

The proposed technique declares reset\_handler as a centralized *singleton* class, which works on a principle of Master-Slave relationship. In this relationship, a VIP component responsible for asserting reset(s) to other component(s) is defined as the *Reset Master* (abbreviated as RM). The VIP component(s) which are invoked because of reset assertion by an RM is/are defined as *Reset Slave*(s) (abbreviated as RS). Based on the VIP architecture, some of the components can serve as both master and slave (RMS). Hence, the various groups of RMs and RSes/RMSes together form the multiple reset-domains. A reset operation execution in a reset-domain can be confined to that domain alone, without impacting other reset-domains and without changing the phase of any of the UVM components.

Existing technique of UVM phase jumping [3] to reset\_phase() is suitable for resetting all the components in the environment but cannot be used where only a set of components in a verification environment need to be reset. It is also difficult to handle different types of resets that can applied to the components using UVM phase jumping approach as it requires proper coordination between the components. Our approach solves these problems by creating multiple reset-domains and handling different modes of reset.

Another technique [4] involves plugging a virtual interface to monitor reset assertion and using a uvm\_thread instance as *reset\_handler* and calling *reset\_handler*.notify(ACTIVATE) to assert reset. The disadvantage of this technique is the inability to handle domains-specific reset using a single instance of uvm\_thread. Also, this technique is not scalable to different modes of reset.

## II. IDENTIFICATION OF RESET DOMAINS

The proposed reset\_handler can manage Global VIP Reset or Domain-specific Reset. This is achieved by using Reset Master and Slaves relationship with optional Reset Master/Slaves in between (RM-*RMS*-RS). Creating multiple-reset domains in a VIP environment employs following initial steps:

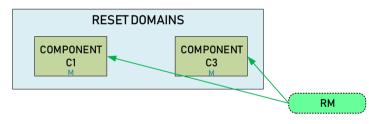

1) Identifying the RM components as VIP components which can assert reset based on any *simulation event*, such as a unique sequence item, trigger of a UVM event/callback, etc. At this step, it is possible that a Reset Master may qualify for reset assertion based on multiple simulation events as well as standalone. In Figure 1 below, components C1 and C3 are identified as Reset Masters.

Figure 1. Identifying Reset Master (RM) components

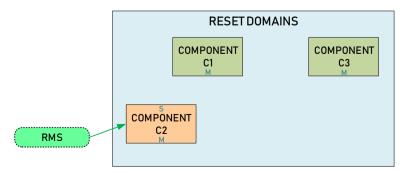

2) Identifying the VIP components which depend on another *reset event* triggered by a Reset Master (RM) to assert reset to a set of VIP components and labeling them as Reset Master/Slaves (RMS). RMS components may undergo reset operation apart from issuing resets to another set of components. In Figure 2 below, component C2 is identified as an RMS component.

Figure 2. Identifying Reset Master/Slave (RMS) components

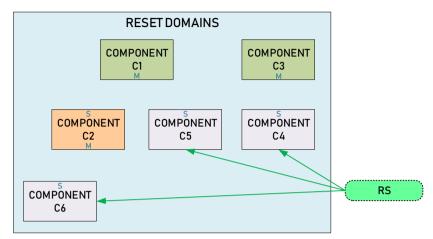

3) Identifying the VIP components which undergo reset operation based on *reset event* triggered by an RM/RMS and labeling them as Reset Slaves (RS). These components are the endpoints of a reset assertion hierarchy and issue no further resets to any other component. In Figure 3 below, components C4, C5 and C6 are identified as Reset Slaves.

Figure 3. Identifying Reset Slave (RS) components

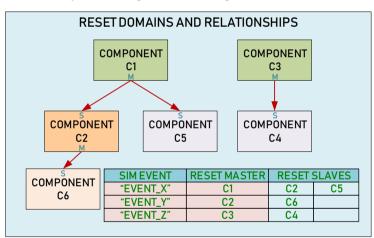

4) Link each of the RMs to the respective RMSes and RSes into separate reset-domains based on every *simulation event* which can cause the RM to assert reset operation. In case the RM asserts reset to the same set of RMSes/RSes for multiple *simulation events*, group all the *simulation events* into a single reset-domain. Figure 4 below shows the final reset hierarchy of the components in a sample VIP environment.

Figure 4. Linking Reset Master and Slaves based on simulation events

Hence, there can be multiple Reset Masters (RMs) in a VIP environment, each of them associated with one or many reset domains. This relationship can be visualized as a database of a Reset Master associated with its Reset Master/Slaves or Reset Slaves, the index to this database being the unique *simulation event* that causes the RM to assert reset.

# III. RESET INTERFACE

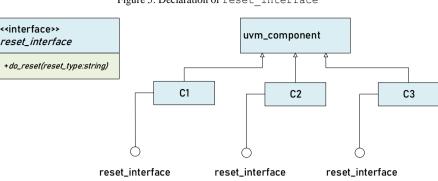

A System Verilog interface class reset\_interface is declared comprising of pure virtual System Verilog task do\_reset(). Any VIP component qualified as an RM/RMS/RS shall **implement** the reset\_interface and hence override the do\_reset() task to specify the details of handling of the reset operation based on the protocol implementation.

```

interface class reset_interface;

pure virtual task do_reset(string reset_type= "");

```

Figure 5. Declaration of reset interface

Figure 6. UVM hierarchy for RM/RMS/RS components

## IV. RESET HANDLER OPERATION

Major operations handled by reset\_handler is abbreviated as R-A-N-C (Registration-Assertion-Notification-Completion). Each of these operations are summarized in below points and described in detail in further sub-sections:

- 1) Registration of Reset Master and Slave components to the reset handler database

- 2) Servicing Assertion of reset request by a registered Reset Master

- 3) Notification of asserted reset request to the registered Reset Master/Slaves or Slaves.

- 4) Monitoring for the Completion of the notified reset requests

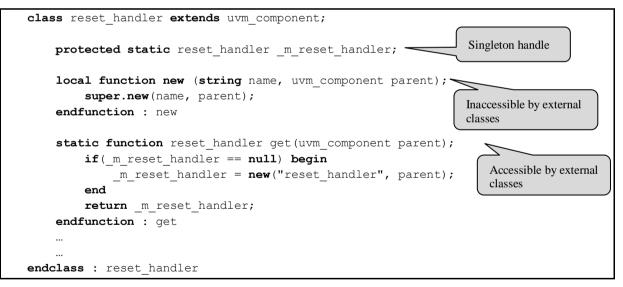

Below code in Figure 7 shows the reset\_handler class declaration. Note that since reset\_handler is a singleton class, there is no factory registration done, as factory overrides are not required.

Figure 7. Reset Handler singleton class definition

## A. Master and Slave Registration

The database of RMs, RMSs, RSs indexed by *simulation event* can be easily represented by associative array. The reset\_handler maintains the associative array, with following properties:

1) **Domain ID** (*string* type) as the index of the array; string representation of the *simulation event*.

2) Each element of the array is a System Verilog queue of type reset\_interface. Each element of the queue is a reset\_interface handle to the RM/RMS/RS associated with the Reset Domain. First element of the queue is the RM of the Reset Domain, followed by the RMSs and RSs associated with the domain.

Another database to maintain status of Reset Master registration is also maintained by reset handler.

| DOMAIN_ID | QUEUE OF RESET INTERFACE HANDLES |

|-----------|----------------------------------|

| "DID_0"   | { <mark>C1</mark> , C2, C5}      |

| "DID_1"   | { <mark>C2</mark> , C6}          |

| "DID_2"   | { <mark>C3</mark> , C4}          |

| DOMAIN_ID | MASTER REGN STATUS |

|-----------|--------------------|

| "DID_0"   | 1                  |

| "DID_1"   | 1                  |

| "DID_2"   | 1                  |

Figure 8. Reset Handler local databases

```

class reset_handler extends uvm_component;

protected static reset_handler _m_reset_handler;

typedef reset_interface t_reset_if_q[$];

// Database declarations

protected t_reset_if_q m_reset_db [string] ;

protected bit m_master_sts_db [string] ;

...

endclass : reset_handler

```

Figure 9. Reset Handler singleton class definition and databases

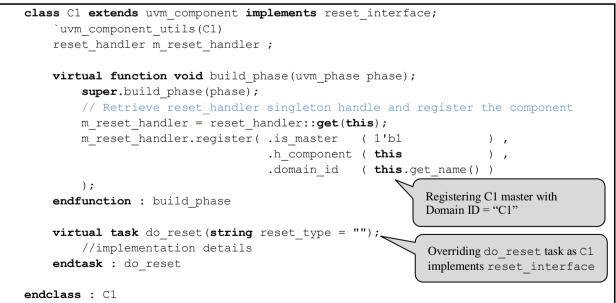

Each of the VIP components associated with the Reset Domains registers itself with the reset\_handler. This registration can be done in the UVM build\_phase() of the VIP components, where the singleton handle of the reset\_handler can be received and reset\_handler.register() function called. There are two modes of register() function call, each for an RM and an RS. For RMS components, two register() function calls are required, one as an RM, another as an RS. Following are the inputs arguments for register() function:

```

1) is_master (bit): Single-bit flag to specify whether the VIP component being registered is a Reset Master (is master = 1) or a Reset Slave (is master = 0).

```

2) h component (uvm component): Handle of the VIP component being registered.

3) domain\_id (string): String representation of the Domain ID of the VIP component being registered. Based on implementation, string representation of master name with optional suffixes can also be used as Domain ID.

Figure 10. Registering a Reset Master component with Reset Handler

```

class C2 extends uvm_component implements reset_interface;

`uvm_component_utils(C2)

reset_handler m_reset_handler;

```

```

virtual function void build phase (uvm phase phase);

super.build phase(phase);

// Retrieve reset handler singleton handle and register the component

m reset handler = reset handler::get(this);

(1'b0),

m_reset_handler.register( .is_master

.h_component ( this ) ,

( "C1" )

.domain id

);

Registering C2 slave with Domain

endfunction : build phase

ID = "C1"

virtual task do reset(string reset type = "");

//implementation details

endtask : do reset

endclass : C2

```

Figure 11. Registering Reset Slave component with Reset Handler

The registration process is order independent, implying any RS can register itself before the RM registration. Order independence is mandatory as registering a component as RM/RS is done in UVM build\_phase() and reset hierarchy can be different from the UVM hierarchy of the components. In other words, the order in which the VIP components are built in build\_phase() may not be the same as an RM to RS relationship/hierarchy. This might cause a problem as there may be chances of a Reset Domain having no registration of a Reset Master, as there is no such compulsion in build phase().

To guarantee that all Reset Domains have a Reset Master registered, the reset\_handler validates the associative array queues and master registration status database in the UVM connect\_phase(). In the validation process, the reset handler checks and flags errors, if found, in the following cases:

- 1) A Reset Slave does not exist for a Reset Master in a domain

- 2) A Reset Domain has no Reset Master registered

- B. Reset Assertion

When a Reset Master needs to assert reset operation to its associated slaves, it uses the reset\_handler handle to call reset\_handler.assert\_reset() function.assert\_reset() is a System Verilog function and takes following input arguments:

1) domain\_id (string): String name of the reset domain for which reset is being asserted

2) h\_component (uvm\_component): Handle of the Reset Master component from which reset is being asserted.

3) reset\_type (string): String representation of the type/mode of the reset being asserted. This is an optional argument.

4) slaves\_only (bit): Single bit to specify whether the reset operation must be performed on the Reset Slaves only (slaves\_only=1) or on Reset Master as well as associated Reset Slaves (slaves\_only=0). This is an optional argument, and the default value for slaves only is 0.

Figure 12. Reset assertion from Reset Master

## C. Reset Notification

When an assert\_reset() call is done from a Reset Master, the reset\_handler validates the Reset Master handle and locally updates a list of all active Reset Domains that have been requested reset. In run\_phase() task, reset\_handler performs following operations:

1) Waits for the list of active Reset Domains (Reset Domains that have been requested reset) to contain at least one element.

2) Gets the queue of reset\_interface handles of all the RMs, RMSs and RSs in the reset domain requested

3) Parallelly, calls do\_reset() task of all the RMs (if slaves\_only = 0), RMSes and RSes. Since the number of parallel threads initiating do\_reset() calls depends on the number of VIP components registered in the domain, the number of such threads is variable for each reset assertion. To handle triggering of variable number of threads each time reset is asserted, fork...join\_none can be used inside a loop over all queue elements. Initiating parallel do\_reset() calls is mandatory, as sequential calls may violate the purpose of achieving the simultaneous resets of all targeted VIP components.

Note that the assert\_reset() function does not directly call do\_reset() per VIP component, but instead just updates a list of active Reset Domains. This is necessary as assert\_reset() must be non-time consuming so that the Reset Master can proceed ahead without consuming any simulation time or blocking other operations while waiting for reset completion.

```

class reset handler extends uvm component;

// Local Databases

protected t reset if q m reset db [string] ;

protected bit m master sts db [string] ;

protected bit reset sts ; // bit to notify reset assertion

protected string active_domain_list[$]; //queue to store active reset domains

function void assert_reset(string domain_id, ...);

reset sts = 1 ;

active domain list.push back (domain id);

// Add code to record slaves only option

endfunction : assert reset

virtual task run phase(uvm phase phase);

forever begin

wait(reset sts == 1);

// Loop over all active reset domains

while(active domain list.size > 0) begin

automatic string curr domain = active domain list.pop_front();

if(m reset db.exists(curr domain)) begin

// Loop over all the elements of the curr domain

```

| DESIGN AND VERIELCATION<br>CONFERENCE AND EXHIBITION    |                                                                                  |  |  |  |

|---------------------------------------------------------|----------------------------------------------------------------------------------|--|--|--|

| <b>foreach</b> (m_reset_db[curr_c                       | lomain][i]) <b>begin</b>                                                         |  |  |  |

| fork                                                    |                                                                                  |  |  |  |

| <pre>automatic int comp_id = i ;</pre>                  |                                                                                  |  |  |  |

| <pre>m_reset_db[curr_domain][comp_id].do_reset();</pre> |                                                                                  |  |  |  |

| join_none                                               |                                                                                  |  |  |  |

|                                                         |                                                                                  |  |  |  |

| end                                                     | do_reset() call for the<br>RM/RMS/RS components in the<br>requested reset domain |  |  |  |

| end                                                     |                                                                                  |  |  |  |

| else begin                                              |                                                                                  |  |  |  |

| // Throw Error Message                                  |                                                                                  |  |  |  |

| end                                                     |                                                                                  |  |  |  |

| end                                                     |                                                                                  |  |  |  |

| reset_sts = 0 ;                                         |                                                                                  |  |  |  |

| end                                                     |                                                                                  |  |  |  |

| <pre>endtask : run_phase</pre>                          |                                                                                  |  |  |  |

| <pre>endclass : reset_handler</pre>                     |                                                                                  |  |  |  |

Figure 13. Handling reset notification to RM/RMS/RS components in the requested Reset Domain

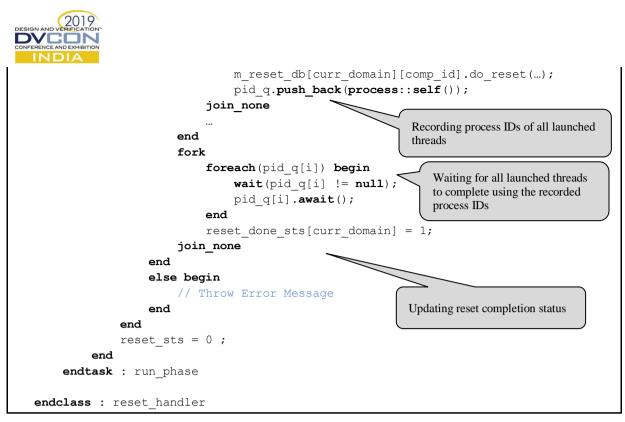

## D. Reset Completion

Once all the do\_reset() calls are parallelly triggered through multiple fork...join\_none threads, it becomes mandatory for reset\_handler to track all the launched threads and ensure all of them are completed and notify the completion. Reset Master may wait for reset completion using a separate task reset\_handler.wait\_reset\_done() since assert\_reset() call is non-time consuming. To track all the parallelly launched do\_reset() threads, process IDs of all the threads are recorded at the launch time. After all the threads are launched, the recorded process IDs are used to wait for threads to get finished. Reset completion is notified when await() calls on all the process IDs are completed.

```

class reset handler extends uvm component;

// Local Databases

protected t reset if q m reset db [string] ;

protected bit reset done sts [string]; // Stores reset completion status of

each reset domain

function void assert reset(string domain id, ...);

// Update initial status of requested domain

reset_done_sts [domain_id] = 0;

endfunction : assert reset

// wait reset done task: to be used by master for waiting on reset completion

task wait reset done(string domain id);

wait(reset done sts[domain id] == 1);

task to wait for reset completion of

endtask : wait reset done

the requested reset domain

virtual task run phase(uvm phase phase);

forever begin

// Loop over all active reset domains

while(active domain list.size > 0) begin

automatic process pid q [$];

if(m reset db.exists(curr domain)) begin

// Loop over all the elements of the curr domain

foreach(m reset db[curr domain][i]) begin

fork

```

Figure 14. Monitoring for Reset Completion of Active Reset Domains

#### V. BEYOND PLAIN RESET HANDLING

#### A. Clock Gating and Un-Gating

When verifying a design with clock gating features, the VIP environment might also be required to model clockgating of a set of VIP components. Like reset management, reset\_handler can be used to manage clock-gate assertions and notifying respective VIP components. Note that a VIP component must employ implementation dependent mechanism to clock-gate its own processes when notified to do so by reset\_handler. One of the ways that VIP component can use to clock-gate its own processes is to use suspend() calls on all its process IDs.

To achieve clock-gating management, two tasks are added to reset\_interface: do\_suspend() and do\_resume(). These tasks shall be overridden in the VIP component which implements the reset\_interface. When a Reset Master asserts clock-gating in a Reset Domain using reset\_handler.assert\_suspend() function, reset\_handler calls do\_suspend() on all the RMs, RMSes and RSes registered in the requested Reset Domain. Similarly, a Reset Master uses reset\_handler.assert\_resume() function call to issue do\_resume() for the requested Reset Domain and mimics clock un-gating feature.

## B. Disable vs Reset

Expanding the scope further, reset\_handler can also be used to trigger disabling of a set of VIP components registered in a Reset Domain. A task do\_disable can be added to the reset\_interface. A VIP component implementing the reset\_interface in this case, shall also override do\_disable task to implement disabling of the processes in the component. The difference between do\_disable and do\_reset is that the component which is disabled does not start running the processes again automatically until a do\_reset call is made to the component. On the other hand, do\_reset call is intended to perform both, disabling of the processes in the component as well as re-starting and re-initialization of the processes.

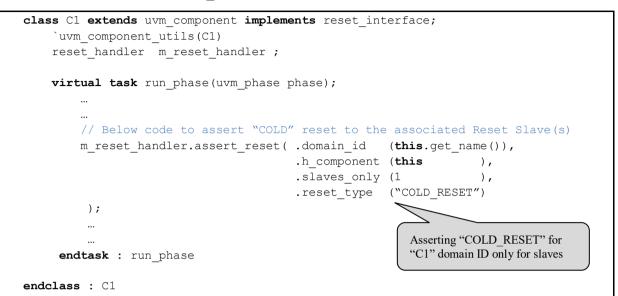

#### C. Multi-Variant Reset Management

As mentioned earlier, <code>assert\_reset()</code> call from a Reset Master has a string input argument <code>reset\_type</code>. This argument can be used by a Reset Master to specify the mode/variant of reset to be issued to the Reset Slaves. For example, the argument <code>reset\_type</code> can be set to "COLD RESET" or "WARM RESET".

The reset\_handler takes no action based on reset\_type and directly forwards it to the Reset Slaves by passing the same argument to the do\_reset() call for each Reset Slave. Since, the Reset Slaves are protocol dependent, the do\_reset() task in the Reset Slave shall be implemented to handle all the reset types according to the protocol. Hence, it becomes simpler for a VIP component writer to handle different varieties of resets based on the string input argument of the do reset() task.

Figure 15. Asserting "COLD RESET" from Reset Master

Figure 16. Handling "COLD RESET" in a Reset Slave

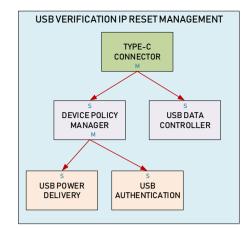

# VI. DEPLOYMENT IN USB POWER DELIVERY VIP

The proposed technique is deployed successfully in USB Power Delivery (PD) Verification IP environment and various possibilities like resetting sub-components with different types of resets have been extensively tested. The overall structure of environment for USB PD Verification IP and reset relationship is shown in Figure 17 below.

Figure 17. USB PD Verification IP Reset Hierarchy

This technique is also extended for disabling and suspending the sub-components apart from resetting. Also, it is used to handle SOFT\_RESET and HARD\_RESET variations in USB Power Delivery protocol. The failure debugs related to reset testing were faster and simpler using the proposed technique.

## VII. CONCLUSION

This paper defines a standard flow which helps in performing dynamic reset operations and modeling reset management in a scalable, efficient and graceful way. Maintaining a central database eases the development of Reset Master/Slave components, which just need to define the handler tasks: do\_reset(), do\_disable, etc. Structuring the VIP with a centralized reset\_handler also helps in faster debugs, modification of existing scenarios and adding new scenarios.

#### REFERENCES

- [1] Accellera, Universal Verification Methodology 1.2, June 2014.

- [2] IEEE Computer Society, System Verilog, 2017.

- [3] Brian Hunter, Ben Chen and Rebecca Lipon, "Reset Testing Made Simple with UVM Phases," in Synopsys User Group, 2013.

- [4] Courtney Fricano, Stephanie McInnis, Uwe Simm and Phu Huynh, "Reboot your Reset Methodology: Resetting Anytime with the UVM Reset Package," in *Design and Verification Conference*, Europe, 2014.