Next-Generation Automotive Functional-Safety<sup>™</sup>

#### Revitalizing Automotive Safety Hard and Soft Error Approaches

Presented as tutorial at DVCon 29, 30 Oct 2019, Munich

www.optima-da.com Nael Qudsi nael@optima-da.com Ayman Mouallem ayman@optima-da.com

**OPTIMA** Next-Generation Automotive Functional-Safety 7 - © Optima Design Automation – Confidential - All Rights reserved – Delivered at DVCon Oct 2019, Munich, Germany

## Agenda

- About Optima

- New challenges in semiconductor land: ISO-26262

- Challenges and solutions for Hard-Errors

- The Optima-Medini/Ansys integration

- Optima-SA<sup>™</sup> for early structural Analysis and fault-model sizing

- Optima-SA demo

- Optima-HE<sup>™</sup> Hard-Error or permanent faults analysis

- Optima-HE demo

- Soft-error or transient faults problem definition

- Optima-SE<sup>™</sup> Soft-error analysis solution

- Optima-SE demo

### **Optima Design Automation**

- Portfolio of advanced solutions for complex safety scenarios

- Key challenges addressed with automated, effective safety apps

- Revolutionary, high-performance fault simulation technology

Radical, new algorithms drive 1,000X performance improvement

- CoverageMaximizer™ Technology

- $\circ$  ~ For manual and automated diagnostic Coverage closure

- Well funded\* core team of verification & safety experts

• Substantial EU funding has enabled a world-leading expert team

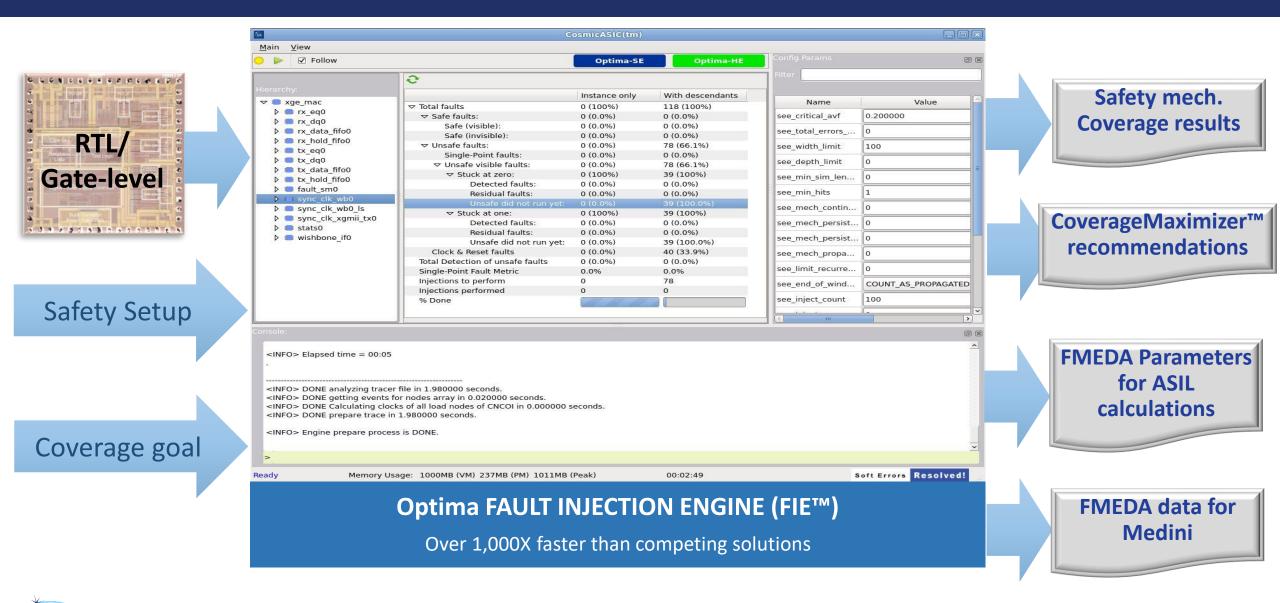

Optima-SE<sup>™</sup> Soft Error Simulation and Selective Hardening

Automated FIT rate reduction to enable ASIL-D with minimal silicon cost

Optima-HE<sup>™</sup> Hard Error Coverage Measurement & Boosting

Rapid fault coverage measurement with automated coverage boosting

Optima-SA<sup>™</sup> Structural Analysis Solution

Provide accurate FMEDA, for safety setup alternatives size calculation

Optima Fault Injection Engine<sup>™</sup> (FIE) Technology Platform: 1,000x faster than competing solutions

\*This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No. 850104.

**OPTIMA** Next-Generation Automotive Functional-Safety<sup>TM</sup> - © Optima Design Automation – Confidential - All Rights reserved – Delivered at DVCon Oct 2019, Munich, Germany

## New Challenges in Semiconductor Land: ISO-26262

## Hard-errors: Different Safety Mechanism methodologies

## Logic-BIST

Stop the unit, perform Logic-BIST test on it Reset it

Put it back in operation

Suitable if you have redundant cores and can stop one or a few of them for testing

# STL SW Test Lib

Dedicated STL process that reads and writes to CPU register to check it's lack of permanentfault Lockstep

Duplicate the IP twice Both get same inputs Compare outputs at each cycle Other Methods

Parity bits

ECC, CRC

Hand crafted methods

Watchdog

Etc.

Suitable for CPU designs only, some IP vendors provide it with the CPU IP

Suitable for mostly for CPUs But can be used for other designs

## Hard-errors: Measuring SM Coverage

- Whatever the methodology used for a given unit

- Need to measure the Safety Mechanism coverage

- Perform fault-simulation on all pins of all gates

- Measure if the SM can detect this fault or not

- Run all needed fault models

- Stuck-at-0

- Stuck-at-1

- Bridging-fault

- Etc.

- Need to be done on gate-level

- The task is immense, given the number of gates in the chip X time-per-faultsim

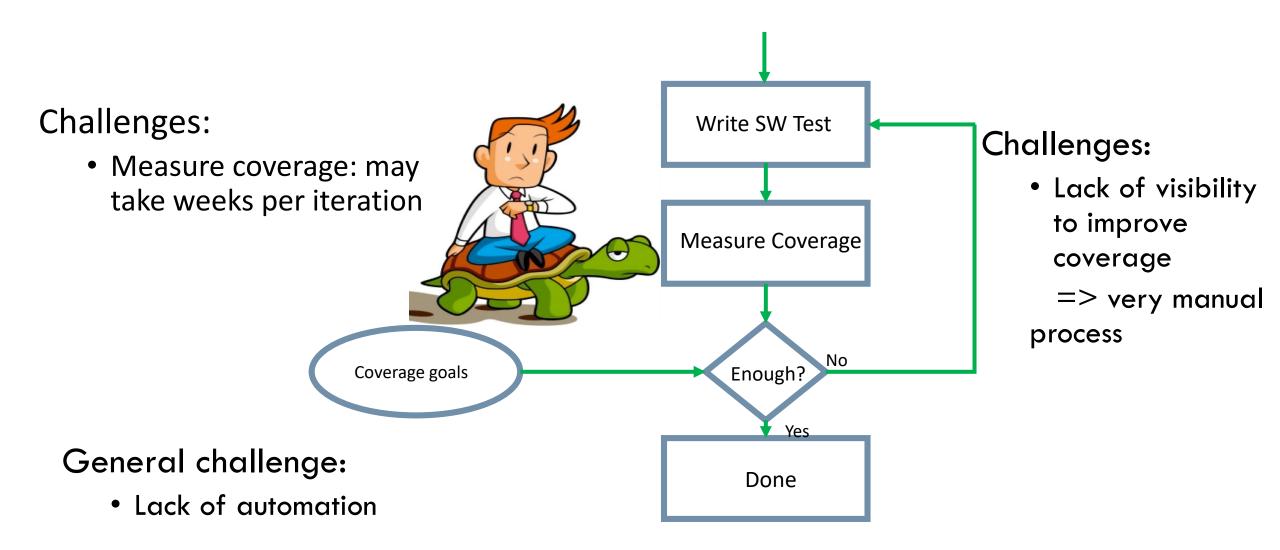

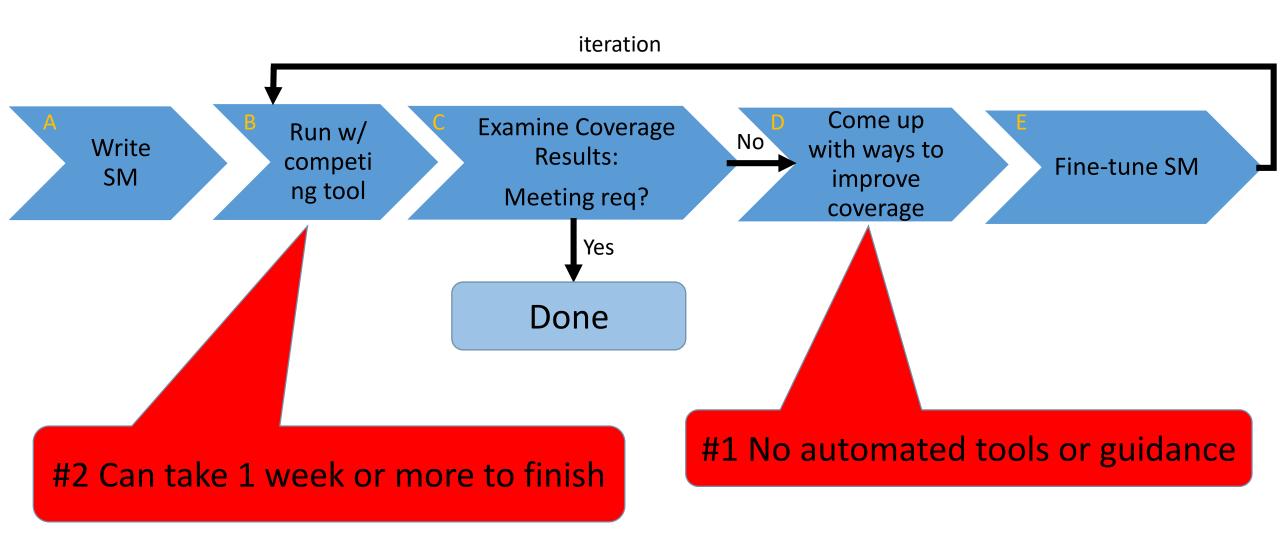

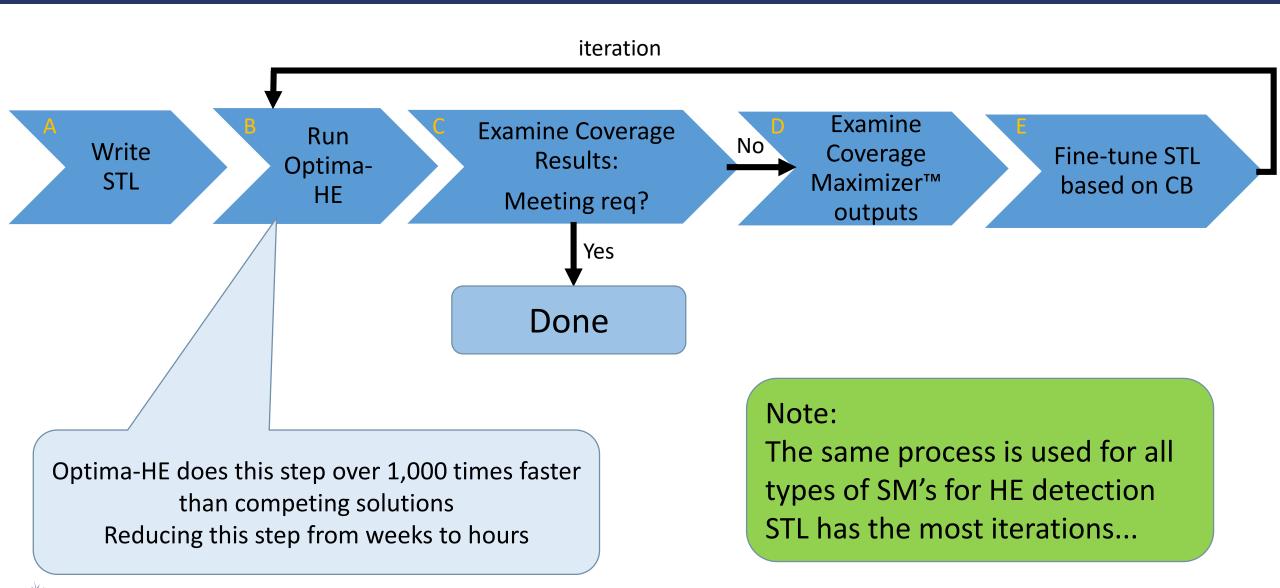

## The General Work-Flow (without Optima)

## Challenges:

# Challenge 1: Reaching Coverage goal can be very manual and human-resource intensive

- No automated way to improve coverage

- No guidance and information to improve coverage

- No easy way to browse coverage results

• Optima is changing this with CoverageMaximizer<sup>™</sup>

# Challenge 2: Run-time to measure SM coverage could become hundreds of compute years problem

- Need to be done at gate-level

- Each gate in the design need to be simulates 2..3 times (for each fault-model)

10 Million gates x 2 x 5 min = 100 million min (before fault-pruning reduction)

## ~190 machine years

11

• Optima is changing this with

• Optima's fault-simulations are over 1,000x faster than competing solutions

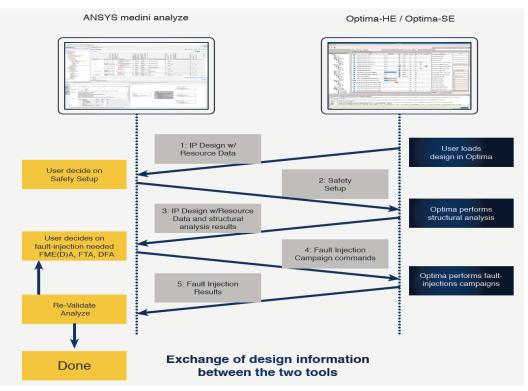

# Optima-Ansys flow

#### Contraction of Contra Optima Medini 1: IP Design w/ User loads **Resource Data** design in Optima User decide on Safety Setup 2: Safety integrat Setup Optima performs 3: IP Design w/Resource structural analysis Data and structural analysis results User decides on fault-injection needed 4: Fault Injection FME(D)A, FTA, DFA Campaign commands Optima performs fault-5: Fault Injection injections campaigns Results **Re-Validate** Analyze ratic סטוווומ שפוקון אתנטוומנוטון – כטוווטפונומן - און אוקוונג ופגפו יפט – שפוויפופט מג שי כטון טכנ לטבש, ויוטוונון, ספווומווץ тэ

#### ANSYS medini analyze

Ansys

ion

#### Optima-HE / Optima-SE

## Benefits of the Optima Medini integration

- Formalized communication between the "ASIC world" and "FuSa world"

- Seamless, closed-loop integration

- Fusa management platform

- Safety analyst, FME(D)A

- ASIC fault simulation platform

- 1000X faster fault-simulation

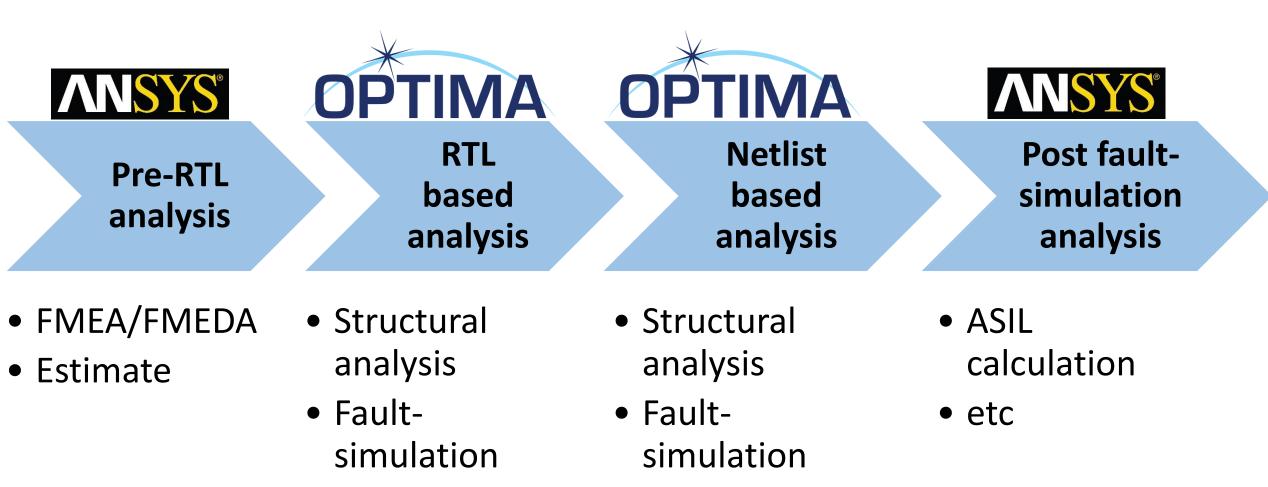

## High-level Safety Flow

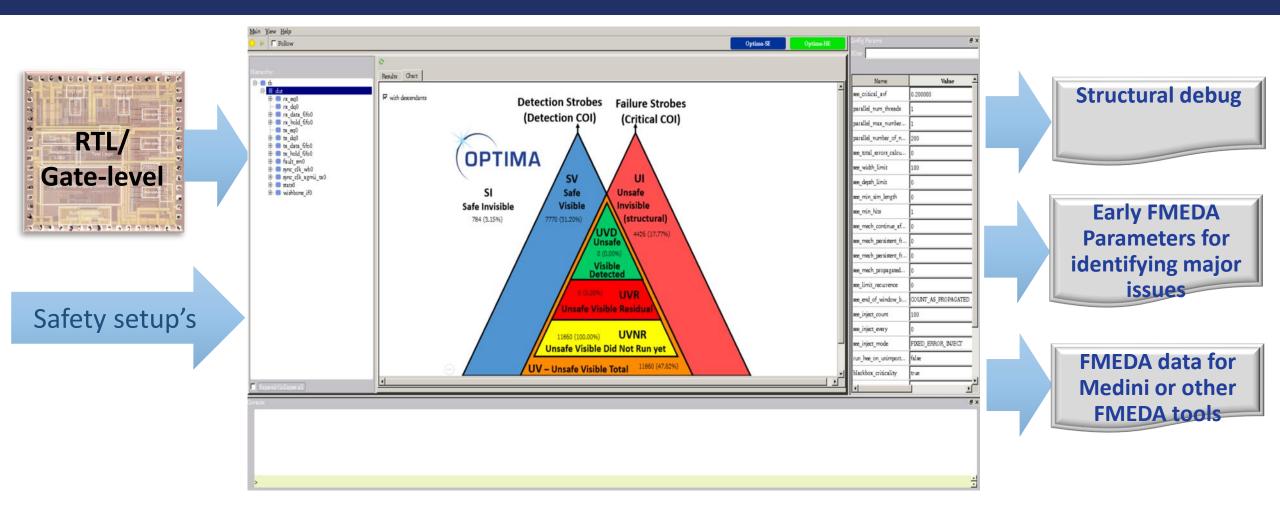

## Optima-SA<sup>™</sup>

Early structural Analysis and fault-model sizing

## Optima-SA<sup>™</sup>: Early structural analysis and FMEDA sizing

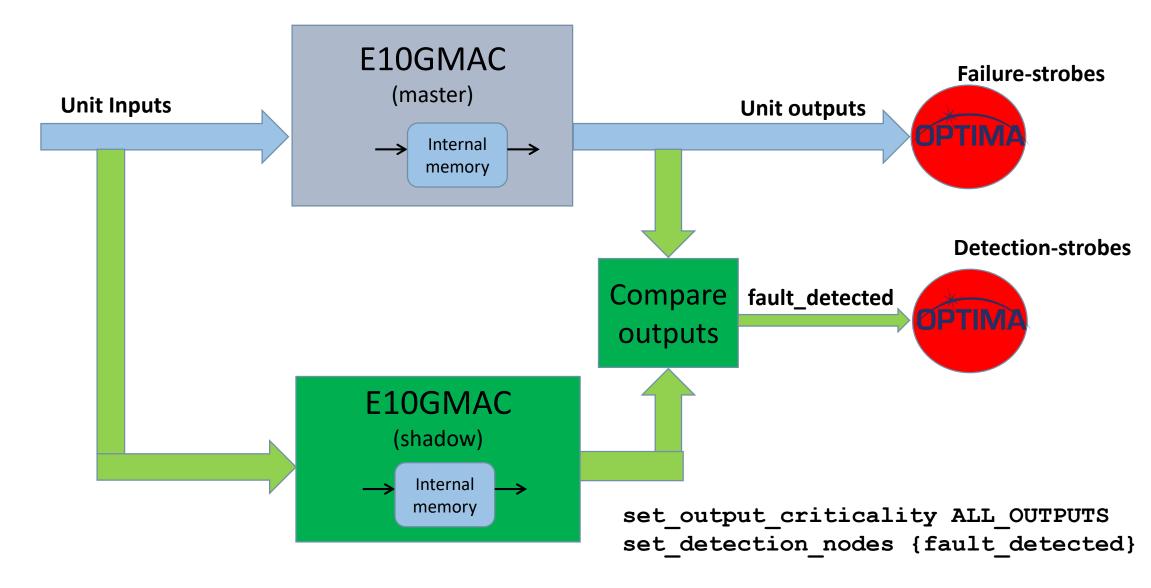

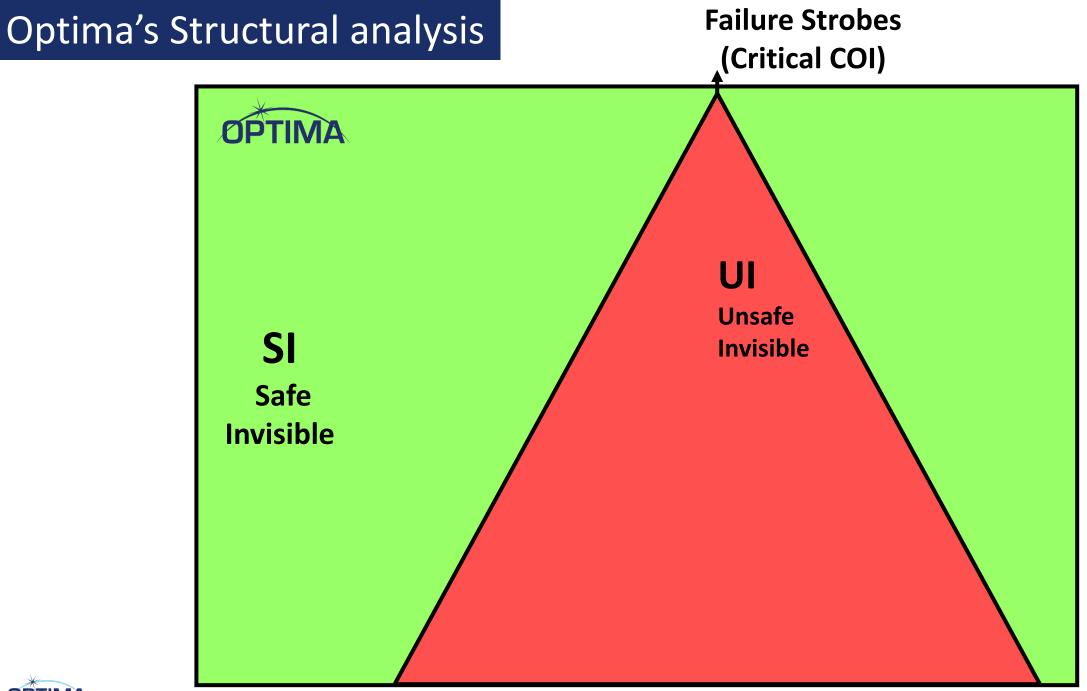

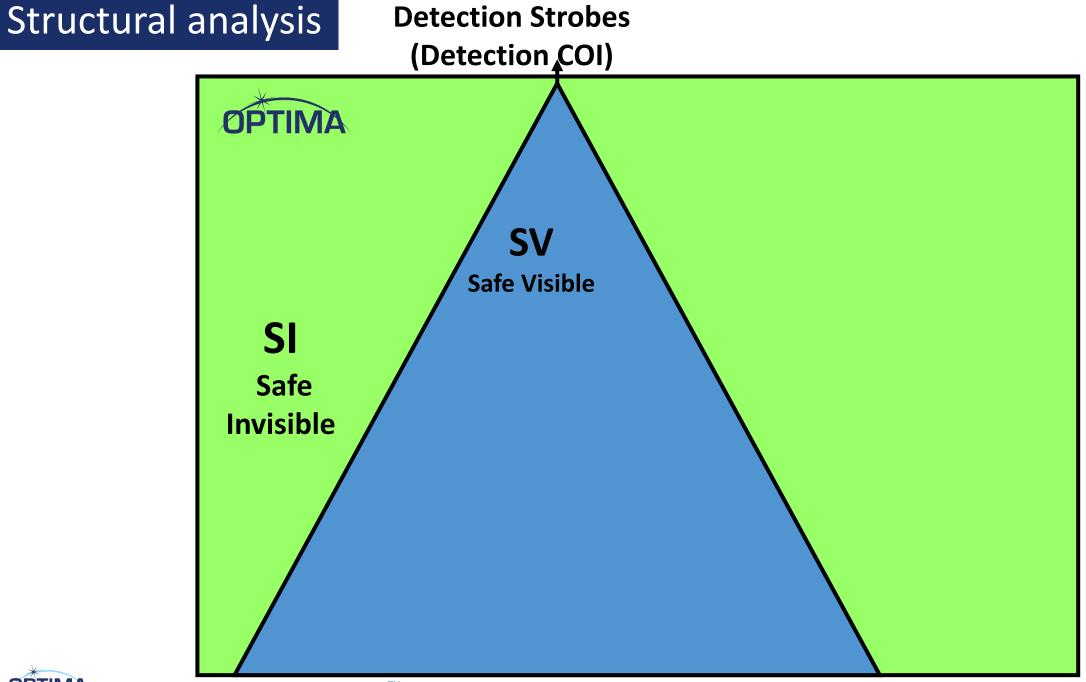

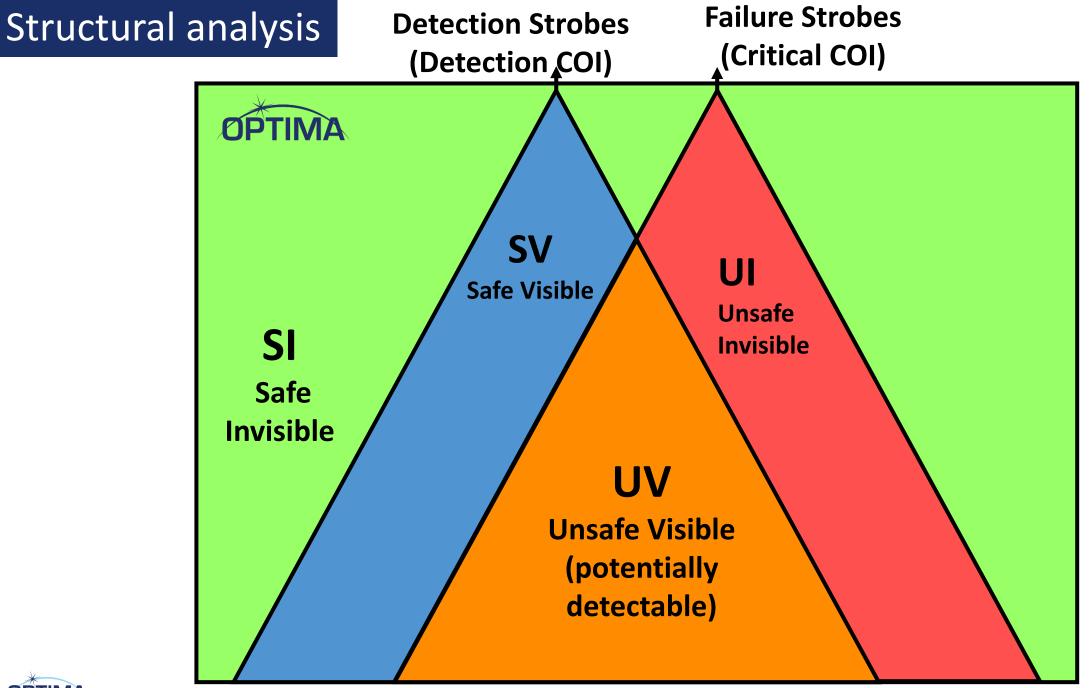

## Safety Setup: definition

- Given a design in RTL or GL-netlist, a Safety Setup includes:

- A given Failure Mode (Safety Goal)

- and its covering Safety Mechanism

- Need to specify the related signals:

- Failure-Mode Strobes of a Failure-mode are the hardware signals that if fault arrives to them the Failure-mode is activated

- Detection strobes of a Safety Mechanism are outputs of the Safety Mechanism, hardware signals or SW variables, that are activated when a fault is detected

## Example with Lockstep SM methodology

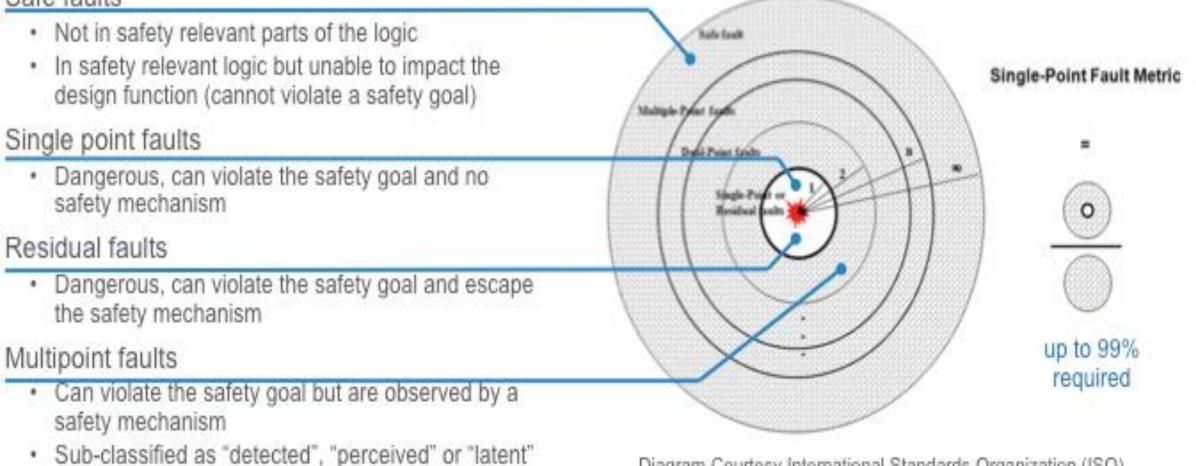

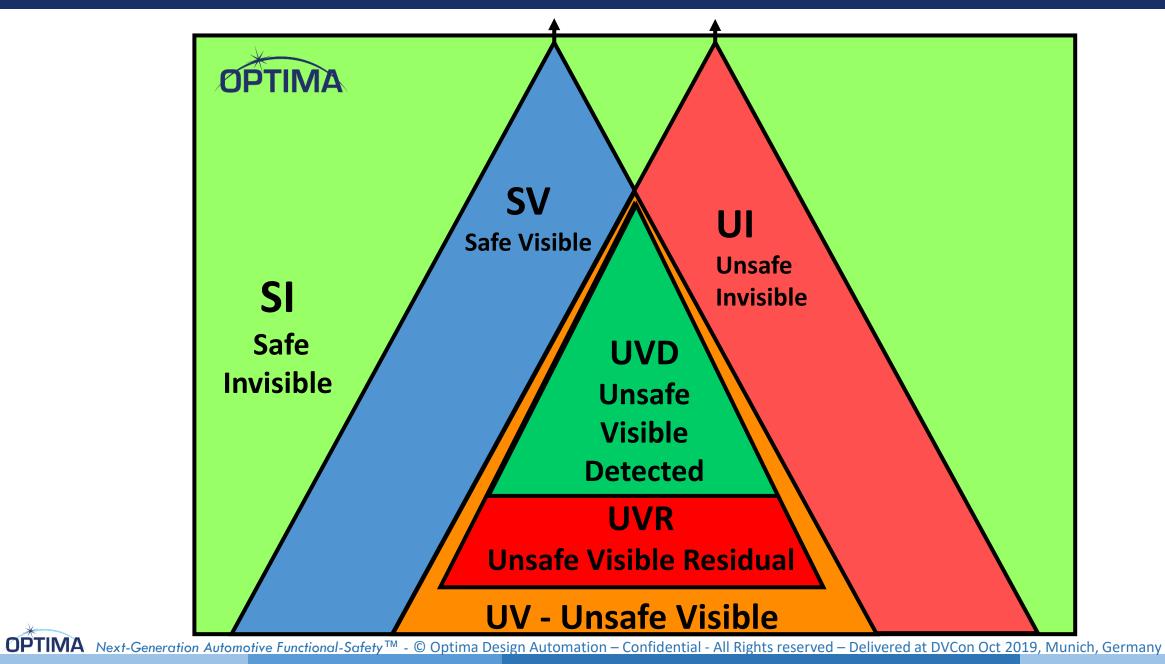

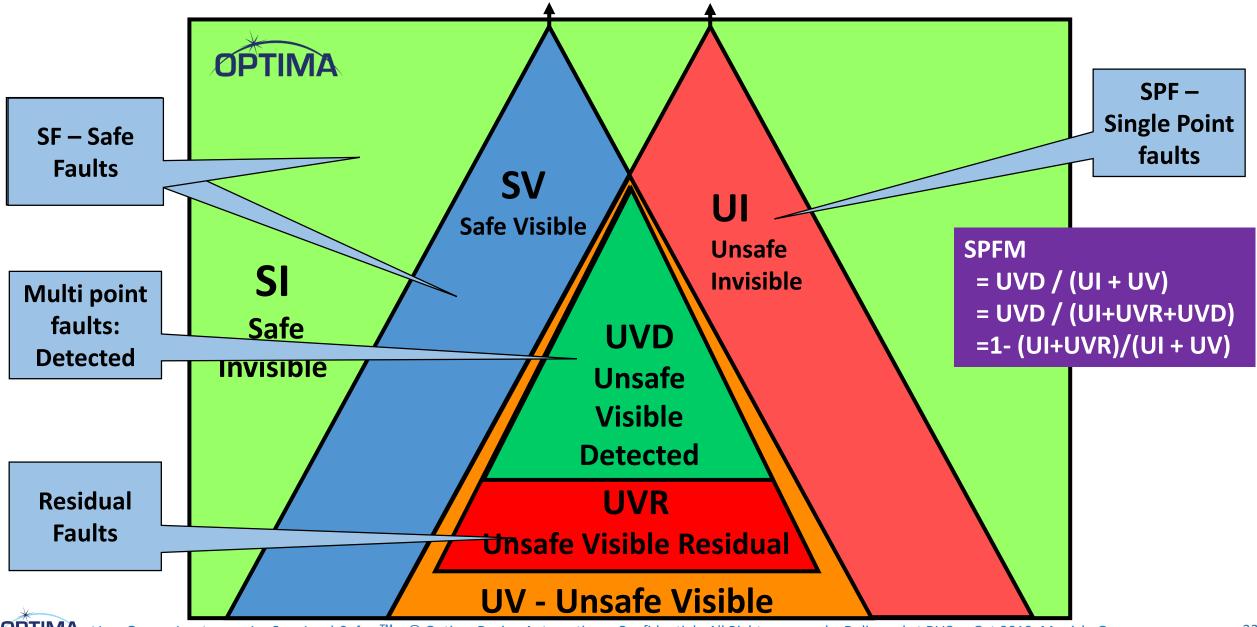

#### **ISO-26262 FMEDA parameters**

#### Safe faults

Diagram Courtesy International Standards Organization (ISO)

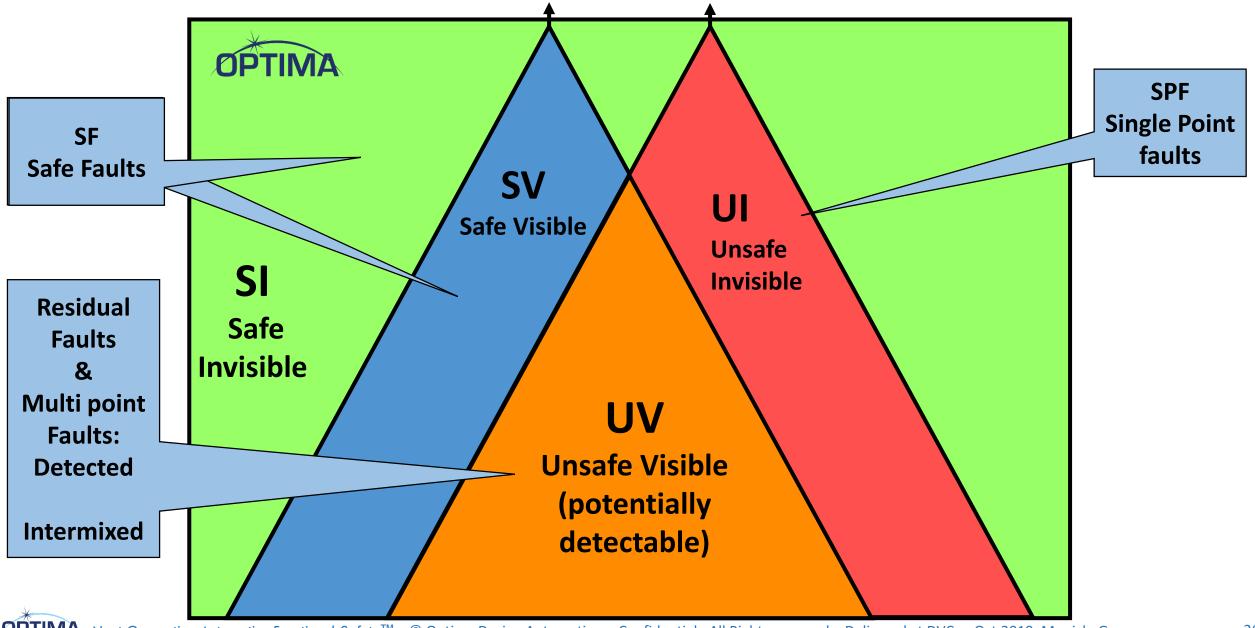

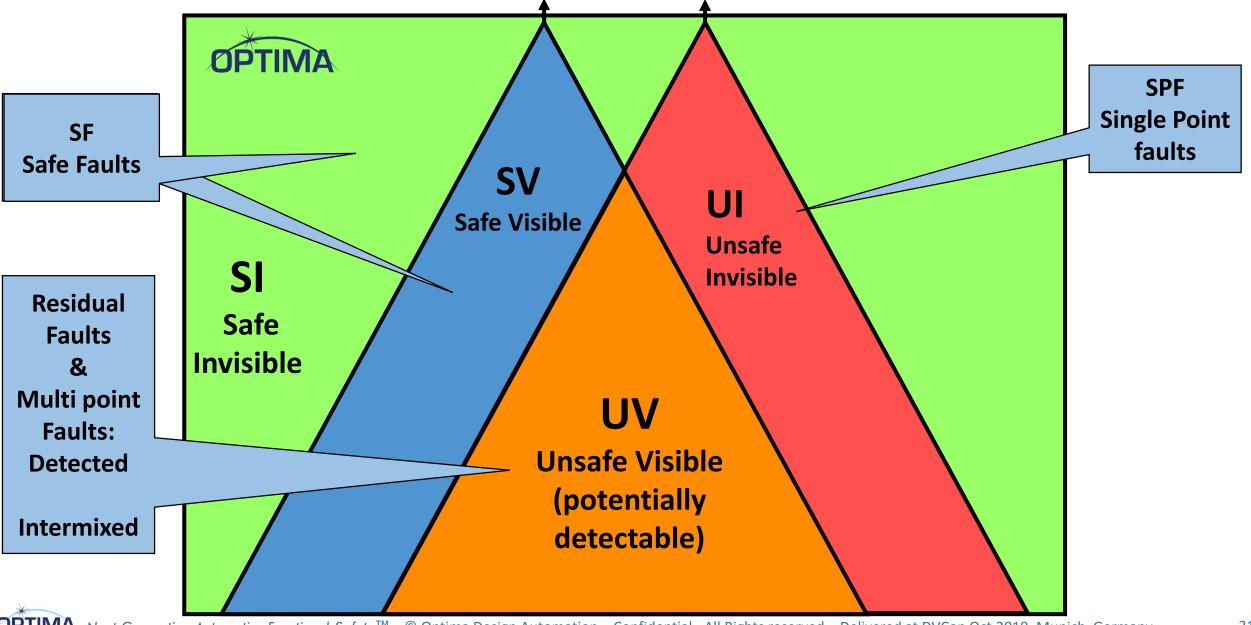

#### Mapping Optima's Structural analysis to FMEDA terms

## Optima-SA<sup>™</sup> demo

### Optima-SA: Early structural analysis and FMEDA parameters sizing

#### Features

- Size the FMEDA parameter

- Early detection of major issues:

- Like SPF is too large

- Certain areas not covered by any SM

- Unnecessary overlap between SM's

- Works on both RTL (early estimation) or gate-level (final results)

- Advanced structural debug capabilities

- Hierarchical based results

#### Benefits

- 0-effort

- Very fast, results available in minutes to 2 hours

- Identify issues early in the project, based on RTL only

- Analyze each fault-model separately, by groups, or all FM's combined

- Export your results to your FMEDA tool (Ansys, Excel, or any other)

## Optima-HE<sup>™</sup>

## Hard Error fault-simulation

## Optima-HE<sup>™</sup>

- Will take-over after Optima-SA<sup>™</sup>

- Perform accelerated fault-simulation in the UV area

- Split the UV area into Detected and not Detected

#### What Optima-SA gave us....

#### Optima-HE results:

#### Optima-HE results:

## Optima-HE<sup>™</sup>: Complete Hard-errors solution

## Application Example: Tuning STL – Software Test Library

## **Optima-HE: Features**

- Ultra fast fault simulation engine

- Fast single-thread performance

- Parallel multi-threading, work on as many CPU-Cores available as possible

- With 64 Cores machine, speedup can reach 64X the single thread performance

- Fault-Pruning

- Identify only the faults needed for ISO-26262 requirements

- Do faults only on them

- Fault-Collapsing

- Identify faults that will produce the same results and do only what is needed

- Works both on RTL and Gate-Level Netlist

- RTL for initial estimations etc

- GL for final results for the audit report

## **Optima-HE: Ultra-fast Hard-Error fault simulation**

#### Features

- Exhaustive fault simulation

- Safety-Mechanism coverage

- CoverageMaximizer<sup>™</sup>:

- guidance for raising coverage

- For both gate-level and RTL

#### Benefits

- Faster fault simulation

- High accuracy

- Low effort coverage boosting

- Reduce Time-to-Market

- Reduce design costs

- Reduce needed compute resources

## Optima-HE<sup>™</sup> demo

## CoverageMaximizer™

#### Guided-Manual and automated closure of diagnostic coverage

## More details can be delivered under NDA

## Transient faults or Soft-Errors Problem definition

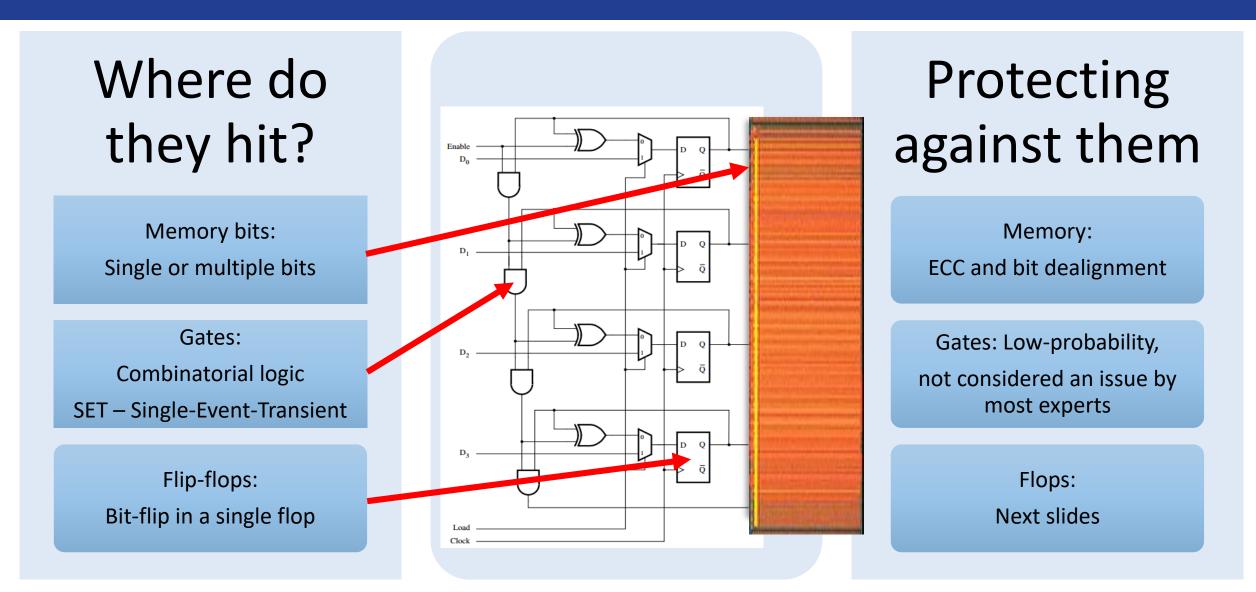

## Transient-faults (Soft-errors/SEU/SET): What are they?

Bit-flips caused mostly by cosmic-rays (radiation coming from the Sun)

## Protecting against Transient-faults at the flops:

Unit-level Lockstep mechanism (cost: 70% more silicon) Hardening all flops (cost: 30% more silicon) Selective flip-flop hardening (cost: 1-5% more silicon) Using older silicon nodes (like 180nm) Using special Rad-Hard silicon technology

**OPTIMA** Next-Generation Automotive Functional-Safety<sup>™</sup> - © Optima Design Automation – Confidential - All Rights reserved – Delivered at DVCon Oct 2019, Munich, Germany

## Transient-faults (Soft-errors/SEU/SET)

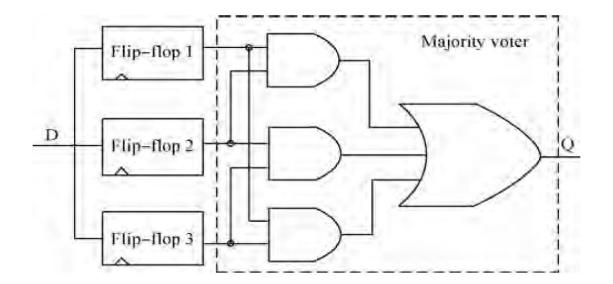

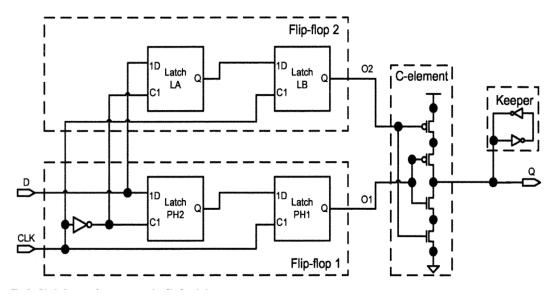

## Soft-errors: Examples of flip-flop hardening methods:

#### TMR with Majority voter

#### **DMR** with C-element

## Transient-faults: logical-masking, deration and AVF

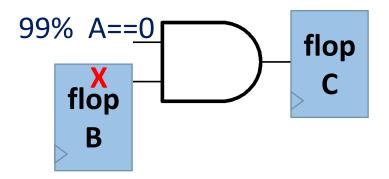

• Most flop TF are masked by the "logical masking" phenomena

if 99% of the time: A== 0

Then most faults on B or coming from B will be masked

- Some flops are logically masked most of the time

-> they have low AVF

- Some are not

-> they have high AVF

#### AVF : Architectural Vulnerability Factor

AVF of flop\_a is:

the probability that when a TF (bit-flip) happened on flop\_a, then the error will propagate and reach a safety-goal output

## Optima-SE: Soft Error: Selective Hardening

- While some designers resolve Soft Errors by complete duplication of fullunits, or sometimes even full-CPU (lock-step or TMR), selective-flip-flop hardening is considered to be the most optimal and cost effective method

- Our tools enables selective flip-flop level hardening

- Definition: Find the 5-10% of the flops that contribute the 99% of the FIT, and perform hardening only on them. Reduce the FIT rate to close to 0

- This is an old problem in the industry, but almost has No commercial and accurate solution, all solutions require immense compute resources (measured in years and hundreds of years of simulations)

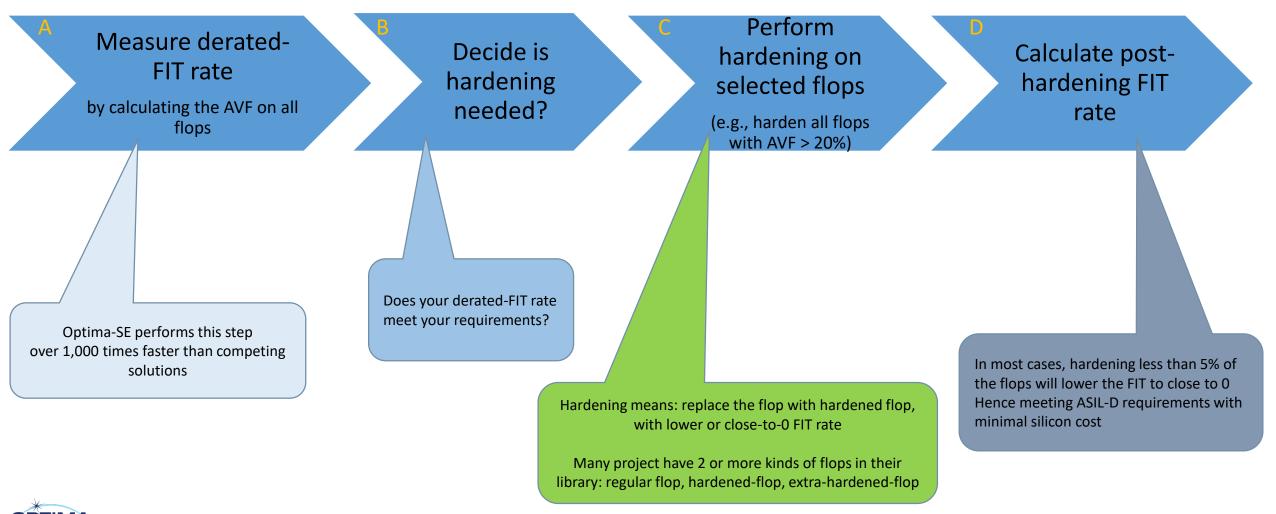

## Selective hardening process:

### Challenge: Calculating AVF can take hundred of compute years

- Calculating AVF involves performing fault simulations on all flops

- Each flop needs to be fault-simulated 50 to 1000 times to build reliable statistics

- Historically, this has been "very lengthy and expensive task"

50 sims X 1M flops X 10 min = 500M min =

# 950 machine years

- Optima is changing this with

- Optima's fault-simulations are over 1,000x faster than competing solutions

- Reducing the 950 machine years to ~4 machine days

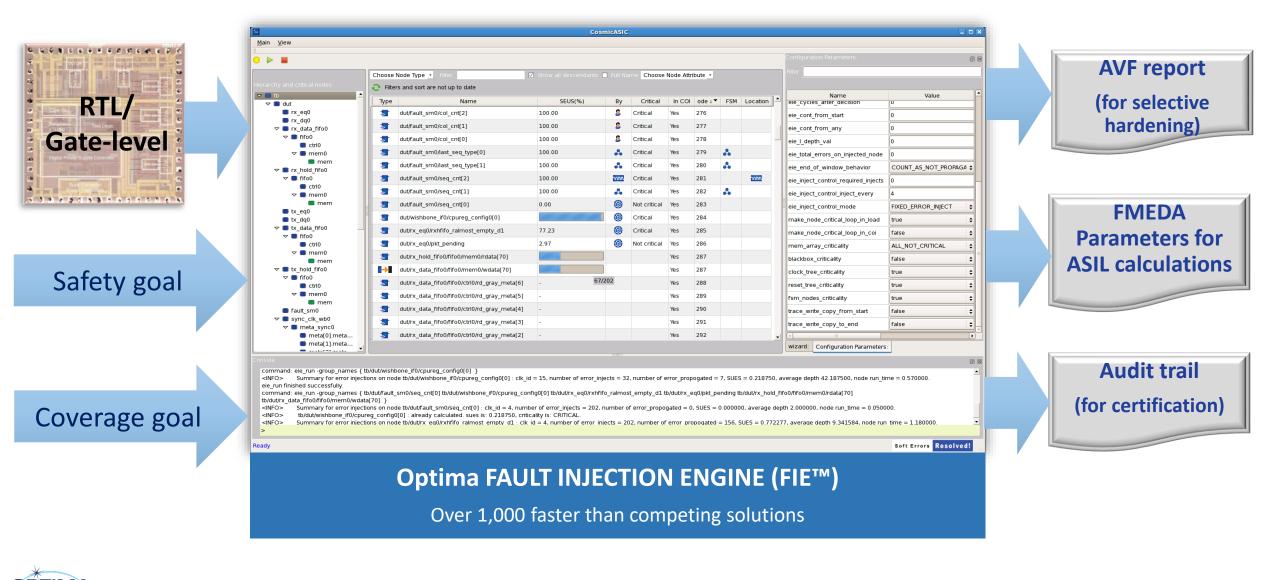

## Optima-SE Soft-Error – Transient faults solutions

## Optima-SE<sup>™</sup>: Complete Soft-errors solution

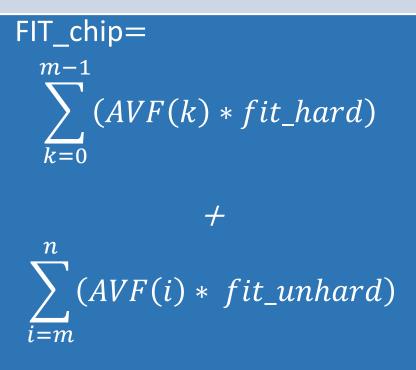

#### Another way to look at it: FIT rate calculation

<u>Without knowing</u> the "personal" AVF of each flip-flop

FIT\_chip= n \* fit\_unhard <u>With knowing</u> the "personal" AVF of each flop

(using Optima-SE or other methods)

#### Without hardening

$FIT_chip = \sum_{k=0}^{n} (AVF(k) * fit\_unhard)$

With knowing the "personal" AVF of each flop

(using Optima-SE or other methods)

With selective hardening of m flops

63

n = Number of flops in the chip/IP/unit AVF(k) = The "personal" AVF of specific flop k m= number of hardened flops FIT\_chip fit\_unh fit\_hard

= FIT Rate for the chip/IP/unit from flop from soft-error

= FIT Rate of a single flop, unhardened regular flop

= FIT Rate of a single flop, for hardened flop

## Pre-silicon application of Optima-SE

- All 4 steps are possible

- Lower the FIT rate to achieve the required ASIL level

- Easley balance silicon hardening cost with lower-FIT rate

- Fault-simulations can be performed multiple times during the project

- Early RTL for estimation

- Re-run after different version and different hardening decisions or Safety-Mechanism changes

- At RTL-freeze as close-to-final results

- At Gate-Level for final results and certification

- Etc..

- Optima's Fault-simulation speed

-> increased fault-capacity

-> raise the accuracy of measurements

## Post-silicon (Post-Software) application of Optima-SE

- Only steps A is possible (calculate derated FIT rate), however:

- In many projects, due to the limited fault-simulation capacity

- Derated-FIT rate is not calculated

- No deration is taken in the ASIL and FIT calculations

- Over-estimation and safe-guards are used

- Resulting in higher FIT rate and lower ASIL than the chip really is

- Measuring deration with Optima-SE allows:

- Accurate measurement of actual derated FIT rate

- The measurement can lower the previously calculated FIT rate

- Hence, raise the ASIL level

- In some cases, tweaking the SW can also lower the derated-FIT rate (post-silicon)

- Value proposition to our customers:

- Re-certify your chip to higher ASIL

- Raise the price/value of the chip

- Bid on projects closed to you before, due to low ASIL

Another option: Combine selective hardening with planned re-spin to improve FIT rate

## Optima-SE: Value proposition:

- Industries only:

- Automated and complete solution for soft-errors

- RTL based solution

- Lower the FIT rate to close to 0 at low silicon cost => Meet ASIL-D requirements

- Hardening results can either be inserted to RTL or to Gate-Level

- Ultra-fast fault simulator allows accurate results

- Vast savings in:

- Silicon cost

- Compute power

- Engineering time and costs

## Optima-SE<sup>™</sup> demo

## **Optima-SE: Ultra-fast Soft-error Fault Simulation**

#### Features

- Calculate derated FIT rate

- Selective-hardening

- Lower FIT rate to close to 0

- Measure SM effectiveness

- 1,000x faster than competing solutions

#### **Benefits**

- High accuracy

- Improve ASIL

- Reduce:

- Time-To-Market

- Silicon and power

- Compute-resources needs

#

#### **Next Generation Automotive Functional Safety**

www.optima-da.com info@optima-da.com +972-4-619-4602

# Terminology

## Glossary (key confusing terms)

OPT

| <b>"Old" Scientific term</b>                  | ISO-26262 term               | Meaning                                                                                                                                                                                                      |

|-----------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEU<br>Single Event Upset<br>SE<br>Soft-Error | <b>TF</b><br>Transient-fault | <ul> <li>Bit-flip at a storage element:</li> <li>memory bit</li> <li>latch</li> <li>flop</li> <li>Soft: No hardware damage happened</li> </ul>                                                               |

| <b>SET</b><br>Single Event Transient          | <b>TF</b><br>Transient-fault | <ul> <li>Particle hitting a gate, causing a glitch that travels through the combinatorial logic</li> <li>It may be latched at flip-flop → become SEU Mostly, it will not be latched and dissipate</li> </ul> |

| HE<br>Hard-Error                              | Permanent Fault              | Physical damage in the chip.<br>A burnout of a transistor.<br>Seen as stuck-at-0, stuck-at-1, bridging fault etc.                                                                                            |

## Measuring failure: FIT – Failure in Time

FIT: Number of failures in 1 Billion hours

ISO-26262 requirements are in the range of 100 FIT

1 FIT = 1 Failure in 114,080 y

100 FIT = 1 Failure in 1,140 y

Why it has to be this low?

If Toyota has sold 1M cars (from certain model/year) with FIT=100 per car

The FIT of all the cars is 1M\* 100 FIT

They will have 1 failure every 10 hours