## **REUSABLE UPF:** Transitioning from RTL to Gate Level Verification Durgesh Prasad, Jitesh Bansal, Madhur Bhargava Mentor Graphics Corp. 8005 SW Boeckman Rd. Wilsonville, OR 97070

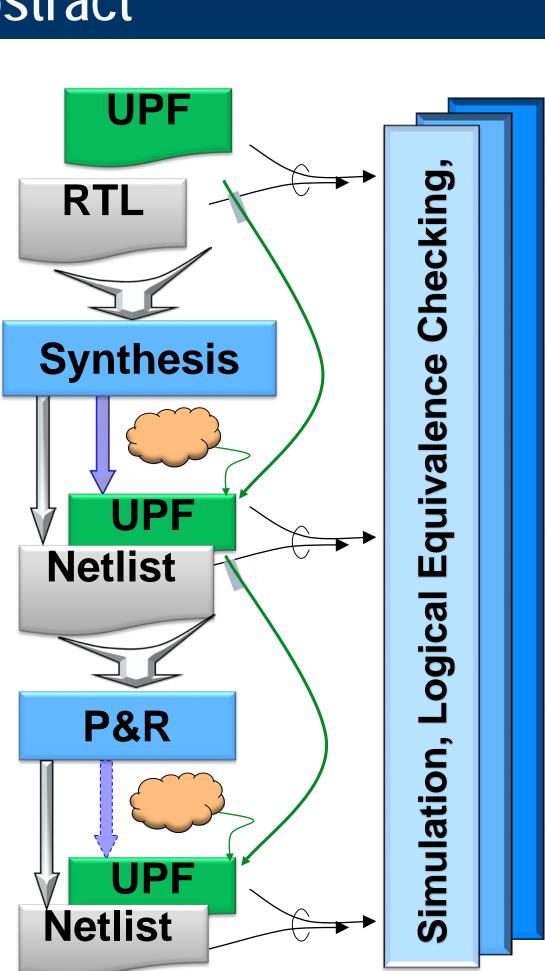

## Abstract

- Often UPF needs to be modified at the next verification stage (RTL to GLS)

- Hierarchy changes

- Cell placements

- Cell connections

- Problems

- Managing different UPFs

- Logic Equivalence

- Highlight differences between RTL and GLS UPF

- Proposed methodology to write RTL UPF

- > Minimal UPF changes required during gate-level power verification

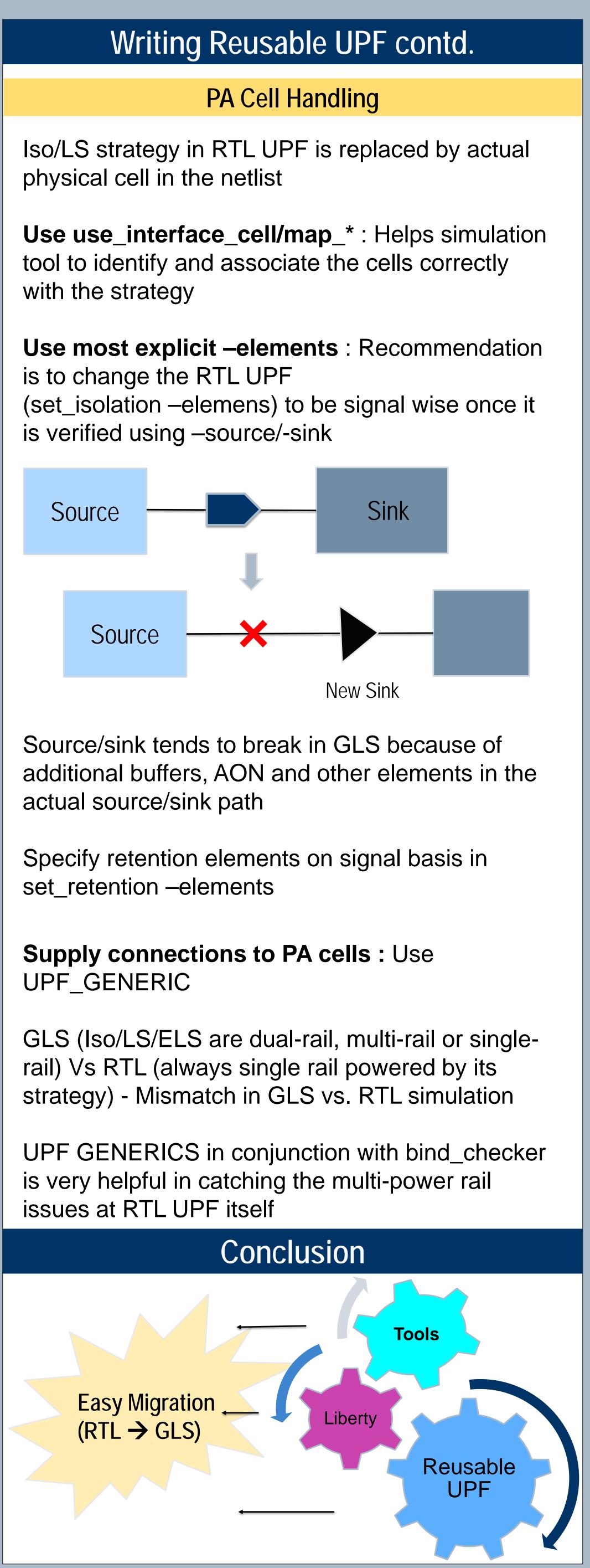

Benefits of Re-usable UPF

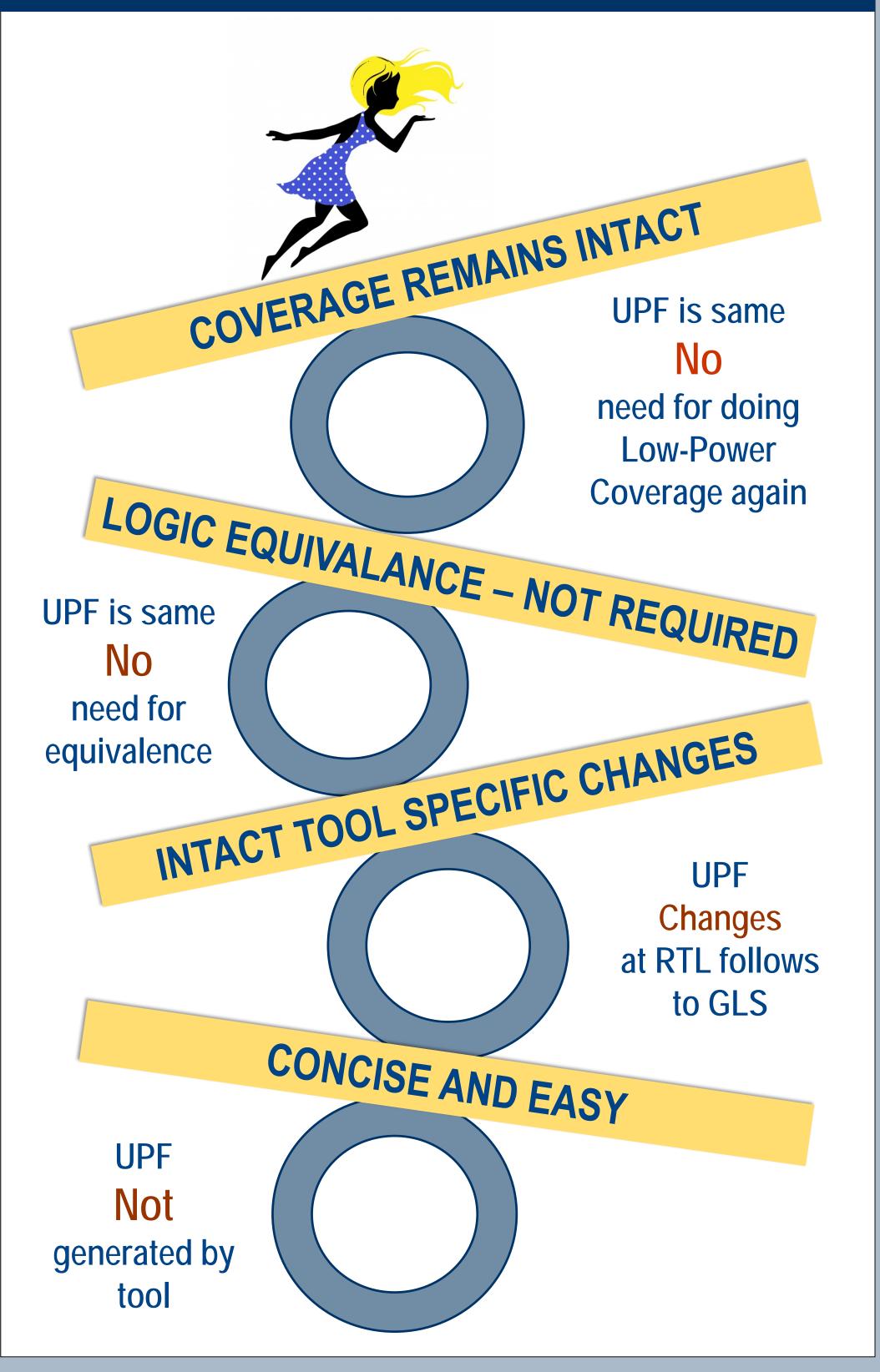

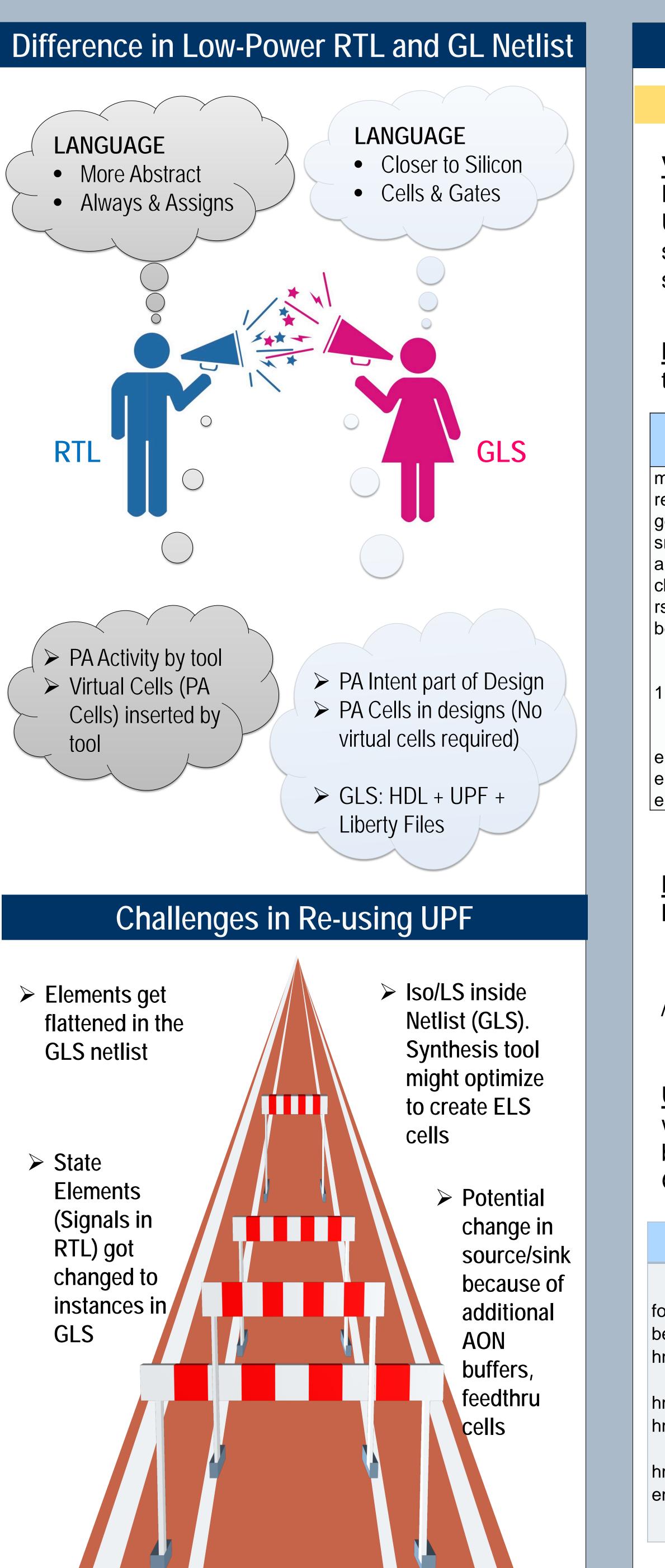

## Writing Reusable UPF

Hier-Path Related Issues in RTL Vs GLS UPF

**Vector signal in UPF** : Writing consistent UPF Definition: reg [2:0] A

Usage:

set\_retention –elements  $\{A\} >> X$ set\_retention -elements { A[0] A[1] A[2] } >>

**Hier-path scope difference** : Recommendation is to write the elements in the gate-level UPF form

| DTL ototo                                                                                                                                                                                                       | CI Stata                                                     |                                                                                       |                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| RTL state<br>element                                                                                                                                                                                            | GL State<br>Element                                          | GL UPF                                                                                | RTL UPF                                                                      |

| nodule dft()<br>eg srpg_flp1;<br>jenerate begin :<br>irpg<br>ilways@(posedge<br>ilk or negedge<br>st_t)<br>begin<br>if(!rst_t)<br>srpg_flp1 <=<br>'b0;<br>else<br>srpg_flp1 <=<br>enable;<br>end<br>endgenerate | module srpg ()<br>srff_dff<br>srpg_flp1 ();<br><br>endmodule | <pre>set_retention ret1 \   -domain pd \   -elements {dft_inst/sr pg/srpg_flp1}</pre> | <pre>set_retention ret1 \ -domain pd \ -elements {dft_inst/srpg _flp1}</pre> |

Hier-path separator "." : Separate the generate hierarchies with "." instead of "/"

GLS RTL >> /tb/top/gen[0]/mid\_inst >> /tb/top/gen[0].mid\_inst

**<u>UPF "find\_object"</u>**: Use find\_object command wherever possible, since it supports wildcard based search also, so a little change of a name in GLS would not be a problem for RTL UPF.

| RTL                                                                                                                                  | GLS                                                                                    | RTL UPF                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| or(i=0;i <num;i=i+1)<br>oegin:cfg_gen<br/>am_cfg<br/>am_cfg1_mem1();<br/>am_cfg1_mem2();<br/>am_cfg1_mem2();<br/>end</num;i=i+1)<br> | hm_cfg<br>\cfg_gen[0].hm_cfg1_<br>mem1();<br>hm_cfg<br>\cfg_gen[0].hm_cfg1_<br>mem2(); | set ret_exclude_list [<br>join [find_objects . –<br>transitive true –pattern<br>*hm_cfg1_mem* -<br>object_type instance] ] |