#### February 28 – March 1, 2012

#### Register This! Experiences Applying UVM Registers

by

Kathleen Meade Verification Solutions Architect Cadence Design Systems

## cādence<sup>™</sup>

#### **Register Package: Motivation**

- Almost all devices have registers

- Hundreds (even thousands) of registers is not uncommon

- In verifying a DUT, one needs to control, observe and check register behavior

- Randomize a configuration and initialize register values

- Execute transactions to write/read registers and memories

- Check registers and compare to a reference model

- Collect coverage of device modes

- Much of the DUT configuration is done at the register level!

#### UVM\_REG

- UVM\_REG is the register and memory package that is included in UVM

- Streamlines and automates register-related activities

- Used to model registers and memories in the DUT

#### • Features

- Built on top of UVM base classes

- Access APIs to write, read, update, peek, get reg values

- front-door and back-door access to registers and fields

- Hierarchical architecture

- Built-in sequences for common register operations

## Configuring the DUT with uvm\_reg

#### **Register Monitoring and Checking**

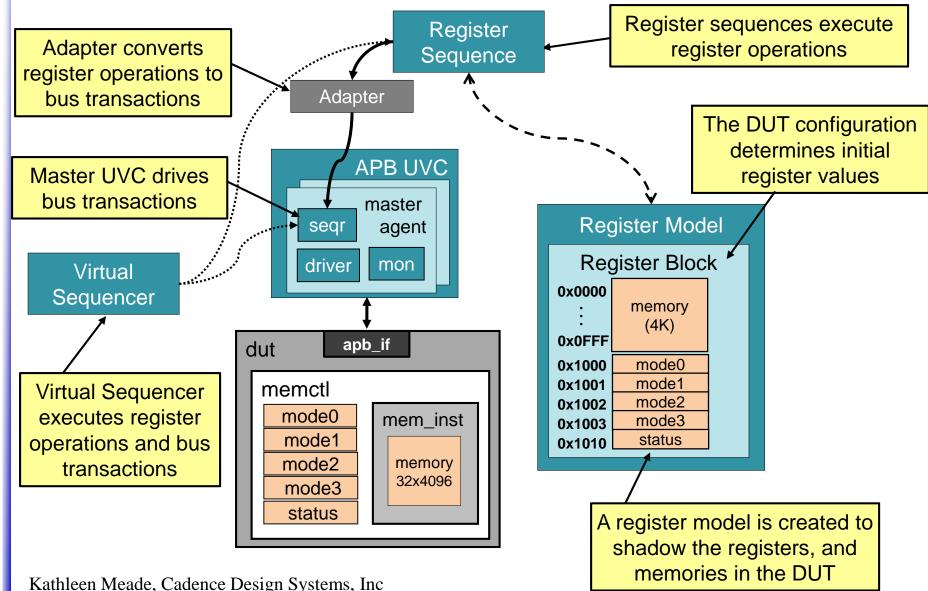

#### **The Register Model**

- Defines fields, registers, register blocks and memories for the DUT

- Includes attributes for registers and register fields (size, reset value, compare mask and access)

- Also tracks the expected values for checking

- Register operations are used for register-related stimulus

- Separating register operations from bus protocols

- Don't need to learn protocol-specific details

- Can easily change underlying protocol

- Registers and blocks can be reused within and between projects

- Configuration sequences can be packaged and reused

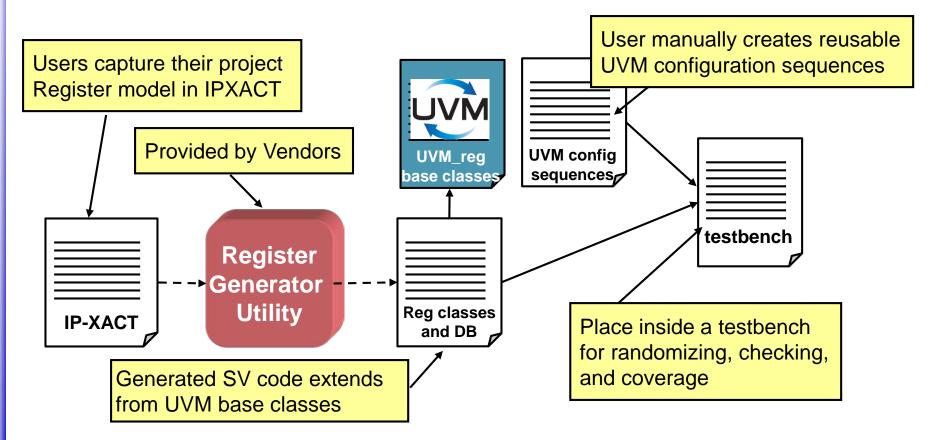

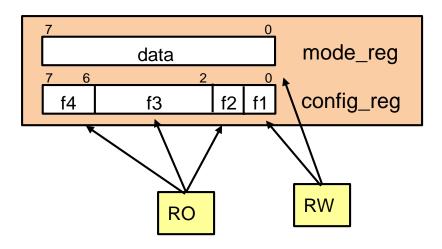

#### Creating the UVM\_REG Model Following the IP-XACT Hierarchy

• IP-XACT is the Accellera XML standard format to capture the register model (driven by the IPXACT sub-committee)

mode\_reg

config\_reg

0

f2 | f1

#### **IP-XACT Register Format (XML)**

<spirit:register> <!- CONFIG REGISTER -->

<spirit:name>config\_reg</spirit:name>

<spirit:addressOffset>0x0010</spirit:addressOffset>

<spirit:size>8</spirit:size>

<spirit:reset> <spirit:value>OxOO</spirit:value>

<spirit:mask>Oxff</spirit:mask> </spirit:reset>

<spirit:field> <!- FIELD DEFINITIONS -->

<spirit:name>f1</spirit:name> <spirit:bitOffset>0</spirit:bitOffset> <spirit:bitWidth>1</spirit:bitWidth> <spirit:access>read-write</spirit:access>

```

</spirit:field>

```

```

<spirit:field> <spirit:name>f2</spirit:name>

<spirit:bitOffset>1</spirit:bitOffset>

<spirit:bitWidth>1</spirit:bitWidth>

```

```

<spirit:access>read-only</spirit:access></spirit:field>

```

Vendor extensions can be used in the XML file to capture additional register and field dependencies (backdoor path, constraints or coverage info)

data

f3

f4

2

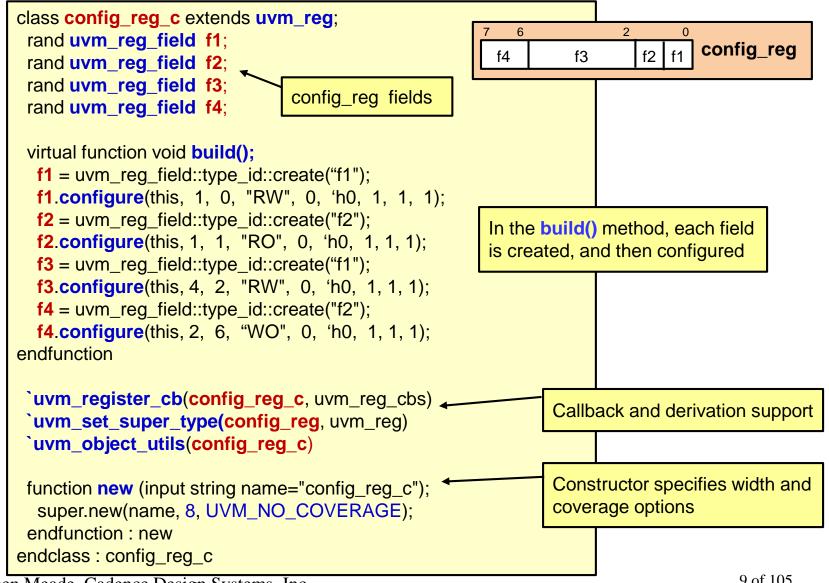

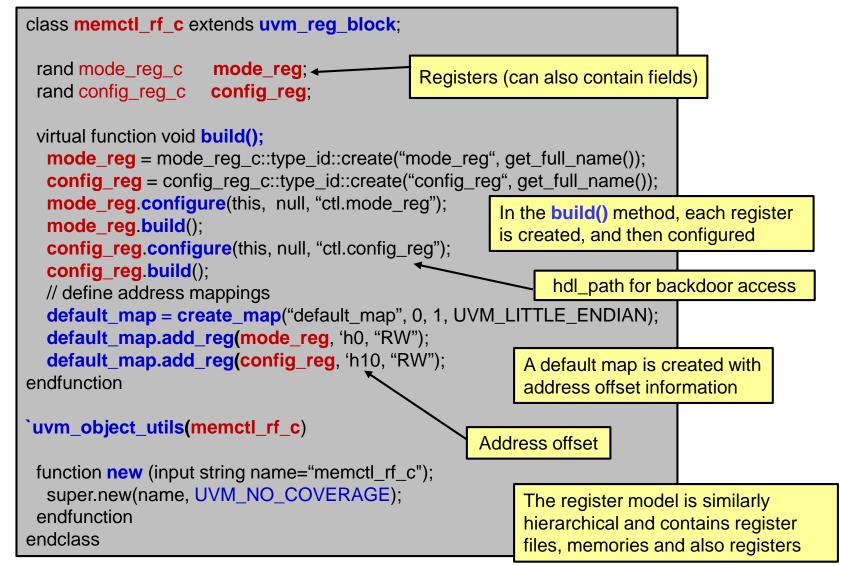

#### **Generated Register Definition**

#### **Register File/Model Declaration**

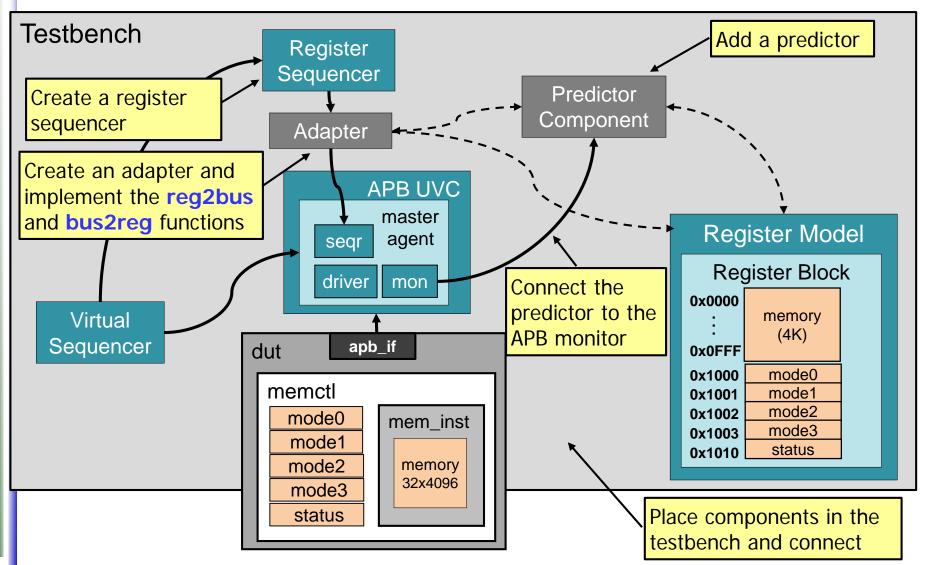

#### **Instantiation and Hook-up**

#### **Accessing the Register Model**

- Each *register field* holds three copies of data:

- Mirrored: What we think is in the HW

- Value: A value to be randomized

- <u>Desired value</u>: A desired value for the field for reference and comparison

- Has an associated access policy (RW, RO, WO, W1C, etc)

# Access APIs for Registers, Fields and Memories

| write()/read() | Write/read immediate value to the DUT                                                                                                                                                                                      |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| set()/get()    | Sets or gets desired value from the register model                                                                                                                                                                         |

| randomize()    | Randomizes and copies the randomized <u>value</u> into the <u>desired</u> <u>value</u> of the <u>mirror</u> (in post_randomize())                                                                                          |

| update()       | Invokes the <b>write()</b> method if the <u>desired value</u> (modified using <b>set()</b> or <b>randomize()</b> ) is different from the <u>mirrored</u> value                                                             |

| mirror()       | Invokes the <b>read()</b> method to update the <b>mirrored</b> value based<br>on the read back value. Can also compare the read back value<br>with the current <b>mirrored</b> value before updating it. (for<br>checking) |

Use UVM\_BACKDOOR mode to directly access the DUT (via HDL path)

randomize(), update() and mirror() can be called on a container (block) too

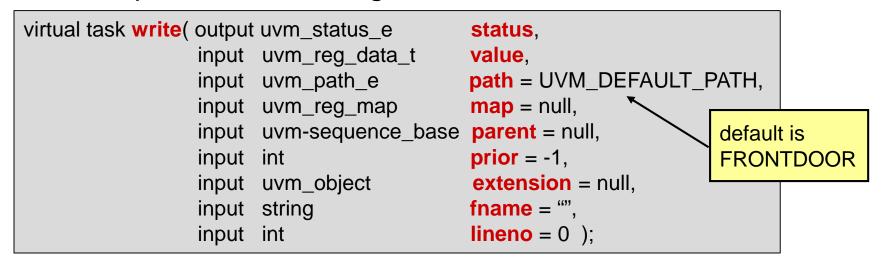

### UVM\_REG write() API

• An example of the task signature for write is:

#### • Usage of write() inside a sequence looks like this:

model.block.mode\_reg0.write(status, 8'h34, UVM\_BACKDOOR, .parent(this)); model.block.config\_reg.write(status, 8'h20, UVM\_FRONTDOOR, .parent(this));

> bound by name instead of position

### Configuring Your DUT Using uvm\_reg

- Use the register database API to configure the DUT and update the register model

- To maximize automation and reuse use UVM sequences for configuration

- Advantages:

- Registers are great candidates for vertical reuse

- Sequences are the most natural way for UVM users

- Leverage built-in sequence capabilities: grab, lock, priorities, etc

- Easy system-level control via virtual sequences

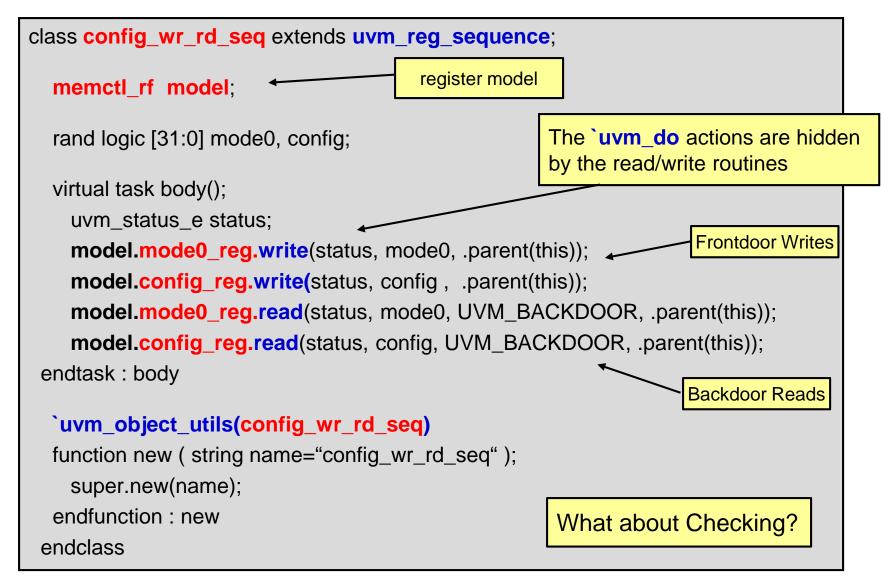

#### **Configuration Sequences**

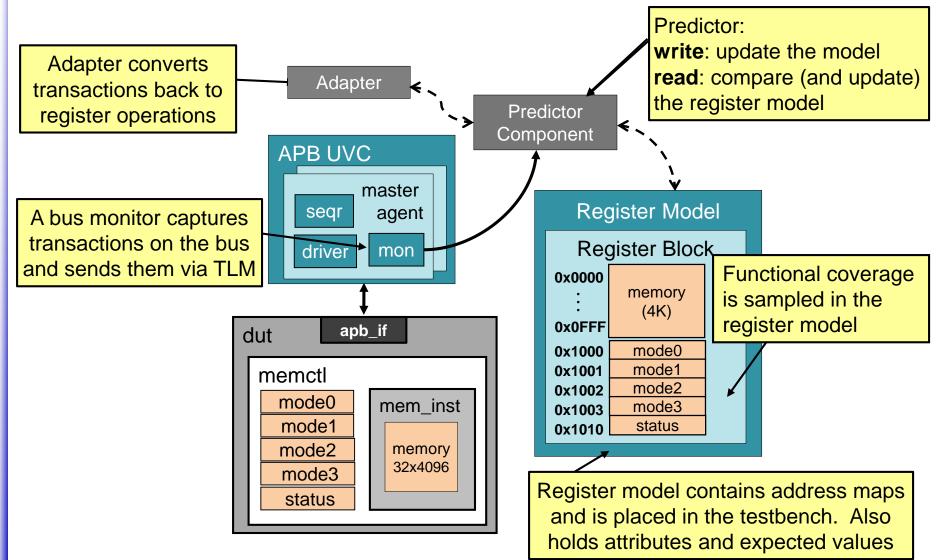

#### **Checking for Correctness**

- Register checking and coverage is useful

- Register field values map to DUT operation modes and designers can observe the combinations of configurations that were exercised

- Consistency checking against a mirror/reference can identify errors regardless of the testbench implementation or DUT complexity

- Where do I place the monitoring logic? Directly in sequences where I want to check? or a passive monitor?

- UVM\_REG supports two types of monitoring: implicit and explicit

### **Checking: Implicit Monitoring**

- Implicit monitoring

- The sequence automatically updates the desired value

- Easy to set up but dangerous, not reusable (no support for passive), no support for other activity on the bus

- To activate: my\_reg\_model.default\_map.set\_auto\_predict(1)

- Use the mirror() method n a sequence body and enable the check:

// Read and check the mode register via back-door access

model.mode0\_reg.mirror(status, UVM\_CHECK, UVM\_BACKDOOR, .parent(this));

model.mirror(status, UVM\_CHECK, UVM\_FRONTDOOR, .parent(this));

Can also **mirror()** the register model or any sub\_container

## **Checking: Explicit Monitoring**

- Explicit Monitoring:

- The bus monitor and a predictor are used for monitoring and checking

- Much safer and more reusable

- Checking logic needs to be added to module UVC

- Separation of the injection and monitoring paths is one of the basic concepts of UVM

- We recommend passive monitoring independent capture of transactions on the bus that can be recognized as bus operations.

- Note: It's OK to have a check in a sequence body if that is the purpose of the sequence, but want to be able to do independent checking too

### Coverage Model in UVM\_REG

- The register model can include functional coverage

- Details of coverage points, bins are left to generator

- Coverage model can be very large, so instantiate/cover only what needs to be covered

- UVM\_REG pre-defined coverage models

- Register bits (all bits have been read/written)

- Address maps (addresses have been accessed)

- Field values (specific values are covered)

- A register generator creates a coverage model for you.

- Uses IP-XACT vendor-extensions to enable coverage at the field-level

- Also allows command-line option to enable/disable register-level functional coverage generation

#### **Questions?**

## **Thank You!**