### RegAnalyzer -A tool for programming analysis and debug for verification and validation

#### **Abstract**

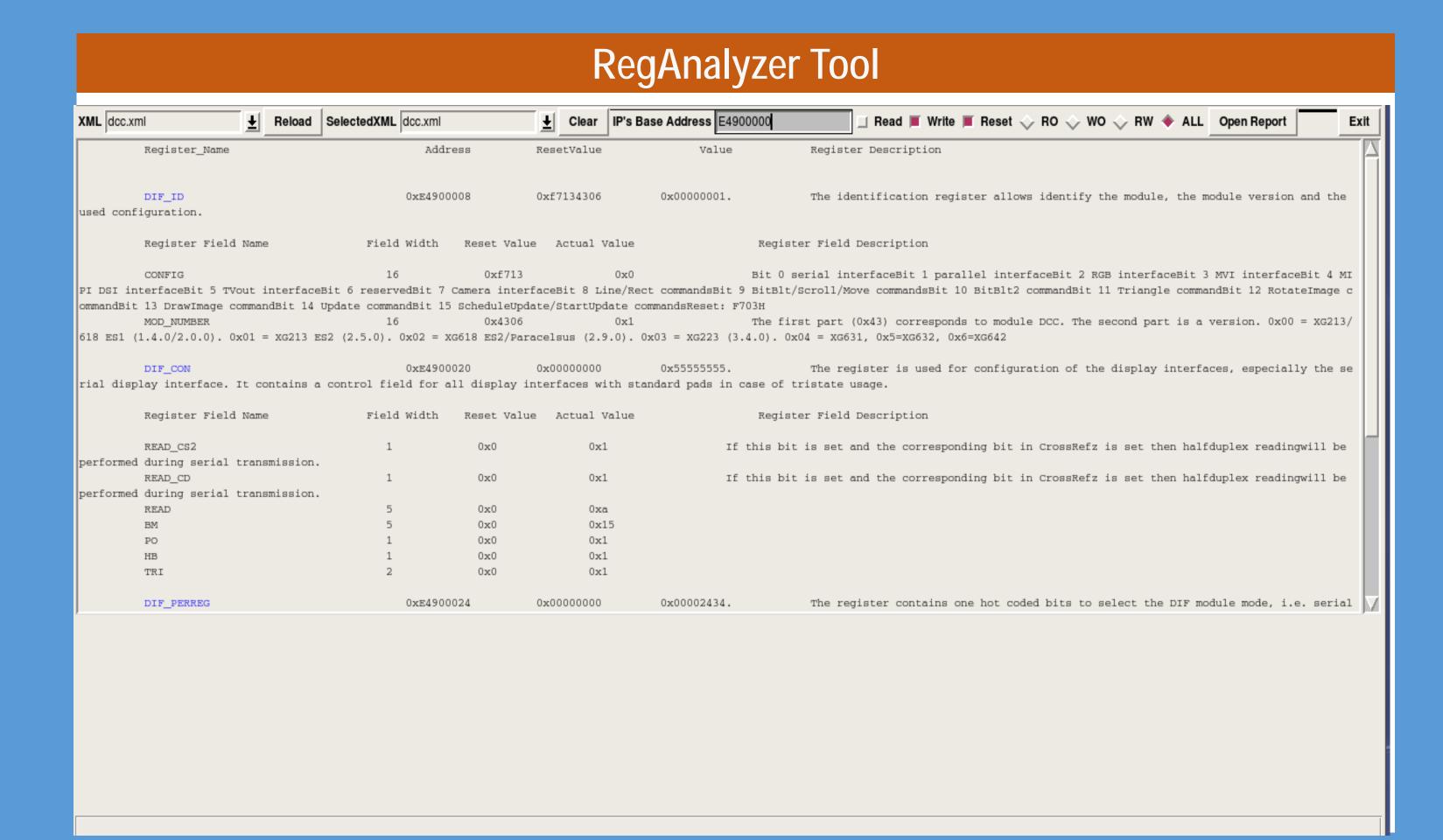

As the technology node is shrinking, more and more IPs are getting integrated in single System-on-chip. In the System-on-chip, verification is getting more tedious, time consuming and challenging task. Based on case study on different internal and third-party IP's, realized that there are no mechanism nor internal / external tools available for doing the quick debug by understanding the test cases and its programming. Verification Engineers are putting manual effort to understand the IP programming in the test cases and there is no direct way to map the register programming to the Technical Reference Manual / Programmers model. This poster presents a tool RegAnalyzer which resolves this problem.

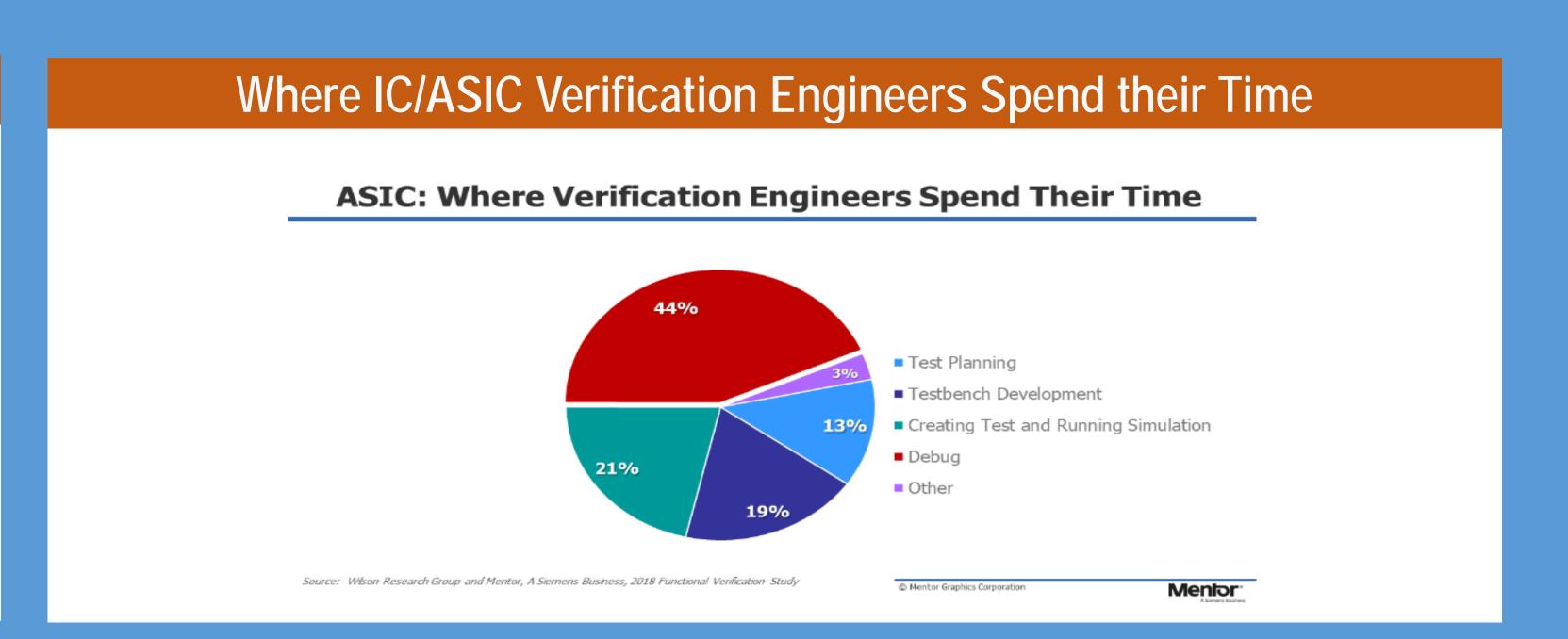

## ASIC: Percentage of Project Time Spent in Verification 2012: Average 55% 2014: Average 57% 2016: Average 54% 2018: Average 53% 2018: Aver

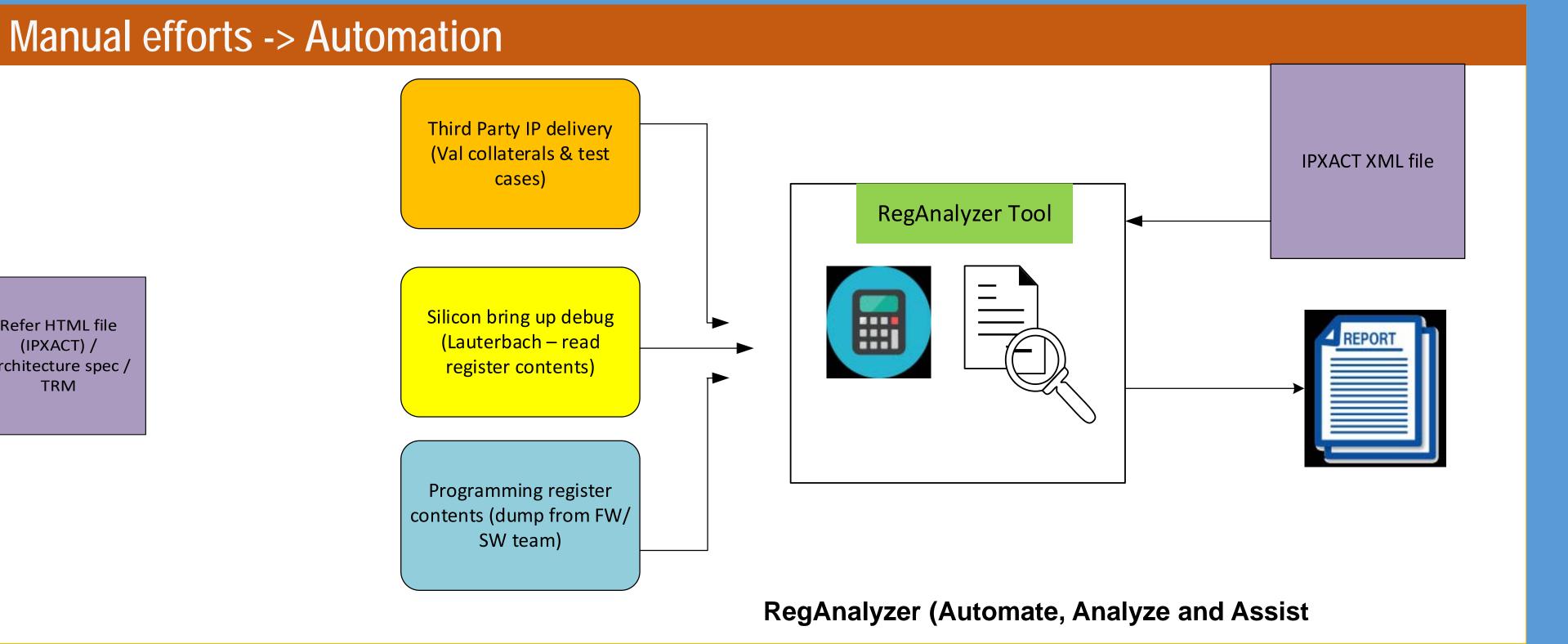

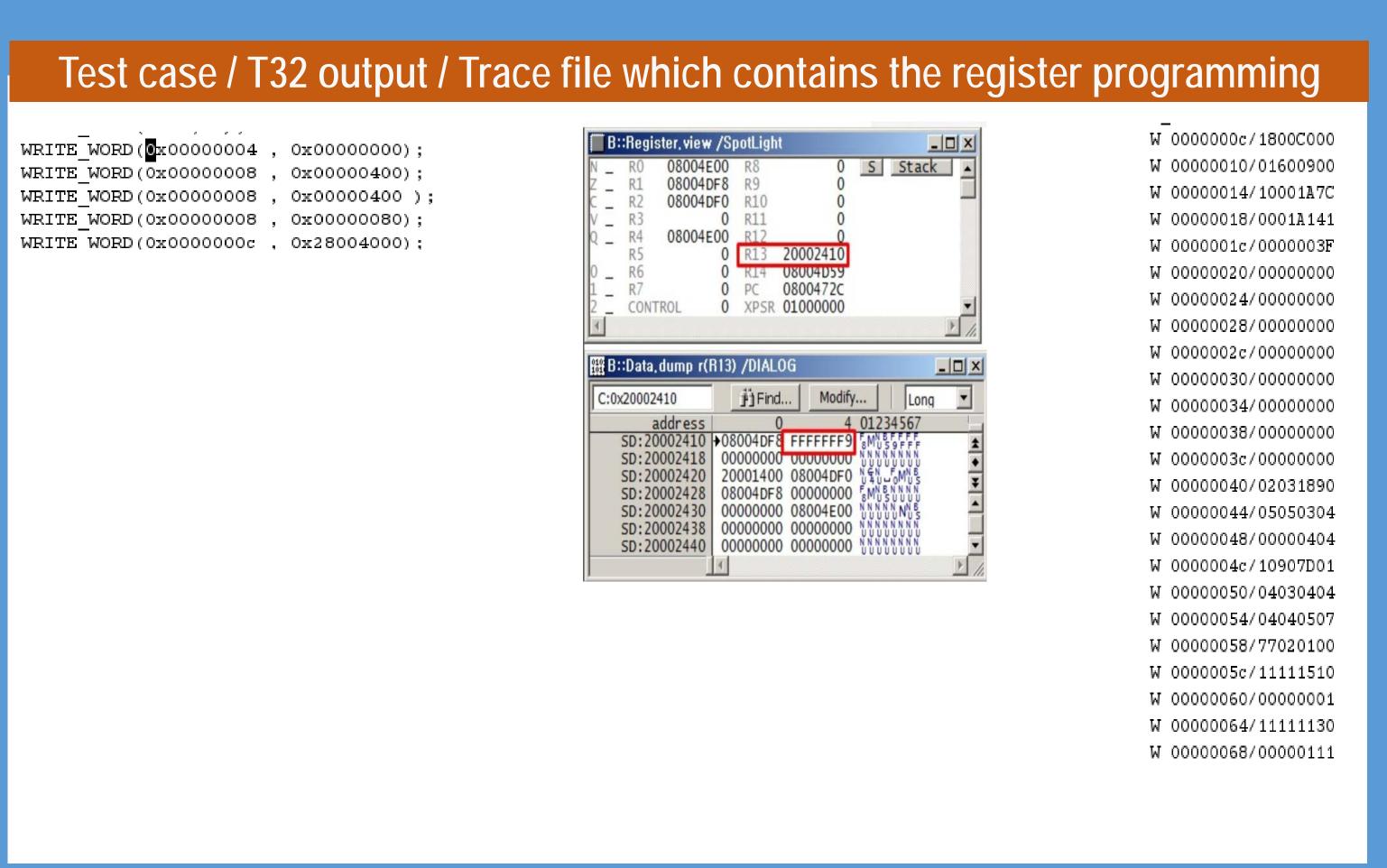

#### Third Party IP delivery (Val collaterals & test cases) Silicon bring up debug (Lauterbach – read register contents) Refer HTML file Decode the (IPXACT) / register field Architecture spec / values Programming register contents (dump from FW/ SW team) What is verified in this IP's test case? What is programmed? How do I debug? Manual efforts in Verification & Validation debug

# RegAnalyzer Results COMPLEX MEDIA IP (30 TC) MMU IP (12 TC) 0 2 4 6 8 10 12 14 16 RegAnalyzer (No of days) Manual (No of days)

#### Conclusion

RegAnalyzer is an effective GUI tool which will help in day-to-day verification activities, reduce the manual efforts drastically and save debug time. This tool will help during the design pre-silicon verification and post silicon validation to understand the register programming and its details. By using all the different features supported by this tool, verification and validation Engineers can make tremendous progress and reduce the overall debug time during Silicon-On-Chip development.