Probing UPF Dynamic Objects: Methodologies to

**Build Your Custom Low-Power Verification Platform**

Progyna Khondkar

# SYSTEMS INITIATIVE

Mentor Graphics, A Siemens Business

## **OUTLINE & CONTRIBUTION**

- This paper proposes a completely new low-power verification methodology

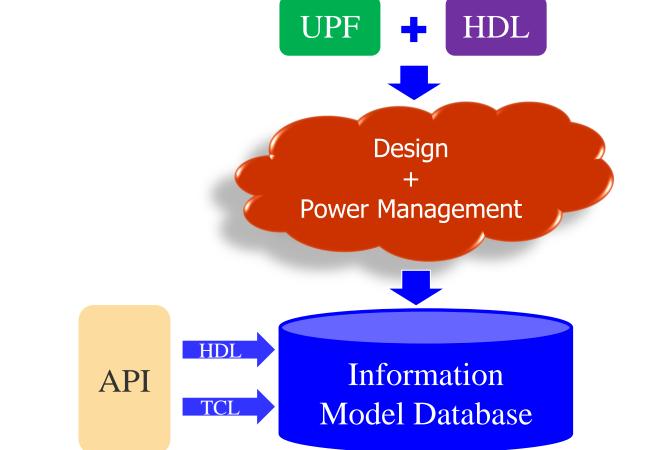

- On the key concepts of low-power (UPF) information model (UPFIM)

- Allows to query any dynamic properties of UPF objects -

- like continuously probe ON, OFF status of a power domains (during elaboration steps)

- Through Tcl API and passed the objects information on to

- Appropriately instantiated SV API based design codes.

- Example: Tcl API can be used on the simulation execution fly

- To populate any attributes for low-power SystemVerilog checker modules

- Already quarried and bound during elaboration steps into RTL design through

## **UPF & LOW POWER (TERMINOLOGIES?)**

DESIGN AND VERIFIC

CONFERENCE AND EXHIBITION

ELRDPE

- UPF: Unified Power Format/IEEE 1801- Not just power spec language

- Full set for verification, architecting & implementing low power artifacts on any design

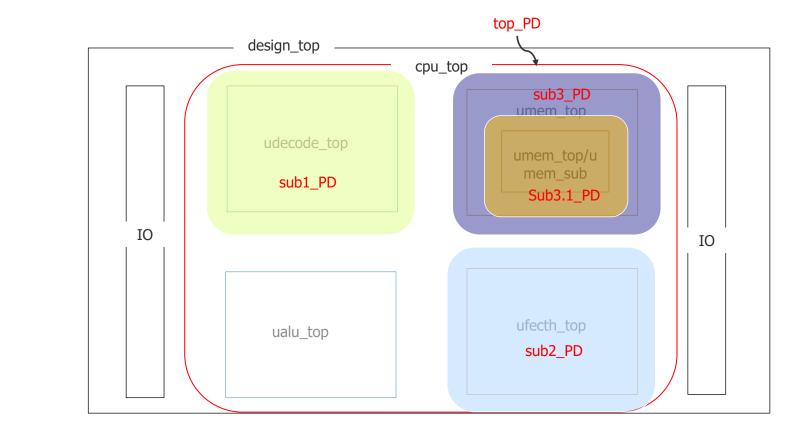

- UPFIM: A database with UPF objects processed in phases

- 5 phases before UPF objects on a design can be quarried

- bind\_checker: A mechanism of custom low power checker

- Done by embedding the binding of the design and checker within the UPF/Tcl file

- Provides consolidated verification, messaging & debug environment and

- Simulator access all instances of a target design with a custom checker

- bind\_checker assertions are distinctively different from SVA

- They can access all the UPF objects i.e. UPF power supply, power states etc. through Tcl query or HDL native API available in UPFIM.

#### RESULTS

- Complete user perception that allows to query UPFIMDB

- On simulation fly & populate any attributes of user low-power SV checker modules

- That are bound in elaboration steps into RTL design through UPF bind\_checker.

| Phases  | UPF Processed on Designs in each Phases                                                                                            |

|---------|------------------------------------------------------------------------------------------------------------------------------------|

| Phase 1 | Read UPF specifications                                                                                                            |

| Phase 2 | Build UPF model                                                                                                                    |

| Phase 3 | Recognize the implemented UPF and process simulation controls                                                                      |

| Phase 4 | Apply UPF model to the design, including any checkers introduced by the UPF <b>bind_checker</b>                                    |

| Phase 5 | Query UPF model through Tcl and HDL API based quarry. This phase also implements checkers quarries resulting from the bind_checker |

• At design optimization (i.e. vopt)

•

• Simulator leverages consolidated UPF flow

### RESULTS

## Regular Power Management UPF `dut\_top.upf' create power domaon PD -elements {<list of elements e.g.> top vl top vl1}

#### . . . . . . . . . . *## Retention Strategy*

53

46 set\_retention pd\_retention \ -domain pd -save\_condition {!UPF\_GENERIC\_CLOCK && sc} \ -restore condition {UPF GENERIC CLOCK && !UPF GENERIC ASYNC LOAD && rc} ## Regular UPF Commands/Options ## For e.g. defining other PD, PD's supply set, association, ## Power state etc. ## Binding design module, Regular UPF and Custom Retention Checker through UPF bind\_checker bind checker \$instance name -module checker retention -bind to tb -ports \$ports list ## Utilization of UPF Tcl Query Functions in Consolidated UPF flow foreach RET\_STRATEGY [upf\_query\_object\_properties \$PD -property upf\_retention\_strategies]

{set ret\_save\_signal [upf\_query\_object\_properties \$RET\_STRATEGY -property upf\_save\_signal] set ret\_sav\_sig\_port [list sav\_sig [upf\_query\_object\_properties \ set **ret\_restore\_condition** [upf\_query\_object\_properties \$RET\_STRATEGY -property upf\_restore\_condition] set ret res cond port [list res cond \$ret restore condition] set RET\_STRATEGY\_NAME [upf\_query\_object\_properties \$RET\_STRATEGY -property upf\_name] set RET\_QUERY [query\_retention \$RET\_STRATEGY\_NAME -domain \$PD -detailed] array set RET DETAILS [join \$RET QUERY]

set RET CLK \$RET DETAILS(upf generic clock)

| Consist of UPF commands & UPFIM Tcl API in single UPF file                                                                                                                                                                                                                                                                            | <pre>set ret_clk_port [list ret_clk \$RET_CLK] set ports_list {} lappend ports_list \$ret_sav_sig_port \$ret_res_sig_port \$ret_sav_cond_port ## Printing Useful Information for the Retention Strategy ## Output for the Retention for</pre> |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>## Custom SV Checker 'ret_checker.sv'<br/>import UPF::*;<br/>module checker_retention(sav_sig, res_sig, sav_cond, res_cond, ret_clk);<br/>input sav_sig, res_sig;<br/>input upfExpressionT sav_cond;<br/>input upfExpressionT res_cond;<br/>input ret_clk;<br/>wire clk;<br/>assign #1step clk = ret_clk;<br/>property p1;</pre> | <pre>puts "RET INFO STRATEGY: \$RET_STRATEGY\n PATH: \$ret_path\n type: \$cell_type\n"}  ## Useful Information for the Retention Strategy Loading module checker_retention STRATEGY: /tb/pd.pd_retention1 PATH: /tb/pd.pd_retention1 type: upfRetentionStrategyT ## Assert Property p1 and p2 # ** Error: (vsim-8906) QPA_RET_SEQ_ACT: Time: 36 ns, clock toggled during retention period for retention element(s) in scope '/tb/top_vl': q # File: ~/test.upf, Line:46, Power Domain:/tb/pd # 37 pwr= 1, ret= 1, ret1= 0, clk= 1, rst= 0, d=1, q_vl= 01 01, q_vl1= 01 # # &gt;&gt;&gt; 37 Save not executed</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| endmodule                                                                                                                                                                                                                                                                                                                             | # >>> 37 Restore success                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## CONCLUSIONS

- Propose methodology allows to create LP checker

- User can readily utilize object passing by query function,

- Hierarchical references as well with or without native SV HDL representations.

- Recognize UPF 3.1 LRM lack clarification on coordinating

- **upfExpressionT** (creates relational objects to captures Boolean expressions for save, restore) with

- Retention strategy record field or UPF generics, like the UPF\_GENERIC\_CLOCK, UPF\_GENERIC\_DATA

- Specifically UPF mirror object function and *bind\_checker* for generic requires clarification IEEE 1801.

[1] Progyna Khondkar, "Low-Power Design and Power-Aware Verification", Hard Cover ISBN: 978-3-319-66618-1, October, 2017, Springer International Publishing.

REFERENCES

[2] Design Automation Standards Committee of the IEEE Computer Society, "IEEE Standard for Design and Verification of Low-Power, Energy-Aware Electronic Systems", IEEE Std. 1801<sup>™</sup>-2018.

[3] Progyna Khondkar, et al., "How UPF 3.1 Reduces the Complexities of Reusing Power Aware Macros" March, DVCon 2020."

[4] Progyna Khondkar, et al., "Low Power Coverage: The Missing Piece in Dynamic Simulation", February March, DVCon 2018.

[5] Progyna Khondkar, et al., "Free Yourself from the Tyranny of Power State Tables with Incrementally Refinable UPF", February March, DVCon 2017.

[6] Design Automation Standards Committee of the IEEE Computer Society, "IEEE Standard for Design and Verification of Low-Power, Energy-Aware Electronic Systems", IEEE Std. 1801-2015, 5 December 2015.

- Proposed and implemented a novel methodology that paved the way to continuously probe UPF dynamic objects and

- Allows to build custom low-power verification portfolio on existing low-power \_\_\_\_ simulation platform.

- If carefully designed, these custom checkers can be reused across any low-power projects.

© Accellera Systems Initiative