### Practical Issues in Implementing Fast and Accurate SystemC-Constructed Virtual Platform Simulation

Authors: Yu-Fu Yeh<sup>1,2</sup> and Chung-Yang (Ric) Huang<sup>2</sup> Affiliation: <sup>1</sup>ICL @ ITRI; <sup>2</sup>GIEE @ NTU Presenter: Yu-Fu Yeh

### Outlines

- Introduction

- Preliminaries

- Simulation overhead in virtual platform simulation

- Synchronization reduction by an asynchronous discrete event simulation scheme

- QuteVP+ Implementations:

- QuteVP+ engine

- QuteVP+ utility library

- Experimental Results

- Conclusions

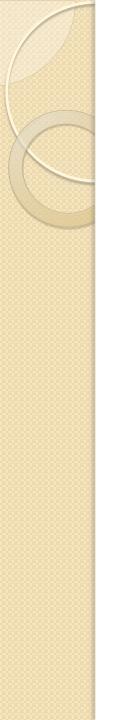

### What is virtual platform simulation

- A software-constructed hardware simulation platform

- Hardware components are constructed by software language (e.g: SystemC)

- Software program can be executed on the processor model (e.g: Instruction set simulator, ISS)

- Usually contains everything for a system

- Hardware: processor, bus, memory, DMA...

- Software: OS, firmware, drivers, embedded programs

- Objectives:

- System design optimization, architecture exploration, system-level verification

# The problem in virtual platform simulation

A trade-off between simulation efficiency and simulation accuracy

V.S

- Simulated models with higher abstract levels

- better simulation efficiency

- E.g. functional simulation

- Simulated models with lower abstract levels

- More accurate outcome

- E.g. cycle accurate simulation

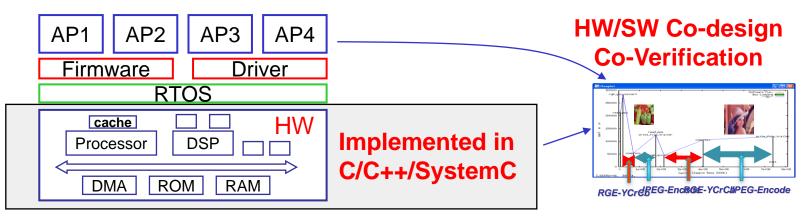

#### Introduction

Our experience of SoC-based virtual platform simulation

- m13 Version

- 2007.05 Finished

- Cycle Accurate

- Pin Accurate

- m17 Version

- 2008.05 Finished

- Cycle Accurate

- OSCI TLM 1.0

- About 12.0 KIPS About 27.5 KIPS UNACCEPTABLE SIMULATION SPEED

### Introduction

QuteVP+, a simulation framework, is proposed to follow our proposed simulation scheme to conduct fast and accurate SystemC-constructed virtual platform simulation

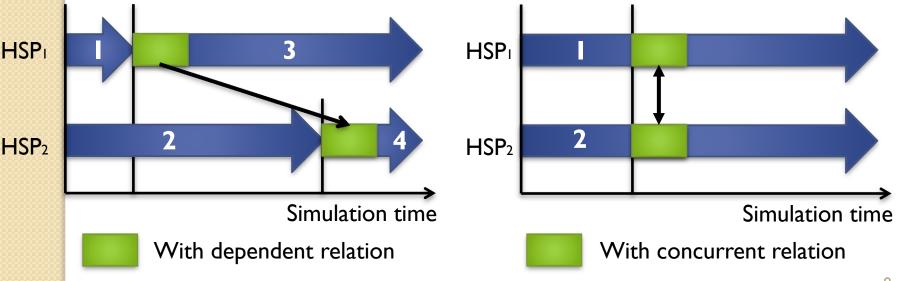

Virtual platform simulation must consider dependent and concurrent relations among hardware components

Schedule Hardware Simulation Process (HSP) in a proper chronological order

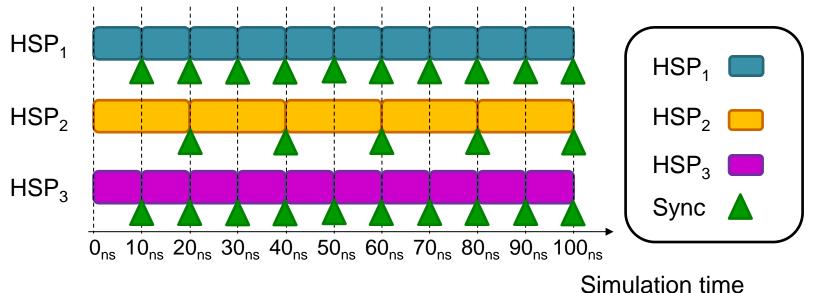

To accurately mimic the concurrent hardware behavior, SystemC simulator schedules the HSPs created by SC\_METHOD, SC\_THREAD with synchronous discrete-event scheme (Sync-DES), or called clock-step simulation scheme (CSSM)

To schedule HSPs, SystemC kernel evokes synchronization (thread context switches), during simulation

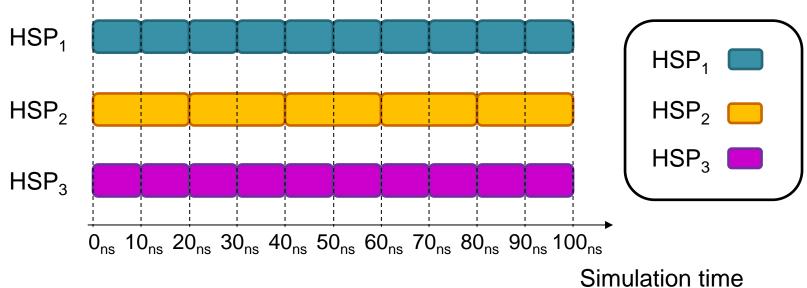

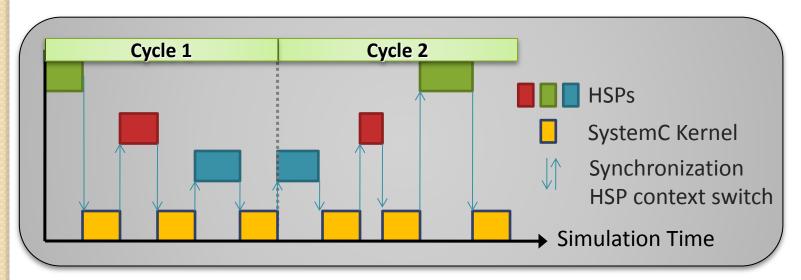

### • Each module gets scheduled one or multiple times in one clock cycle

- Using serial simulator to mimic concurrent behavior

- Synchronizing HSPs with big simulation overhead

Context switches across one clock cycle over simulation time chart

#### What's the problem?

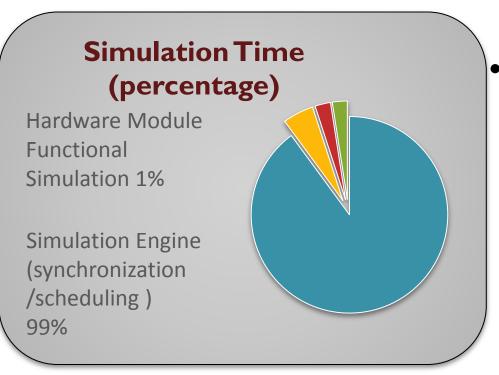

**Ob**servation

- The biggest bottleneck of SystemC simulation is in the simulation kernel

Serious simulation overhead

- Context Switches

- Scheduling

- Data copy

Virtual platform simulation time profiling

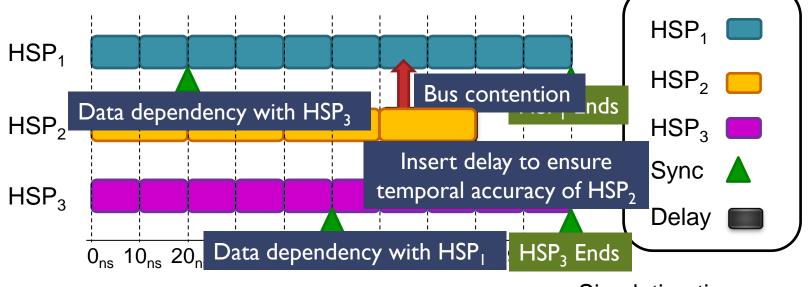

### Asynchronous discrete even simulation for synchronization reduction

In contrast to sync-DES, asynchronous discrete event simulation (async-DES) scheme benefits synchronization reduction

Simulation time

# Asynchronous discrete event simulation (async-DES)

- In the virtual platform simulation with "async-DES", there are two requirements

- A synchronization checking mechanism to

"avoid dependency violation"

- A timing reconstruction technique to "maintain temporal accuracy"

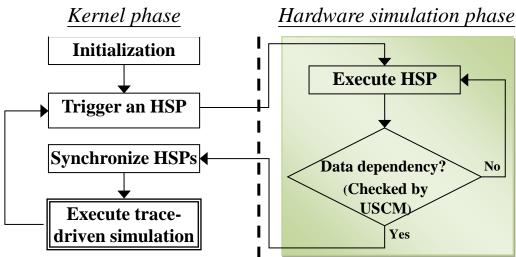

# Synchronization reduction with our proposed simulation scheme

This work is based on our proposed simulation scheme <sup>[1]</sup> with USCM<sup>[2]</sup> and Trace-drive simulation to conduct fast and accurate MPSoC virtual platform simulation

[1]:Y.F.Yeh, H.S. Lin and C.Y.(Ric) Huang, "A Fast and Accurate MPSoC Virtual Platform Simulation with Ultra Synchronization Checking Method and Trace-driven simulation", accepted by IEEE transactions of Computer-Aided Designs of Integrated Circuits and Systems, 2013, Jan.

[2]:Y.F.Yeh, C.Y. (Ric) Huang, C.A. Wu, and H.S. Lin, "Speeding Up MPSoC Virtual Platform Simulation by Ultra Synchronization Checking Method", in Proc. IEEE Design Automation and Test in Europe (DATE), Mar 211, pp. 1-6.

- Goal:

- Realize the introduced async-DES scheme on SystemC-Constructed virtual platform simulation

- Difficulties

- The simulation scheme in SystemC follows Sync-DES (Clock-step simulation scheme)

- Modifying simulation scheme, the simulation must solve issues in "compatibility" and "adaptability"

- Compatibility

- Ensure the replacement of simulation scheme without affecting the primitive SystemCdefined functions

- E.g. the functions, such as event notify(), wait() is relevant to the scheduling behavior

- Easy to use

- Consider the convenience to adapt the parallel out-of-order execution approach on SystemC-Constructed virtual platform

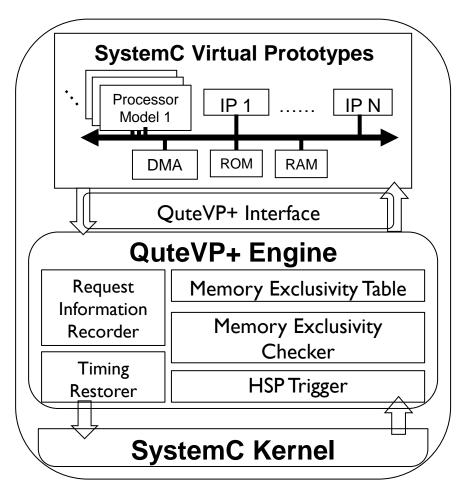

QuteVP+ Overview

#### Use QuteVP+ interface to connect hardware model and QuteVP+ Engine QuteCore **Static** DMA processor Memory qvp+ Interface Memory **Bus** qvp+ Interface qvp+ Interface Map qvp+ Interface qvp+ Interface qvp+ Interface Master port

ASIC

Slave port

Dynamic

Memory

Input

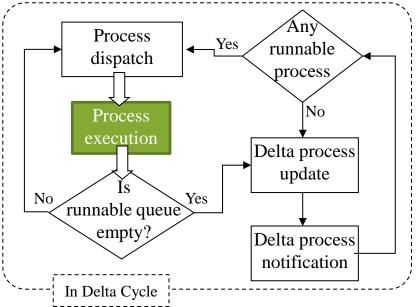

- QuteVP+ creates an independent process to manipulate HSPs by out-of-order execution

- Delta cycle scheduling

- HSPs use timeless wait function for synchronization

- QuteVP+ engine enables async-DES scheduling in each delta cycle

- Record simulation traces of each HSP for trace-driven simulation

- Maintain dependency relation

- Reconstruct accurate simulation time

- Process notification

- QuteVP+ utility library

- While requesting a memory access, an HSP can use our utility library to check data dependency

```

#include <QuteVP_Utility.h>

.... // QVP+ communication channel inheritance

void ARM_ISS::send_request() {

// replace TLM communication function call, e.g. m_master_port->nb_put(mReqs);

// by calling data-dependency checking function

// and execute synchronization if necessary

if (QuteVP_Engine->DataDependencyChecker(mReq, mResp)) {

wait(sync_ok_event);

QuteVP_Engine->RequestTransmitter(mReq, mResp);

}

if (mReq.get_command()==MEM_READ)

M_resp_data = mResp.get_data();

}

```

- QuteVP+ utility library

- RequestTransmitter() performs "direct data access" to reduce data copy

#include <QuteVP\_Utility.h>

// Using targetID mapping to the corresponding get\_request function

qvp\_response Qutevp\_Engine::RequestTransmitter(qvp\_request& mReq) {

targetAddr = mBeg\_get\_address();

targetAddr = mReq.get\_address();

targetID = findIDfromMemMap(targetAddr);

return pHSP[targetID].HSPptr()->get\_request(mReq);

// Calculate the request address to seek the target ID

unsigned int pSysc::findIDfromMemMap(unsigned int& Addr) {

return TargetID

....

- We compare the simulation efficiency of MPSoC virtual platform simulation where QuteVP+ performs with different simulation approaches

- CSSM: Clock-Step Simulation Method, the synchronous discrete event simulation scheme that the primitive SystemC follows

- **USCM**: USCM, the asynchronous discrete event simulation scheme in our previous work

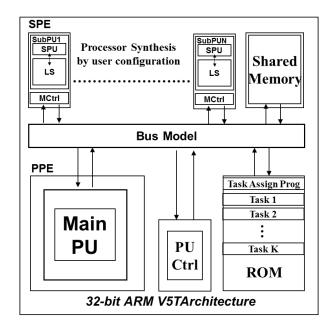

- We construct an CELL-Like MPSoC virtual platform and JPEG encode and sparse matrix multiplication programs as test software cases running on the MPSoC virtual platform

- Experimental environment

- Workstation with Intel xeon CPU (qual-core\*2) 2.2 GHz, I6GB RAM

- CentOS kernel 2.6

- Virtual platform constructed with SystemC v2.2

The comparison of synchronization count (Sync-Count) with CSSM and USCM

| Sparse matrix multiplication |                                           |                                                               |                                                                       |                                        |  |  |  |  |

|------------------------------|-------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------|--|--|--|--|

| #CPU                         | #Inst                                     | Simulation Cycle                                              | Sync-Count by CSSM                                                    | Sync-Count by USCM                     |  |  |  |  |

| 1                            | 169,314,561                               | 254,261,472                                                   | 722,859,678                                                           | 28,423,967                             |  |  |  |  |

| 2                            | 121,085,896                               | 156,417,989                                                   | 460,436,669                                                           | 12,508,290                             |  |  |  |  |

| 4                            | 107,747,016                               | 124,834,536                                                   | 365,547,740                                                           | 7,564,476                              |  |  |  |  |

| 8                            | 105,501,921                               | 114,852,199                                                   | 335,037,092                                                           | 3,891,842                              |  |  |  |  |

| 16                           | 112,941,976                               | 119,699,619                                                   | 349,944,254                                                           | 2,075,848                              |  |  |  |  |

| 32                           | 135,121,633                               | 145,001,298                                                   | 419,101,187                                                           | 1,220,659                              |  |  |  |  |

| JPEG-Encode                  |                                           |                                                               |                                                                       |                                        |  |  |  |  |

|                              |                                           | JPEG                                                          | -Encode                                                               |                                        |  |  |  |  |

| #CPU                         | #lnst                                     | JPEG<br>Simulation Cycle                                      | -Encode<br>Sync-Count by CSSM                                         | Sync-Count by USCM                     |  |  |  |  |

| #CPU                         | #lnst<br>512,513,774                      |                                                               |                                                                       | Sync-Count by USCM<br>87,409,800       |  |  |  |  |

| #CPU<br>I<br>2               |                                           | Simulation Cycle                                              | Sync-Count by CSSM                                                    | , ,                                    |  |  |  |  |

| 1                            | 512,513,774                               | Simulation Cycle<br>771,969,678                               | Sync-Count by CSSM<br>2,212,558,094                                   | 87,409,800                             |  |  |  |  |

| <br>2                        | 512,513,774<br>386,970,594                | Simulation Cycle<br>771,969,678<br>507,338,577                | Sync-Count by CSSM<br>2,212,558,094<br>1,520,454,360                  | 87,409,800<br>45,790,479               |  |  |  |  |

| <br>2<br>4                   | 512,513,774<br>386,970,594<br>314,622,268 | Simulation Cycle<br>771,969,678<br>507,338,577<br>376,936,991 | Sync-Count by CSSM<br>2,212,558,094<br>1,520,454,360<br>1,093,803,850 | 87,409,800<br>45,790,479<br>21,489,726 |  |  |  |  |

Simulation speed =  $\frac{\sum_{i=0}^{n=\#CPU} \text{the number of simulated instructions}}{\text{Simulation runtime}_{\text{Simulation scheme}} (\text{sec})}$

Speedup  $Ratio_{(Scheme_A with respect to Scheme_B)} = \frac{Simulation speed_{Scheme_A}}{Simulation speed_{Scheme_B}}$

| #CPU | SMM                    |                        |               | JPEG-Enc               |                        |               |  |

|------|------------------------|------------------------|---------------|------------------------|------------------------|---------------|--|

|      | CSSM <sub>(KIPS)</sub> | USCM <sub>(KIPS)</sub> | Speedup Ratio | CSSM <sub>(KIPS)</sub> | USCM <sub>(KIPS)</sub> | Speedup Ratio |  |

| 1    | 11.4                   | 1376.5                 | 121.0         | 13.7                   | 1331.2                 | 96.8          |  |

| 2    | 16.3                   | 1121.2                 | 68.6          | 17.4                   | 1236.3                 | 70.9          |  |

| 4    | 21.7                   | 1007.0                 | 46.3          | 20.7                   | 1096.2                 | 53.0          |  |

| 8    | 32.4                   | 933.6                  | 28.8          | 29.7                   | 1043.7                 | 35.1          |  |

| 16   | 24.3                   | 824.4                  | 33.9          | 23.3                   | 901.0                  | 38.7          |  |

| 32   | 21.0                   | 682.4                  | 32.6          | 22.5                   | 747.4                  | 33.2          |  |

KIPS means "Kilo Instruction Per Second

| Rate of                 | The number of simulating processors (#CPUs) |       |       |       |       |       |  |

|-------------------------|---------------------------------------------|-------|-------|-------|-------|-------|--|

| DDC.Runtime             | I                                           | 2     | 4     | 8     | 16    | 32    |  |

| DDC.Runtime %<br>(USCM) | 0.23%                                       | 0.22% | 0.24% | 0.27% | 0.23% | 0.23% |  |

The rate of simulation runtime for data-dependency checking (DDC) with respect to total simulation runtime

### Conclusions

- QuteVP+ can performs an async-DES to reduce unnecessary synchronization and reconstruct accurate simulation time

- QuteVP+ can

- Perform the better simulation speed over 100+ times with respect to the conventional SystemC-based virtual platform

- Offer accurate simulation outcome