# Portable Stimulus Models for C/SystemC, UVM and Emulation

Mike Andrews, Mentor Graphics Boris Hristov, Ciena

# Why Portable Stimulus

- Re-writing the stimulus model for multiple environments is a big challenge

- Non SV options for constrained random have not been satisfactory

- E.g. SCV had too many limitations

- In 2014, Accellera Proposed Standard Working Group approved formation of a new standard

- Primary standard requirements:

- Self-contained

- Independent of any specific language (SV/SC)

#### **Portable Stimulus Features**

- Abstracted rule-based (declarative) description of legal stimulus scenarios

- Blend of Backus-Naur Form and algebraic constraints

- Able to be mapped to any specific verification environment:

- SystemVerilog UVM

- SystemC SCV / CRAVE

- Software driven verification

- Post-silicon validation

Backus Naur Form is a "context-free grammar"

Note: These are features of an existing portable stimulus application, not the TBD Standard

# Portable Stimulus Example

Uses existing graph-based rule language

```

rule_graph simple_protocol {

import "decls.rseg";

Interfaces here

action init, do idle;

indicate data

transfer to or from

trans tro:

the testbench

interface do trans(trans);

input state vars curr state;

Repeats can be

interface get_state(state_vars);

inside the sequence,

nested if desired

simple protocol = init repeat {

get state(curr_state)

(if {curr_state.intf == ready} do_trans(tr0))

"is

(if {curr_state.intf == busy} do idle)

choice

} :

operator

```

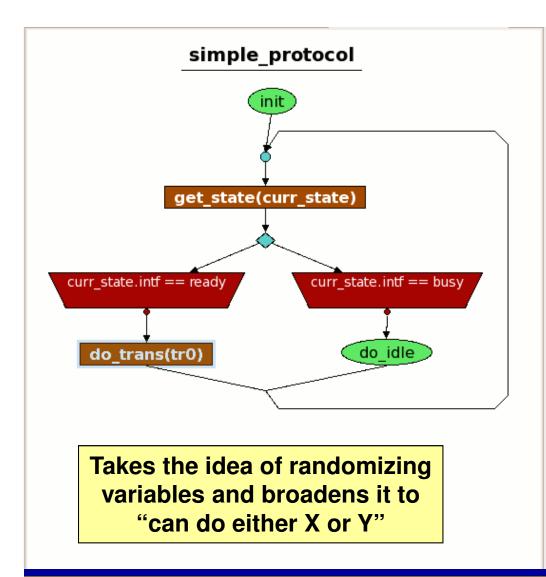

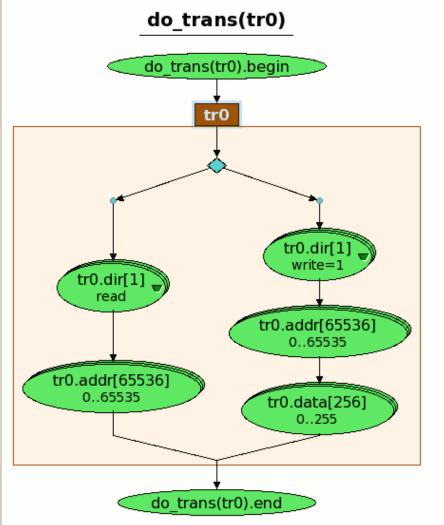

#### **Example as a Graph**

#### Sequential Dependencies

- Uses instances and constraints on instance fields

- Generates a simple scenario of:

- write to random address

- then read from same address

```

rule_graph write_read_test_seq {

import "decls.rseq";

action init:

interface do trans(trans);

trans tro, tr1;

constraint do write read c {

tr0.dir == write:

tr1.dir == read:

tr0.addr == tr1.addr:

write read test seg = init repeat {

do trans(tr0) do trans(tr1)

} :

```

# **HLS Flow Application 1**

- Growth in high-level synthesis drives need for advanced verification methodology for C/C++ (ESL)

- Random stimulus generation

- Functional coverage collection

- The stimulus model is developed at system architecture stage

- More functional verification earlier in design cycle

- Re-usable at implementation-level

- Common stimulus model is a communication bridge

# **HLS Flow Application 2**

- Methodology requires:

- Alignment of stimulus architecture

- E.g. input variables collected into a class

```

class fir_filter_ld_stimulus

{

public: // data (one class member per DUT function argument)

ac_int<8, true > inp;

ac_int<8, true > coeffs[8];

ac_int<3, false > addr;

bool ld;

public: // interface

fir_filter_ld_stimulus() {}

Analogous to

SystemVerilog UVM

Sequence Item

```

# **HLS Flow Application 3**

- Methodology requires:

- SystemC analog to class.randomize()

- E.g. using interface to the stimulus graph to populate stimulus class fields

#### **New Flow Possibilities**

- Same stimulus model can drive:

- Abstract ESL model

- SystemVerilog UVM simulation

- Fast interface to emulation / other hardware acc.

- What if a solver could provide random stability?

- Portable stimulus produces same scenarios

- Determined by a seed independent of language

- Problems found in one domain can be debugged in any other...

#### **Summary**

- Portable stimulus model provides:

- Enhanced power in verification scenario description

- Another opportunity for re-use of significant coding investment

- Eases project bottleneck by allowing more functional verification at abstract level