# Portable Stimuli over UVM using portable stimuli in HW verification flow

Efrat Shneydor, Cadence Design Systems, Israel (*efrat@cadence.com*) Slava Salnikov, Ben Gurion University & Texas Instruments, Israel (*slava.s@ti.com*) Liran Kosovizer, Texas Instruments, Israel (*lirank@ti.com*) Dr' Shlomo Greenberg, Ben Gurion University, Israel (shlomog@ee.bgu.ac.il)

cādence<sup>®</sup>

# Agenda

- UVM challenges

- PSS solvability

- PSS to UVM flow

- Summary

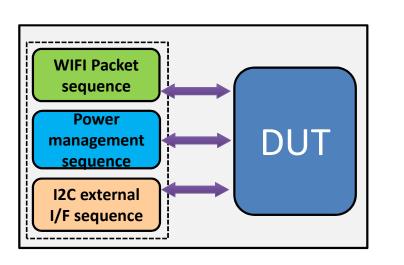

#### Texas Instruments Wi-Fi router

- Multiple CPU cores, power domains & HW hierarchies

- Advanced verification environments, using Specman and UVM-e

- -eight levels of reuse

accellera

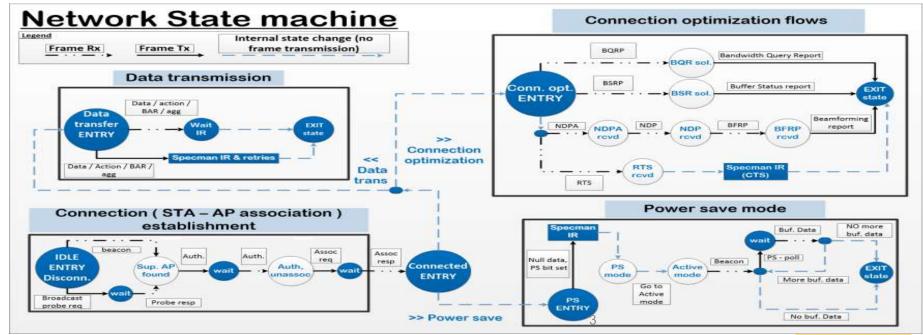

### Verification requirements, stimuli generation

- Capture rules of system behavior

- Achieve a robust, re-usable solution for system level test composition

- Changes of DUT should not require more than minimal modifications of the TB

Δ

#### Each scenario is well defined

#### Sequences libraries

CONFERENCE AND EXHIBITION

EUROP

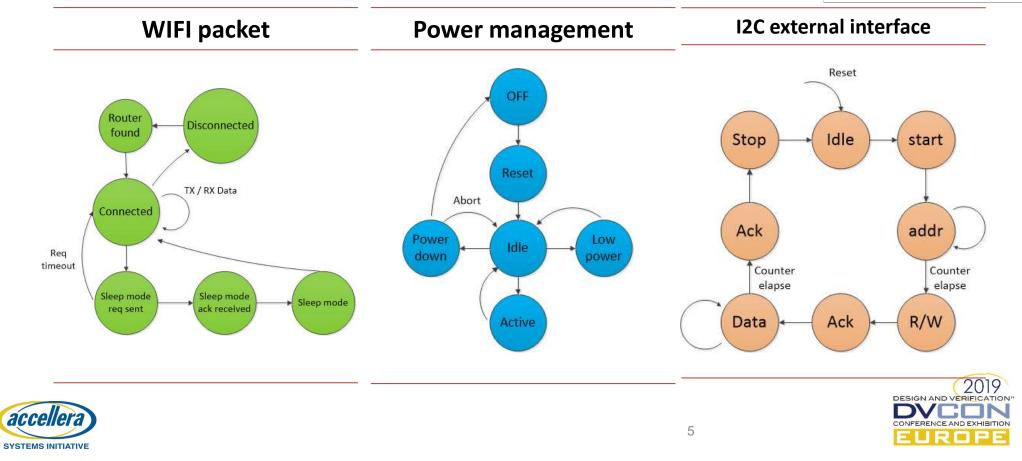

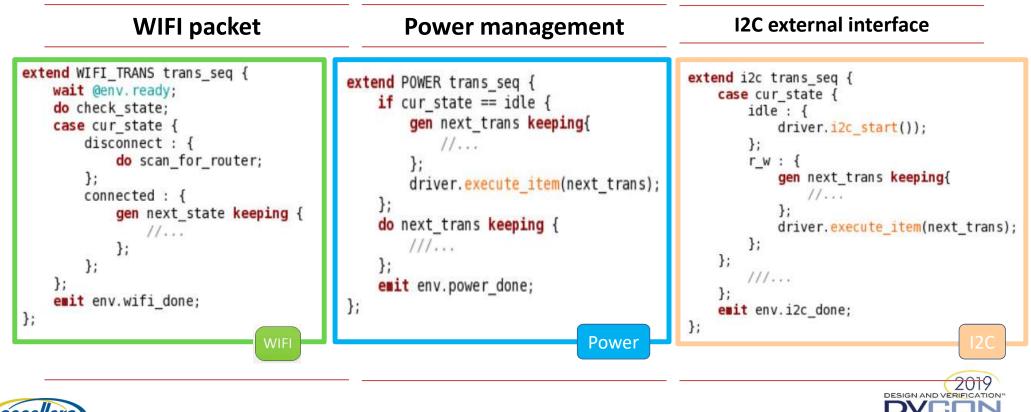

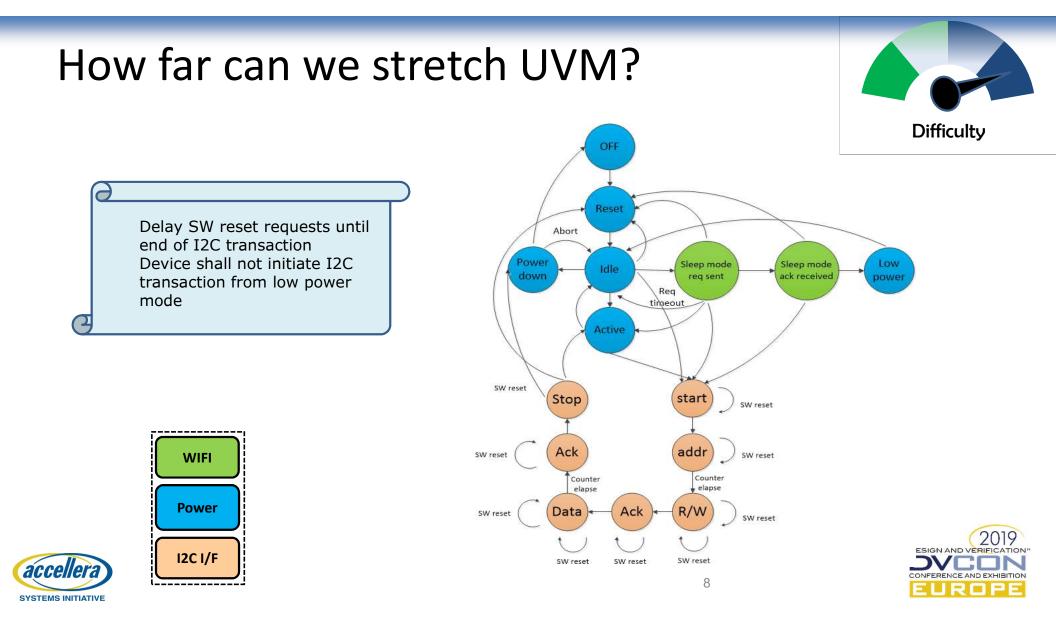

## Interdependence of sub-modules

- Sequence should contain synchronization aids

- Multi-channels sequences

Device shall not enter low power mode before notifying router with a dedicated packet sequence Device shall not send a sleep mode request from any power state but 'idle'

Difficulty

## Agenda

- UVM challenges

- PSS solvability

- PSS to UVM flow

- Summary

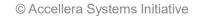

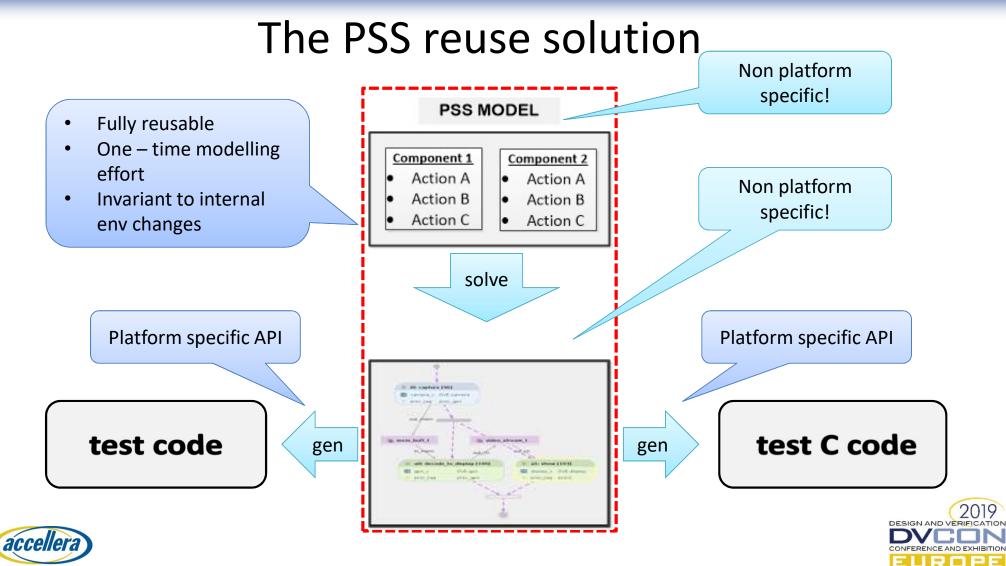

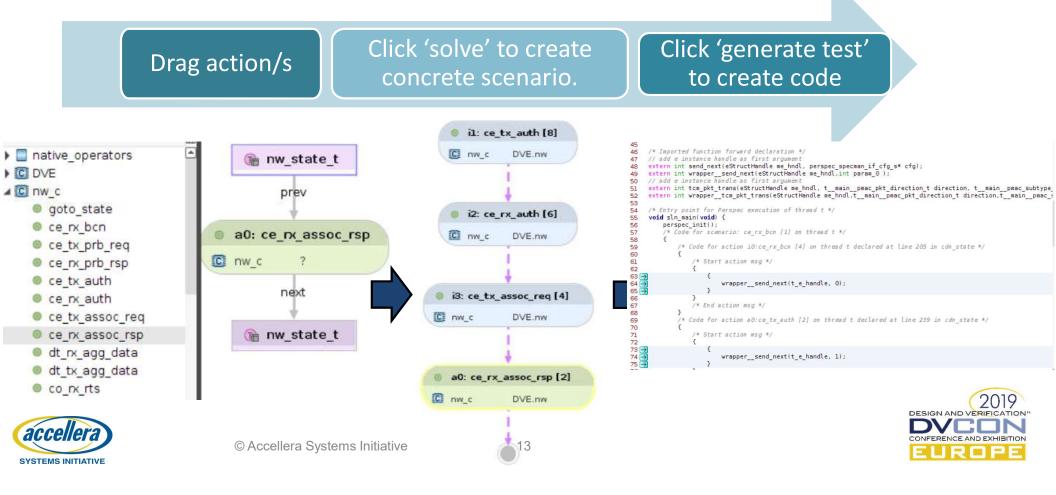

#### **Generating Scenarios Using PSS**

#### **Portable Stimuli actions**

#### **Generating Scenarios Using PSS**

## Agenda

- UVM challenges

- PSS solvability

- PSS to UVM flow

- Summary

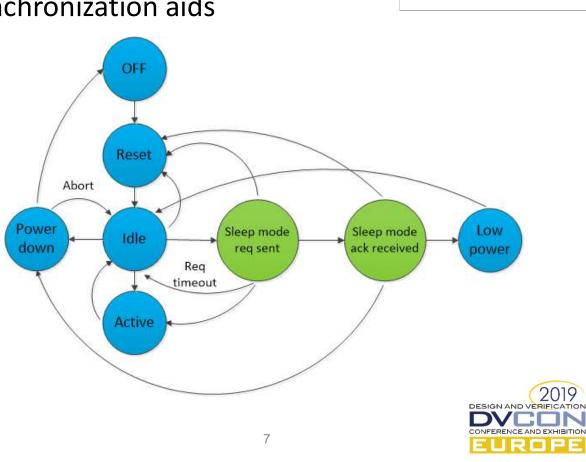

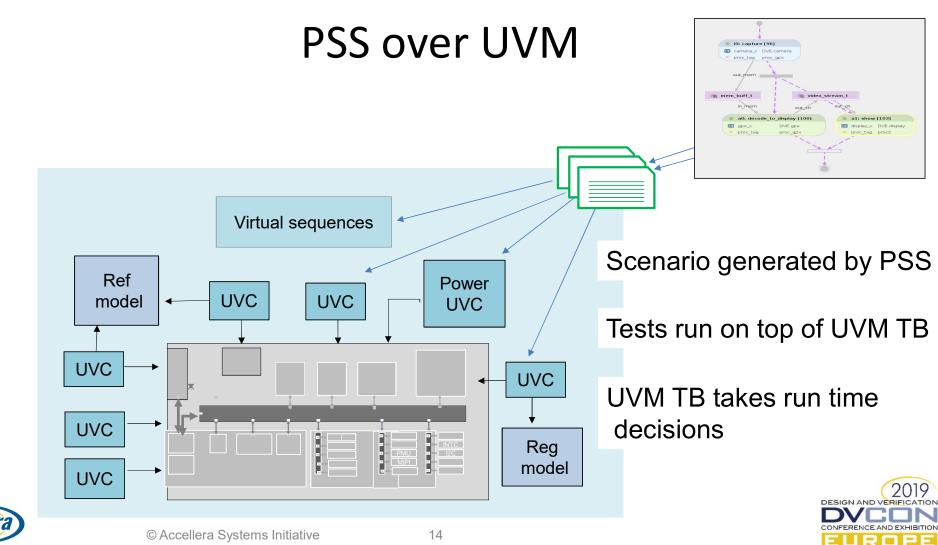

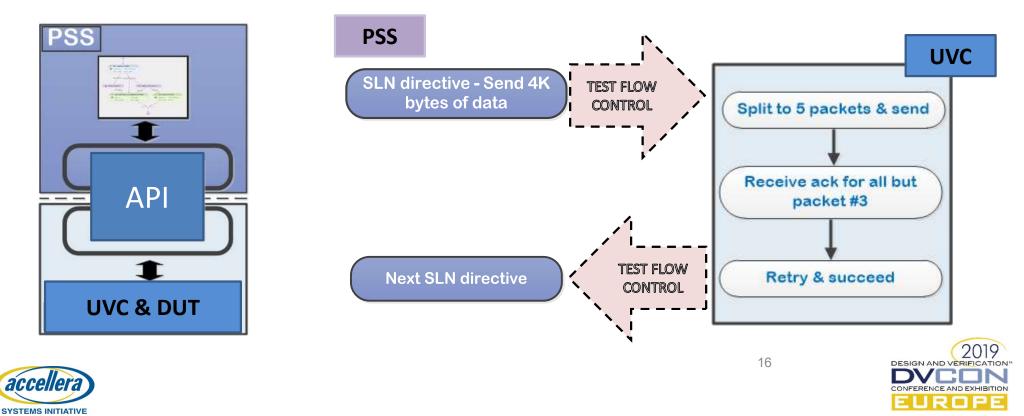

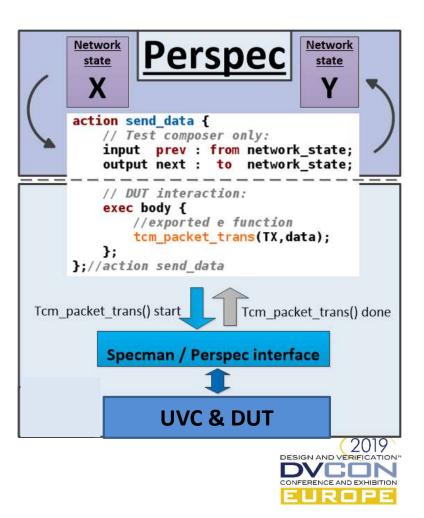

#### **PSS/UVM** Partitioning – the hybrid model

- Perspec scenario provides high level test case backbone

- UVM sequencers handle signal level transactions

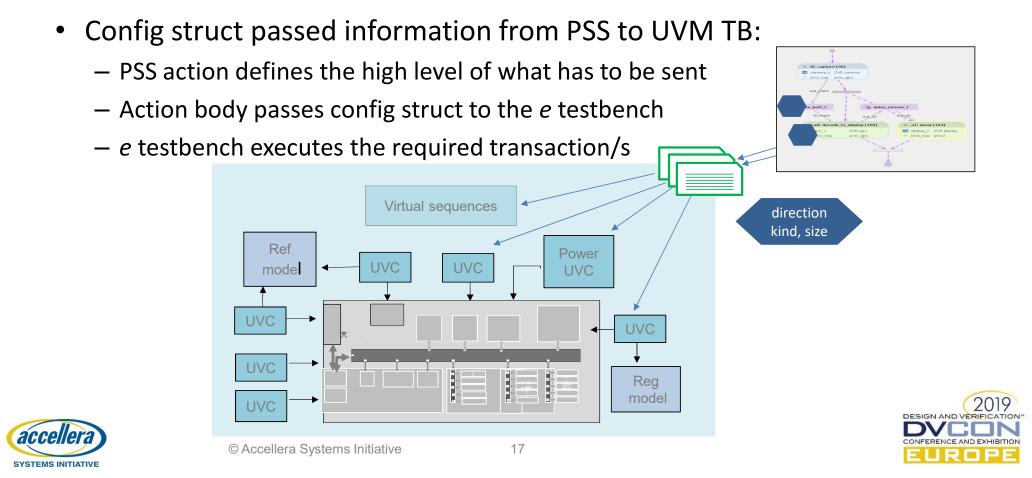

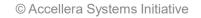

#### Driving the scenario, from PSS to e

```

action change_state {

input prev : from state_var;

output next : to state_var;

cfg : cfg_s ;

exec body {

// Imported function

send_next(cfg);

};

};

```

**PSS Model**

#### From action to test /\* Imported function forward declaration \*/ // add e instance handle as first argument extern int send\_next(eStructHandle me\_hndl, perspec\_specman\_if\_cfg extern int wrapper\_\_send\_next(eStructHandle me\_hndl,int param\_0); action tx auth like change\_state { /\* Entry point for Perspec execution of thread t \*/ constraint prev.state == sup ap found; void sln\_main(void) { constraint next.state == wait auth; perspec\_init(); /\* Code for scenario: ce\_rx\_bcn [1] on thread t \*/ constraint cfg.direction == TX; /\* Code for action i0:ce\_rx\_bcn [4] on thread t declared a constraint cfg.transfer\_kinds.size() /\* Start action msg \*/ == 1; { constraint cfg.transfer kinds[0] wrapper\_\_send\_next(t\_e\_handle, 0); == AUTHENTICATION; }; 44 /\* End action msg \*/ Perspec /\* Code for action a0:ce\_tx\_auth [2] on thread t declared a **PSS Model** © s: sample\_state [11] /\* Start action msg \*/ Perspec { wrapper\_\_send\_next(t\_e\_handle, 1); tore false 0 A: A [14] 0 C: C [18] /\* End action msg \*/ 0 B: B (15) 0 D: D (19) } } @export fli c() send\_next(cfg: perspec\_specman\_if\_cfg\_s) @sys.any is { !seq : vir\_sequence; gen seg keeping { Create scenario, according to config struct .direction == cfg.direction; 11 ... }; seq.start\_sequence(); wait @seq.ended; All fields not constrained here will be }; 2019 randomized, according to UVC constraints DESIGN AND VERIFICATION 100 7 H CONFERENCE AND EXHIBITION © Accellera Systems Initiative 20 UROP

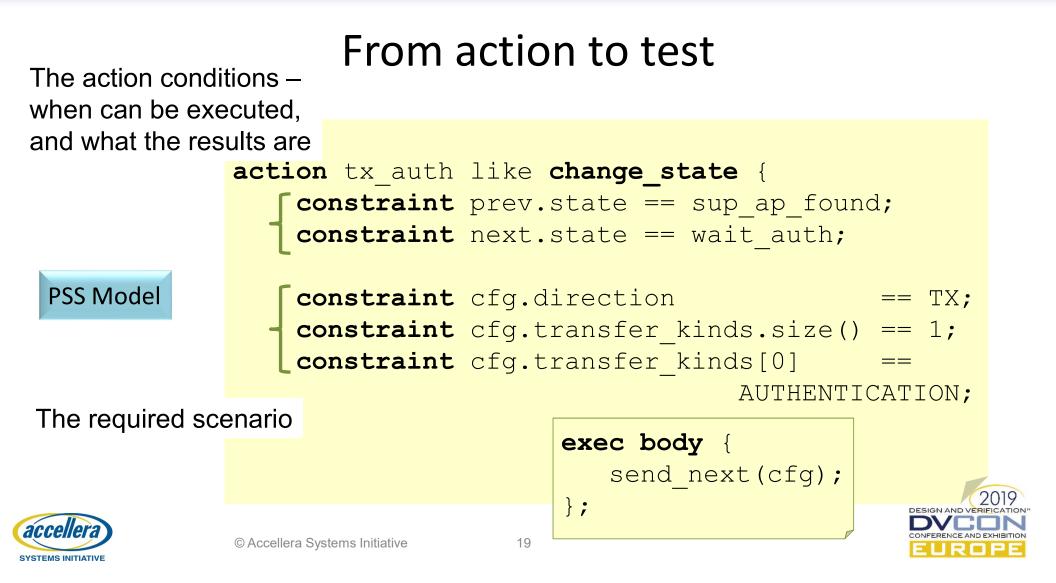

#### The test flow extend sys { The simulator and Specman start running run() is also { start perspec main(); Specman calls the C main in run phase }; perspec main()@sys.any is { From now – C test controls the scenario raise objection(TEST\_DONE); C t.pss main(); drop objection (TEST DONE); void pss main(void) { }; config(MODE 3A); }; send next(t e handle, 0); This code is created automatically by the tool /\* ... In each test pss main() is different, acc based on generated actions

#### Altering the *e*-C synchronization

#### Agenda

- UVM challenges

- PSS solvability

- PSS to UVM flow

- Summary

#### Yet to be added

- Seamless regression invocation

- Vmanager integration, Perspec regression abilities

- Enhance Debug abilities

- Sync UVM test phases with Perspec scenarios

- Perspec/Specman migration to validation platforms (embedded C code)

- Full coverage closure using Perspec WIFI simulator

PSS model

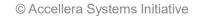

**Network State machine**

- Inputs, Outputs

- Rules of coexistence

- e API to test platform

- Platform specific implementation

#### Summary

- Few weeks ramp up period, hundreds of tests created

- What usually takes several months

- Model is easily updated to new needs

- Concept shift makes integration not intuitive

- Perspec C Specman API impairs seamless integration

- Need to adjust debugging techniques

#### Bottom line: TI decided to expand the usage of Perspec over UVM

2019

DESIGN AND VER

© Accellera Systems Initiative

Questions?