# Co-simualtion platform of SystemC and System-Verilog for algorithm verification

Li Jinghui, Xi' An R&D Center, Inspur, Xi'an, China (<u>lijinghui01@inspur.com</u>) Shao Haibo, Xi' An R&D Center, Inspur, Xi'an, China (<u>shaohaibo@inspur.com</u>) Gou Jiazhen, Xi' An R&D Center, Inspur, Xi'an, China (<u>goujiazhen@inspur.com</u>)

# Agenda

- Current Verification Challenges

- Why SystemC

- The SystemC model of compression algorithm

- Verification with SystemC

- C/C++ vs. SystemC model for Verification

- Advantages of Co-sim Platform of SystemC and System-Verilog

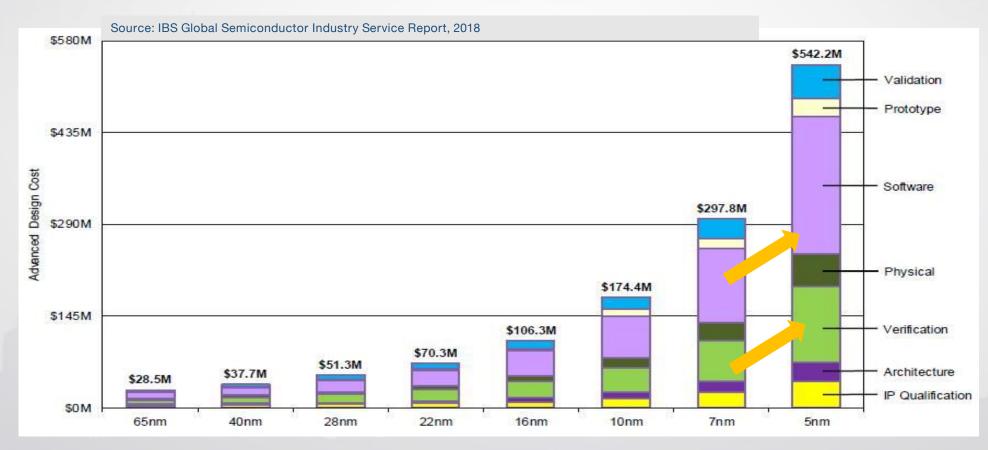

#### **Current Verification Challenges**

- increasing complexity of SoC design

- time to market is getting shorter and shorter

- verification growth in cost and schedules

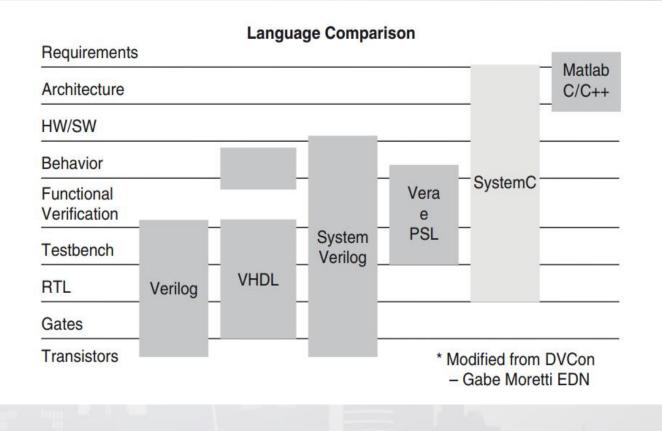

# Why SystemC

- extended library of C++

- hardware-oriented features

- Time model

- Hardware data types

- Module hierarchy to manage structure and connectivity

- Concurrency model

- Communications

management between

concurrent units of

execution

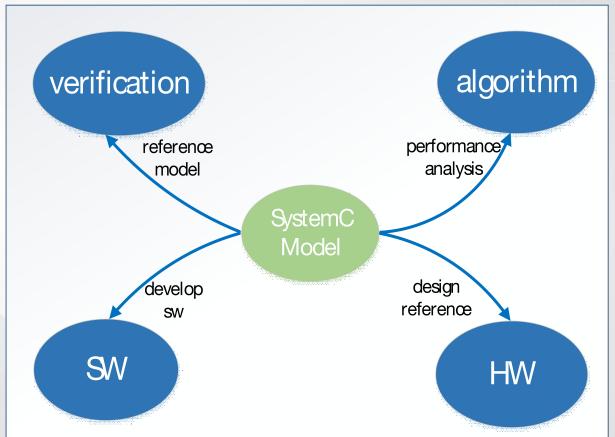

# Why SystemC

- Support modeling at different levels of abstraction

- -ALM

- SAM

- TLM

- RTL

- highly reused in the development of SoC

- as a bridge between various departments

#### Why SystemC

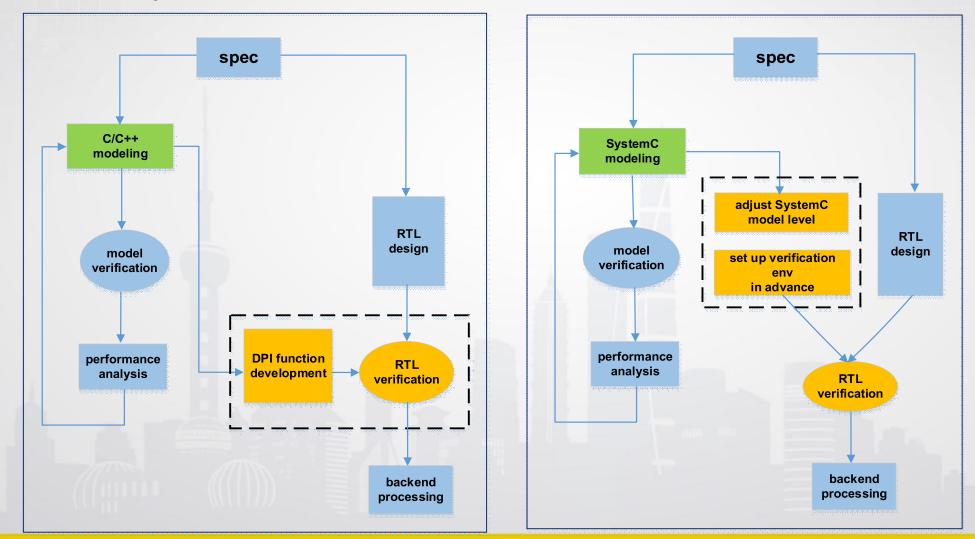

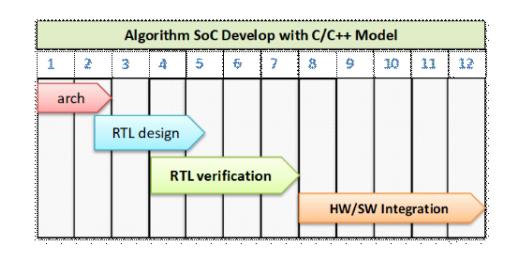

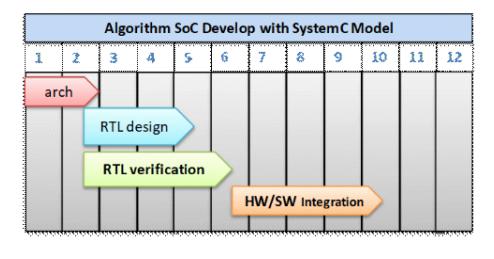

C/C++ vs. SystemC for development processes

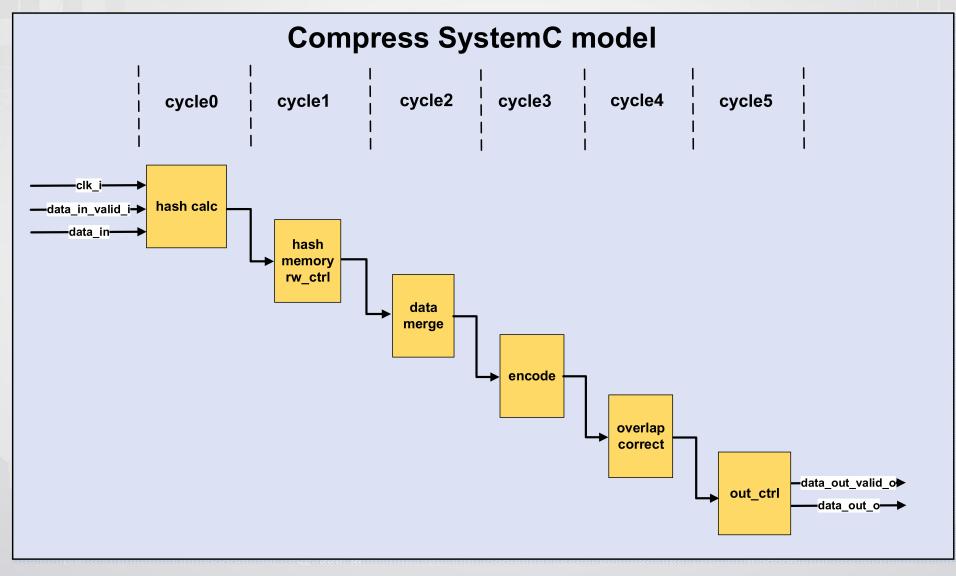

## The SystemC model for compression algorithm

# algorithm requirements

- Original algorithm is to find a possible matching character byte by byte, can only process one byte of input data per cycle

- Need to increase the data throughput rate, explore the parallelization of hardware implementation, process more data in one cycle

- Limited memory resources, HW architecture has no input buffer

- Pipelined processing methods are used to implement a forward and branch-free algorithm

The SystemC model for compression algorithm

| performance analysis |          |               |                   |                   |                   |  |

|----------------------|----------|---------------|-------------------|-------------------|-------------------|--|

|                      | QAT      | initial arch  | updated arch      |                   |                   |  |

| File                 |          | SRAM<br>240KB | SRAM<br>1152KB    | SRAM<br>576KB     | SRAM<br>288KB     |  |

|                      |          | ratio         | ratio<br>BW12_C12 | ratio<br>BW11_C12 | ratio<br>BW10_C12 |  |

| dickens              | 1.659    | 1.449         | 1.58              | 1.652             | 1.592             |  |

| mozilla              | 2.188    | 1.853         | 1.966             | 1.953             | 1.922             |  |

| mr                   | 1.992    | 1.754         | 1.91              | 1.905             | 1.875             |  |

| nci                  | 5.765    | 2.681         | 4.36              | 4.356             | 4.34              |  |

| ooffice              | 1.618    | 1.453         | 1.53              | 1.521             | 1.489             |  |

| osdb                 | 1.89     | 1.710         | 2.22              | 2.131             | 1.86              |  |

| reymont              | 2.207    | 1.736         | 1.96              | 1.941             | 1.902             |  |

| samba                | 2.889    | 2.079         | 2.73              | 2.696             | 2.61              |  |

| sao                  | 1.158    | 1.188         | 1.18              | 1.173             | 1.162             |  |

| webster              | 2.165    | 1.808         | 2.18              | 2.154             | 2.092             |  |

| x-ray                | 1.136    | 1.057         | 1.124             | 1.107             | 1.072             |  |

| xml                  | 3.714    | 2.641         | 3.73              | 3.875             | 3.772             |  |

| average              | 2.247249 | 1.823031      | 2.131843          | 2.119311          | 2.061693          |  |

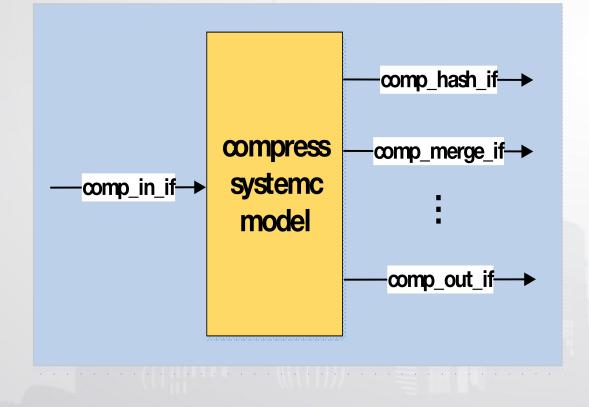

Build a pin-level algorithm model

- The interface timing of the model is exactly the same as the RTL ;

- Output intermediate results through the SystemC out port for debugging

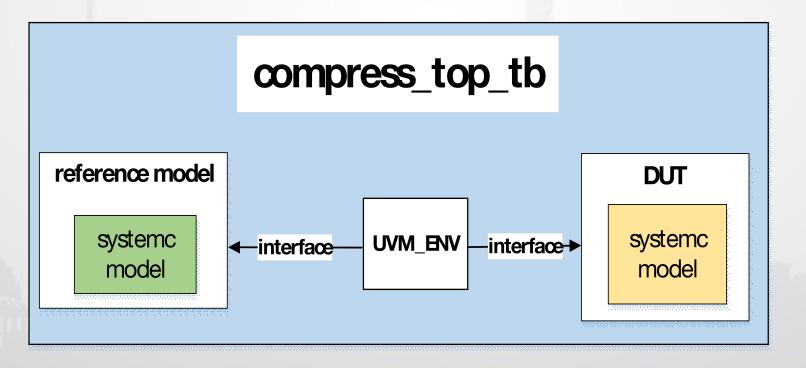

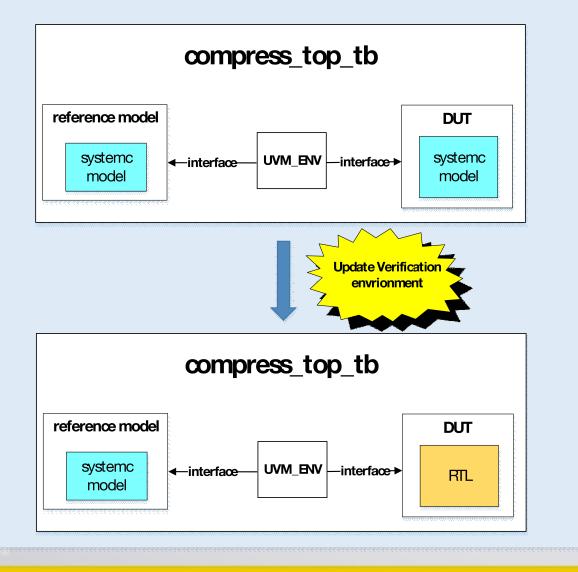

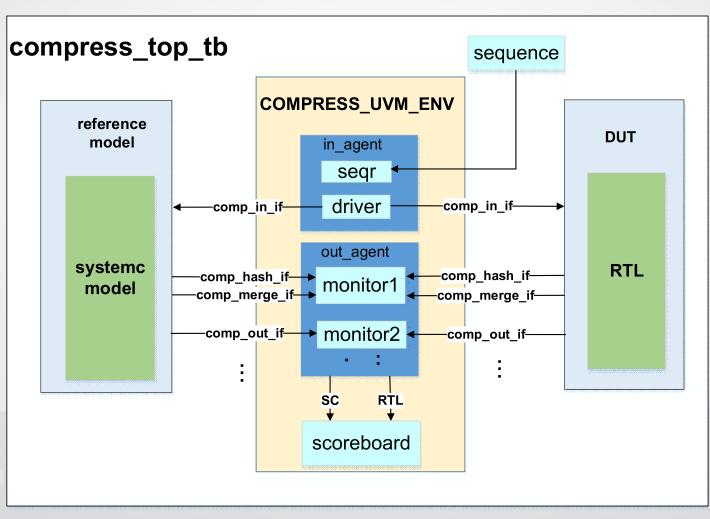

- Use the SystemC model to build UVM TB in advance

- Before RTL is available, the SystemC model can be used as a DUT to build TB for preliminary verification

- Verify the real RTL

- Upgrade the verification environment

- EDA tools such as VCS has built-in support for SystemC.

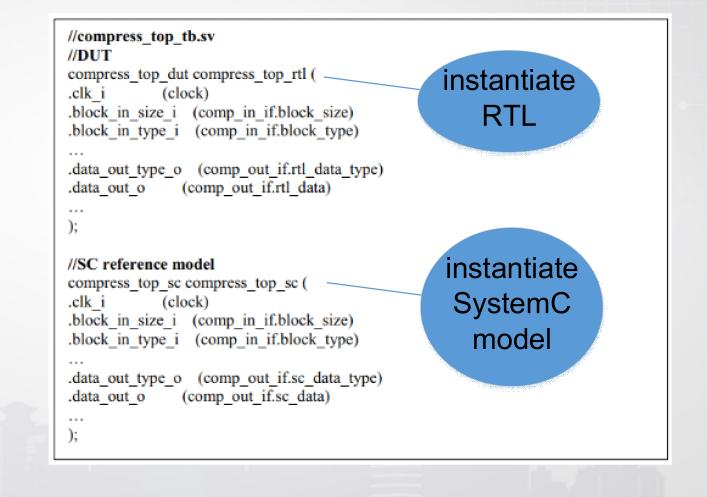

- When integrating the SystemC model into the System-Verilog environment, just instantiate the model like an RTL module

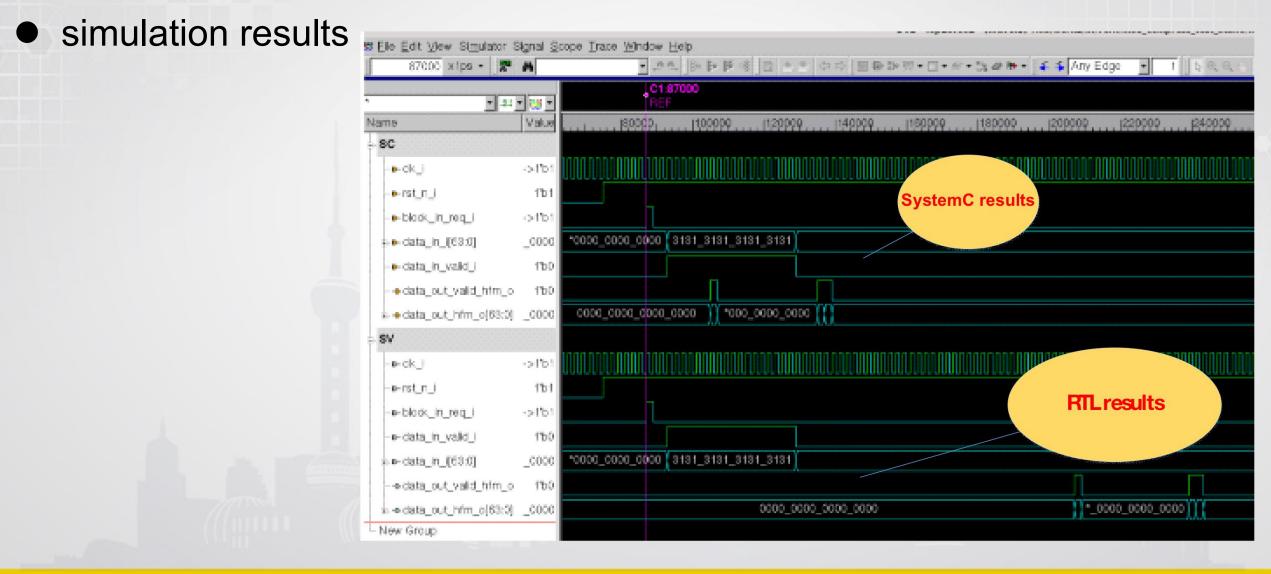

#### Co-sim platform of SystemC and System-Verilog

simulation command with VCS

//Compile Systemc: syscan -cpp g++ -cc gcc -cflags -g -full64 \$(SC\_SRC)

```

//Compile System-Verilog:

vlogan -full64 -sverilog $(SV_SRC)

```

//elaboration

vcs -full64 -cpp g++ -cc gcc -sverilog -sysc SV\_TOP\_TB

debug SystemC model with VCS Cbug

| 3270000 x1ps                                  | Set <u>up</u><br>Rebuild and Start<br>Start/ <u>C</u> ontinue | F5 25000          | nber.1∖                                      | • 8 • ~ • 19. |

|-----------------------------------------------|---------------------------------------------------------------|-------------------|----------------------------------------------|---------------|

| Hierarchy                                     | Step/Ne <u>x</u> t<br>Run To Source Line<br>Set Continue Time | •                 | ulti_result_dly_r[63<br>dly_r[4:0]           | 3:0]          |

| tunnamed<br>tunnamed<br>trunnamed<br>tash32_n | Restart.<br>Terminate                                         | Ctrl+E5           | _dly_r[4:0]<br>lt_s[63:0]<br>lf_data_s[63:0] |               |

| ■gen_n[1].<br>■gen_n[1].<br>■gen_n[1].        | Save State<br>Restore State                                   | 252959            | [31:0]                                       | 250315311     |

| +≣gen_n[1].<br>+≣gen_n[1].                    | Add Checkpoint<br>Rewind To Checkpoint<br>Delete Checkpoint   | •                 |                                              |               |

| ■gen_n[1]. ■gen_n[0]. ■gen_n[0]. ■gen_n[0].   | Eorce Value<br>Change Value<br>Dump Full Hierarchy            | Parising.         | [9:0]<br>[9:0]                               | Party Ind.    |

| ■gen_n[0].<br>•■gen_n[0].<br>•■gen_n[0].      | Add Dump<br>Dump<br>Capture Delta Cycle Value                 | 20 <sup>205</sup> | .0<br>0[16:0]                                | 2535314       |

| gen_n[0].                                     | Periodic Waveform Update<br>C/C++ Debugging<br>Constraints    | •                 | /IDTH[31:0]<br>- Enable<br>Show External E   | unctions      |

| Type: - Seve                                  | rity: - Code: All                                             |                   | * @ * *                                      | S             |

- VCS SystemC co-simulation interface

- Enables Verilog, VHDL and SystemC modeling to work together

- Supports for Verilog-top/SystemC-top/multiple-top topology

- VCS Extensions to SystemC Library, such as get\_full\_name()...

- Unified compilation/simulation/debug flow

- Transaction Level Interface (TLI) enables integrating transaction level SystemC models into a SystemVerilog environment seamlessly and efficiently

## Advantages of Co-sim Platform

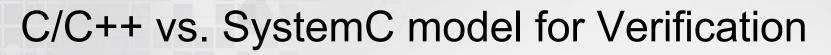

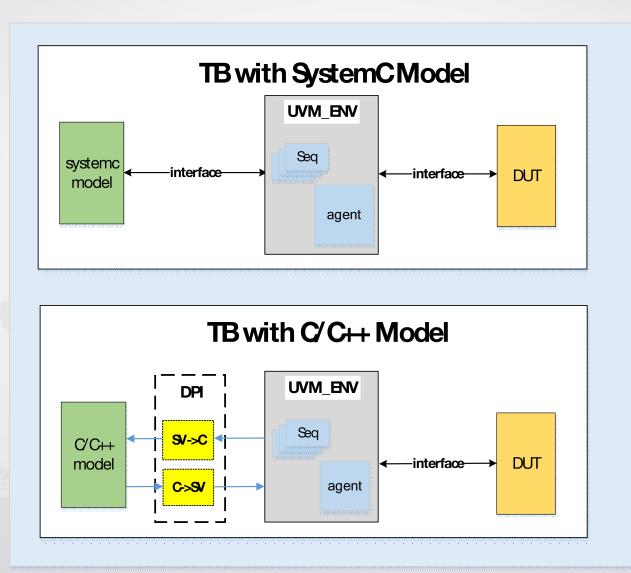

## C/C++ vs. SystemC for Verification

| items           | C++                                                                                           | SystemC                                                  |

|-----------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------|

| integratio<br>n | Develop DPI-C function                                                                        | As simple as instantiating RTL                           |

| driver          | Call the DPI function in the test case                                                        | Driven by the same driver of RTL                         |

| checker         | Need to store the results of C/C++<br>model<br>Take up additional storage space               | Monitor the results through interface                    |

| debuggin<br>g   | Internal variables are difficult to<br>debug<br>Dump variables to files or use<br>breakpoints | Output key variables through<br>SystemC ports or signals |

#### Verification start earlier

Be reused by Arch/HW/SW team

Be easily reused for module/sub-system/SOC verification

When the RTL of some modules has not been delivered, SystemC model can be used to start sub-system or SOC level verification

| items                      | C/C++ Model  | SystemC Model   |  |

|----------------------------|--------------|-----------------|--|

| Model integration time     | About 3 days | Less than 1 day |  |

| Debug                      | difficult    | easier          |  |

| Verification start earlier | No           | Yes             |  |

| Verification reusability   | low          | high            |  |

|                            |              |                 |  |

# THANK YOU!