Tom Fitzpatrick

Verification Evangelist, Mentor Graphics

Dave Rich

Verification Architect, Mentor Graphics

## Multiple Sources = Bloat

- Why have two ways to do the same thing?

- Worse: almost the same thing

always @\* C = A & B; always\_comb C = A & B;

- Verilog 1364-2001

SUPERLOG

- Evaluated when RHS

Evaluated when RHS changes

- changes and at time 0

- Use this one

- Once something is in a standard, it's almost impossible to remove it

#### More SystemVerilog Bloat

- program blocks left over from Vera

- Starts executing at time 0

- Simulation terminates when last program exits

- Not needed for UVM

- Defined new timing semantics to avoid test/design race conditions

- Mimics semantics of PLI application

- Still subject to races in the testbench

- clocking block handles test/design races

- Doesn't affect timing/semantics of testbench

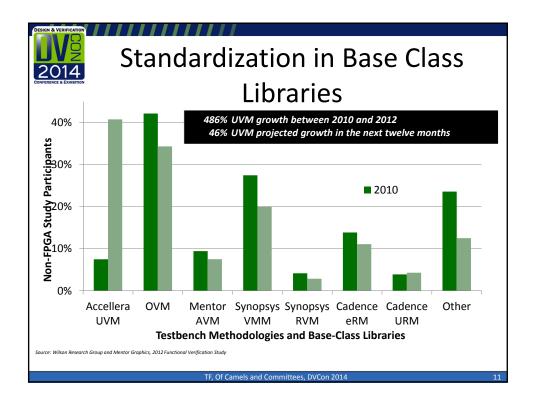

#### User Feedback is Critical

- New code should benefit users

- Phasing still doesn't work

- "Top Priority"

- Don't repeat mistakes

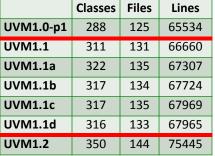

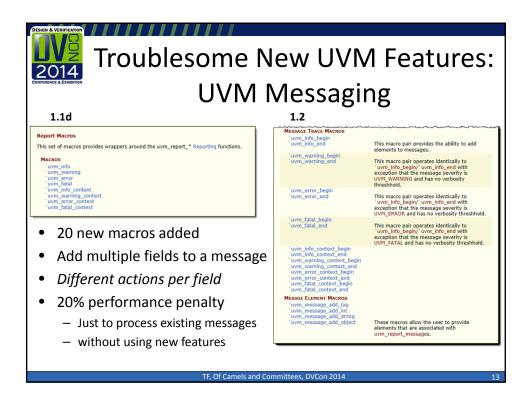

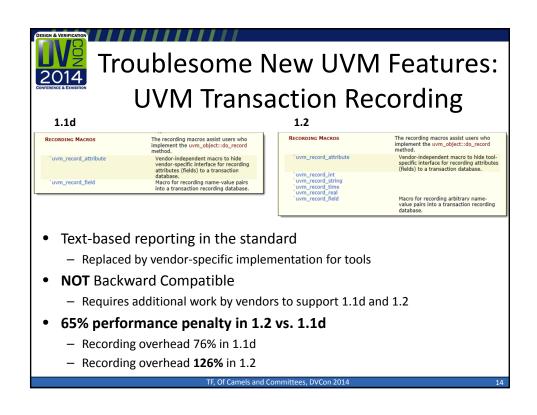

- UVM1.2 introduces 13 backward-incompatible changes

- Considerable performance degradation

- No extended user feedback period

F, Of Camels and Committees, DVCon 2014

12

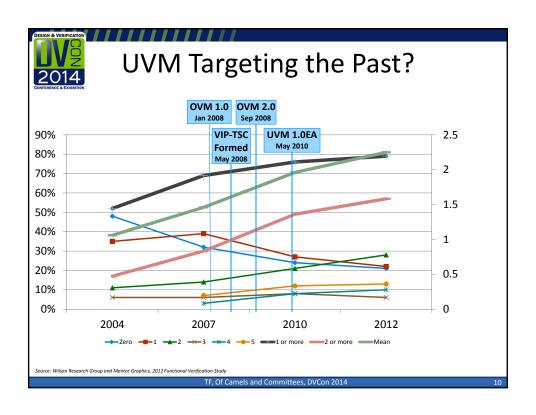

#### Aim at the Right Target

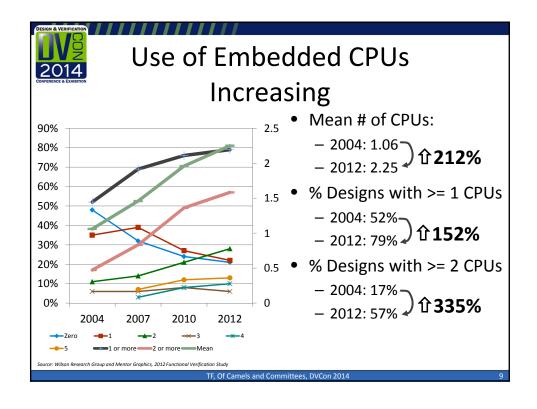

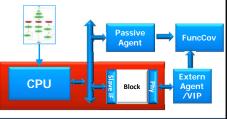

- Verification has clearly moved beyond block-level

- Multi-core

- Complex interconnect

- Constrained-random sequences don't cut it anymore

- Impossible to write constraint equations for cache coherency

- Need higher level of abstraction

FF, Of Camels and Committees, DVCon 2014

15

### Real Reuse Requires Abstraction

- Begin with the End in Mind

- UVM ideally suited for structural reuse

- Factory, config, build\_phase(), connect\_phase()

- Stimulus reuse requires abstract specification

- Retargetable to UVM sequences and software

F, Of Camels and Committees, DVCon 2014

16

# Real Reuse Requires Abstraction

- Begin with the End in Mind

- UVM ideally suited for structural reuse

- Factory, config, build\_phase(), connect\_phase()

- Stimulus reuse requires abstract specification

- Retargetable to UVM sequences and software

#### The Problem Has Changed

- System-level verification requires more than UVM

- Software execution coordinated with external stimuli

- Constrained-random isn't enough anymore

- UVM 1.1d is a structural innovation platform

- Flexibility to specify the environment

- Allow innovative technology to drive verification

- UVM 1.2 is not necessary

- Certainly not without extended user feedback period