# Novel Mixed Signal Verification Methodology Using Complex UDNs

Rakesh Dama, Ravi Reddy, Andy Vitek

**Roche Sequencing Solutions**

1

# Outline

- Introduction

- Modeling Analog Nets using UDNs

- Defining a Generic UDN

- Modeling of SAR-ADC

- Power Aware Verification

- Q&A

# Introduction

- Mixed signal designs are increasing by number and complexity

- Modeling approach for analog design is determined by

- Accuracy (SPICE > Verilog-AMS > SV-RNM)

- Simulation perf (SV-RNM >> Verilog-AMS > SPICE)

- Effort (SV-RNM > Verilog-AMS > SPICE)

- SV-RNM is ideal for SOCs due to:

- Simulation performance (approx. 300x Spice, 100x Verilog-AMS)

- Portability of models

- Acceptable accuracy and effort

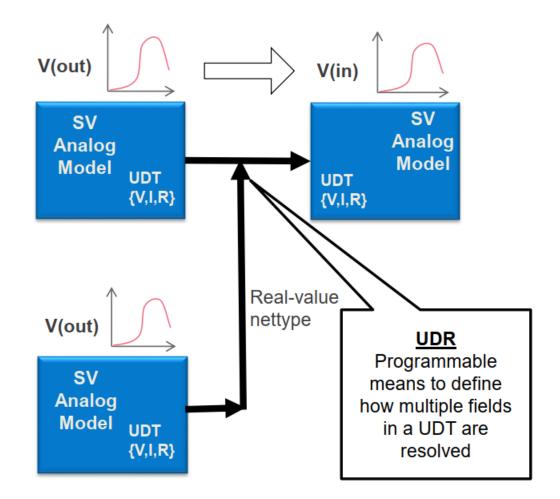

# **SV-RNM** and **UDN**

- Simple 'real' nets

- Single Driver nets

- Straight forward and simple

- User Defined Nettype (UDN)

- Multiple Driver nets

- Multiple values can be passed (such as Voltage, Current, Impedance)

- A User Defined Resolution function computes the resultant value

From: How To's of Advanced Mixed Signal Verif, DVCon 2015

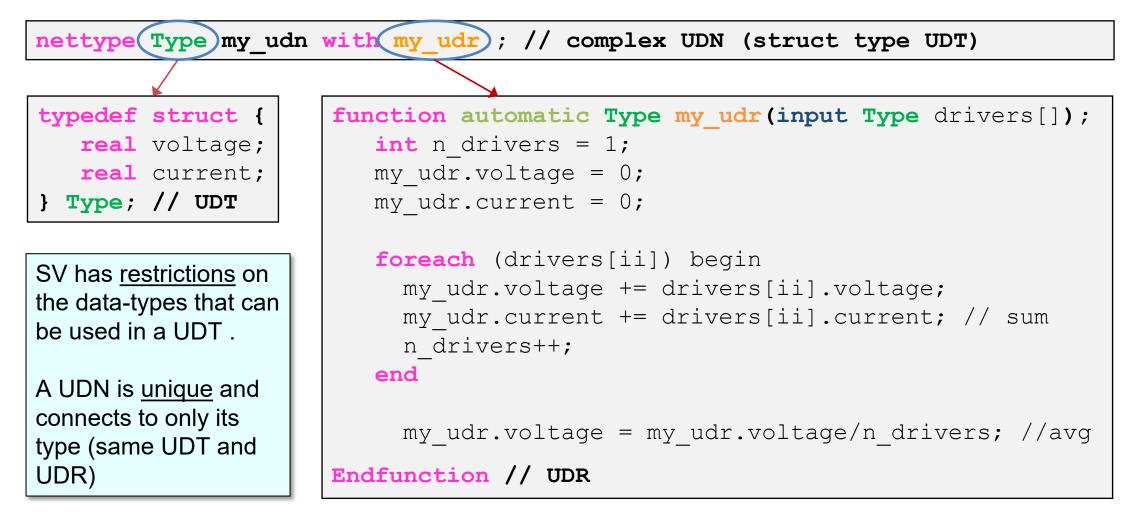

## **Declaring UDN with Resolution**

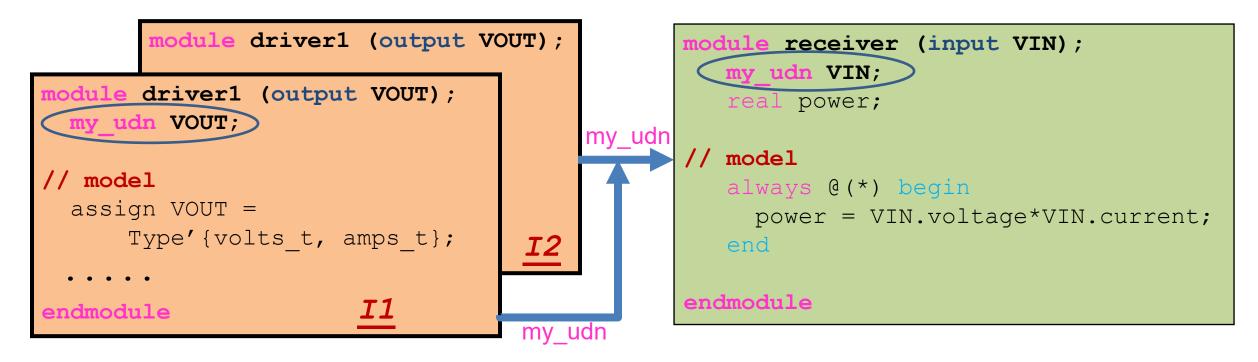

# **UDN Usage**

nettype Type my\_udn with my\_udr ; // complex UDN (struct type UDT)

typedef struct { real voltage; real current;} Type; // UDT

Any change in the drivers (in I1 and I2) of the UDN (my\_udn) will trigger the UDR function (my\_udr) and the resolved value is computed and made available to the modules.

# Motivation for a Generic UDN

- In an analog circuit

- A net has different types of drivers (voltage, current, capacitive, switches...)

- The same net has to be resolved in different ways at run time

- UDN nets must connect to 'same type' ports i.e. same UDT + UDR

- No dynamic selection of UDR allowed

- Should multiple UDN types be declared?

- Even so, how to connect port of different types?

- While EE\_net (Cadence) implements a generic electric equivalent, it cannot handle capacitance and more – how to implement ideal switch?

## Concept of a Generic UDN

- A generic UDN that can replace all other UDNs across the design

- Only a single UDT and a single UDR function

- Can be used to connect any set of ports in a design

- Can resolve different scenarios at run time

- Provides extensibility for new use cases (when the need arises)

- Ability to compute resultant currents and voltages (like EE\_net)

- Offers modeling efficiency by standardizing and abstracting out UDR

# Generic UDN – UDT and UDR

- Analog port types are defined

- V\_OUT, I\_OUT > V\_PT, I\_PT > V\_CAP > V\_IN, I\_IN

- UDT has a field, port\_type, to assign port type for a port

- A UDR function is written to resolve based on port types of all ports connected to the net.

- The dominant port type is resolved, i.e. strongest driver

- Based on the resolved port\_type, values for V and I are resolved

- When the strongest driver is `Z, then the next dominant driver determines the resolved values

```

// UDT for generic UDN

typedef struct {

// V_OUT, V_PT, V_CAP...

PORT_TYPE port_type;

```

```

// Driven values on ports

real v_value;

real i_value;

real g_value;

real c_value;

```

```

// vars for active drivers

real v_active;

real i_active;

real g_active;

real c_active;

GENERIC_PORT;

```

#### A Generic UDN example

| <pre>// Resolution function for generic UDN function automatic GENERIC_PORT GEN_RES (input drv[]);     // code to resolve using port_types     // endfunction</pre> | Vout net2<br>Vout Vcap Vin<br>V C R                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>// Generic UDN for generic UDN nettype GENERIC_PORT GENPORT with GEN_RES;</pre>                                                                                |                                                                                                                                                                              |

| <pre>// Module definitions module V (output GENPORT v_src);   real v_val;   assign v_src = { V_OUT, v_val, `Z, `Z,};   //</pre>                                     | <pre>// TB module TB (); wire net1; //net coerced to GENPORT wire net2; //net coerced to GENPORT V v1 (net1); SW sw1 (net2, net1); C c1 (net2); R r1 (net2); endmodule</pre> |

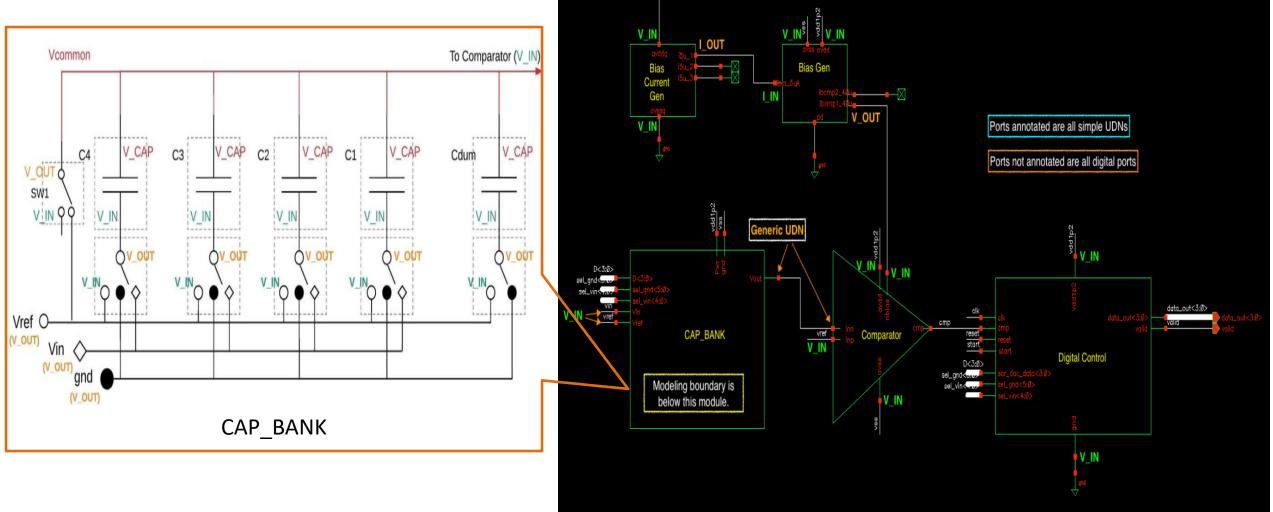

#### Modeling a SAR ADC

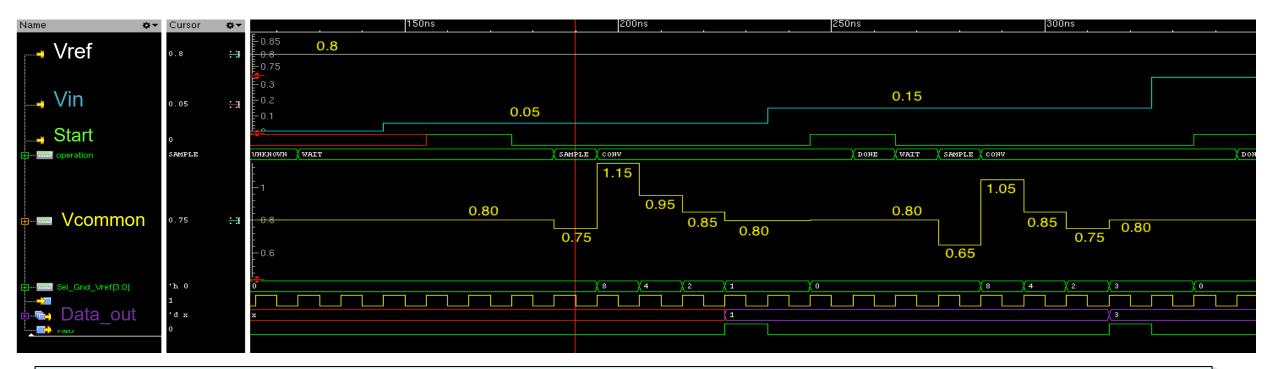

#### Simulation Results of SAR ADC

- Vcommon node is the capacitive node where charge re-distribution happens

- Conversion starts 2-clk cycles after the falling edge of 'Start' signal and takes 4-clks for data\_out

- Capacitors are connected to Vref in a sequence (MSB to LSB), this changes the Vcommon volts

- Digital logic determines if capacitor stays connected to Vref or Gnd

#### **Comparison with SPICE**

|                    | RNM   | Spice  |

|--------------------|-------|--------|

| SNR (dB)           | 20.05 | 18.16  |

| THD (%)            | 10.9  | 10.2   |

| SINAD              | 16.63 | 15.89  |

| ENOB               | 3.03  | 2.72   |

| Sim Time (seconds) | 4.7   | 1183.3 |

accellera

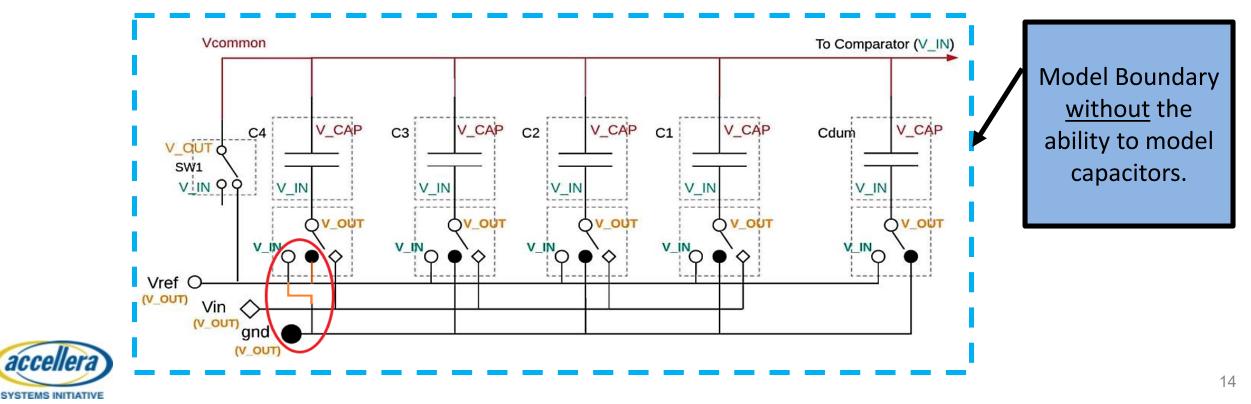

## Bug

- Switch polarity reversal for MSB cap ullet

- Due to schematic error, the Vref and GND connections for MSB were interchanged

- Resulting in 0.5\*Vref or 8-LSBs of error

- Lowering model boundary can expose this bug. \_\_\_\_

#### **Bug Exposed**

- Switch polarity reversal for MSB cap

- Resulting in 0.5\*Vref or 8-LSBs of error

- Lowering model boundary enabled easy detection of the bug

| Baseline ▼ = 410.21ns Cursor-Baseline ▼ = -128.75ns |          |                |                             |       |       | TimeA               | = 281.46ns |       |       |       |       |       |       |       |       |       | Baselir | e = 410.21i | ns     |

|-----------------------------------------------------|----------|----------------|-----------------------------|-------|-------|---------------------|------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------|-------------|--------|

| Name 😽                                              | Cursor   | Q.             | Ins                         | 260ns | 270ns | 2 <mark>80ns</mark> | 290ns      | 300ns | 310ns | 320ns | 330ns | 340ns | 350ns | 360ns | 370ns | 380ns | 390ns   | 400ns       | _4►    |

|                                                     |          |                | L 0.4                       |       |       |                     |            |       |       |       |       |       |       |       |       |       |         | (           | 0.45 🔶 |

| j <sup></sup> ⊡ x_vAin                              | 0.15     | -1             | ₽0.3<br>₽02                 |       |       |                     | 0.15       |       |       |       |       |       | 0.35  |       |       |       |         |             | ÷      |

|                                                     |          |                | <u>-0.2</u><br>-0.1<br>-1.2 |       |       |                     |            |       |       |       |       |       |       |       |       |       |         | (           | 0.05 🚽 |

| Group 1<br>Buggy_vout                               |          |                | E1.2                        |       |       |                     |            |       |       |       |       |       |       |       |       |       |         | 1.24        | 876 🔶  |

| 📰 buggy_vout                                        | 1.04876  | <del></del> .  | E=1<br>= 0.8<br>= 0.6       |       |       |                     |            |       |       |       |       |       |       |       |       |       |         |             | ÷      |

| wout                                                | 0.648757 | <del>: 1</del> | E-0.6                       |       |       |                     |            |       |       |       |       |       |       |       |       |       |         | 0.452       | 488 🖵  |

| ⊕ <b>[</b> ] <b>[</b> ]:0]                          | 'h 5     |                | 5                           |       |       |                     |            |       | ( 3   |       |       |       |       |       |       |       |         | ( 7         |        |

| ⊕                                                   | 'h D     |                | D                           |       |       |                     |            |       | В     |       |       |       |       |       |       |       |         | F           |        |

| 📫 valid                                             | 0        |                |                             |       |       |                     |            |       |       |       |       |       |       |       |       |       |         |             |        |

|                                                     |          |                |                             |       |       |                     |            |       |       |       |       |       |       |       |       |       |         |             |        |

## Assumptions and Limitations

- To simplify, all active source are ideal (zero output resistance)

- Non-ideal behavior has to be implemented in the source driver model

- V\_OUT and I\_OUT connections aren't allowed

- Implementation done in Cadence Incisive simulator only

- For efficiency reasons, generic UDN to be used to augment simple UDN

- Certain port combinations are yet to be implemented

- Series capacitance, chaining of two-way switches (V\_PT, I\_PT ports)

- Debug of generic UDR is tricky due to limited debug hooks

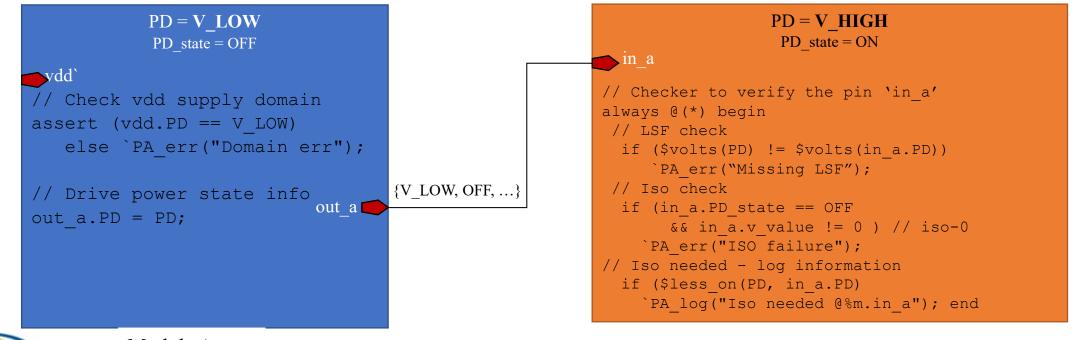

# Future Enhancement - Power Aware Ports

- Adding attributes to the UDT PD\_name and PD\_state

- Power Domain information is available at run time

- Checkers inside the models utilize this PD info to verify power intent

#### Questions?

#### Thanks!

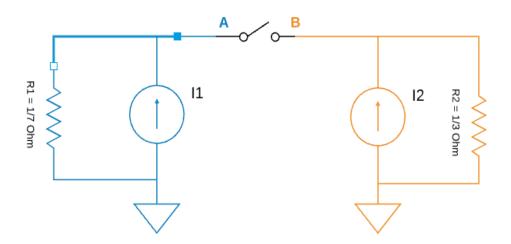

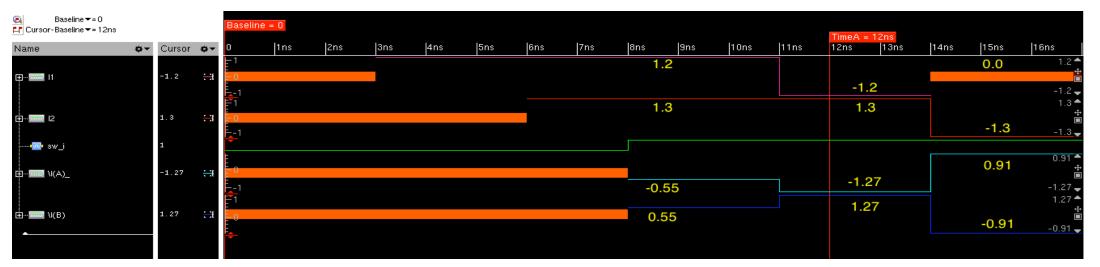

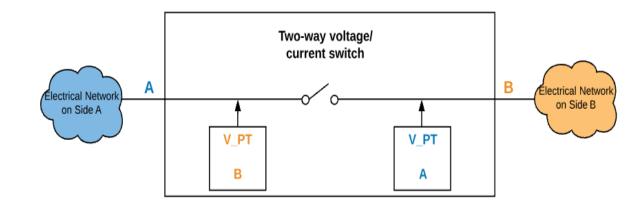

#### Additional – Bi-directional Switch

- Presents the resolved resistance, capacitance, current and voltage of all external sources from one port to the other port using V\_PT ports

- Accurate when connecting two current branches

## Additional – Bi-directional Switch e.g.

A switch connecting two current carrying branches is tricky to implement to reflect true currents on either side