# Mixed Signal Verification of Dynamic Adaptive Power Management in Low Power SoC

Neyaz Khan Architect - Mixed Signal & Low Power Verification Cadence Design Systems, Inc. Plano, TX, USA <u>nkhan@cadence.com</u>

#### ABSTRACT

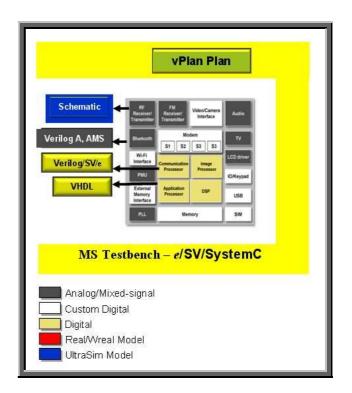

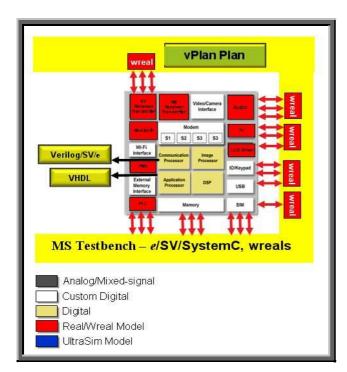

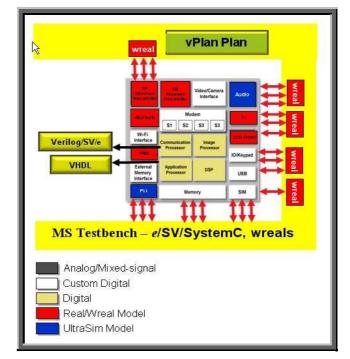

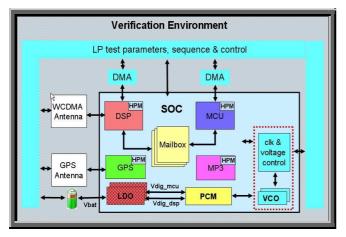

Virtually all modern SoC designs today are mixed-signal in nature. Most systems have to interface their millions of gates, DSPs, memories, and processors to the real world through a display, an antenna, a sensor, a cable or an RF interface. The already complex task of functional verification at the SoC level is getting harder and more time consuming. Up until recently, mixed-signal designs could be decomposed into separate analog and digital functions. Traditionally, digital verification engineers have made assumptions and approximations about the analog components and likewise, the analog designers have made assumptions about the digital behavior. Present day mixed-signal designs have multiple feedback loops with complex system-level interaction between digital and analog components, which is often a rich source of errors. There is a need for an integrated mixed-signal simulation and verification strategy and methodology that can be used to extend advanced verification techniques from the digital verification realm to analog components without compromising speeds needed to verify digital components while preserving the accuracy needed to model and verify analog components.

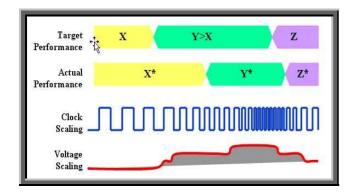

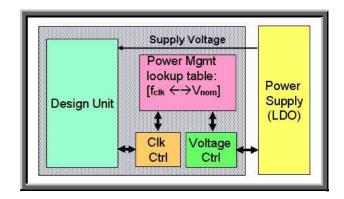

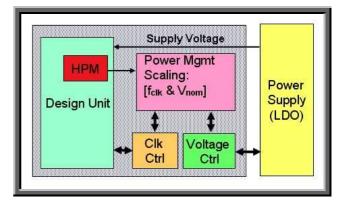

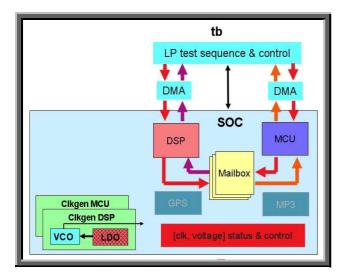

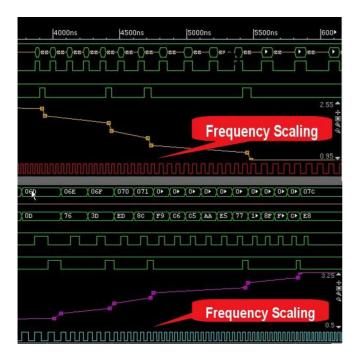

On an orthogonal plane, the mandate for power reduction is being pursued at every level of IC design for more energy efficient systems. For static power reduction, IC designers are widely deploying power shut-off (PSO) techniques in the design. In applications where PSO is not applicable, power management is often achieved by dynamically scaling the operating frequency and voltage of the target design in real time – a technique know as DVFS (Dynamic Voltage and Frequency Scaling). The verification of DVFS is often a very difficult and delicate task that involves tremendous interaction between the digital and the analog domains. This further increases the complexity of functional verification, which was already a bottle neck, and now becomes even more complex and time-consuming task at the SoC level.

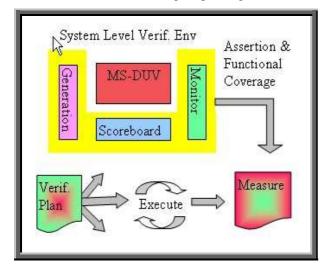

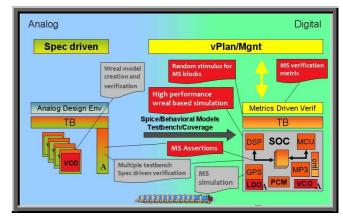

This paper will introduce Digital-centric Mixed Signal (DMS) Verification methodology and provide an overview of how it can enable high performance SoC-level mixed signal verification at digital speeds using Real Number Modeling (RNM) of analog components. Dynamic Power management techniques will be examined in detail. DMS methodology will be applied to an SoC example running Adaptive DVFS as a case study.

## **1 INTRODUCTION**

The complexities involved in SoC level mixed signal verification reveal themselves in a number of ways – ranging from the various languages and disciplines used to the level of abstraction involved in modeling the functionality of complex modern mixed signal SoCs. While the analog components are functionally verified using transient analysis and typically use tools that are based on sparse-matrix based numerical methods, on the digital side functionality is verified using event driven simulation. Both disciplines come together at the SoC level and the task of verifying functional correctness, which was already a daunting task, now gets even more complex and needless to say, much more difficult.

On the digital side, there are advanced verification techniques available to gauge the thoroughness and completeness of the verification effort and require multiple regression runs. With that comes the need for simulation speed and throughput. On the analog side, there is a need for a high-level of accuracy – a single event like a clock edge on the digital side may require numerous computations on the analog engine. This becomes a very severe bottleneck in the MS Verification process. While this accuracy may be required for verification within the analog environment itself, it may not always be necessary for interacting with the digital side. A desirable solution would be to move high frequency events from the analog engine onto the digital engine while preserving the accuracy needed for analog/digital interaction. This forms the basis of a newly proposed Digital Mixed Signal (DMS) Verification Methodology based on Real Number Modeling (RNM) which is presented in this paper in section 2.1.

It's no secret that power management is a key careabout and is emerging as a mandatory requirement in all modern SoCs. While leakage power is well managed by powering down design units that are not functionally needed during the operational cycle of a device [8], there are some key sections of the device that can not be powered down. These are often very power hungry and need to be addressed. Dynamic power management is a very delicate task whereby the operating voltage and frequency are modulated based on processing needs – see section 3.1. This requires a lot of very complex interaction between the analog and digital components to orchestrate dynamic power management at the SoC level. Needless to say, this is a very difficult task to verify on a digital simulator – so far in the industry there is very little support to verify dynamic power management. This paper addresses the verification of Adaptive Dynamic Voltage and Frequency Scaling (DV FS) as an application of the proposed DMS Verification methodology. See section 5 for details.

This paper will first introduce and propose a DMS Verification Methodology – section 2.2, followed by an introduction to the concept of dynamic power management – section 3.1. It will then apply DMS methodology to an SoC example for verifying Adaptive DVFS – section 5.

## 2 DIGITAL MIXED SIGNAL VERIFICATION

Digital Mixed Signal (DMS) methodology is based on the use of Real Number Modeling (RNM) to model analog components at the SoC level. With the help of RNM, users can perform verification of their analog or mixed-signal designs using discretely simulated real numbers that involves using only the digital solver. By avoiding traditional, slower analog simulation, intensive verification of mixed signal design can be performed in short period of time.

To meet the verification goals, certain amount of simulation data and data accuracy are required, e.g. a detailed analysis of an RF low noise amplifier requires very high simulation accuracy but a single RF sinusoid period might be sufficient. On the other hand, a pin connectivity check for a large digital block has an extremely low sensitivity towards accuracy but may require a long transient simulation time to cover all sorts of events and states.

Consequently, a long full-chip simulation run using highest level of simulation accuracy would be desirable. The limiting factor in this context is simulation performance. The only practical way around this problem is a hierarchical verification approach that uses different level of design abstractions for different verification goals. Real numbers modeling is an interesting add-on to classical mixed signal verification approaches, like a Verilog and Spice mixed signal simulation or a pure digital modeling of the analog block in the mixed signal design. The extremely high accuracy of traditional analog simulation is traded off for speed while still preserving enough accuracy to enable highly accurate interaction between digital and analog domain that is required for a full SoC level simulation.

The target audiences for DMS are analog, digital as well as mixed signal engineers seeking high performance mixed signal verification with the ability to:

- Perform high volume, digital-centric nightly regressions tests to verify their mixed signal SoCs

- Verifying Top-level SoCs that have a small to moderate amount of analog in the design

RNM also opens the possibility of linkage with other advanced verification techniques such as metrics driven and assertion-based verification without the difficulty of interfacing to the analog engine or defining new semantics to deal with analog values.

# 2.1 Real Number Modeling (RNM) for Digital Mixed Signal Simulation

The simulation approaches in analog and digital are fundamentally different due to the structure of the underlying equation system to solve. While the digital solver is solving logical expressions in a sequential manner based on triggering events, the analog simulator must solve the entire analog system matrix at every simulation step. Each element in the analog design can have an instantaneous influence on any other element in the matrix and vice versa. Thus, there is not an obvious signal flow in one or the other direction. Time and values are continuous. In digital, time and values are discrete. The solver can apply a well-defined scheme of signal flow and events to solve the system. RNM is a mixed approach borrowing concepts from both domains. The values are modeled as continuous floating-point (real) numbers to emulate the analog world. However, time is discrete, meaning the real signals change values based on discrete events. In this approach, we apply the signal flow concept, so that the digital engine is able to solve the RNM system without support of the analog solver. This guarantees a high simulation performance that is in the range of a normal digital simulation and orders of magnitudes higher than the analog simulation speed.

Real number modeling capabilities are supported in different standard HDL languages (ref. [7] for details):

- wreal ports in Verilog-AMS

- real in VHDL

- real in SystemVerilog

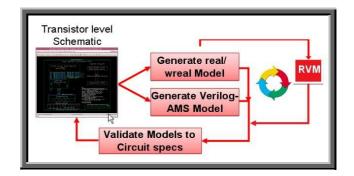

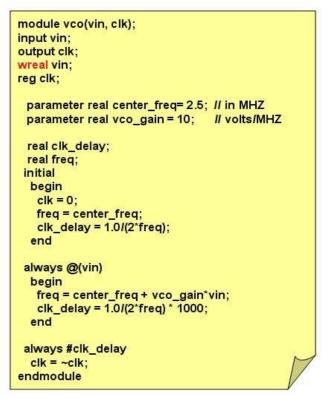

It is important to note that the real-wire (wreal) is defined only in the Verilog-AMS LRM. Thus, a wreal can only be used in a Verilog-AMS block. However, it is the digital kernel only that solves the wreal system. There are no major performance drawbacks when using these types of Verilog-AMS modules in a digital simulation context. A detailed understanding of the reference design – in most cases the transistor level circuit – is required for the model creation process. This includes transistor level simulations that are mostly driven from the simulation environment (ADE). Verilog-A models are also frequently used. On the other hand, the model is created for a specific verification purpose with its performance and accuracy requirements. While analog designers mainly own the first skill set, the mixed signal verification engineers understand the verification requirements better. Therefore, a close cooperation between both parties is needed. Figure 1 shows a simple example of RNM using Verilog-AMS wreals.

| we dule we col Al                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | C (DOUT ADD CK MDD MES)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| output [`Nbits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | OC (DOUT, AIN, CK, VDD, VSS);<br>-1 01 DOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | СК;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | AIN, VDD, VSS;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| wreal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | AIN,VDD,VSS;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Td=1n;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| real                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PerBit, VL, VH;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| integer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Dval;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| always begin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | // get dV per bit wrt supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DD-VSS) / ((1<<`Nbits)-1);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VL = VSS;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VH = VDD;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| @(VDD,VS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | S); // update if supply changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| alwaya @/CV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ) hagin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |