# Mixed ESL Power/Performance Estimation using SystemC/TLM2.0 Modeling and PwClkARCH Library

Antonio GENOV, NXP Semiconductors

Loic LECONTE, NXP Semiconductors

François VERDIER, University Cote d'Azur, CNRS, LEAT

## Agenda

CONFERENCE AND EXHIBITION

EURO

#### Automotive multimedia

- Feel at home on the road

- Complex SoCs for simplification of in-car media entertainment and mobile devices connection

- Strong relation between Comfort and Power consumption

- Each Watt counts ...

#### Context

Power-aware designs era

Increasing SoC performances?!

Great, but at what price?

Insufficient early stage architecture investigation capabilities

- Architecture power waste

- Increased production cost and time-to-market period

- Architecture definition tremendous Power/Perf trade-off impact It is always good to make abstractions ...

DESIGN AND VERIFICATION

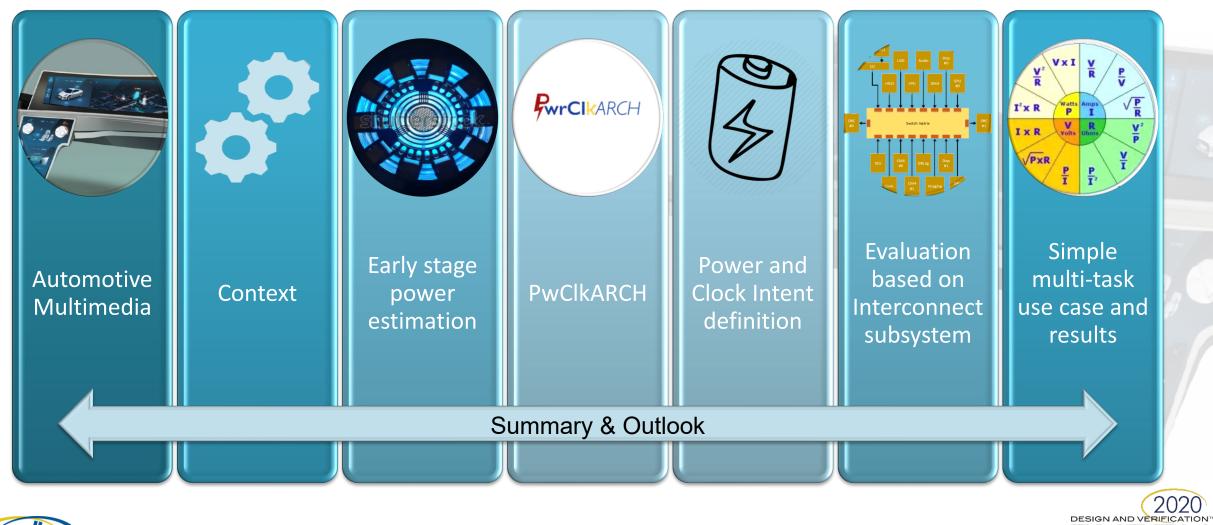

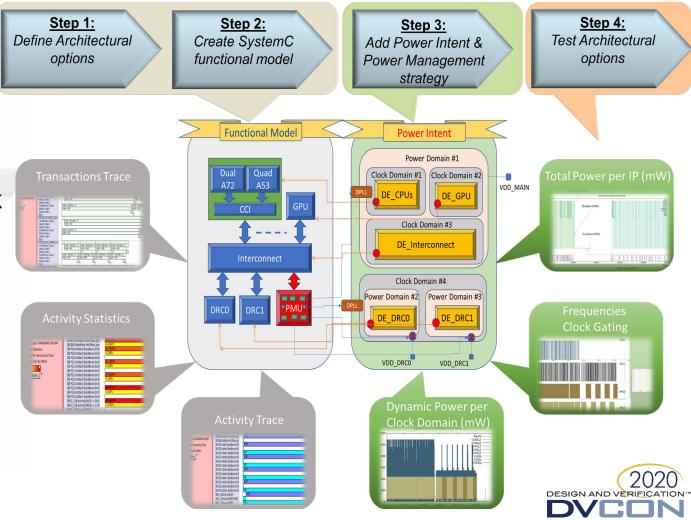

# Early Stage power estimation

#### • What?

- Power estimation in the very first stages of Design Flow (before RTL)

- DYNAMICALLY estimate power on complex use cases

#### • Why?

- Study different architecture options from beginning

- Creating references for developers

- Catching/Avoiding bugs earlier in the flow

- Reduce design iterations

#### • How?

- High-Level Virtual Prototyping using SystemC/TLM2.0 for behavioral/communication model

- Using PwClkARCH library for power intent description

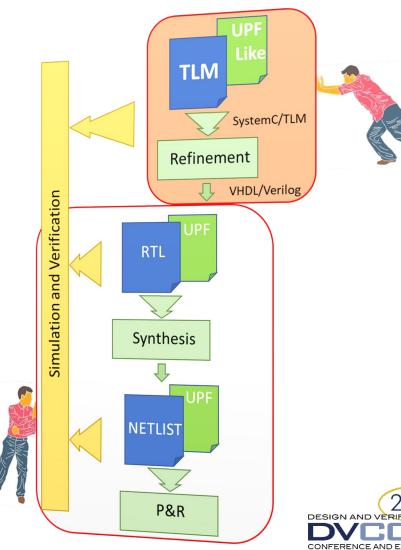

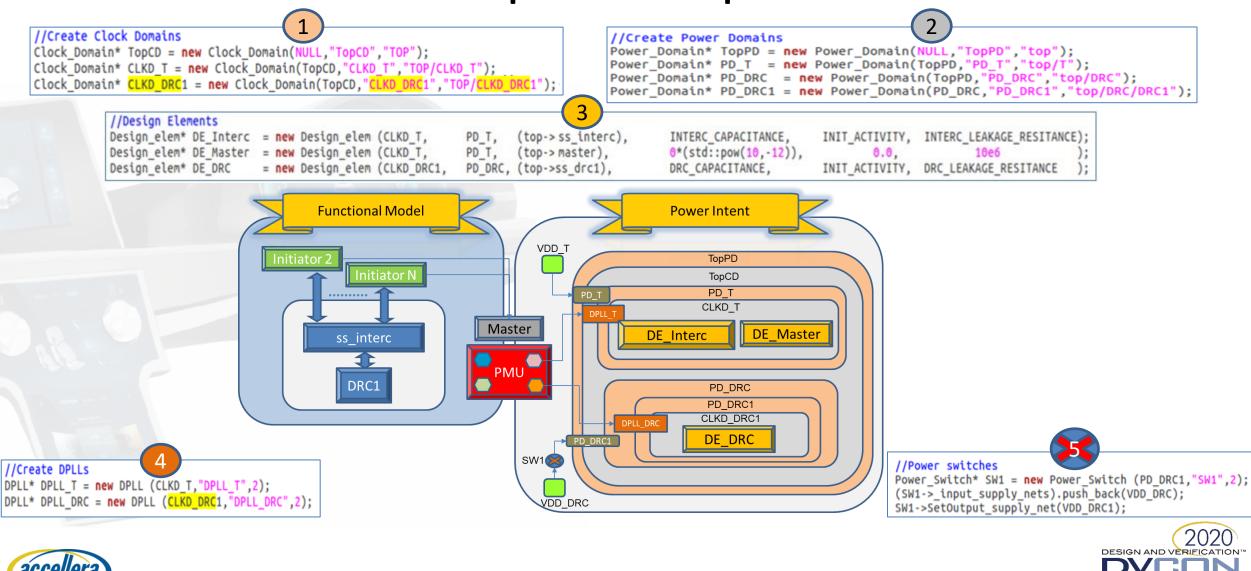

# **PwClkARCH** - semantics

- C++ classes and SystemC/TLM modules

- UPF-based high-level approach

- Design elements, power state table, power switches, supply nets

- Added clock tree description

- External clocks, generated clocks, DPLLs, clock state table, clock managers

- Power and Clock domains

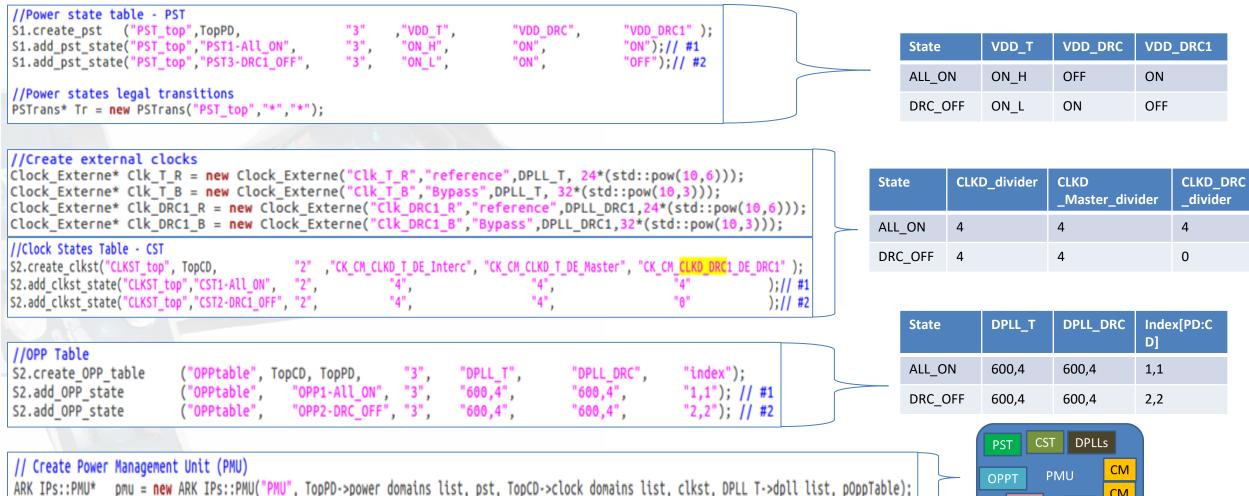

- Power management

- OPP Table, Clock gating, Auto clock gating, Power gating, DVFS

# PwClkARCH - power management and estimation

- Advantages:

- Functional model / Power intent separation

- Parallel DYNAMIC Co-simulation

- Mixed Perf/Power estimation framework

- Test power reduction technics early in the flow – (Power/Clock gating, DVFS)

- Other existing solutions

- not easily applicable and they lack of precise power reduction technics mechanisms at high abstraction level.

#### Simple example

© Accellera

SYSTEMS INITIATIVE

CONFERENCE AND EXHIBITION

#### Tables

CM

2020

DESIGN AND VERIFICATION

CONFERENCE AND EXHIBITION

ELROP

CM

ΡM

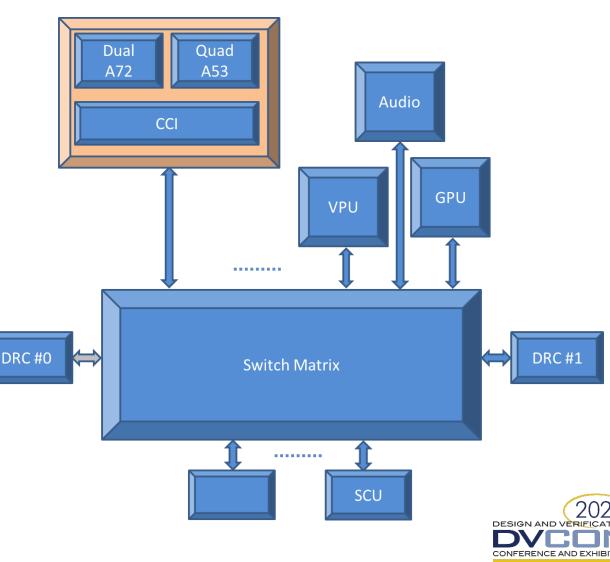

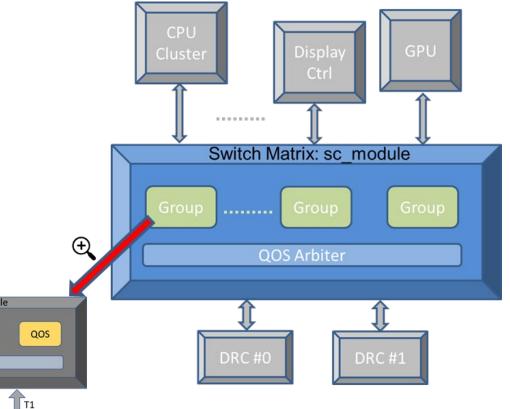

## Evaluation - based on Interconnect subsystem

- Each device in i.MX8 family has:

- 1x Switch matrix where all subsystems are plugged-in

- Functional model is targeting both performance and power consumption

- SCU (System Control Unit)

- Handling reset, clock and power control

- Those policies are modeled using PwClkARCH

- 1x or 2x DRAM controller(s)

- All devices in i.MX8 family are following the same structure

- Subsystems are scaled or replaced

## Evaluation - based on Interconnect subsystem

- Switch Matrix (SM)

- Contains a large number of complex sub-blocks

- Manages QoS of in-coming transactions

- Apply Multi-level QoS based arbitration between subsystems

- Handled interleaving to DRCs and routing system accesses

- Executes multiple scheduling algorithms to assure optimal memory usage and performance

QOS

Little Arbiter

= 1x voltage domain – low-power support

QOS

- ~ 5x power domain

- > 25 clock domains HW auto clock gating

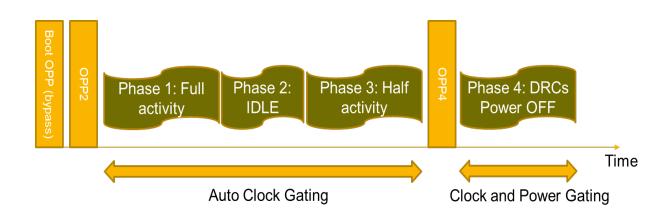

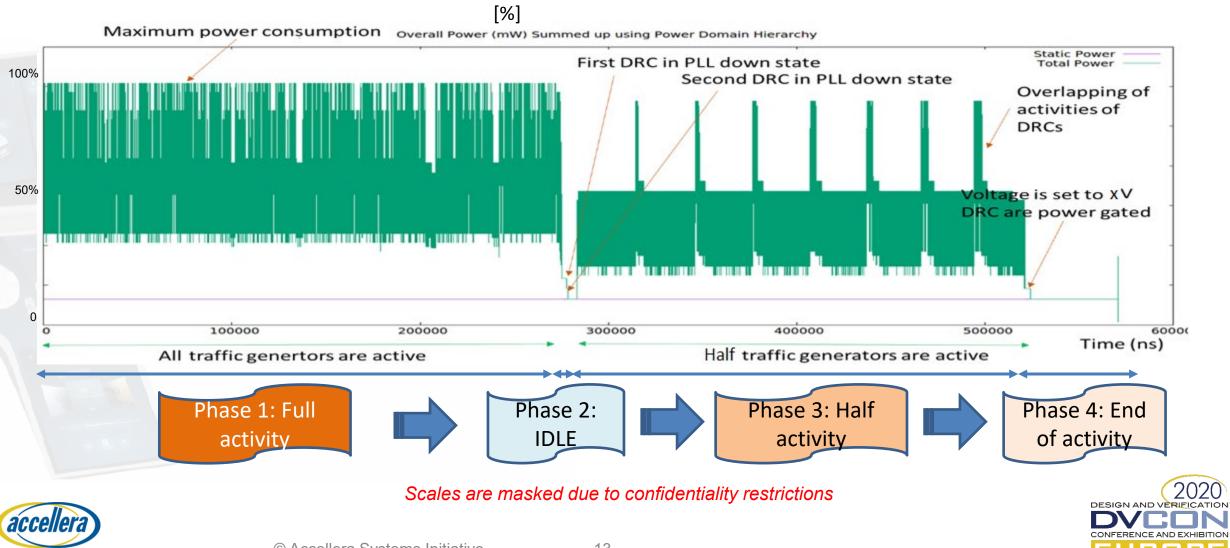

# Simple multi-task use case - with power management

- Full activity all Switch Matrix blocks and the 2 DRCs are active

- IDLE no activity clock gating (all clock domains in the Switch Matrix and those for DRCs)

- Half activity half of the Switch Matrix is active and only 1 DRC is active at a time

- Power OFF end of activity Clock gating, Low-power mode for Switch Matrix and DRC power gating

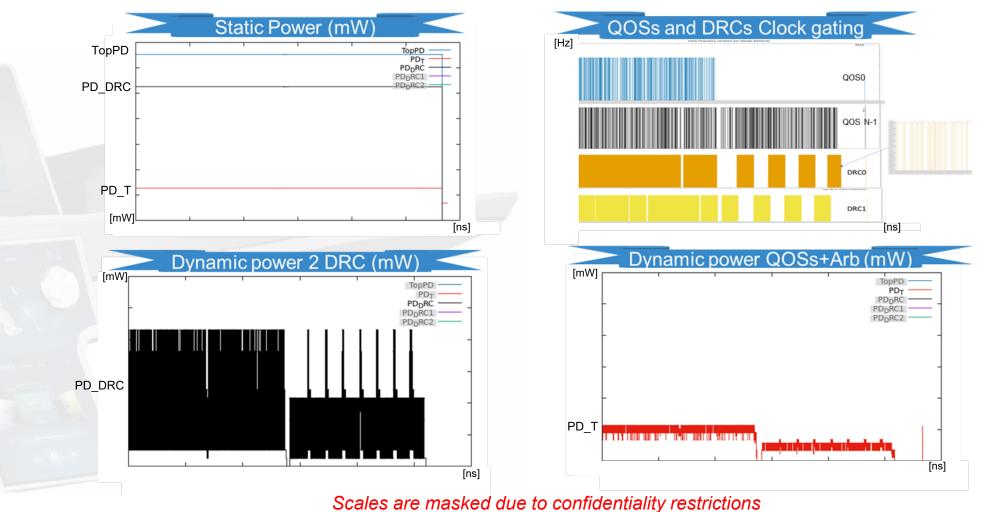

#### **Results - Total Power**

SYSTEMS INITIATIVE

#### **Results - Observations**

DESIGN AND VERIFICATION

CONFERENCE AND EXHIBITION

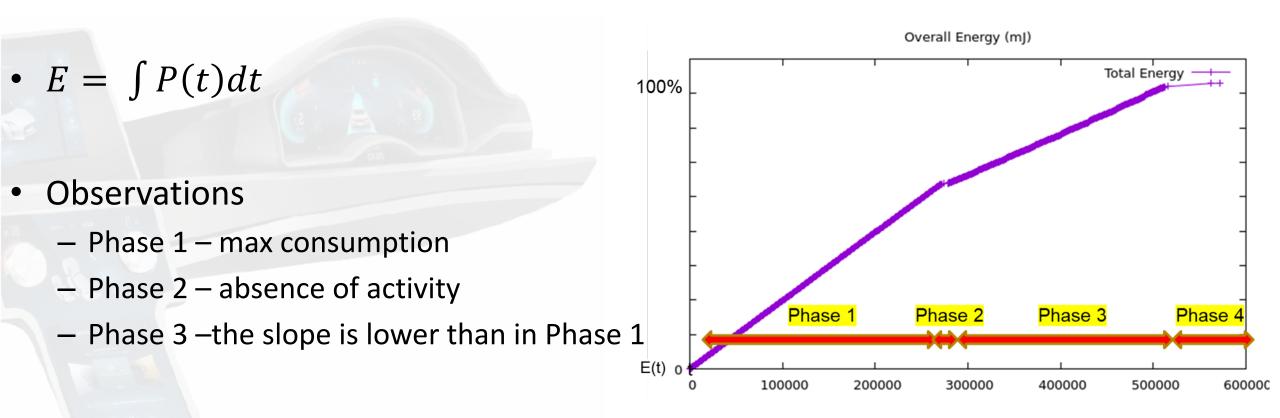

## **Results - Overall energy**

Scales are masked due to confidentiality restrictions

#### **Results - Correlation**

| Subsystems power contribution | Simulation/Silicon power measurements correlation |

|-------------------------------|---------------------------------------------------|

| Interconnect dynamic power    | 95%                                               |

| Interconnect static power     | 97%                                               |

| 2 DRC dynamic power           | 95%                                               |

| 2 DRC static power            | 97%                                               |

| Total power under 1.1V        | 95-97%                                            |

Values are masked due to confidentiality restrictions

© Accellera Systems Initiative

# Summary & Outlook

- Based on initial assessment, we are convinced by PwClkARCH technology and we continue to support and test it with different use cases and silicon measurements comparison.

- It would be very interesting to integrate this technology into an industrialized EDA.

- Our second DVCon2020 paper presents some additional use case simulations and methodology enhancements.

- "Timing-Aware high level power estimation of industrial interconnect module" (presented by Amal Ben Ameur)

#### Thank you!

Q&A