# Metric Driven Mixed-Signal Verification Methodology and Practices for Complex Mixed-signal ASSPs

Frank Yang; Andy Sha; Morton Zhao

Yanping Sha

Analog Devices, Beijing, China

Cadence design Systems, Beijing, China

## **Abstract**

Abstract - Most ASSPs today are mixed-signal systems and this higher level of integration means the verification of these ASSPs is becoming more and more complex. For the 'digital only' SOCs there already exists advanced verification methodologies are widely used throughout the industry i.e. VMM, UVM, metric driven verification (MDV). The push in verification is now to extend these advanced verification methodologies to be used in analog/mixed-signal ASSP verification as well.

A recent ASSP in ADI is an example of this trend. The ASSP was a true mixed signal development, incorporating a Cortex-M3 MCU with analog peripherals including, ADC, VDAC, IDAC and PLL etc. This paper will discuss how we implemented MDV for the mixed-signal ASSP, how we defined verification metrics for analog/mixed-signal blocks and how we built up the mixed-signal constrained random verification environment. Defining verification metrics for analog/mixed-signal blocks is a key common problem for mixed-signal MDV and a lot of the discussions will focus on this topic.

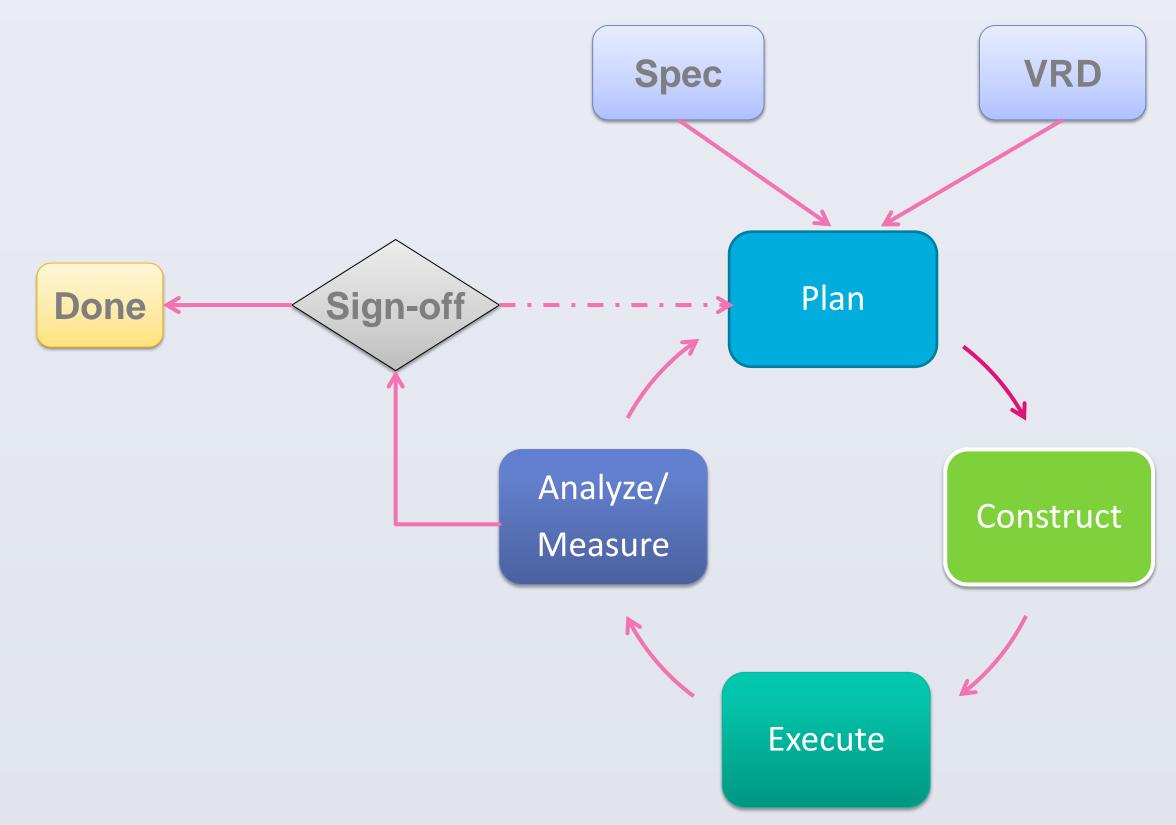

#### **Metric Driven Verification Flow**

The metric driven verification flow is shown as below.

## Verification Plan

We used Eplanner as the verification plan tool. An example is shown as below.

| ੋਂ <b>≰ vPlan</b>         | Goal Relativi<br>Grade | Refinement Mode: local Perspective: [automatic top] |  |  |

|---------------------------|------------------------|-----------------------------------------------------|--|--|

| Info                      |                        |                                                     |  |  |

| □··· 100% 1009            | % (OF) 2 - auto        | matic_top                                           |  |  |

| in 100% (0F) 2.1 – LDO1P8 |                        |                                                     |  |  |

| □ 100%                    | 100% (0F) 2            | .1.1 - Testcases                                    |  |  |

| □ 100%                    | 100% (OF)              | Ido_env_test_normal                                 |  |  |

|                           | 0% Passed              |                                                     |  |  |

| □ 100%                    | 100% (0F)              | Ido_env_test_sin                                    |  |  |

|                           | 0% Passed              | ldo_tests.ldo_env_test_sin                          |  |  |

| ⊟ 🔯 100%                  | 100% (0F)              | Ido_env_test_power_on                               |  |  |

|                           | 10% Passed             | ldo_tests.ldo_env_test_power_on                     |  |  |

| □ □ 100%                  | 100% (0F) 2            | .1.2 – Metrics                                      |  |  |

| □ 100%                    | (no checks)            | 2.1.2.1 - Function Coverage                         |  |  |

|                           | (no checks)            | power down function check                           |  |  |

|                           | 10% (no checks)        | Trimming function check                             |  |  |

|                           | (no checks)            | power supply range function check                   |  |  |

| <b>.</b> ⊕ 10             | (no checks)            | loop stability function check                       |  |  |

| <b>.</b> ⊕ 10             | (no checks)            | abnormal input function check                       |  |  |

|                           | 10% (no checks)        | ready function check                                |  |  |

|                           | (no checks)            | startup function check                              |  |  |

|                           | 10% (no checks)        | power supply rejection function check               |  |  |

|                           | 0% (no checks)         | critical points voltage check                       |  |  |

| 100%                      | 100% (0F)              | 2.1.2.2 - Checker_Assertions                        |  |  |

|                           | 100% (OF)              | Ido_pd_assertion                                    |  |  |

|                           | 100% (OF)              | ldo_trim_assertion                                  |  |  |

|                           | 100% (OF)              | ldo_line_regulation_assertion                       |  |  |

|                           | 100% (OF)              | Ido_loop_stability assertion                        |  |  |

|                           | 100% (OF)              | Ido_abnormal input assertion                        |  |  |

|                           | 100% (OF)              | ldo_ready_time assertion                            |  |  |

|                           | 100% (OF)              | Ido_enable time assertion                           |  |  |

|                           | 100% (OF)              | ldo power supply rejection assertion                |  |  |

| <u>+</u>                  | 100% (OF)              | ldo_critical points voltage assertion               |  |  |

## UVM Verification Environment Build Up

Some simple real-life UVM code is shown as blow.

```

// Integration for UVM-compliant Program block

// Interfaces

`include "mstr_slv_intfs.incl"

module ldo_env_tb_mod; //integration module

`include "uvm_macros.svh"

include "ldo_env_env.sv"

`include "ldo_env_test.sv"

// All interfaces

typedef virtual ldo_magt_if v_if1;

typedef virtual ldo_sagt_if v_if2;

typedef virtual analog_stim_if v_if3;

// Configure TB / Run Test

initial begin

uvm_config_db #(v_if1)::set(null, "", "mst_if", u_ldo_tb_sv.mst_if);

uvm_config_db #(v_if2)::set(null,"","slv_if",u_ldo_tb_sv.slv_if);

uvm_config_db #(v_if3)::set(null, "*.x_analog_stim_agt0", "analog_agt_if",

u_ldo_tb_sv.x_analog_stim_if0);

uvm_config_db #(v_if3)::set(null,"*.x_analog_stim_agt1","analog_agt_if",

u_ldo_tb_sv.x_analog_stim_if1);

run_test();

endmodule: ldo_env_tb_mod

```

### Analog/MS verification metric definition and implementation

We defined the following types of analog/mixed-signal verification metrics.

#### Real number analog assertions

The following table shows the features which are suitable to use real number analog assertions to define metrics.

| Features                  | Detailed Features and Examples             |                              |

|---------------------------|--------------------------------------------|------------------------------|

| Timing                    | Settling time, none-overlap signals timing |                              |

| Digital controlled analog | Voltage trimming                           | Reference/LDO/POR trip point |

| trimming                  |                                            | trimming                     |

|                           | Current trimming                           | Bias current trimming        |

|                           | Clock frequency                            | VCO/Oscillator trimming      |

|                           | trimming                                   |                              |

| Digital assisted analog   | ADC offset/gain calibration                |                              |

| calibration               | DAC offset/gain calibration                |                              |

| Algorithm                 | ADC chop, average, redundant, dither       |                              |

| Critical signal monitors  | Monitor power supply, reference and bias   |                              |

The following code shows a real number analog assertion example: LDO power supply rejection performance check.

#### • Real Number Functional Coverage

The following table shows the features which are suitable to use real number function coverage to define metrics.

| Features              | <b>Detailed Features and Examples</b> |

|-----------------------|---------------------------------------|

| Voltage range         | ADC input voltage range               |

|                       | DAC output voltage range              |

|                       | Voltage reference range               |

| <b>Current range</b>  | Bias current range                    |

| Clock frequency range | PLL VCO clock frequency range         |

|                       | PLL input reference clock range       |

The system verilog real number functional coverage code for ADC input range is shown as below.

```

real ain_r

covergroup real_bin_cg

option.per_instance = 1

adc in range : coverpoint ain r {

= {<mark>0</mark>};

bins HalfScale = {1.25};

// half scale input

bins FullScale = \{2.5\};

bins OverFlow

bins ain_rangel = \{[0.1 : 0.25]\}; // 0.1-0.25

bins ain_range2 = \{[0.25:0.5]\}; // 0.25-0.5

bins ain_range3 = \{[0.5 : 0.75]\}; // 0.5-0.75

bins ain_range4 = \{[0.75 : 1.0]\}; // 0.75-1.0

bins ain_range5 = {[1.0 : 1.25 ]}; // 1.0-1.25

bins ain_range6 = \{[1.25 : 1.5]\}; // 1.25-1.5

bins ain_range7 = {[1.5 : 1.75 ]}; // 1.5-1.75

bins ain_range8 = {[1.75 : 2.0 ]}; // 1.75-2.0

bins ain_range9 = \{[2.0 : 2.25]\}; // 2.0-2.25

bins ain_range10 = {[2.25 : 2.5 ]}; // 2.25-2.5

endgroup : real_bin_cg

```

## Memery mapped register function coverage

Function coverage of memory mapped register is defined to cover the function of each bit of memory mapped register.

## • Toggle coverage of analog/digital interface signals

The toggle coverage of analog/digital interface signals is defined to cover the different control sequences.

## Code coverage

Code coverage of RTL in analog control blocks.

# Conclusions

Implementing these advanced metric driven mixed-signal verification techniques on our recent ASSP development was a great success and resulted in first pass silicon success. The initial revision of silicon was successfully sampled to our customers.

## <u>Acknowledgements</u>

Thank you to David Brownell for reviewing and polishing this paper and to Bridge Dowling for editing and formatting help.

## Contacts

We can be contacted by email <a href="mailto:Frank.Yang@analog.com">Frank.Yang@analog.com</a> and Andy.Sha@analog.com