February 28 – March 1, 2012

#### Memory Debugging of Virtual Platforms

by

George F. Frazier

Neeti Bhatnagar

Qizhang Chao

Kathy Lang

Cadence Design Systems, Inc.

#### Virtual Prototypes (VP)

- VPs are models of systems that typically contain a hardware design and software.

- Embedded OS, device drivers, bare metal test programs, applications, etc.

- VPs model instructions on the processor(s) accurately so are appropriate for full scale pre-RTL software development.

- Types of software involved informs the debug strategy.

- Challenge is to create debug environments that provide a richness & visibility not available to environments that contain physical prototypes of the hardware.

- TLM standard can help.

### SystemC VPs

- A SystemC-based VP is a SystemC/TLM-based model of the hardware along with software.

- Hardware components are written in SystemC or at least wrapped in TLM 2.0 interfaces.

- Includes hardware such as processor models and memories along with SystemC/TLM implementations of peripherals.

- Embedded software such as an embedded OS, drivers, and application software.

- TLM standard helps in creation of rich debug environments for both HW and SW for VP-based systems.

### Role of Memory sub-systems in SystemC-based VPs

- Many possible memory implementations and configurations can exist.

- The program memory, data memory, and stack need not be stored in a single memory model.

- They can be stored in a single memory model but implemented with sparse memory or other advanced memory modeling techniques that are often predicated by performance.

- From a tooling perspective, we need a generic way to inspect and modify values of VP memories that is external to any implementation details of a particular system.

- This is where the TLM 2.0 standard assists us.

# TLM 2.0 functions for inspecting target values

| Function name   | description       | Has side effects? |

|-----------------|-------------------|-------------------|

| b_transport     | Blocking          | Yes               |

|                 | transport.        |                   |

| nb_transport_fw | Non-blocking      | Yes               |

|                 | forward transport |                   |

| nb_transport_bw | Non-blocking      | Yes               |

|                 | backward          |                   |

|                 | transport         |                   |

| transport_dbg   | Debug transport   | No                |

|                 | call              |                   |

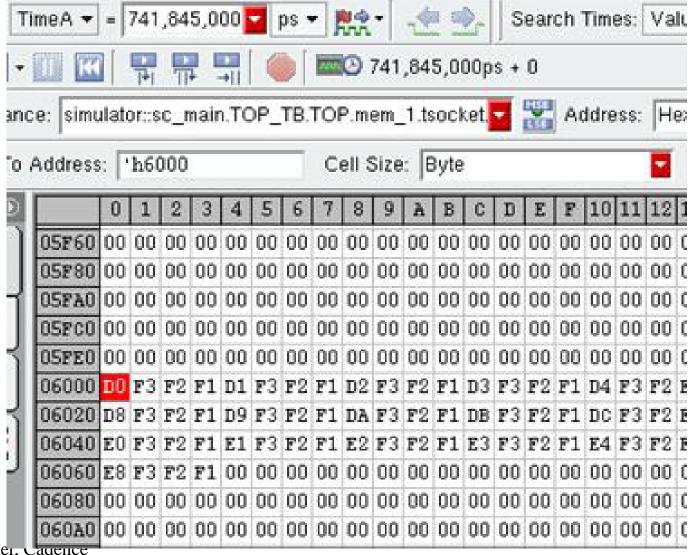

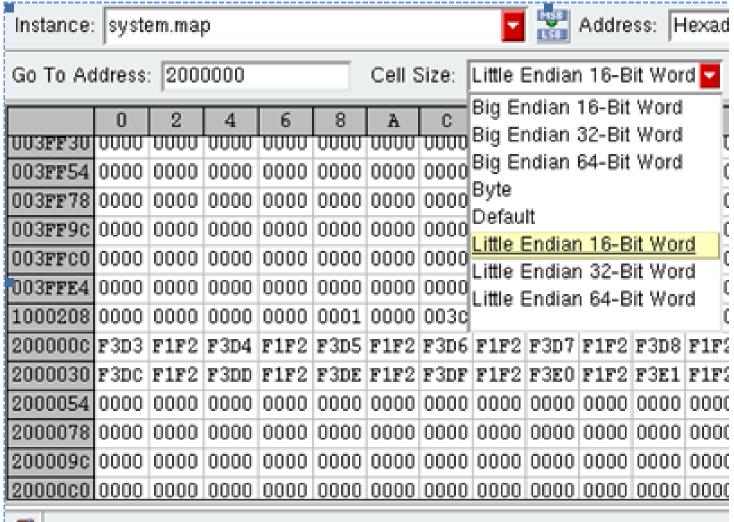

# Provisioning a Memory "view" with transport\_dbg

- If you know which blocks in a design represent memories, it is possible to collect the values of the memory for debugging purposes using transport\_dbg calls.

- This can be done without side effects or advancing simulation time, and without modifying a user design.

- Values can be collected and presented as a "memory view"

Memory "Viewer" provisioned by TLM target inspection

George Frazier, Cauence

#### **TLM VP that runs Android**

- Two ARM processor models (processor models were generated by ARM tools and have a TLM wrapper).

- A9 and M3.

- TLM Simple Memory (RAM).

- Devices connected to the bus.

- System Memory Map.

- Android Goldfish.

| Device name             | TLM Target        | Local start<br>address | Local end<br>address | System base address |

|-------------------------|-------------------|------------------------|----------------------|---------------------|

| ram                     | ram.tsocket       | 0                      | 0x5FFFFFF            | 0                   |

| Interrupt<br>controller | interrupt.tsocket | 0                      | 0xFFF                | FF00000             |

| timer                   | timer.tsocket     | 0                      | 0xFFF                | FF01000             |

| tty                     | tty0.tsocket      | 0                      | 0xFFF                | FF02000             |

| audio                   | audio.tsocket     | 0                      | 0xFFF                | FF03000             |

| Battery                 | battery.tsocket   | 0                      | 0xFFF                | FF04000             |

## Common Steps in VP development

- Choose your processors and how to model them (QEMU, Arm, Imperas, etc).

- Create SystemC peripherals as needed.

- Write drivers for any hardware peripherals you authored, if you are only extending a system you might only need drivers for new hardware blocks you added.

- Port embedded OS.

- Run the system, and test by running middleware on the OS.

#### Time to Debug!

```

Dee.Y'.;'+19VL0000e0: _$YER%?oy*v-K~?O401zSV-2g01; XA*_g1;2Ey.O E'-De6 DO

+U\...D0:xV3#;DX6E607E%e00 DX0

e) Ga (-b-AA*Das DD*DJ¥ D K;O D

RDSBT1Ê TODB%2eÊSDDÊDD1@~JDR$D

kÞL,∐

-686[5°D#88iip54nTÝ01xD0·Dw^áµk

>b\gIsRHEs7-a;o"i'f200Puut.

&A'U. = 01.1 ( c#~+~

>Y±&DÜ+yûsy'!(ng-

Eg<=DE-méricanG#fEA/c/4/20DM

‡ ZÕ[Ô 14, 'ÖÖ2AD...DUDD1M¥-0€1-

*3Déóibf« IDD3#!+!

:$iDÜDHO*s∢Cz¥D46″þ,*ÄDÌX*D[#

2000 + y 1 +0000cc \ omr 4 Y00 ; B

W-lyxEoxCzDha(±%(

ÖVÖña6ׯ⊟þköRÇ⊟•ò^T⊟áBoË□^>ñú

"ué"cOw7[,±+%ûV·=86bb6N62@1dæ84

ypgH°µ×k>XôfōIÎD>Ot#āc°6L×I£=10D*āp`[f€Sm µıpò°·y.,üLat.

00190J-0010004 && TOOV28... OSS; IDZ500; 6880H04885; , • 18n • -

et .£°K'DÜ×SNÞ9w×9z±ùX*DĬ-ps^ÖPt*DE»E-R.

```

#### **VP Debugging Terminology**

- Device drivers and embedded programs that run on the VP without an OS are called "bare metal" programs.

- Debugging a bare metal program is called "bare metal" debugging.

- If the debugger deals natively with OS constructs such as threads and signals it is "OS-aware."

- The following examples apply to "bare metal."

# Bare Metal debugging of VPs is a low visibility endeavor. TLM-based Memory Debug can help.

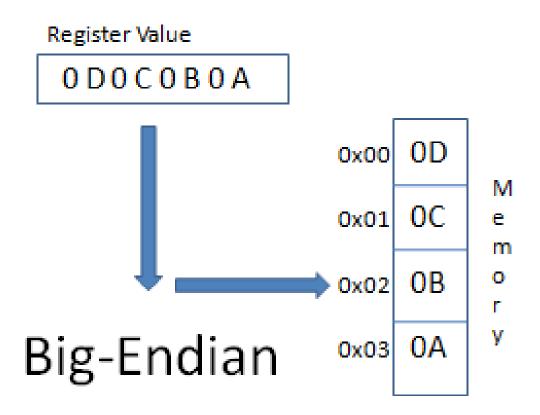

#### Finding an endianness mismatch

- In any SOC design, it is important that processors, peripherals, and the embedded SW agree on endianness of data items passed between components.

- Sometimes it can be tricky to keep this straight.

- Tracking down an endianness mismatch can be very challenging.

### **Big Endian**

George Frazier, Cadence

### Configuring endianness for ARM A9s

- At least 2 different ways.

- When we generated the A9 processor, hostendianness of Linux was explicitly chosen (little endian).

- TLM standard suggests that for debug, choose endianness of host (LT models need to be fast). In this case both initiator and target share host endianness.

### On boot-up, the system crashed

- So early in boot process no traditional embedded software debugging even of assembly language is possible.

- Instead we investigated memory using TLMbased memory debug.

- Running the bare metal design, we noticed memory content register value was in big endian.

#### **Endian display in Memory View**

# Led to investigation of other ways to set endianness for the ARM A9

Arm documentation pointed to assembly language code that sets the core to big-endian.

MRC p15, 0, r0, c1, c0, 0 ORR r0, r0, #0xf8 MCR p15, 0, r0, c1, c0, 0

- •This was from code we inherited.

- •TLM-based debug gathers the memory values of the RAM and supports displays in different endianness.

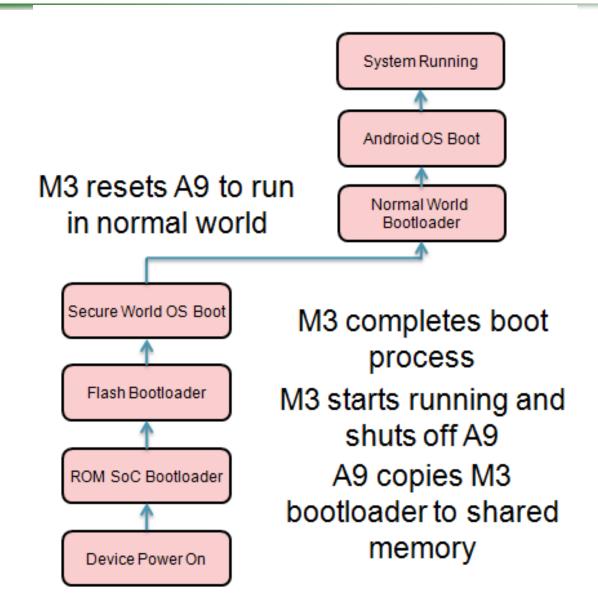

### Finding problems in dualprocessor boot up

- This issue related to the multiphase boot sequence for dual ARM Cores.

- We were working from a spec from ARM that explains how the bootup works.

George Frazier, Cadence 21 of 25

### If the boot fails, the system freezes

- Early access to memory contents invaluable in this case.

- We examined the memory in the phase where A9 boots and copies the rest of the bootup code into memory so the M3 can read it.

- Only part of the bootup code made it.

#### Possible Causes of the Problem

- Problem in synchronization of accesses to the RAM being used by the A9 and M3.

- A problem with the multi-processor communication hardware block.

- A problem with the interrupt configuration.

- Without TLM Memory debug, you would have to instrument the memory to dump its values and change the model.

# An ARM General Interrupt Controller programming error.

- We used values in the address registers to identify the location of the bootup code in RAM.

- Even with this, we had to go down several fruitless paths.

- By tracing interrupt signals, we found a missing signal which led to discovery of an error in GIC (Generic Interrupt Controller) programming.

- INTS[0] corresponds to GIC Interrupt ID 32, but the software wrote to a different bit in the register.

## Redirecting Android kernel messages to memory.

- Possible using TLM Memory Debug.

- Very early in the Android boot before the TTY is initialized, "printk" messages sit in the ring buffer in memory.

- Ring buffer is a static array:

```

static char __log_buf[__LOG_BUF_LEN];

static char *log_buf = __log_buf;

```

#### Conclusion

- Debugging a SystemC-based VP can be a difficult challenge involving problems caused by the hardware models, the low-level software, the application software, or all three.

- TLM standard provides a powerful methodology for creating, via the transport\_dbg interface, TLM-based debug tools such as Memory Debug.