### May the powers be with you! – Unleashing powerful new features in UPF IEEE 1801

Srinivasan Venkataramanan, DV Consultant, VerifWorks LLC,

srini@verifworks.com,

Ajeetha Kumari, VerifWorks

Thejas @CVC

- Introduction

- Sample SoC, UPF basics

- Model Simstates

- Sim Reply control

- Sim Assertion Control

- Information Model In UPF

- Automating PST coverage closure

- Summary

# Introduction

- Low power requirements omnipresent now

- IEEE 1801 UPF a TCL based language to capture Low Power requirements

- Various levels of abstraction

- Various tools consume & update UPF code

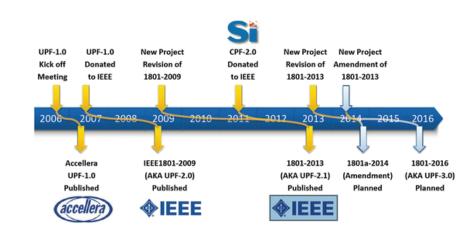

- UPF evolution:

- 1.0, 2.0, 2.1 and 3.0

- New features, enhancements, deprecations

- We highlight few key new features/powers of UPF 3.0

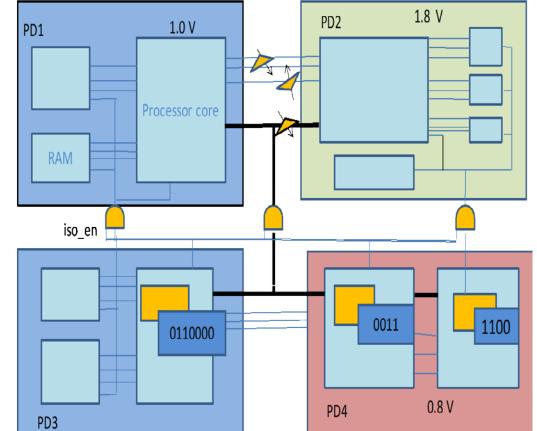

#### Concepts in Low Power DV

- Power Domains

- Isolation mechanism

- Level Shifters

- State Retention

- Power State Tables

Credits: Mentor Graphics

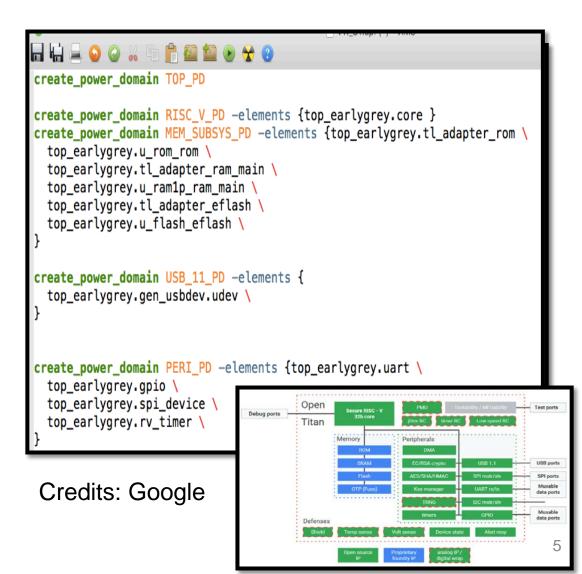

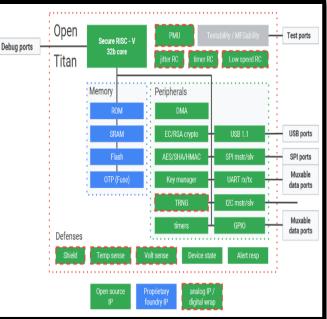

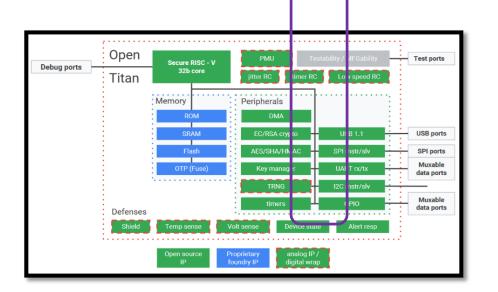

### Sample SoC – first-cut UPF

- Ref: Google's Opentitan RoT chip

- Listing power domains is easy

- Architecture

- Why that PD? different topic

- Coding them in UPF can be tedious

- First timers

- Too many options, verbose TCL

- We used a UPF generator

- DVCreate-LP

- List all hierarchies (upto a depth)

- Let users pick

### Power State Tables - PSTs

- Next step identify the necessary power strategies

- Power State Table (PST) necessary to arrive at appropriate strategies

- PST a detailed list of various modes in which the design is intended to be used.

|   | <u>Mode</u> | <u>RISC_V_PD</u> | <u>MEM_SUBS</u><br><u>YS_PD</u> | <u>PERI_PD</u> | <u>USB_11_PD</u> | TOP_PD |

|---|-------------|------------------|---------------------------------|----------------|------------------|--------|

|   | ALL_ON      | ON               | ON                              | ON             | ON               | ON     |

|   | LP0         | ON               | ON_LOW                          | ON_LOW         | ON_LOW           | ON     |

|   | LP1         | ON_LOW           | OFF                             | OFF            | ON_LOW           | ON     |

|   | SLEEP       | OFF              | OFF                             | OFF            | OFF              | ON     |

| ) |             |                  |                                 |                |                  |        |

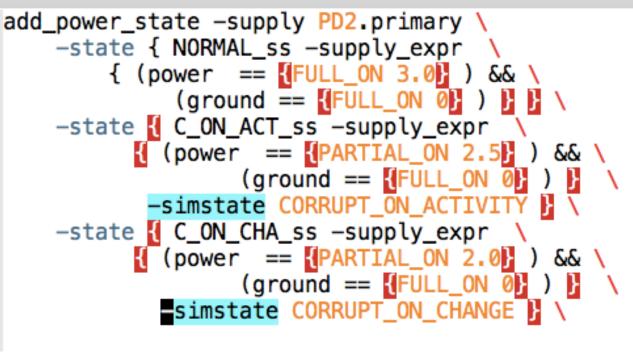

# Concept of SIMSTATE in UPF

- Simstate defines precise simulation semantics in a given power state.

- Used to describe the expected behavior of the cells connected to thi supply set.

- UPF 1.0 had basic support:

- NORMAL (When ON)

- CORRUPT (When OFF)

- Designs have more than the above two states:

- Normal as long as there is no new activity/change etc.

| CORRUPT_STATE_ON_CHANGE | Corrupt                                                                      | Norma                                                                        |  |  |

|-------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|

| NOT_NORMAL              | Deferred – tools may provide an<br>override mechanism, default ==<br>CORRUPT | Deferred – tools may provide an<br>override mechanism, default ==<br>CORRUPT |  |  |

SYSTEMS INITIATIVE

#### Power Mode changes in simulation

function bit **supply on** (string pad name, real value = 1.0; endfunction : supply on function bit supply\_off (string pad name); endfunction : supply\_off 16 glue\_logic g\_0(); 17 18 initial begin : supply\_init 19 int status: 20 status = supply\_on("VDDH", 1.8); 21 status = supply\_on("VSS", 0.0); 22 status = supply\_on("core\_0/VDD\_CPU", 1.8); 23 status = supply\_on("core\_0/VSS\_CPU", 0.0); 24 status = supply\_on("core\_1/VDD\_CPU", 1.8); 25 status = supply\_on("core\_1/VSS\_CPU", 0.0); 26 status = supply\_on("VSS\_IP1", 0.0); 27 status = supply\_on("VDD\_IP1", 1.08); 28 status = supply\_on("VSS\_IP1", 0.0); status = supply\_on("VDD\_IP2", 1.8); 29 30 status = supply\_on("VSS\_IP2", 0.0); 31 end : supply\_init

`g2u\_lp\_supply\_on ("VDD\_IP1", 1.08)

```

cgin

int status;

status = supply_on ("VDD_IP1", 1.08);

if (!status) begin

`uvm_error ("VDD_IP1",

""Unable to turn supply_on on given supply net, check net name")

end

end

```

Can be coded inside UVM SEQ

#### SIMSTATEs in waveform

• Mentor's Questa SIM

| <u>t</u> : 💙 | <pre>/cvc_ip_risc_w/du</pre>  | 121050       | Նեենենենեն | ****        |            | ****         |           | h           |            | ****        |              | hhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhh |               | <u>ሉ</u>  |

|--------------|-------------------------------|--------------|------------|-------------|------------|--------------|-----------|-------------|------------|-------------|--------------|--------------------------------------|---------------|-----------|

| ₽♦           | <pre>/cvc_lp_risc_tb/du</pre> | 12'hxxx      |            |             |            |              |           |             |            |             |              |                                      |               |           |

| ₽♦           | /cvc_lp_risc_tb/du            | 8'hxx        |            |             |            |              |           |             |            |             |              |                                      |               |           |

| ₽�           | /cvc_lp_risc_tb/du            | 8'hzz        |            |             |            |              |           |             |            |             |              |                                      |               |           |

| € 🔷          | /cvc_lp_risc_tb/du            | 8'h5d        |            |             |            |              |           |             |            |             |              |                                      |               |           |

| 4            | <pre>/cvc_lp_risc_tb/du</pre> | 1'hx         |            |             |            |              |           |             |            |             |              |                                      |               |           |

| - 🔻          | /cvc_ip_risc_w/au             | INX          |            |             |            |              |           |             | si         | m:/cvc lp : | risc tb/du   | t/RISC CORE                          | S/fast mode   | e @ 20528 |

| ₽�           | /cvc_lp_risc_tb/du            | NORMAL {{FU  | NORMAL     | {{FULL_ON ( | }{FULL_ON  | 1800000}}    |           |             |            | hx _ '_     | -            | -                                    | -             | -         |

| ₽.�          | /cvc_lp_risc_tb/du            | NORMAL {{FU  | NORMAL     | {{FULL_ON 0 | }{FULL_ON  | 1800000}}    |           |             |            |             |              |                                      |               |           |

| € 🔶          | /cvc_lp_risc_tb/du            | NORMAL {{{F  | NORMAL     | {{{FULL_ON  | 0}{FULL_ON | 1800000}} {{ | -11 NORMA | L} NORMAL { | 0 3 NORMAL | }{0 4 NORM  | AL} {0 5 COR | RUPT_ON_A                            | CTIVITY} {0 ( | 6 CORRUP  |

| € 🔶          | /cvc_lp_risc_tb/du            | OFF 32'h0000 | OFF 0      |             | FULL_C     | N 1800000    |           |             |            |             |              |                                      |               |           |

| € 🔶          | /cvc_lp_risc_tb/du            | FULL_ON 32'h | FULL_ON    | 0           |            |              |           |             |            |             |              |                                      |               |           |

| ə 🐴          | leve in rise th/du            |              |            | 00000       |            |              |           |             |            |             |              |                                      |               |           |

| € 🔶          | /cvc_lp_risc_tb/du            | FULL_ON 32'h | FULL_ON    | 1800000     |            |              |           |             |            |             |              |                                      |               |           |

| € 🔶          | /cvc_lp_risc_tb/du            | {FULL_ON 32' | {FULL_ON   | 10}{FULL_0  | N 600000}  |              |           |             |            |             |              |                                      |               |           |

| Ð            | <pre>/cvc_lp_risc_tb/du</pre> | {FULL_ON 32' | {FULL_ON   | 10}{FULL_O  | N 1800000} |              |           |             |            |             |              |                                      |               |           |

|              | Now                           | 28290 ns     |            | 1600        | )0 ns      | 1800         | )0 ns     | 2000        | )0 ns      | 2200        | )0 ns        | 2400                                 | )0 ns         | 26        |

|              | Curren 1                      | 0            |            |             |            |              |           |             |            |             |              |                                      |               |           |

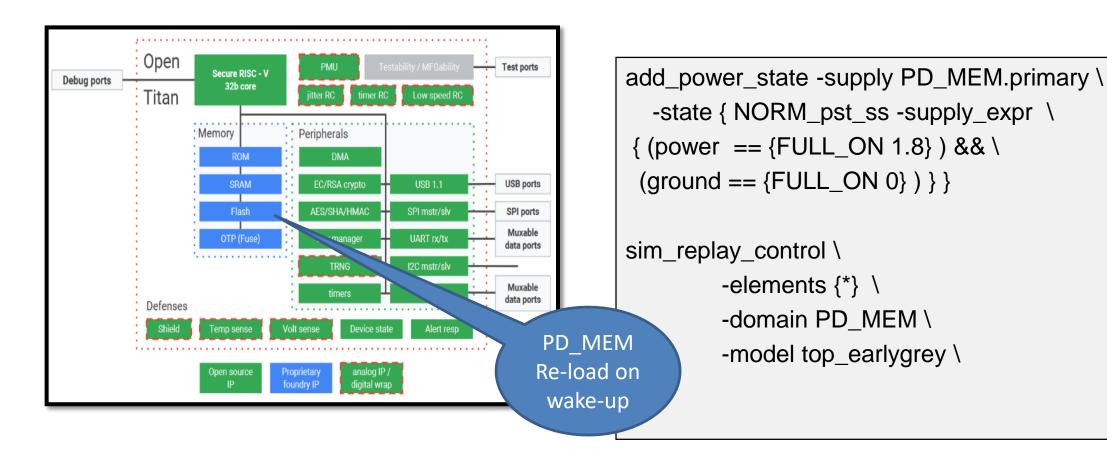

## Sim Reply Control

- Verilog semantics of *initial* block ensures that these blocks get executed at time 0 of a simulation

- What about  $ON \rightarrow OFF \rightarrow ON$  transition?

- Re-load memories (\$readmemh)

- Re-initialize PLL/ADC/DAC etc. parameters/states

- Verilog-only semantics do NOT do these  $\boldsymbol{\otimes}$

- sim\_replay\_control enables this modelling

### Sim Reply Control

© 2014-2019, www.verifworks.com

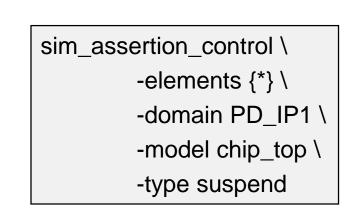

### Sim Assertion Control

- Consider the assertions inside power down logic, they need special care to ensure they do not provide false negatives.

- UPF 3.0 provides control over these assertions written in SVA.

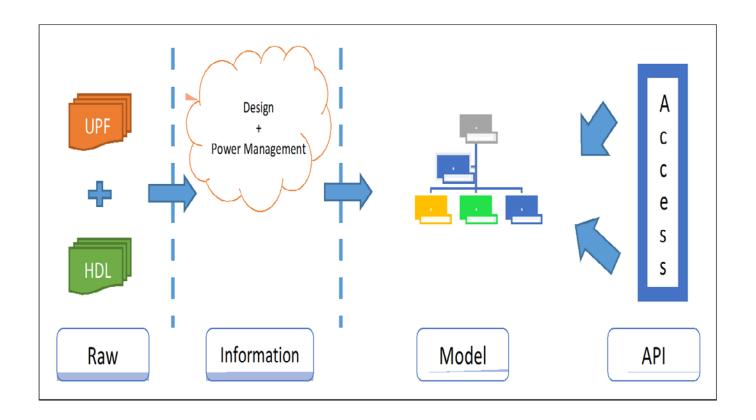

## Introduction – UPF information model

- Reflection APIs great for automation

- UPF has Information Model API

- Query:

- PDs

- Strategies/ISO/LS etc.

- PSTs

- Applications:

- Custom LP rule checker

- Automated PST closure etc.

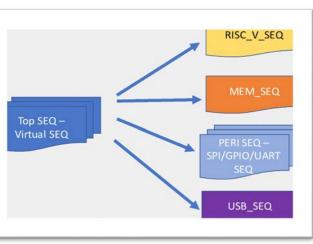

### Automating Power-coverage closure

- UVM is widely used in TB domain

- PSTs define a state-space for UVM to hit/cover

- Manual coding of UVM sequences to hit each state/transition

- Time consuming

- Error prone, debug cycles

- We used a tool to generate UVM sequences

- Inputs: UPF PST, config knobs, UVM base SEQ

- Use Information Model/custom API to query the PST

- Generate UVM sequences

#### Automating PST coverage closure

Top SEQ -

Virtual SEO

RISC\_V\_SEQ

MEM\_SEQ

PERI SEO

USB\_SEQ

| <u>Mode</u> | <u>RISC_V_PD</u> | <u>MEM_SUBS</u><br><u>YS_PD</u> | PERI_PD | USB_11_PD | <u>TOP_PD</u> |

|-------------|------------------|---------------------------------|---------|-----------|---------------|

| ALL_ON      | ON               | ON                              | ON      | ON        | ON            |

| LP0         | ON               | ON_LOW                          | ON_LOW  | ON_LOW    | ON            |

| LP1         | ON_LOW           | OFF                             | OFF     | ON_LOW    | ON            |

| SLEEP       | OFF              | OFF                             | OFF     | OFF       | ON            |

### UPF Information Model

Power D/U SEQ

Power D/U SED

## Summary, Q&A

- Generate first-cut UPF via tool

- SIMSTATE enhancements explained

- New simulation control features introduced with use cases

- Information model in UPF

- Programming API to Low Power structures

- Next generation innovation in LP Design Verification

- THANKS!

- Questions?