#### Maximize Vertical Reuse, Building Module to System Verification Environments with UVMe

Horace Chan PMC-Sierra Brian Vandegriend PMC-Sierra

Deepali Joshi PMC-Sierra

cādence<sup>™</sup>

Corey Goss Cadence

# What is vertical reuse?

SVSTEMS ΙΝΙΤΙΔΤ

- Horizontal Reuse

- Reuse VIP across different projects

- Vertical Reuse

- Reuse new VIP, sequences, checkers among module, subsystem and system testbenches in the same project

- Maximize Vertical Reuse

- Import full module testbenches to subsystem testbench

- Import full subsystem testbeches to system testbench

- Stitch subsystem testcases to create system testcase

# **Benefits of vertical reuse**

- Parallel development of all testbenches

- Plug-n-play architecture to integrate system level testbench from module and subsystem testbenches seamlessly

- Increase verification efficiency

- No duplication of development effort

- Less testbench code maintenance

- Changes in lower level testbench is propagated up automatically

- Better debug support from lower level testbench

- All lower level testbench the checkers and monitors are available

- Easier to move verification engineers among module, subsystems and system level testing

## The testbench architecture

SVSTEMS INITIAT

- 200+ Million Gates Design

- Partition into 10 subsystems and over 50 modules

- Over 20 subsystem and module testbenches

- Testbench implemented in Specman UVMe

All VIPs communicate using TLM interface

- The system testbench is integrated in 1 month

- 2-3 days to bring in a new subsystem testbench

- Early initial system level testing while subsystem testbench is still finalizing features

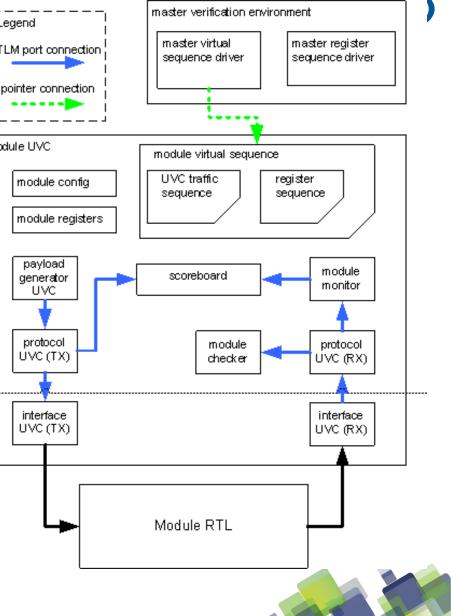

#### Legend master virtual TLM port connection sequence driver pointer connection module UVC module virtual sequence UVC traffic module config sequence module registers payload scoreboard generator UVC protocol module UVC (TX) checker interface UVC (TX) Module RTL

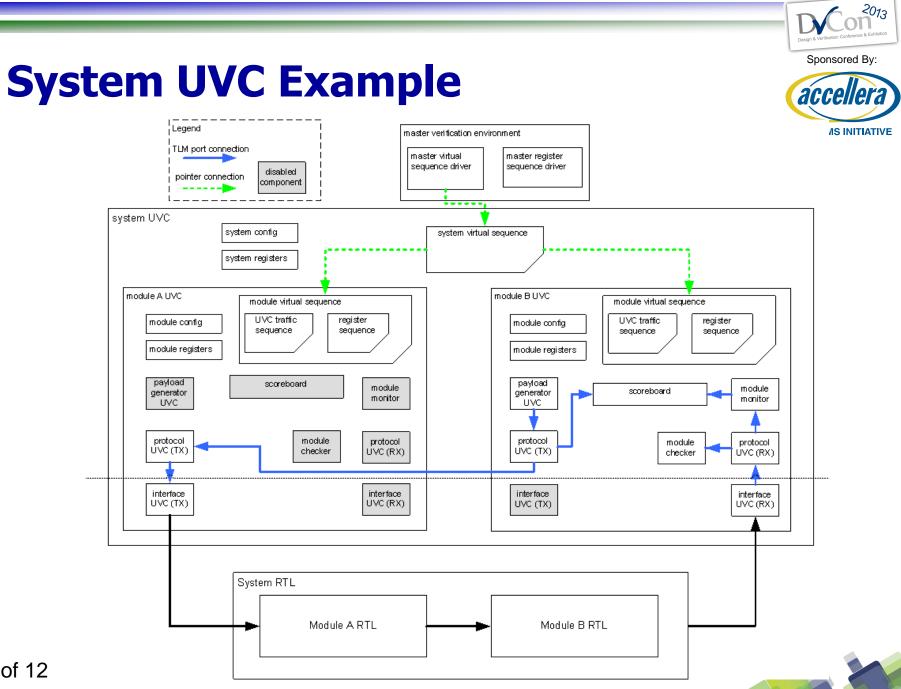

## System UVC Architecture

- Based on Cadence's System UVC Architecture

- Module UVC

- 1. No master virtual sequence or register sequence

- 2. UVCs are layered using TLM ports

- 3. Separate protocol UVCs from interface UVCs that drive the RTL signals

- System UVC is created by putting together multiple module UVCs

Sponsored By:

6 of 12

# **TLM port router**

- TLM port limitations:

- 1. TLM transport port does not support one-to-many binding

- 2. TLM analysis port always broadcast

- 3. Port binding is static in the simulation

- Solution: TLM port router to support dynamic manyto-many port binding with build-in routing table

2013

// sample implementation of TLM analysis port router template unit port router u of (<type>) { in\_ports : list of in interface\_port of tlm\_analysis of <type> is instance; out ports : list of out interface port of tlm analysis of <type> is instance; get channel id(tr : <type>) : uint is {}; set\_channel\_id(tr : <type>, cid : uint) is {} routing\_table : list of src\_route\_table\_entry\_s; }; struct dest\_route\_table\_entry\_s { enable : bool: port\_id : uint; channel id : uint; }; struct src\_route\_table\_entry\_s { enable : bool: port id : uint; channel\_id : uint; destinations : list of dest route table entry s;

};

#### Common UVC Configuration Control

- Unify data structure to control TLM port binding in module UVC

- Enable/disable each individual UVC, checker, scoreboard inside the module UVC

- Preserve all the binding information of the module UVC in system UVC

```

// sample common config control data structure definition

struct config_ctrl_s {

layer_name : layer_t;

enable : bool;

is_active : uvm_active_passive_t;

bind enable : bool;

```

struct port\_config\_ctrl\_s {

port\_name : port\_t; layer config : list of config ctrl s;

#### };

};

extend uvm\_env {

config\_ctrl\_table : list of port\_config\_ctrl\_s;

get\_uvc\_enable(port:port\_t, layer:layer\_t) : bool is {};

get\_uvc\_is\_active(port:port\_t, layer:layer\_t)

: uvm\_active\_passive\_t is {};

get\_uvc\_bind\_enable(port:port\_t, layer:layer\_t)

: uvm\_active\_passive\_t is {};

Sponsored By:

SVSTEMS INITIATIVE

aci

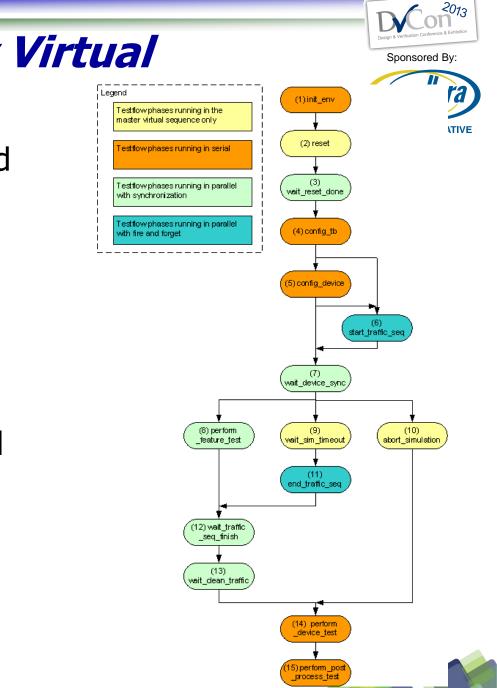

### Common Test Flow Virtual Sequence

- Testflow to co-ordinate and synchronize the behavior of imported module UVCs virtual sequences

- Testflow phases are implemented as empty TCM methods in the virtual sequence base class

- Module UVC fill in testflow phases using extension

# **Benefits and results**

SYSTEMS INITIATIVE

| Statistic Measure                | Previous<br>Project | Current<br>Project | Changes |

|----------------------------------|---------------------|--------------------|---------|

| Gates count                      | 60M                 | 200M               | +133%   |

| Total lines of code              | 575k                | 484k               | -16%    |

| System testbench line of code    | 324k                | 215k               | -34%    |

| % system testbench in total code | 56%                 | 44%                | -22%    |

| Gates verified per line of code  | 104k                | 413k               | +400%   |

- Less code, less bugs

- More reuse, higher quality of the code

- System level testcase as short as 20 lines of code

- Better system level debug support from subsystem and module level verification engineers

# **Challenges and Solutions**

- SYSTEMS INITIATIVE

- Revision conflict of common VIP used by the testbenches

- Solution:

- Freeze common VIP revision early

- Make sure new revision is backward compatible

- Co-ordinate upgrade of non-backward compatible VIP revision across all testbenches

- Poor quality code imported from lower level testbench impact simulation performance

- Solution:

- All testbenches should run profiling to identify CPU and memory bottleneck

- Frequent code review by experienced engineers

### **Future development**

SVSTEMS INITIAT

- Port the framework to SystemVerilog UVM

- SV does not support Aspect Oriented Programming (AOP)

- Possible to work around using design patterns

- More lines of code and complex TB structure

- More upfront planning for hooks and APIs

- More intrusive code maintenance

- More revision control discipline

- *e* constructs used in the framework

- *e* template -> SV parameterized type

- e keyed list -> SV associate array

- e predefined routines -> SV macro-based util libraries