# Low Power Verification With LDO

Shang-Wei Tu MediaTek Inc. +886-3-5670766#23493 kuma.tu@mediatek.com Amol Herlekar Synopsys Inc. +91-80-4018-8337 herlekar@synopsys.com Yu-Juei Chen MediaTek Inc. +886-3-5670766#22794 maso.chen@mediatek.com

Abstract-Low-Dropout Regulators or LDOs are used to regulate an output voltage that is powered from a higher input voltage. Hence, they are commonly used in advanced low power designs, especially for Dynamic Voltage and Frequency Scaling (DVFS). For low power verification engineers, modeling such an LDO is a huge problem. Although Unified Power Format (UPF) or IEEE-1801 standard [1] is defined and released for both the low power implementation and verification, UPF still does not provide a mechanism to model LDOs. Hence, verification engineers are left with no choice but to continue modeling the behavior in SystemVerilog. As the number of LDOs grows in the design, this challenge becomes manifold and can result in a number of verification holes. Also since the LDO is modeled in SystemVerilog, it effectively loses the UPF messaging and debug infrastructure. Besides, another problem verification engineers facing is the resolution mechanism that determines the state and voltage of the supply net when the net has multiple supply sources driving it. Although UPF provides *parallel*, *one\_hot*, and *parallel\_one\_hot* mechanism, these are not sufficient to exactly simulate all kinds of resolution.

In this paper, we share our experience on how we were able to model the LDO in UPF by extending the UPF command "*create\_power\_switch*" with some more option. In addition, we also share how we extended the UPF command "*create\_supply\_net -resolve*" to simulate the required resolution semantics. With the new syntaxes, we are able to model the LDOs and the supply net resolution easily and more accurately.

## I. INTRODUCTION

Optimizing power consumption has become equally important along with optimizing performance for mobile based SoCs. For applications like Internet of Things (IoT), minimizing power consumption is even more important than improving chip computing power, because changing battery could be very difficult and for some extreme cases, devices might require to be self-powered and operate with the very little energy. Hence, to aggressively minimize the power consumption, various power management schemes are used. IEEE-1801 or UPF is commonly adopted to capture the power intent of low power designs. However, adopting UPF into the IC design flow is not simple plug and play. Adopting UPF introduces extra design and verification efforts, since different power states could have different impact on design function and leakage power. Hence, we require a robust low power verification methodology to minimize the risk of failure of low power designs.

Low-Dropout Regulators or LDOs play an important role in the power management. LDOs are used to regulate an output voltage that is powered from a higher input voltage. However, for low power verification engineers, modeling such an LDO is a huge problem. Before the advent of Unified Power Format (UPF) or IEEE-1801 standard, engineers had different ways to model the power management logic within the design. UPF solved that problem to a large extent and now engineers had an industry blessed standard, which could be used to capture the power intent. Unfortunately, UPF still does not provide a mechanism to model LDOs. So verification engineers are left with no choice but to continue to model the same in SystemVerilog. Now this is a challenging task because most of the supply network is captured in the UPF. So engineers have to make sure that LDO inputs in SystemVerilog are connect to and being driven by correct UPF nets and LDO output is connected to corresponding UPF nets. As the number of LDOs grows in the design, this challenge becomes manifold and can result in a number of verification holes. Also since the LDO is modeled in SystemVerilog, it effectively loses the UPF messaging and debug infrastructure.

Another problem verification engineers facing is related to the resolution mechanism that determines the state and voltage of the supply net when the net has multiple supply sources driving it. Although UPF provides *parallel*, *one\_hot* and *parallel\_one\_hot* mechanism, these are not sufficient to exactly simulate all kinds of resolution for real designs.

In this paper, we share our experience on how we were able to model the LDOs in UPF by extending the UPF command "create\_power\_switch" with some more option. Similarly, we also share how we extended the UPF command "create\_supply\_net -resolve" to simulate the required resolution semantics. We plan to submit these UPF

extensions to IEEE-1801 committee. With the new syntax, we are able to model the LDOs and the supply net resolution easily and more accurately and it helps to make our low power verification more robust removing various verification holes and instilling more confidence for us while signing off. With the new syntax, we are also able to specify all LDO output power states with "*create\_power\_switch*" command, and hence the simulator could automatically convert all these states into *covergroup* helping us to achieve comprehensive low power coverage [2].

This paper is organized as follows. Section II describes an example of an LDO and the UPF limitations in modeling LDOs. It also describes the supply net resolution challenges which cannot be resolved with *parallel/one\_hot/parallel\_one\_hot* resolution techniques. Section III details our previous solution for modeling the LDO in SystemVerilog and also captures the issues encountered with that methodology. In Section IV, the new UPF syntax is introduced and its benefits have been illustrated. Finally, Section V concludes this paper.

## II. EXAMPLE LDO DESIGN AND UPF LIMITATION FOR MODELING

#### A. LDO Design and the UPF Limitation

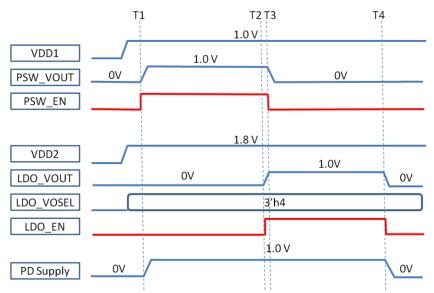

Given an LDO design, the I/O pins of the LDO are illustrated in **TABLE I** and the control sequence waveform is demonstrated in **Figure 1**. In short, the LDO will drive power when **LDO\_EN** is active (i.e. 1'b1) and will be OFF when **LDO\_EN** is inactive (i.e. 1'b0). The LDO output voltage will depend on the value of **LDO\_VOSEL** when **LDO\_EN** is active.

| <b>TABLE I.</b> Pin Specification of the example LDO. |        |           |                                                                                                                                |  |

|-------------------------------------------------------|--------|-----------|--------------------------------------------------------------------------------------------------------------------------------|--|

| Pin Name                                              | Туре   | Direction | Description                                                                                                                    |  |

| VDD                                                   | PG     | Input     | Power                                                                                                                          |  |

| VSS                                                   | PG     | Input     | Ground                                                                                                                         |  |

| LDO_VOUT                                              | PG     | Output    | LDO output voltage                                                                                                             |  |

| LDO_VOSEL[2:0]                                        | Signal | Input     | Output voltage level selection3'h0: 0.600V3'h4: 1.000V3'h1: 0.700V3'h5: 1.100V3'h2: 0.800V3'h6: 1.150V3'h3: 0.900V3'h7: 1.200V |  |

| LDO_EN                                                | Signal | Input     | Enable signal (Active high)                                                                                                    |  |

|           | T  | Г1 Т. | 2 1.8 V | 13   | Т4 |

|-----------|----|-------|---------|------|----|

| VDD       |    | 1.0V  |         | 1.2V |    |

| LDO_VOUT  | 0V |       | 0.6V    |      | ov |

| LDO_VOSEL |    | 3'h4  | 3'h0    | 3'h7 |    |

| LDO_EN    |    |       |         |      |    |

|           |    |       |         |      |    |

Figure 1. Control sequence waveform of the example LDO design.

To the best of the author's knowledge, there is no way such an LDO can be modeled using UPF commands for the power-aware simulation. The "create\_power\_switch" command cannot be used to model the voltage conversion from one voltage level to another. The voltage level of the input supply net and the output supply net used by "create\_power\_switch" command is the same when the power switch is ON and hence it cannot be used for modeling LDO scenarios where the output voltage is lesser that the input voltage.

## B. Real World Design and the Limitation of UPF Supply Resolution

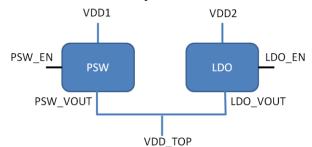

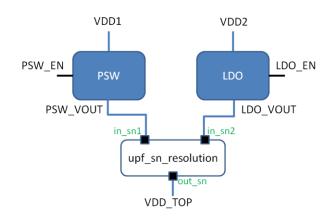

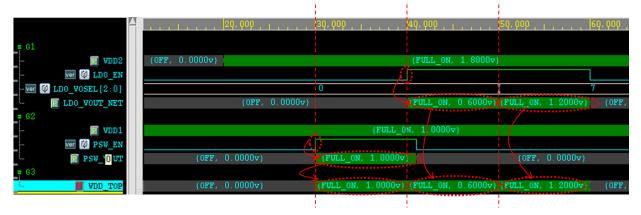

A power supply network as shown in **Figure 2** has been used in our real design. The output of the power switch and the LDO are shorted together and connected to the power domain's primary power. The driving strengths of the power switch and the LDO are similar, and either one can solely supply the domain logic operation. Ideally, either the power switch or the LDO will be enabled for normal operations. This can be handled by "create\_supply\_net - reslove one\_hot" semantics. The control sequence waveform is demonstrated in **Figure 3**. Although conceptually, either the power switch or the LDO will be ON, there will be some overlap between them as shown in **Figure 3**. In real scenario, the switching OFF of one and ON of another should not happen at the same time to take care of voltage spikes. Such control sequence is too risky when considering the circuit delay of the supply network. To avoid voltage spikes, first LDO should be turned ON and then the PSW should be turned OFF or vice-versa. In this way, any voltage spike during the transition between the power switch and the LDO can be avoided.

Figure 2. Power domain is supplied by either a power switch or a LDO.

Figure 3. Control sequence waveform for the example design in Figure 2.

For modeling the LDO design in **Figure 2** and the control sequence in **Figure 3**, we need a suitable resolution function in UPF. The current UPF supply resolution only supports "*one\_hot, parallel, parallel\_one\_hot*", but none can fulfill the requirements above. For "*one\_hot*" resolution, a supply net can be resolved to ON only when there is single supply source ON at any time. However, for the case above, there are certain overlapping scenarios between two supply sources, so this resolution technique is not very useful. For "*parallel*" resolution, a supply net can be resolved to ON when all supply sources are ON. Obviously, this resolution cannot be used either, since we also require ON resolution for a supply net when "either one" supply source is ON. For "*parallel\_one\_hot*" resolution, at most one root supply driver shall be ON at any particular time with all sources sharing that driver resolved using parallel resolution.

### III. SYSTEMVERILOG WORKAROUND SOLUTION

### A. SystemVerilog model for LDO Design

To simulate the LDO design illustrated in **TABLE I** and **Figure 1**, we use a SystemVerilog model in the absence of proper UPF support. The UPF snippet and the behavior model are illustrated in **Figure 4** and **5** respectively. In **Figure 4**, we only describe the input supply ports and nets of the LDO, and we use *connect\_supply\_net* command to connect **VDD** and **VSS** to the dummy supply ports **VDD\_to\_SV** and **VSS\_to\_SV** respectively. To get the information of the supply source on SystemVerilog model side, the dummy supply ports **VDD\_to\_SV** and **VSS\_to\_SV** are created in the behavior model. We need to have a UPF file for the LDO to make these connections. This UPF file may seem redundant, since all the power intent including supply ports **VDD** and **VSS** can be directly modeled in the SystemVerilog model. But this file is required to keep consistent macro/IP UPF integration style across the design. That is the UPF integrator can use *load\_upf* and *connect\_supply\_net* command for loading all the macros' and IPs' UPFs and connecting their input/output supplies respectively. Hence, creating the redundant LDO UPF file can make the UPF integration flow consistent.

| create_power_domain PD_LD0                                                             |

|----------------------------------------------------------------------------------------|

| create_supply_port VDD -direction in                                                   |

| create_supply_port VSS -direction in                                                   |

| create_supply_net VDD -domain PD_LD0                                                   |

| create_supply_net VSS -domain PD_LD0                                                   |

| connect_supply_net VDD -ports {VDD VDD_to_SV}                                          |

| <pre>connect_supply_net VSS -ports {VSS VSS_to_SV}</pre>                               |

| <pre>set_domain_supply_net PD_LD0 -primary_power_net VDD -primary_ground_net VSS</pre> |

Figure 4. Example UPF code for the LDO design in Section 2.

Once the UPF supplies are available in the SystemVerilog model, the supply switching and voltage conversion functionality of the LDO can be coded in the behavior model as illustrated in **Figure 5**. The value of LDO output **LDO\_VOUT** depends on **LDO\_EN** and **LDO\_VOSEL** signals which are already available in the behavior model. The dummy supply ports **VDD\_to\_SV** and **VSS\_to\_SV** should be declared as output ports with *supply\_net\_type* in the behavior model as recommended by IEEE. We should note that although the supply directions will have the same meaning if they are declared as *input* or *output* in the behavior model or defined with UPF "*create\_supply\_port -direction in/out*". But, if we declare the dummy supply ports as inputs, we will get multiple drivers (i.e., input supply port **VDD/VSS** defined in the UPF and input supply port **VDD\_to\_SV/VSS\_to\_SV** defined in the model) to the supply nets **VDD** and **VSS**. Hence, it is better to declare them as outputs. In addition, we also have `*ifdef POWER\_AWARE\_SIMULATION* for hiding all supplies for non-power-aware simulation, since the model will be used for both the power-aware simulation and non-power-aware simulation.

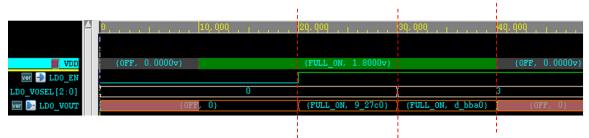

Although UPF has limitations for describing the supply switching and voltage conversion from a source supply net to a sink net, it is very easy and intuitional to model this behavior with SystemVerilog code. The example codes are demonstrated in **Figure 5** from Line 11 to 36. The ON or OFF state of **LDO\_VOUT** depends on the state of both **LDO\_EN** and **VDD\_to\_SV** which connects to **VDD**, and the voltage level of **LDO\_VOUT** depends on the state of **LDO\_EN** together with the value of **LDO\_VOSEL**. Since the unit of *voltage* of *supply\_net\_type* is  $\mu$ V, the real variable **LDO\_VOU\_r** needs to be multiplied by 10<sup>6</sup> and then assigned to **LDO\_VOUT.voltage** (Line 16 in **Figure 5**). The simulation waveform is demonstrated in **Figure 6**, and it shows the desired behavior. We can see that **LDO\_VOUT.state** is *FULL\_ON* only when **VDD.state** is *FULL\_ON* and **LDO\_EN** is 1'b1, and the value of **LDO\_VOUT.voltage** depends on the value of **LDO\_VOSEL** when **LDO\_EN** is 1'b1.

Although this solution works, the power intent is only partially captured in UPF. Since the UPF in **Figure 4** does not have any information of **LDO\_VOUT**, user can get confused while referring to UPF. Besides, the power state table cannot be captured completely due to the same limitation. Hence, although this solution can simulate the LDO perfectly, it is confusing to the UPF integrator and the verification engineer.

```

import UPF::*;

module LDO (

2

ifdef POWER AWARE SIMULATION

3

4

output supply_net_type VDD_to_SV,

output supply_net_type VSS_to_SV,

6

output supply net type LDO VOUT,

7

endif

input LDO_EN,

9

input [2:0] LDO_VOSEL

10

11

real LD0_VOUT_r;

12

ifdef POWER_AWARE_SIMULATION

13

always @(*) begin

14

if(VDD to SV.state == UPF::FULL ON && LDO EN==1'b1) begin

15

16

LD0_VOUT.state = UPF::FULL_ON;

LD0_V0UT.voltage = LD0_V0UT_r*1000000;

17

end

18

19

20

21

22

23

24

25

26

27

else begin

LD0 VOUT.state = UPF::0FF;

LD0 VOUT.voltage = 0;

end

end

endif

always @(*) begin

case (LD0_VOSEL)

3'h0: LD0 VOUT r = 0.6;

28

3'h1: LD0_VOUT_r = 0.7;

29

3'h2: LD0_V0UT_r = 0.8;

30

3'h3: LD0_VOUT_r = 0.9;

31

3'h4: LD0_VOUT_r = 1.0;

32

3'h5: LD0 VOUT r = 1.1;

33

3'h6: LD0 VOUT r = 1.15;

34

3'h7: LD0 VOUT r = 1.2;

35

endcase

36

end

37

38

endmodule

```

Figure 5. Example SystemVerilog behavior model for the LDO design in Section 2.

Figure 6. Simulation waveform of the LDO SystemVerilog model in Figure 5 and the LDO UPF in Figure 4.

## B. SystemVerilog model for Special Supply Resolution

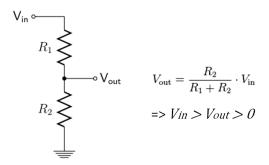

To conquer the UPF limitation for the supply net resolution mentioned in Section II B, a resolution module as demonstrated in **Figure 7** was created. Conceptually, the output supply net will be resolved to ON when "either" one of the source input supply net is ON. The output supply net is resolved to OFF when both input supply nets are OFF (Line 9 to 12). If one input supply net is ON and the other one is OFF, the output supply net will be resolved to ON or partial ON with the voltage level of the ON supply net (Line 28 to 35). However, if both input supply nets are ON or partial ON, we will resolve the output supply net to ON or partial ON and the output voltage level will be resolved to the lower one of the input supply nets (Line 14 to 16 and 23 to 26). For the case of either one input supply net partial ON, we will resolve the output supply net to the other input supply net (Line 17 to 22). This is reasonable. Since when we short two different voltage supplies together, there will be a large short circuit current from the higher

voltage source to the lower voltage source and the higher voltage source will drop the voltage level. However, in real world, there is always some resistance inside the voltage sources. Hence, if we short two different voltage sources, the real output voltage level will be less than the higher one and larger than the lower one. The result is governed by the Voltage divider rule as shown in **Figure 9**, and it is very easy to conclude that the output voltage level is between the higher one and the lower one if we analogues the higher voltage source and the lower one to *Vin* and ground in **Figure 9** respectively.

One thing we have to mention is that if there are more than two supply sources required to be resolved, we have to use multiple resolution modules to resolve all of them and the structure will be similar to a binary tree.

```

1 import UPF::*:

2

module upf_sn_resolution(

input supply_net_type in_sn1,

input supply_net_type in_sn2,

5

7

8

9

10

11

12

13

14

15

output supply_net_type out_sn);

(* vcs_always_on *)

always @(in_snl or in_sn2) begin

if ((in_sn1.state==UPF::OFF) && (in_sn2.state==UPF::OFF)) begin

out_sn.state = UPF::OFF;

out sn.voltage = 0.0;

end

else if((in_sn1.state!=UPF::OFF) && (in_sn2.state!=UPF::OFF)) begin

if (in_snl.state != UPF::FULL_ON && in_sn2.state != UPF::FULL_ON) begin

out_sn.state = in_snl.state;

16

17

18

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

out_sn.voltage = (in_sn1.voltage > in_sn2.voltage)? in_sn2.voltage:in_sn1.voltage;

end else if (in_snl.state != UPF::FULL_ON) begin

out sn.state = in sn2.state;

out_sn.voltage = in_sn2.voltage;

end else if (in_sn2.state != UPF::FULL_ON) begin

out_sn.state = in_snl.state;

out_sn.voltage = in_snl.voltage;

end else begin

out sn.state = in_snl.state;

out sn.voltage = (in sn1.voltage > in sn2.voltage)? in sn2.voltage:in sn1.voltage;

end

end

else if((in_snl.state==UPF::OFF) && (in_sn2.state!=UPF::OFF)) begin

out_sn.state = in_sn2.state;

out_sn.voltage = in_sn2.voltage;

end

else if((in snl.state!=UPF::OFF) && (in sn2.state==UPF::OFF)) begin

out_sn.state = in_snl.state;

out sn.voltage = in snl.voltage;

end

else begin

$display("Error! undefined resolution: in_sn1 %s in_sn2 %s %t",

38

in_sn1.state.name, in_sn2.state.name, $realtime);

39

end

end

<mark>e</mark>ndmodule

```

Figure 7. Supply resolution module for the requirement depicted in Figure 3.

Figure 9. Voltage divider rule.

The next step is to instantiate this module in RTL, and then connects the corresponding UPF source supply nets to the inputs and the output to the target supply net. Comparing to the origin supply network illustrated in **Figure 2**, the new modified supply network with the resolution module is illustrated in **Figure 10** below. Since it is not a good practice to modify the RTL to add the resolution module, we use SystemVerilog *bind* statement to bind the resolution module to the target scope. The example code is demonstrated in **Figure 11**.

Figure 10. Block diagram for the supply network depicted in Figure 2 with the supply resolution module.

Figure 11. Example code for binding the resolution module to top module.

The corresponding UPF code for the supply network in **Figure 10** is demonstrated in **Figure 12**. As shown in **Figure 12**, a dummy supply net **LDO\_VOUT\_NET** (Line 9) is created to connect output port of LDO **LDO\_VOUT** to the input of the resolution model (Line 17). The other input of the resolution model is connected to the output of the power switch (Line 17) through another dummy supply net **PSW\_VOUT**. Finally, the output of the resolution model is connected to the target supply net **VDD\_TOP** in UPF (Line 18). The power switch command (Line 24 to 29) is used to model the power switch functionality. The simulation waveform is demonstrated in **Figure 13**. From **Figure 13**, we can observe that the resolution model can resolve the supply correctly at time 30000 (only PSW ON), 40000 (both PSW and LDO ON), and 50000 (only LDO ON).

Although this solution works correctly, it is cumbersome when we adopt this solution into real project. Besides, it also makes the power intent partial and inadequate in UPF when user is not aware of the resolution function, and the UPF file could be difficult to maintain if there are multiple resolution modules instantiated.

| 1 create_power_domain PD_TOP                                                           |

|----------------------------------------------------------------------------------------|

| 2                                                                                      |

| -<br>3 create supply port VDD1                                                         |

| 4 create supply port VDD2                                                              |

| 5 create_supply port VSS                                                               |

| <pre>6 create_supply_net VDD1 -domain PD_TOP</pre>                                     |

| 7 create_supply_net VDD2 -domain PD_TOP                                                |

| <pre>8 create_supply_net PSW_VOUT -domain PD_TOP</pre>                                 |

| <pre>9 create_supply_net LD0_VOUT_NET -domain PD_TOP</pre>                             |

| 10 create_supply_net VDD_TOP -domain PD_TOP                                            |

| 11 create_supply_net VSS -domain PD_TOP                                                |

| 12                                                                                     |

| <pre>13 connect_supply_net VDD1 -ports VDD1</pre>                                      |

| <pre>14 connect_supply_net PSW_VOUT -ports sn_reso/in_sn1</pre>                        |

| <pre>15 load_upf LD0.upf -scope u_LD0</pre>                                            |

| <pre>16 connect_supply_net VDD2 -ports { VDD2 u_LD0/VDD }</pre>                        |

| <pre>17 connect_supply_net LD0_VOUT_NET -ports { u_LD0/LD0_VOUT sn_reso/in_sn2 }</pre> |

| <pre>18 connect_supply_net VDD_TOP -ports sn_reso/out_sn</pre>                         |

| <pre>19 connect_supply_net VSS -ports VSS</pre>                                        |

| 20                                                                                     |

| <pre>21 set_domain_supply_net PD_TOP -primary_power_net VDD_TOP \</pre>                |

| 22 -primary_ground_net VSS                                                             |

| 23                                                                                     |

| <pre>24 create_power_switch PSW -domain PD_TOP \</pre>                                 |

| <pre>25 -input_supply_port { vin VDD1 } \</pre>                                        |

| <pre>26 -output_supply_port { vout PSW_VOUT } \</pre>                                  |

| <pre>27 -control_port { psw_en PSW_EN } \</pre>                                        |

| <pre>28 -on_state { PSW_ON vin {psw_en} } \</pre>                                      |

| <pre>29 -off_state { PSW_OFF {!psw_en} }</pre>                                         |

Figure 12. Example UPF code for the supply network in Figure 10.

Figure 13. Simulation waveform of the example UPF code in Figure 12 with the resolution module.

# IV. PROPOSED UPF SOLUTION WITH REVISED SYNTAX

# A. Proposed UPF Syntax for Modeling LDO Design

LDO can actually be considered as a special power switch which can not only switch the voltage but also regulate its value based on the control signals. Is it possible to extend the UPF to model such a power switch? *create\_power\_switch* command already supports multiple ON states today and hence if we can associate every ON state with a voltage value, it will serve the purpose. Our proposed solution is extending *create\_power\_switch* command to add one argument *-output\_voltage* as follows:

create\_power\_switch switch\_name

[-output\_voltage {state\_name voltage\_value}]

With the proposed argument *-output\_voltage* for *create\_power\_switch* command, we can rewrite the LDO UPF demonstrated in **Figure 4** to the code demonstrated in **Figure 14**. The major benefit is that all the LDO power intent including the output supply **LDO\_VOUT** (Line 5, 8, and 12), the switching and voltage conversion functionality (Line 16 to 39), and the power state table (not demonstrated in **Figure 14**) can be described completely in the UPF file, so the behavior model can be simplified to an empty module with only input control signals. This solution is much better than the one mentioned in Section III A, and we can get exactly the same behavior as shown in **Figure 6** with the latest version of Synopsys power-aware simulator MVSIM NLP which supports the proposed new argument for *create\_power\_switch* command. In addition, the simulator can automatically convert all the control signals and switch states of the LDO into *covergroup* helping us to achieve comprehensive low power coverage [2].

create\_power\_domain PD\_LD0 3 create\_supply\_port VDD -direction in 4 create\_supply\_port VSS -direction in create\_supply\_port LD0\_VOUT -direction out 5 create\_supply\_net VDD -domain PD\_LDO create\_supply\_net VSS -domain PD\_LD0 create\_supply\_net LDO\_VOUT -domain PD\_LDO 10 connect\_supply\_net VDD -ports VDD 11 connect\_supply\_net VSS -ports VSS connect\_supply\_net LDO\_VOUT -ports LDO\_VOUT 12 13 14 set\_domain\_supply\_net PD\_LD0 -primary\_power\_net VDD -primary\_ground\_net VSS 15 16 create\_power\_switch PSW\_LD0 -domain PD\_LD0 \ 17 -input\_supply\_port { vin VDD } -output\_supply\_port { vout LD0\_VOUT } \ 18 19 -control\_port { en LD0\_EN } \ 20 -control\_port { sl0 LD0\_V0SEL[0] } 21 -control\_port { sl1 LD0\_V0SEL[1] } 22 23 -control\_port { sl2 LD0\_V0SEL[2] } \ -off\_state { LD0\_0FF {!en}} \ 24 -on\_state { LD0\_ST0 vin {en && !sl0 && !sl1 && !sl2}} \ 25 26 27 28 29 30 31 -on state { LDO ST1 vin {en && sl0 && !sl1 && !sl2}} on state { LD0\_ST2 vin {en && !sl0 && sl1 && !sl2}} on state { LDO ST3 vin {en && sl0 && sl1 && !sl2}} -on state { LDO ST4 vin {en && !sl0 && !sl1 && sl2}} -on state { LDO ST5 vin {en && sl0 && !sl1 && sl2}} -on state { LDO ST6 vin {en && !sl0 && sl1 && s12}} -on\_state { LDO\_ST7 vin {en && sl0 && sl1 && sl2}} \ 32 33 34 35 -output\_voltage { LD0\_ST0 0.6 } \ -output\_voltage { LD0\_ST1 0.7 } \ LD0\_ST2 0.8 } \ -output\_voltage { -output\_voltage { LD0\_ST3 0.9 } 36 -output\_voltage { LD0\_ST4 1.0 } \ LD0\_ST5 1.1 } \ 37 -output\_voltage { LD0 ST6 1.15 } -output voltage { LD0\_ST7 1.2 } 39 -output voltage { 10 41 ###port state and PST###

Figure 14. Example UPF code with proposed create\_power\_switch -output\_voltage command for the LDO design in Section 2.

#### B. Proposed UPF Syntax for Special Supply Resolution

To conquer the real supply resolution issue mentioned in Section II B (Figure 2 and 3), we propose new resolution mechanisms as shown below by extending UPF *create\_supply\_net* command:

create\_supply\_net net\_name

[-resolve <unresolved | one\_hot | parallel | parallel\_one\_hot | either | strong | weak>]

The details of the resolution mechanisms for *-resolve either*, *strong*, and *weak* are listed in **TABLE II**, **III**, and **IV** respectively. The difference between *-resolve strong* and *weak* is whether the output voltage is resolved to the higher one of the supply sources or the lower one when multiple supply sources are ON. The reason for providing these two resolution mechanisms is as mentioned in Section III B, the output voltage level will be between two supply sources when we short two supply sources, since the output voltage is governed by the Voltage divider rule. Hence, if someone prefers to simulate this design as the best case scenario, he can use *-resolve strong*. If some user prefers to simulate this design as the worst case scenario, he can use *-resolve weak*. The difference between *-resolve either* and *weak* is whether the output supply is resolved to *UNDETERMINED* or ON when one source supply is *UNDETERMINED* and the other one is ON. This is another best-case and worst-case scenario consideration.

| Supply<br>Source1 (SW1) | Supply<br>Voltage<br>(V1) | Supply<br>Source2 (sw2) | Supply<br>Voltage<br>(V2) | Resolved<br>Supply Net<br>State | Resolved<br>Supply Net<br>Voltage |

|-------------------------|---------------------------|-------------------------|---------------------------|---------------------------------|-----------------------------------|

| FULL_ON                 | 1.5                       | FULL_ON                 | 2.5                       | FULL_ON                         | 1.5                               |

| FULL_ON                 | 1.5                       | OFF                     | 0                         | FULL_ON                         | 1.5                               |

| OFF                     | 0                         | FULL_ON                 | 2.5                       | FULL_ON                         | 2.5                               |

| OFF                     | 0                         | OFF                     | 0                         | OFF                             | 0                                 |

| PARTIAL_ON              | 0                         | FULL_ON                 | 2.5                       | FULL_ON                         | 0                                 |

| FULL_ON                 | 1.5                       | PARTIAL_ON              | 0                         | FULL_ON                         | 0                                 |

| PARTIAL_ON              | 0                         | OFF                     | 0                         | PARTIAL_ON                      | 0                                 |

| OFF                     | 0                         | PARTIAL_ON              | 0                         | PARTIAL_ON                      | 0                                 |

| PARTIAL_ON              | 0                         | PARTIAL_ON              | 0                         | PARTIAL_ON                      | 0                                 |

| UNDETERMINED            | -                         | FULL_ON                 | 2.5                       | UNDETERMINED                    | 0                                 |

| FULL_ON                 | 1.5                       | UNDETERMINED            | -                         | UNDETERMINED                    | 0                                 |

| UNDETERMINED            | -                         | OFF                     | 0                         | UNDETERMINED                    | 0                                 |

| OFF                     | 0                         | UNDETERMINED            | -                         | UNDETERMINED                    | 0                                 |

| UNDETERMINED            | -                         | PARTIAL_ON              | 0                         | UNDETERMINED                    | 0                                 |

| PARTIAL_ON              | 0                         | UNDETERMINED            | -                         | UNDETERMINED                    | 0                                 |

| UNDETERMINED            | -                         | UNDETERMINED            | -                         | UNDETERMINED                    | 0                                 |

TABLE II. Resolution mechanism for *-resolve either*.

| Supply<br>Source1 (SW1) | Supply<br>Voltage<br>(V1) | Supply<br>Source2 (sw2) | Supply<br>Voltage<br>(V2) | Resolved<br>Supply Net<br>State | Resolved<br>Supply Net<br>Voltage                   |

|-------------------------|---------------------------|-------------------------|---------------------------|---------------------------------|-----------------------------------------------------|

| FULL_ON                 | 1.5                       | FULL_ON                 | 2.5                       | FULL_ON                         | 2.5 (maximum<br>of SW1 and SW2<br>voltage values)   |

| FULL_ON                 | 1.5                       | OFF                     | 0                         | FULL_ON                         | 1.5 (voltage<br>value of the root<br>supply driver) |

| OFF                     | 0                         | FULL_ON                 | 2.5                       | FULL_ON                         | 2.5                                                 |

| OFF                     | 0                         | OFF                     | 0                         | OFF                             | 0                                                   |

| PARTIAL_ON              | 0                         | FULL_ON                 | 2.5                       | FULL_ON                         | 2.5                                                 |

| FULL_ON                 | 1.5                       | PARTIAL_ON              | 0                         | FULL_ON                         | 1.5                                                 |

| PARTIAL_ON              | 0                         | OFF                     | 0                         | PARTIAL_ON                      | 0                                                   |

| OFF                     | 0                         | PARTIAL_ON              | 0                         | PARTIAL_ON                      | 0                                                   |

| PARTIAL_ON              | 0                         | PARTIAL_ON              | 0                         | PARTIAL_ON                      | 0                                                   |

| UNDETERMINED            | -                         | FULL_ON                 | 2.5                       | UNDETERMINED                    | 0                                                   |

| FULL_ON                 | 1.5                       | UNDETERMINED            | -                         | UNDETERMINED                    | 0                                                   |

| UNDETERMINED            | -                         | OFF                     | 0                         | UNDETERMINED                    | 0                                                   |

| OFF                     | 0                         | UNDETERMINED            | -                         | UNDETERMINED                    | 0                                                   |

| UNDETERMINED            | -                         | PARTIAL_ON              | 0                         | UNDETERMINED                    | 0                                                   |

| PARTIAL_ON              | 0                         | UNDETERMINED            | -                         | UNDETERMINED                    | 0                                                   |

| UNDETERMINED            | -                         | UNDETERMINED            | -                         | UNDETERMINED                    | 0                                                   |

TABLE III. Resolution mechanism for *-resolve strong*.

**TABLE IV.** Resolution mechanism for *-resolve weak*.

| Supply<br>Source1 (SW1) | Supply<br>Voltage<br>(V1) | Supply<br>Source2 (sw2) | Supply<br>Voltage<br>(V2) | Resolved<br>Supply Net<br>State | Resolved<br>Supply Net<br>Voltage                 |

|-------------------------|---------------------------|-------------------------|---------------------------|---------------------------------|---------------------------------------------------|

| FULL_ON                 | 1.5                       | FULL_ON                 | 2.5                       | FULL_ON                         | 1.5 (minimum<br>of SW1 and SW2<br>voltage values) |

| FULL_ON                 | 1.5                       | OFF                     | 0                         | FULL_ON                         | 1.5                                               |

| OFF                     | 0                         | FULL_ON                 | 2.5                       | FULL_ON                         | 2.5                                               |

| OFF                     | 0                         | OFF                     | 0                         | OFF                             | 0                                                 |

| PARTIAL_ON              | 0                         | FULL_ON                 | 2.5                       | FULL_ON                         | 0                                                 |

| FULL_ON                 | 1.5                       | PARTIAL_ON              | 0                         | FULL_ON                         | 0                                                 |

| PARTIAL_ON              | 0                         | OFF                     | 0                         | PARTIAL_ON                      | 0                                                 |

| OFF                     | 0                         | PARTIAL_ON              | 0                         | PARTIAL_ON                      | 0                                                 |

| PARTIAL_ON              | 0                         | PARTIAL_ON              | 0                         | PARTIAL_ON                      | 0                                                 |

| UNDETERMINED            | -                         | FULL_ON                 | 2.5                       | FULL_ON                         | 2.5                                               |

| FULL_ON                 | 1.5                       | UNDETERMINED            | -                         | FULL_ON                         | 1.5                                               |

| UNDETERMINED            | -                         | OFF                     | 0                         | UNDETERMINED                    | 0                                                 |

| OFF                     | 0                         | UNDETERMINED            | -                         | UNDETERMINED                    | 0                                                 |

| UNDETERMINED            | -                         | PARTIAL_ON              | 0                         | PARTIAL_ON                      | 0                                                 |

| PARTIAL_ON              | 0                         | UNDETERMINED            | -                         | PARTIAL_ON                      | 0                                                 |

| UNDETERMINED            | -                         | UNDETERMINED            | -                         | UNDETERMINED                    | 0                                                 |

With the proposed new resolution mechanisms which has already been implemented in MVSIN NLP, we can create a UPF code as demonstrated in **Figure 15**. To fulfill the requirement depicted in **Figure 3**, we can use – *resolve weak* (Line 8) for **VDD\_TOP** and then connect it directly to the output of the power switch rule (Line 22) and the output of the LDO (Line 14). The benefits are obvious comparing the solution used in Section III B (i.e., we don't need to create a resolution module or a bind file to instantiate the module. We also don't need to create dummy supply nets in UPF and connect them). Hence, the UPF supply network connection will be very simple with the proposed resolution mechanisms and designers can even choose the best-case or the worst-case scenario for the resolution result to be simulated in the power-aware simulation.

| 1              | create_power_domain PD_TOP                                           |

|----------------|----------------------------------------------------------------------|

| 2              |                                                                      |

| 3              | create_supply_port VDD1                                              |

| 4              | create_supply_port VDD2                                              |

| 5              | create_supply_port VSS                                               |

| 6              | create_supply_net VDD1 -domain PD_TOP                                |

| 7              | create_supply_net VDD2 -domain PD_TOP                                |

| 8              | create_supply_net VDD_TOP -domain PD_TOP -resolve weak               |

| 9              | create_supply_net VSS -domain PD_TOP                                 |

| 10             |                                                                      |

| 11             | connect_supply_net VDD1 -ports VDD1                                  |

| 12             | load_upf LD0.upf -scope u_LD0                                        |

| 13             | connect_supply_net VDD2 -ports { VDD2 u_LD0/VDD }                    |

| 14             | connect_supply_net VDD_TOP -ports u_LD0/LD0_V0UT                     |

| 15             | connect_supply_net VSS -ports { VSS u_LD0/VSS }                      |

| 16             |                                                                      |

| 17             | <pre>set_domain_supply_net PD_TOP -primary_power_net VDD_TOP \</pre> |

| 18             | -primary_ground_net VSS                                              |

| 19             |                                                                      |

| 20             | create_power_switch PSW -domain PD_TOP \                             |

| 21             | <pre>-input_supply_port { vin VDD1 } \</pre>                         |

| 22             | <pre>-output_supply_port { vout VDD_TOP } \</pre>                    |

| 23<br>24<br>25 | -control_port {    psw_en PSW_EN    }                                |

| 24             | -on_state { PSW_ON vin {psw_en} } \                                  |

| 25             | <pre>-off state { PSW OFF {!psw en} }</pre>                          |

Figure 15. Example UPF code for the supply network in Figure 2 with the proposed resolution mechanism.

### V. CONCLUSIONS

Minimizing power consumption is very crucial for the IC design especially for the mobile applications. Hence, the low power verification is "must" to guarantee correct circuit functionality after adding low power techniques to a design.

Although UPF helps in capturing the power intent of such designs to a large extent, there are some low power techniques which cannot be modeled using UPF like LDOs and special supply net resolution, which have been described in this paper. Initially, we presented our existing solution using SystemVerilog modules connected to the UPF supply network. The existing solution can meet the desired functionality but it leaves some verification holes related to coverage. The existing solution is a bit cumbersome to understand and maintain as the UPF code is unable to have a view of the complete supply network. Therefore, we propose some extensions to the UPF commands "create\_power\_switch -output\_voltage" and "create\_supply\_net -resolve weak/strong/either" to easily model LDOs and special supply net resolution. This will help in making our low power verification more robust. We have collaborated with Synopsys to implement these extensions into the power-aware simulator MVSIN NLP and verified these solutions, and the extensions are only for power-aware simulation. We hope to donate these to the IEEE-1801 committee and hope that these will be accepted and find their place in the next version of the standard.

#### REFERENCES

- [1] IEEE Standard for Design and Verification of Low-Power Integrated Circuits, IEEE Std 1801, May 2013.

- [2] Shang-Wei Tu, Tom Lin, Archie Feng, and Chen Ya Ping, "UPF Code Coverage and Corresponding Power Domain Hierarchical Tree for Debugging," *Design and Verification Conference (DVCon)* 2015.