# Low-Power Verification Methodology using

**UPF Query functions and Bind checkers**

Madhur Bhargava, Durgesh Prasad

### INTRODUCTION

- Electronic devices have become complex and energy aware

- Require sophisticated power management architectures and strategies

- If not applied properly, will affect design functionality •

- Complex protocols, many power modes need to be verified

- Need for advanced & efficient power aware verification

- Catch low-power bugs at early stages and save design cycles

- Power intent specification format (UPF) is used to define power management logic - without modifying HDL

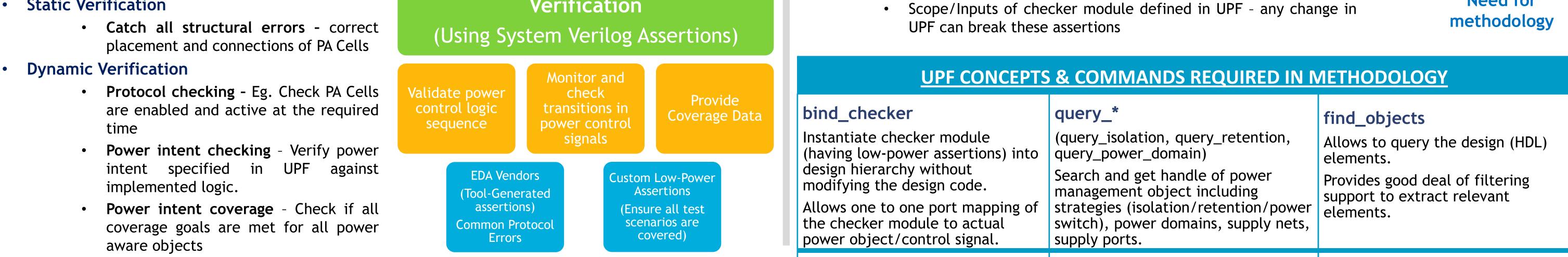

### **Low-Power Verification**

Static Verification

**Assertion Based Low-Power** Verification

### **MOTIVATION FOR METHODOLOGY**

- Tool-generated assertions used for low-power verification

- Some specific scenarios may not be met

- New protocols may require new assertions not yet supported by any tool

- Custom Assertions & Coverage Items: Club in Checker Module and instantiate into design using UPF command "bind\_checker"

- Low-Power assertions require access of power objects only present in UPF and not HDL (RTL Stage)

- Some property checking require design/power control signals spanning across multiple domains.

Custom Assertions B **Coverage Items**

Model assertions Immune from

change in UPF )

**Need for**

### **METHODOLOGY**

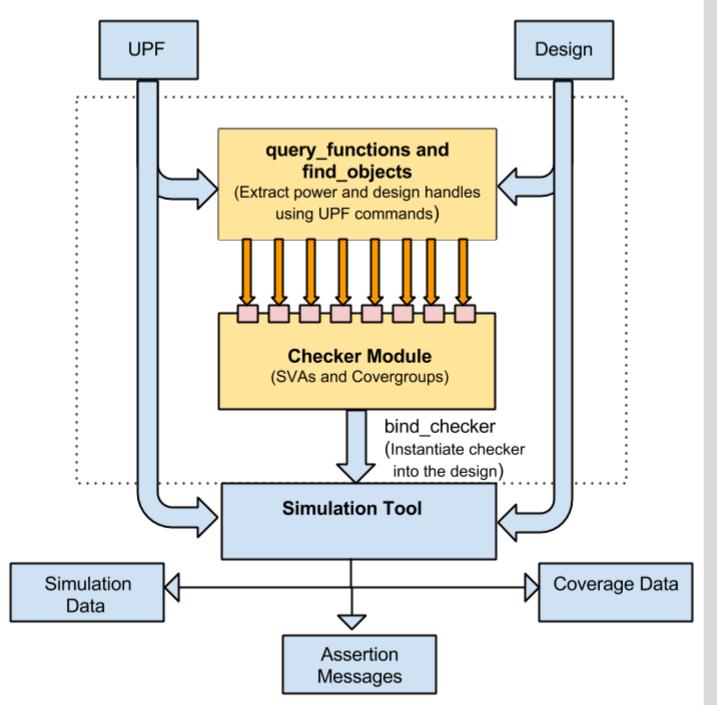

Assertions and covergroups needed for low-power verification are packed in a checker module. This module is then instantiated in the design scope using UPF command "bind\_checker". Since these SVAs and covergroups reside inside checker module, the required design/power signals need to be passed as actual argument to the checker module. This is achieved by using UPF commands query functions and bind checkers.

- **Failing Assertions** Indicate functional issue or a low-power bug

- **Coverage Data** Help achieve verification closure

### **Steps for Methodology**

Model protocols/power intent to be checked • Use SystemVerilog assertions and club

### **CASE STUDY**

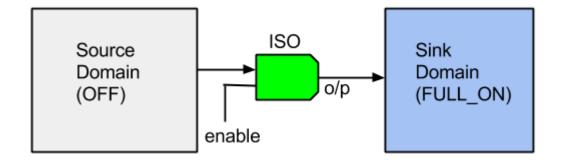

**Isolation Protocol Checking** - Whenever the driving logic supply is switched off while the receiving logic supply is still ON, an isolation cell is required. One of thing to be verified is that the output port (op) is clamped to golden expected value throughout the duration isolation enable is asserted.

#### Step1 - Write checker module

#### **Checker module:** module checker\_isolation(input op, iso\_en, clk); parameter int clamp\_value = 1; parameter isolated\_signal\_name = ""; parameter iso\_strategy\_name = "";

always@(posedge clk)

#### if(iso\_en)

assert (op == clamp\_value) else \$error("isolated signal '%s' for isolation strategy '%s' is not clamped(%b) correctly", isolated\_signal\_name, iso\_strategy\_name, clamp\_value); endmodule

#### **Tcl Proc:**

proc chk\_isolation\_properties { foreach domain [query\_power\_domain \*] { foreach isolation [query\_isolation \* -domain \$domain] { array set Iso\_Strat[query\_isolation \* -domain \$domain] foreach iso sig \$lso Strat(elements) {

them together in a checker module

#### Define interface based on UPF commands

- Extract out required power/control signals (UPF objects) from power architecture using UPF query\_\* commands. Extract out design signals (HDL objects) using UPF command find\_objects.

- Pass on above handles to checker module and instantiate it in the design with help of UPF command "bind checker".

Above check can be expressed in the form of SVA which is written inside a checker module

#### **Step2 - Define interface**

- Checker module requires the handle of isolated signals, isolation\_enable, clk and parameter values.

- Extract these handles from power architecture (using query\_\*) and pass these as actual to the formal port names in the checker module.

- Attach the checker module to the design using the bind\_checker command.

| foreach iso_sig \$iso_Strat(elements) {                 |

|---------------------------------------------------------|

| bind_checker                                            |

| hk_\$lso_Strat(isolation_name)_\$domain(domain_name)    |

| -module checker_isolation                               |

| -ports [list \                                          |

| [list op \$iso_sig] \                                   |

| [list iso_en \$lso_Strat(isolation_signal)]\            |

| [list clk clk]\                                         |

| ] \                                                     |

| -parameters [list \                                     |

| <pre>[list clamp_value \$lso_Strat(clamp_value)]]</pre> |

| }                                                       |

| }                                                       |

## **ADVANTAGES OF METHODOLOGY**

| Immune to change in UPF                        | <ul> <li>As query_*, bind_checker commands used in methodology are<br/>UPF commands, so any change in UPF will automatically reflect<br/>on output of these commands and will be fed to bind_checker</li> </ul> |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Highly programmable and easy to use            | <ul> <li>Based on Tcl, so can be embedded in UPF file to automate the verification process</li> </ul>                                                                                                           |

| Access to all power objects and design signals | <ul> <li>As it relies on method to query and extract information from<br/>UPF</li> </ul>                                                                                                                        |

### **EXTENTIONS REQUIRED IN UPF CONCEPTS/COMMANDS**

### query\_\* commands

Extend these commands to return the object handle as the full hierarchical path of the object referenced from the design top - methodology require the handle of power/control signals needs to be the full hierarchical path.

#### bind\_checker command

Certain SVAs and covergroups require object name or constant values to give intuitive messages, which are passed on as parameters to the checker module. Extension of "bind\_checker parameters" needs to be added.

### CONCLUSION

- SystemVerilog assertions and Cover groups

- used to achieve the verification closure of low-power designs

- Some EDA vendors provides fixed set of low-power assertions and coverage

- Still a need for custom low-power assertions and coverage items

- UPF command bind\_checker can be used

- Standalone usage doesn't provide a strong way of writing custom assertions and cover groups

- Suggested methodology using bind\_checkers, query commands and find\_objects

- Allows to write some of the very powerful low power assertion having considerable immunity from any change in the UPF or the design

- The kind of flexibility the methodology provides in writing assertions and covergroup would be a leap forward in low-power verification.

**Note:** The purpose of the query\_\* command in the methodology is just to extract out the handles of power/control signals from the power architecture. However any other way apart from query\_\* commands can also be used in the methodology to extract out the same information.

Some query\_\* command need to be extended to provide additional information which is not as defined, per the UPF LRM. For example, query\_power\_domain needs to be extended to provide the primary supply (power/ground) of the queried power domain.

Support for expressions in -ports in bind\_checker: In certain cases, the actual port of checker module can be an expression composed of power objects extracted from power architecture. For example, save\_condition/restore\_condition of set\_retention.

In fact UPF 2.0 query function definitions were somewhat ambiguous and they have been moved to an appendix in UPF 2.1. The P1801 working group is working on an information model and API that will serve as the basis for a new set of query functions in UPF 3.0.

### REFERENCES

IEEE Std 1801<sup>™</sup>-2013 for Design and Verification of Low Power Integrated Circuits. IEEE Computer Society, 29 May 2013 Rudra Mukherjee, Amit Srivastava, Stephen Bailey: "Static and Formal Verification of Low Power Designs at RTL using UPF", DVCon 2008.

© Accellera Systems Initiative