### It Should Just Work! Tips and Tricks for Creating Flexible, Vendor Agnostic Analog Behavioral Models

### Chuck McClish Microchip Technology Inc.

# Motivation for paper

- It should just work!... But it doesn't always

- Lots of little gotchas to consider for true portability

- Who supports what when?

- Different UDNs don't play well together

- Useful features that aren't yet LRM 'compliant'

- But are supported by the tools

### What are UDNs?

- User Defined Nettypes == UDNs, AKA the shiny new wheel!

- Introduced SV 1800.2012 LRM

- Abstract representation of a SV 'wire'

- Made of single or fixed structure of reals or 2 or 4 state integral types

- User defined resolution function

- Replaces the non-LRM 'wreal'

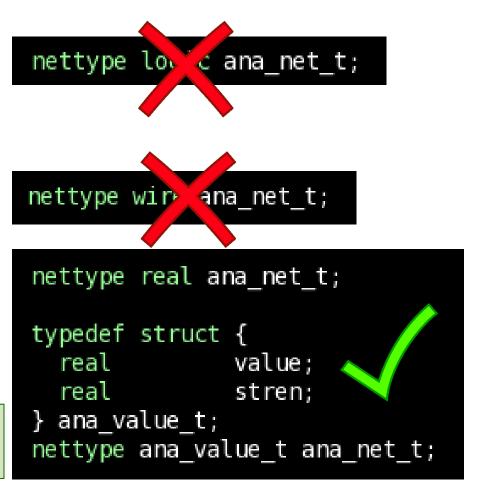

### Simple UDN

- Single 4 state nettype?

- Legal, but not supported by most!

- Is SV 'wire' a nettype?

- No!

- What is portable?

- Scalar or structures of reals

Guideline #1: Always use scaler or structures of reals for all nettype definitions

SYSTEMS INITIATIV

### What about X and Z?

- Old style 'wreal' types had `wrealXState and `wrealZState

- UDNs are just a value set, there is no special X or Z value predefined

- If you want it, you have to define it! Pick some obnoxious value.

- Tools don't understand X or Z, can make waveform plotting with these difficult

- Simple resolution function to handle X and Z:

| deline Astate 100                                                                                                                                                | Vendor Suggestion #1: Waveform viewer variable to define X and Z for pretty plotting |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| <pre>function automatic `ana_value_t re   res = `ZSTATE;   for(int i = \$low(driver); i &lt; \$s     if (driver[i] &gt; res) res = dri     end endfunction</pre> | <pre>size(driver); i++) begin: res_loop</pre>                                        |

| nettype `ana_value_t ana_net_t wit<br>`define ana_net_t ana_net_t                                                                                                | th res;                                                                              |

# Type Matching

define ana net t ana net t

- All UDN types MUST match. This is simpler, but not always desirable:

- Communication challenges, external IP

- Different complexities at IP level vs SoC level

- UDN license costs

- Flexible UDN examples:

```

// simple wire

`define ana_value_t logic

`define ZSTATE 1'bz

`define XSTATE 1'bx

`define ana_net_t wire

```

Guideline #2: Define and utilize X/Z values, UDN value set, and UDN as `defines

```

typedef struct {

real

value:

real

stren;

ana value t;

define ana value t ana value t

define ZSTATE - 100

define XSTATE 100

function automatic `ana value t res (input `ana value t driver[]);

res.value = `ZSTATE;

res.stren = 0;

for(int i = $low(driver); i < $size(driver); i++)</pre>

(driver[i].value != `ZSTATE)

(res.stren == driver[i].stren) begin

res.value = `XSTATE;

$warning("Contention on net. %m");

end

else if (res.stren < driver[i].stren)</pre>

res = driver[i];

endfunction

nettype `ana value t ana net t with res;

```

# Value Setting and Getting

- Because UDN types are flexible, helper functions are required

- Superset set function that can set all possible fields

- Superset get functions covering all possible fields

'Reasonable' defaults

```

define ana_value_t logic

define ZSTATE 1'bz

define XSTATE 1'bx

define ana_net_t wire

```

```

function automatic real get_s (input `ana_value_t ana_net);

get_s = 6; //No strength, everything 'strong'

sendfunction

```

Guideline #3: Define superset of functions to ensure compile time compatibility

| ypedef | struct | {   |  |

|--------|--------|-----|--|

| rool   |        | vol |  |

```

function automatic real get_s (input `ana_value_t ana_net);

get_s = ana_net.stren;

endfunction

```

# **UDN Type Checking**

- Flexibility requires additional model complexity

- Different behavior based on type

- Additional UDNs for model level verification

- Many times, incoming signals are 'OK' if they fall within a certain range:

assign vref\_ok = (get\_udn\_type() == LOGIC) ? get\_v(vref) : (get\_v(vref) inside {[MIN:MAX]});

Organize these 'OK' level checks in a common location in the model

Guideline #4: Maintain minimal set of SoC and subsystem level UDNs with explicit type naming scheme and organize checks in common location in models

### **UDN Bi-Dir Switches**

### • How to model a bidirectional switch with UDNs?

#### So sayeth the LRM

Burn the tools!!

### **UDN** capable switch primitives

- With simple wrapper, can use tran, tranif0, and tranif1 gates with UDNs

- Will likely be added to the LRM in a future release

9

### **Integration Tips**

- Along with UDNs, the LRM introduced 'interconnect'

- Typeless hierarchy connectors

- All end points must be of the same type

- Synthesis and APR tools replace these with 'wire'

- To use UDNs in a LRM compliant manner, need to write a script to replace wire with interconnect

- All the simulation tools treat 'wire' as 'interconnect' as long as interconnect rules are followed

Guideline #5: Don't use interconnect, always use wires for hierarchical transport of UDNs

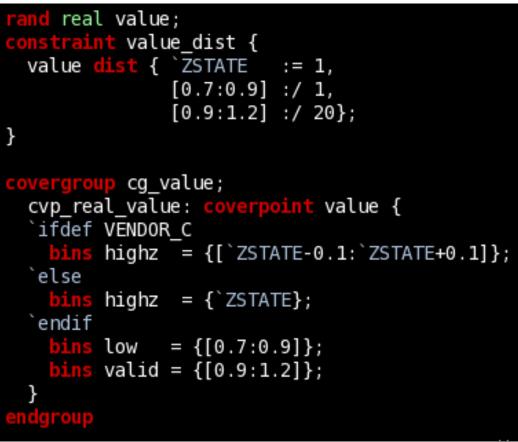

### **Real Coverage and Stimulus**

- The LRM says that only integral types can be used for randomization/coverage

- but all vendors now support constrained random real stimulus and coverage!

- Be aware that it doesn't always just work!

- There are several gotchas noted in the paper

- Some tools pull a special license

Guideline #6: Use constrained random real stimulus and real coverage collection if you have the license capacity

### **UPF for Behavioral Models**

- What are UPF aware behavioral models?

- React according to UPF supply connections

- Complex corruption semantics handled entirely by the model

- Generate supply voltages for other blocks (e.g. regulators)

```

module foo (

input UPF::supply_net_type vdd, vss,

inout `ana net t

vref out,

output wire

rdy);

real vdd real, vss real;

vdd real = $itor(vdd.voltage) / (10**6);

vss real = $itor(vss.voltage) / (10**6);

vdd ok = (vdd.state == UPF::FULL ON) && (vdd real inside {[ 1.8 : 3.3]});

= (vss.state == UPF::FULL_ON) && (vss_real inside {[-0.1 : 0.1]});

vss ok

rdv

= 1'b1:

vref_out = (get_udn_type() == LOGIC) ? set_n(1'b1) : set_n(0.700);

rdy

= (vdd ok & vss ok) ? 'z : 'x;

vref_out = (vdd_ok && vss_ok) ? `ZSTATE : `XSTATE;

endmodule

```

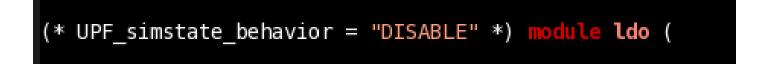

## **Disabling Automatic Corruption**

- Disabling automatic corruption semantics must be done for UPF aware models with real UDNs

- Corruption sets outputs to default state, for reals, this is 0

- Initial blocks are not retriggered when power comes back up!

- Automatic corruption occurs immediately, no delays!

- Setting module attribute is portable and behavior is self contained:

Guideline #7: Always disable automatic UPF corruption in behavioral models with the UPF\_simstate\_behavior SV attribute

### UPF Modelling Tips, Tricks, and Gotchas UNITED STATES

- Each vendor interpreted the UPF LRM differently for SV implementation:

- Always prefix UPF package types and enumerations with 'UPF::'

- Avoid using UPF package functions like get\_supply\_state(), supply\_on(), etc.

- Create a common define for the state enumeration

DESIGN AND VERIFIC

SYSTEMS INITIATIVE

- Can be either UPF::upfSupplyStateE or UPF::state depending on your tool

- Always drive or read the UPF supply net struct fields directly:

```

UPF::supply net type vout, vin;

real vin real;

assign vin_real = $itor(vin.voltage) / (10**6);

Lgn vin_ok = (vin.state == UPF::FULL_ON) && (vin_real inside {[ 1.8 : 3.3]});

(@*

(vin_ok) begin

vout.state = UPF::FULL ON;

vout.voltage = \frac{100}{1.0} \times 10^{10};

Guideline #8: Follow UPF

end else beain

= UPF::0FF:

vout.state

modelling rules on this page

vout.voltage = 0;

end

```

### Conclusion

- UDN based, UPF aware behavioral models add many new modelling and verification capabilities

- The vendors are working to add features to make our lives easier

- Following the guidelines in this paper will ensure that every just works!