1 of 126

# IEEE 1800.2 UVM - Changes Useful UVM Tricks & Techniques

#### **Clifford E. Cummings**

World Class Verilog, SystemVerilog & UVM Training

Life is too short for bad or boring training!

1639 E 1320 S, Provo, UT 84606 Voice: 801-960-1996 Email: cliffc@sunburst-design.com Web: www.sunburst-design.com

## **New IEEE UVM Features**

• IEEE UVM 1800.2 Topics

Agenda

- Quick Introduction

- Resources & References

- Most Obvious IEEE UVM 2017 Question & Answer

- Virtual classes & the UVM Factory

- `uvm\_do macro replacement

- UVM comparators status

Introduction

Do not exist !! UVM Best Known Methods (BKMs) ... ۲ (At least not all) In my opinion, Nothing! Frequently Asked Question: What will replace UVM? • (At least for a very long time) IEEE 1800.2 is the first set of IEEE **BUT** ... there will be modifications, simplifications and enhancements to UVM standardized enhancements to UVM **Complementary methodologies will emerge PSS will help generate** (such as PSS) **UVM** sequences **UCIS (Unified Coverage Interoperability Standard)**

helps with collection of coverage data

3 of 126

#### References

1800.2-2017 - IEEE UVM

1800-2017 - IEEE SystemVerilog

You need free video registrations & two free logins

- DVCon 2018 Tutorial IEEE-Compatible UVM Reference Implementation and Verification Components

To watch this presentation, go to:

- videos.accellera.org/videos.html

- DVCon 2017 Tutorial Introducing IEEE 1800.2 The Next Step for UVM

To watch this presentation, go to: videos.accellera.org/videos.html

• forums.accellera.org/

Access the SystemVerilog and UVM Forums

Linked from www.accellera.org/downloads/ieee

• https://ieeexplore.ieee.org/document/7932212

Downloading PDF documents requires IEEE login (You can create a free IEEE login account)

• https://ieeexplore.ieee.org/document/8299595

#### Mark Glasser **Slides 63-70**

accellera)

DVCon 2017 - UVM Features Described Reference Material Mark Glasser - NVIDIA Corporation

- 63 Summary of TLM Mantis Items

- 68 Register models documentation enhanced / system level / dynamic

- 69 Reg model unlock models can now be unlocked & re-locked

- 70 Register changes virtual and non-virtual classes

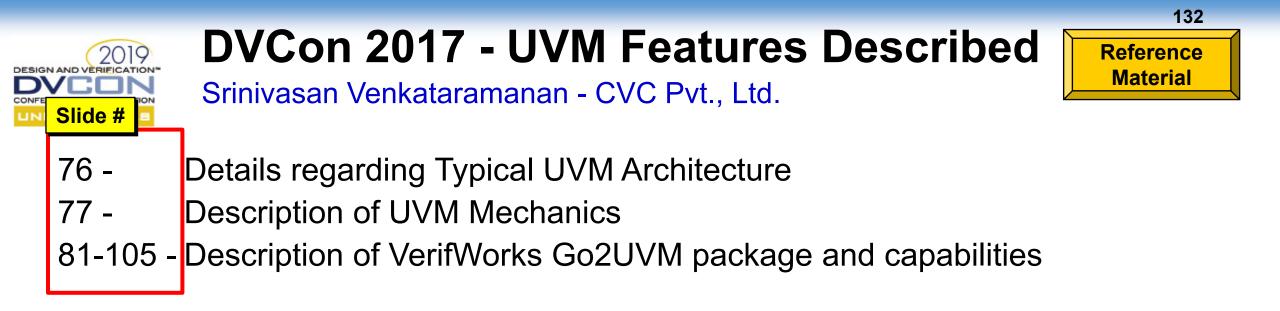

#### Srinivasan Venkataramanan **Slides 76-105**

DVCon 2017 - UVM Features Described Srinivasan Venkataramanan - CVC Pvt., Ltd.

Reference Material

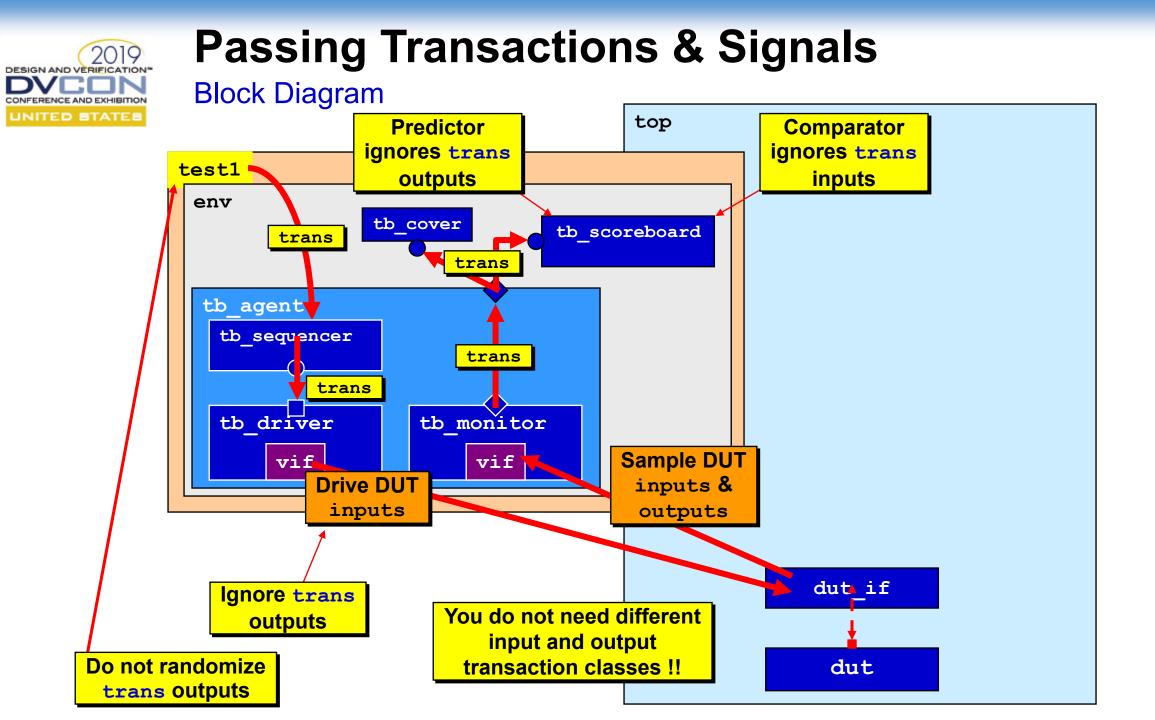

- Details regarding Typical UVM Architecture

- 77 -Description of UVM Mechanics

Slide #

76 -

(accellera)

81-105 - Description of VerifWorks Go2UVM package and capabilities

SYSTEMS INITIATIVE

#### **DVCon 2018 - UVM Features Described**

#### **Reference Slides at End of Presentation**

Reference Material

6 of 126

76 -

77 -

(accellera)

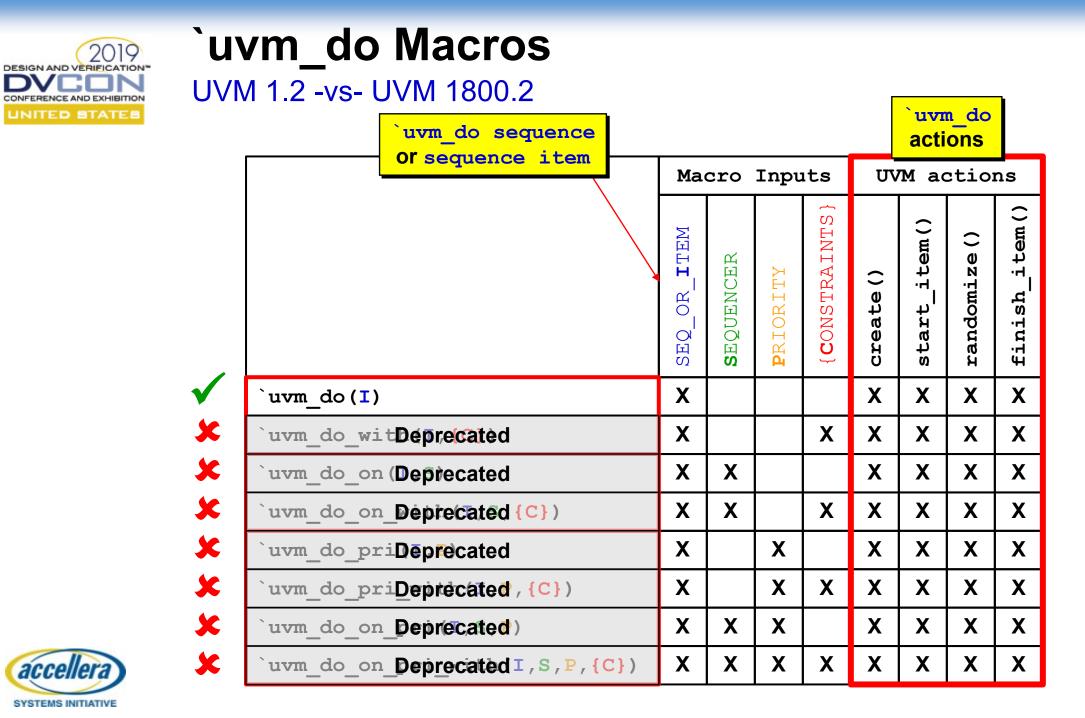

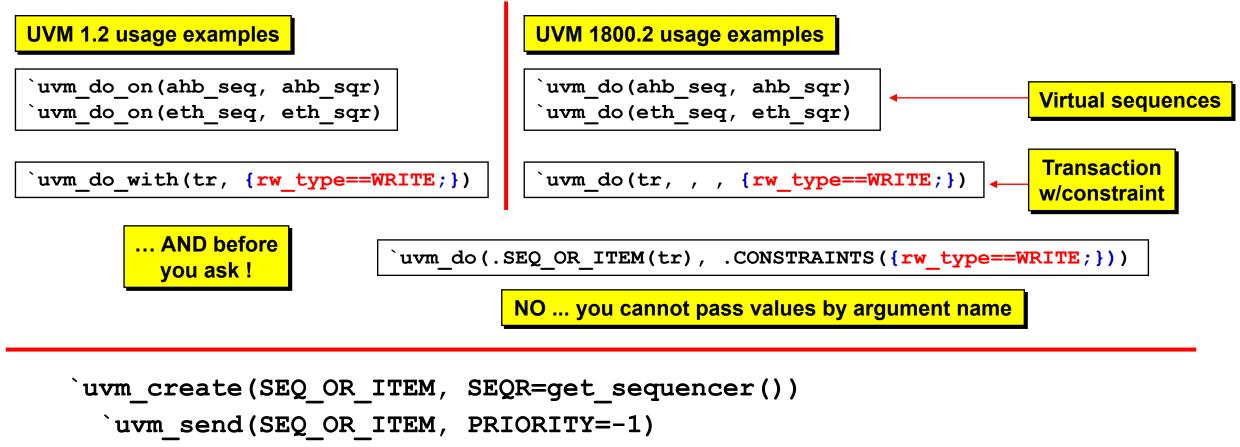

'uvm do replaces all earlier 'uvm do \* macros

uvm do \* deprecation notes

- uvm\_coresevice\_t ::get() / uvm\_init() / run\_test()

53-56 UVM deferred initialization examples

- 57-58 uvm\_run\_test\_callback / pre\_run\_test() / post\_run\_test() / pre\_abort()

- 59-62 uvm\_reg\_block.lock\_model() / unlock\_model()

accellera)

63 - Miscellaneous uvm\_reg notes & changes including uvm\_door\_e

## Where to Get Latest UVM BCL

Accellera Base Class Library

http://www.accellera.org/downloads/standards/uvm

Latest release is: UVM 2017-1.0 Reference Implementation

## **Most Obvious IEEE UVM 2017 Question**

http://forums.accellera.org/

- From the UVM 2017 Methodology and BCL Forum

- Question from Brian Hunter:

"Who can provide a summary of what is new and what has changed?"

Response from Justin Recife +

Accellera UVM Group Chair

"Wow, starting the questions off with a (*not entirely unexpected*) doozy!"

"Unfortunately *there's no single document* which states 'Here's a full list of everything that changed'. This is because a large number of changes were performed by the Accellera UVM WG prior to the IEEE UVM WG ..."

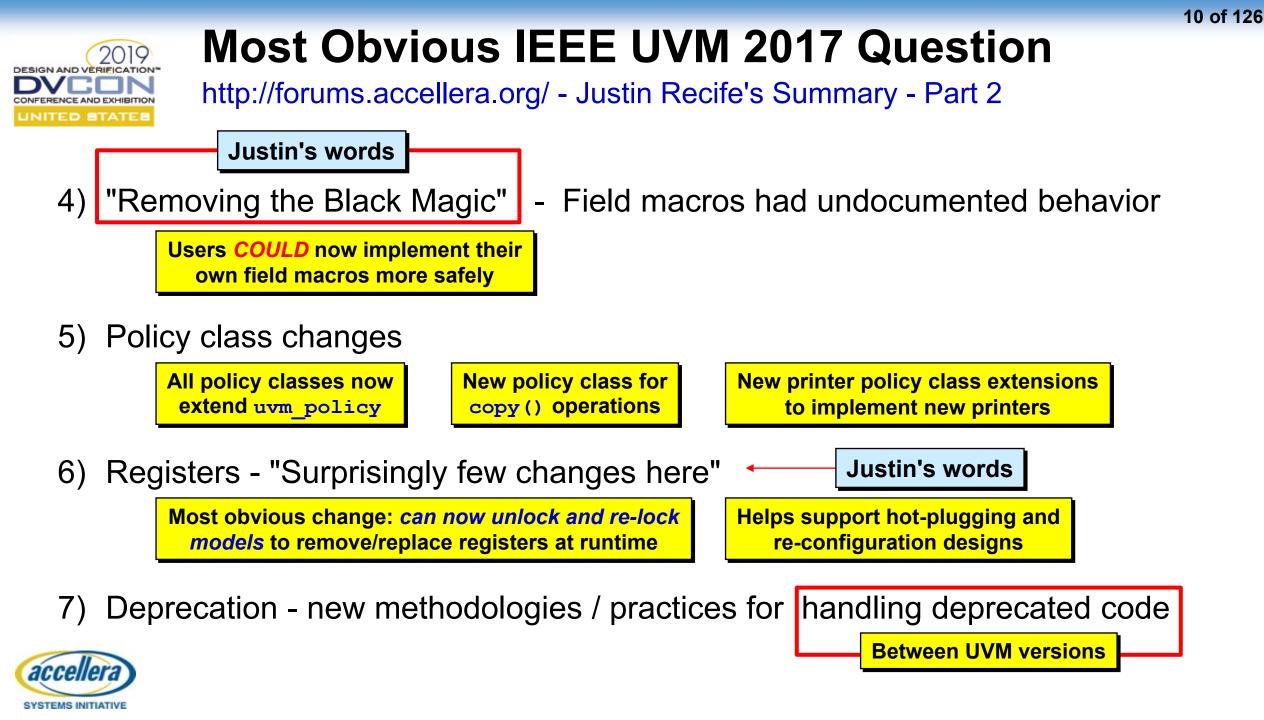

#### **Most Obvious IEEE UVM 2017 Question**

http://forums.accellera.org/ - Justin Recife's Summary - Part 1

0) Removal of the User Guide -

"User Guide" material removed

- It's not standard-worthy"

- DVCon 2017 Slide 10

- 1) Added more **set** / **get** accessor methods to replace some current knobs

Knobs still work but accessor methods are a better coding practice

2) Users can insert code into the UVM core services

Advanced topic - example:<br/>create factory debuggerAllows users to make custom version of<br/>libraries without hacking existing UVM

3) Library initialization ordering

Advanced topic - but might allow "parameterized classes participating in the name-based factory"

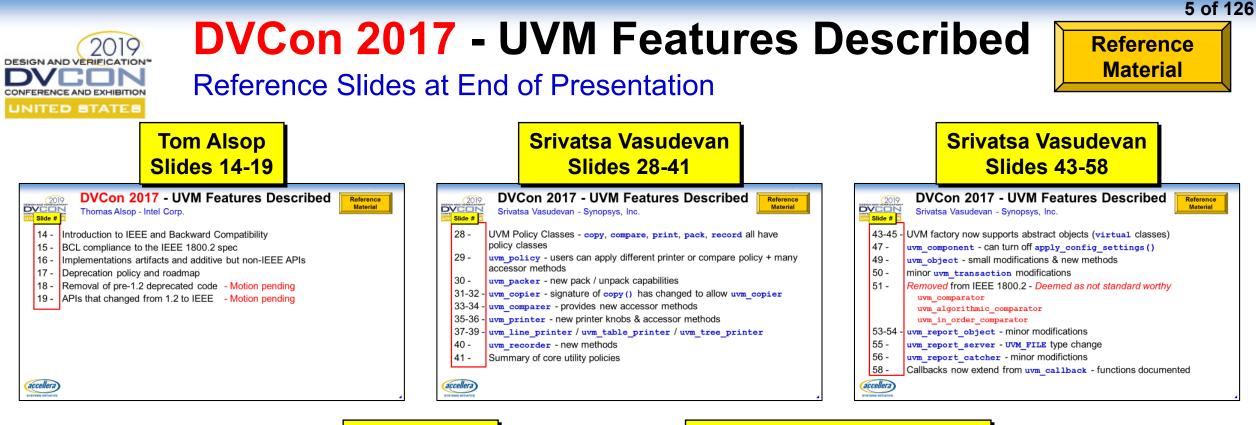

### **Accellera DVCon Resources**

http://www.accellera.org/resources/videos

Registration & viewing the videos is FREE!

Justin - "At DVCon 2017 & 2018, there were tutorials which covered all of the above and more, with detailed examples."

- U.S. DVCon 2018 Presentation by:

- Justin Refice -

Nvidia

Mark Strickland -

Cisco Systems

Mark Peryer -

Mentor, a Siemens Business

– Uwe Simm -

Cadence Design Systems

- Srivatsa Vasudevan -

Synopsys

- U.S. DVCon 2017 Presentation by:

- Thomas Alsop -

Intel

Srivatsa Vasudevan -

Synopsys

- Mark Glasser Nvidia

- Srinivasan Venkataramanan CVC Pvt., Ltd.

- Krishna Thottempudi Qualcomm

**#1** Added more set\_/get\_accessor methods to replace some current knobs

Justin - "Aside from #1, most of those changes are for advanced use cases, or providers of infrastructure. Day-to-day users shouldn't necessarily see a drastic change."

### DVCon 2017 & 2018 Tutorials

Multiple features shared but most were very

complex corner-case enhancements

(Complex) examples in the DVCon presentation slides

• Personally, I never tried to implement the corner-case functionality:

- I could re-show:

- Excellent examples from DVCon presentations

- And show advanced corner-case topics that most would barely understand

I want to show you more mainstream enhancement examples

## DVCon 2017 & 2018 Tutorials

- Justin's list of 1800.2 features shows topics

covered in the DVCon presentations

- Doing anything tricky or complex?

Now you know you can register for free login on the Accellera web page

Please *review the excellent examples* that you will find in the DVCon presentations

• See the slides and hear the explanations by the actual presenters

**Presentation audio always includes more than the presentation slides**  If you are *doing anything complex*, it is worth a listen

## **New UVM Features Will Be Shown**

- This is Cliff's way of saying these guys are really smart!

- To Be Shown: Enhancement features that the average UVM coder can use

- Where appropriate: List DVCon slides where you can find more info

- I will also show you a few of my favorite tricks

To make your attendance worth while

... and Cliff is

really average!

#### Virtual Classes Purpose and Usage

• **virtual** classes - only intended to be a base class

Not enough functionality to use as stand-alone constructed objects

Most UVM components must be extended to be useful - so they are virtual classes

- virtual class methods can be virtual or non-virtual

- non-virtual methods means extended class can override and change the prototype

Prototype = function/task header Polymorphism not possible with non-virtual methods

virtual methods create placeholders with required prototype

Same function/task header Can include default implementation if the extended class does not override the method.

#### Virtual Classes Purpose and Usage

• You want **virtual** classes to have **virtual** methods

**virtual** methods make upcasting and polymorphism possible

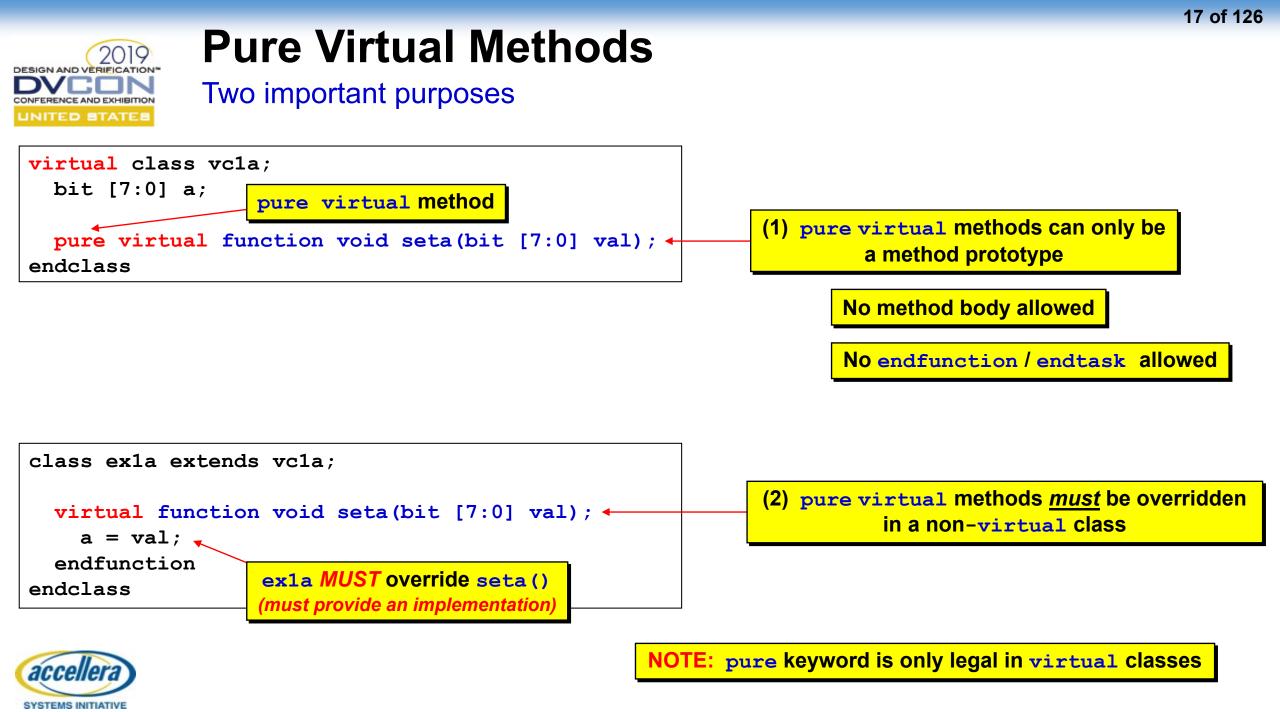

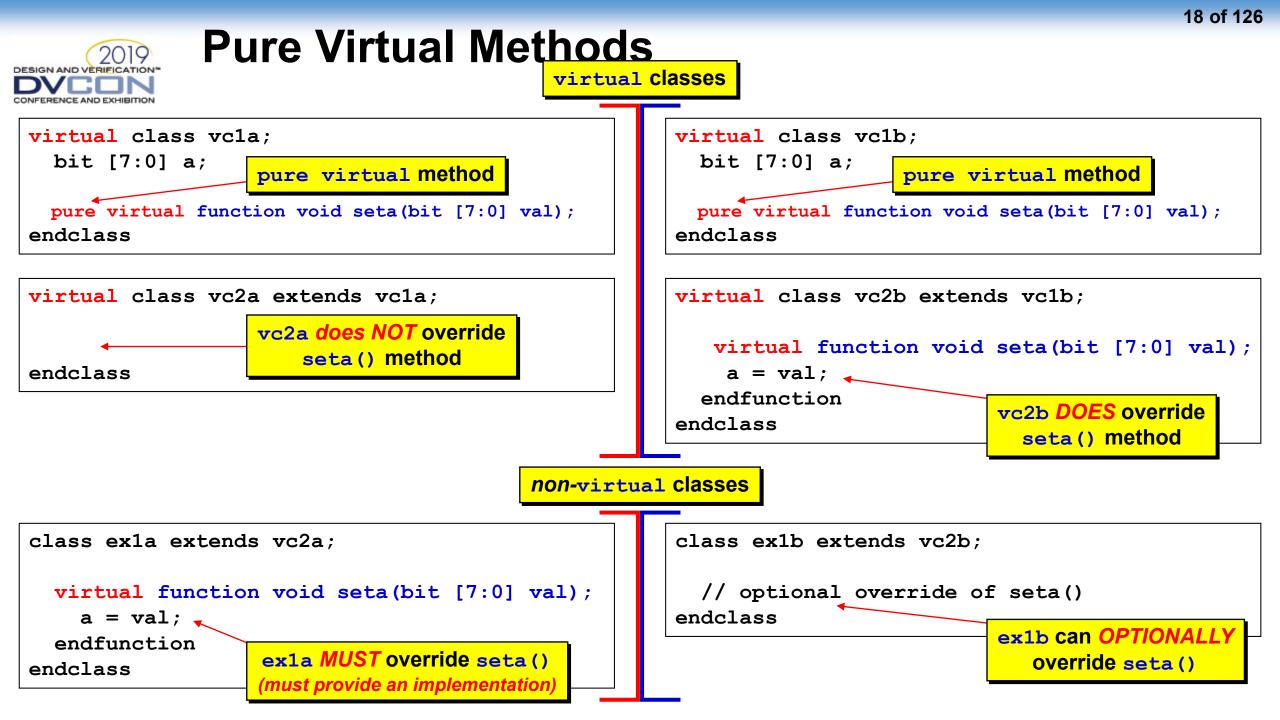

• SystemVerilog-2009 added pure virtual methods

*Just like virtual methods -*Requires the same prototype

Unlike virtual methods -There can be no default method implementation

• pure virtual methods REQUIRE extended classes to override the method

Extended class *must* provide an implementation pure keyword is only legal in a virtual class

SYSTEMS INITIATIVE

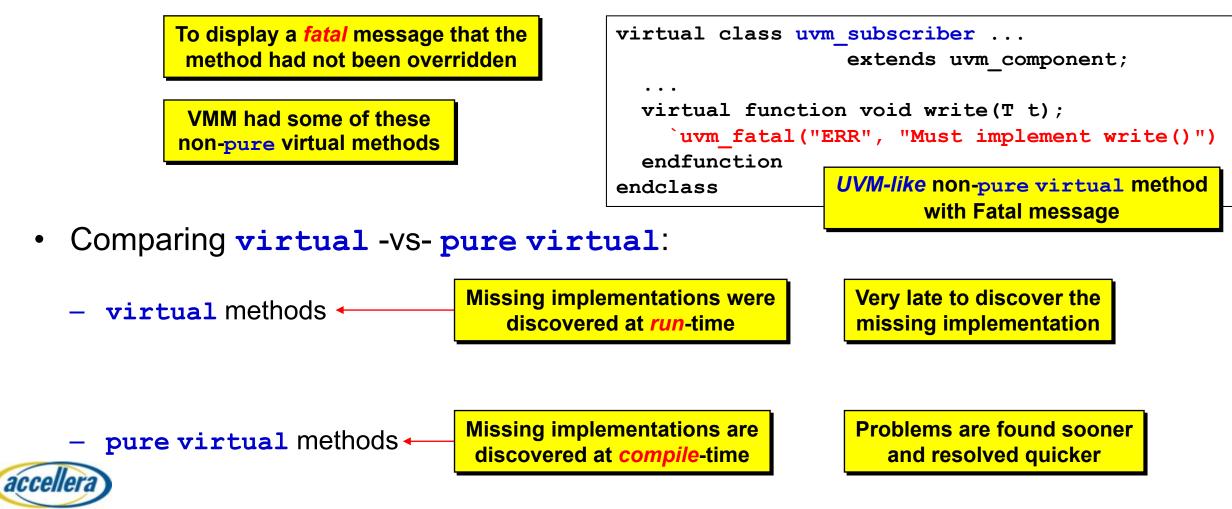

#### **Prior to Pure Virtual?**

How was the pure-virtual functionality implemented?

• Engineers would code virtual methods with a simple implementation

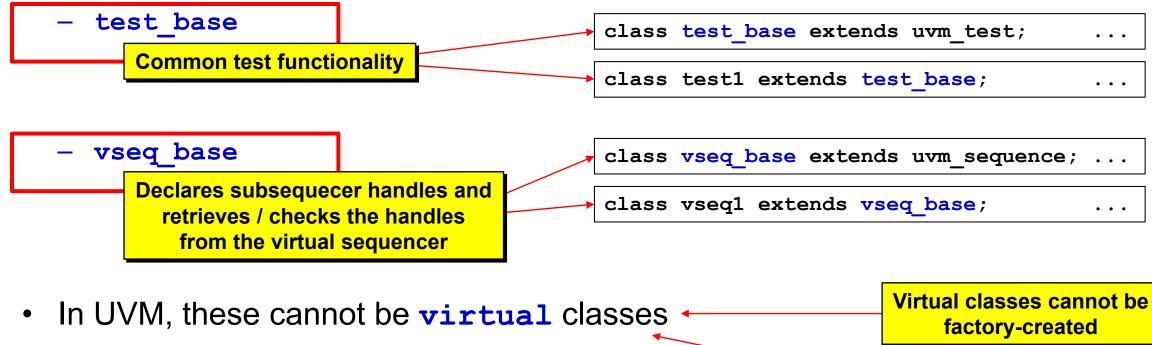

#### **Two Common Testbench Base Classes**

20 of 126

UVM compilation errors if put in the factory

**Common User-Defined Base Classes**

• User-defined classes that should not be directly created:

**Typical error:** "An abstract class cannot be instantiated ..."

accellera systems initiative

## **Virtual Classes in the Factory**

UVM 1800.2 Enhancement - For uvm\_objects

```

Utils-macros for Classes:

`define uvm_object_utils(T)

`define uvm_object_utils_begin(T)

`define uvm_object_utils_end

```

```

`define uvm_object_param_utils(T)

```

`define uvm\_object\_param\_utils\_begin(T)

`define uvm\_object\_param\_utils\_end

• Utils-macros for Virtual Classes:

```

`define uvm_object_abstract_utils(T)

```

```

`define uvm_object_abstract_utils_begin(T)

`define uvm_object_abstract_utils_end

```

```

`define uvm_object_abstract_param_utils(T)

```

```

`define uvm_object_abstract_param_utils_begin(T)

`define uvm_object_abstract_utils_end

```

Now virtual base classes for transactions and sequences can be stored in the factory

**NOTE:** Now you can store **virtual** classes with **pure virtual** methods in the factory

## **Virtual Classes in the Factory**

UVM 1800.2 Enhancement - For uvm\_components

| Utils-macros for Classes:                  | Utils-macros for Virtual Classes:                   |

|--------------------------------------------|-----------------------------------------------------|

| `define uvm_component_utils(T)             | `define uvm_component_abstract_utils(T)             |

| `define uvm_component_utils_begin(T)       | `define uvm_component_abstract_utils_begin(T)       |

| `define uvm_component_utils_end            | `define uvm_component_abstract_utils_end            |

| `define uvm_component_param_utils(T)       | `define uvm_component_abstract_param_utils(T)       |

| `define uvm_component_param_utils_begin(T) | `define uvm_component_abstract_param_utils_begin(T) |

| `define uvm_component_param_utils_end      | `define uvm_component_abstract_utils_end            |

Now virtual base classes for tests and other components can be stored in the factory

SYSTEMS INITIATIVE

**NOTE:** Many of the UVM virtual base classes are now factory enabled using the abstract\_utils macros

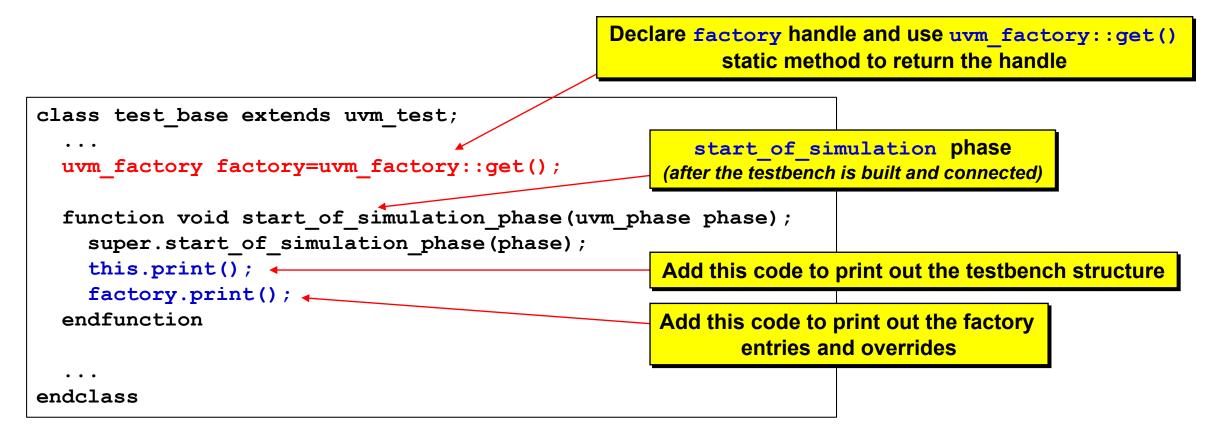

#### Testbench & Factory Access UVM 1.1d

• UVM 1.1d allowed access to the **factory** handle

# Testbench & Factory Access

• UVM 1.2 & 1800.2 require declaration of the **factory** handle

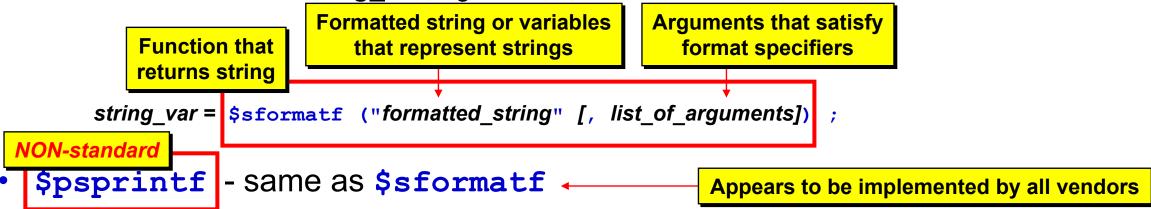

#### UVM 1.2 -vs- UVM 1800.2 uvm macro actions uvm *macro* sequence Or sequence item Macro Inputs UVM actions $\mathbb{C}$ Ŋ item() tem TEM TNT C randomize QUENCER CONSTRA ·H PRIORITY $\mathbb{C}$ create sh 0R start Less frequently ini used macros SEQ Ē Ψ S uvm create(I) Χ Χ X Χ Χ uvm create Deprecated Χ $\checkmark$ Χ Χ uvm send(I) Х X Χ Χ X uvm send prDeprecated Χ $\checkmark$ Χ Χ uvm rand send(I) Х Χ X Χ Χ Χ uvm rand seprecated , {C}) Х Χ X Χ Χ Χ Х uvm rand se**Deprecated** P) Χ X Χ Χ uvm rand seprecated th(I,P,{C}) Χ Χ Χ Χ

# New 1800.2 `uvm\_do Commands

`uvm\_do `uvm\_create `uvm\_send `uvm\_rand\_send

`uvm\_do(SEQ\_OR\_ITEM, SEQR=get\_sequencer(), PRIORITY=-1, CONSTRAINTS={})

`uvm\_rand\_send(SEQ\_OR\_ITEM, PRIORITY=-1, CONSTRAINTS={})

# **UVM Comparator Classes**

DVCon 2017 - Slide 51

Removed from P1800.2

uvm\_comparator

uvm\_algorithmic comparator

uvm\_in\_order\_comparator

Deemed as not standard-worthy" DVCon 2017 - Slide 51

NOT Deprecated: The Source files are still there

> These are some of my favorite UVM 1800.2 new features

#### Some of Cliff's favorite UVM topics

- Cliff's favorite UVM topics

- UVM transaction why is it a class?

- UVM do\_methods -vs- field macros

- start\_item() / finish\_item() -VS-`uvm\_do

- UVM messaging macros, tricks & guidelines

- UVM factory & factory.print()

- Analysis paths

## Why Is UVM Hard To Learn?

- UVM User Guide was written by Cadence

- UVM tutorials by Mentor on <u>VerificationAcademy.org</u>

- OVM Cookbook written by Mentor employees

Based on earlier versions of OVM

User Guide, tutorials and Cookbook do not acknowledge alternate methods

Authors of UVM materials are really, really smart software engineers Authors assume everyone knows

**Teaches Cadence** recommended methods

Uses a large number of UVM macros

Teaches *Mentor* recommended methods

Fewer UVM macros / more UVM method calls

Users think one or more sources have bugs

SV, OO and polymorphism

Authors don't know how to teach the concepts to beginners

CONFERENCE AND EXHIBITION

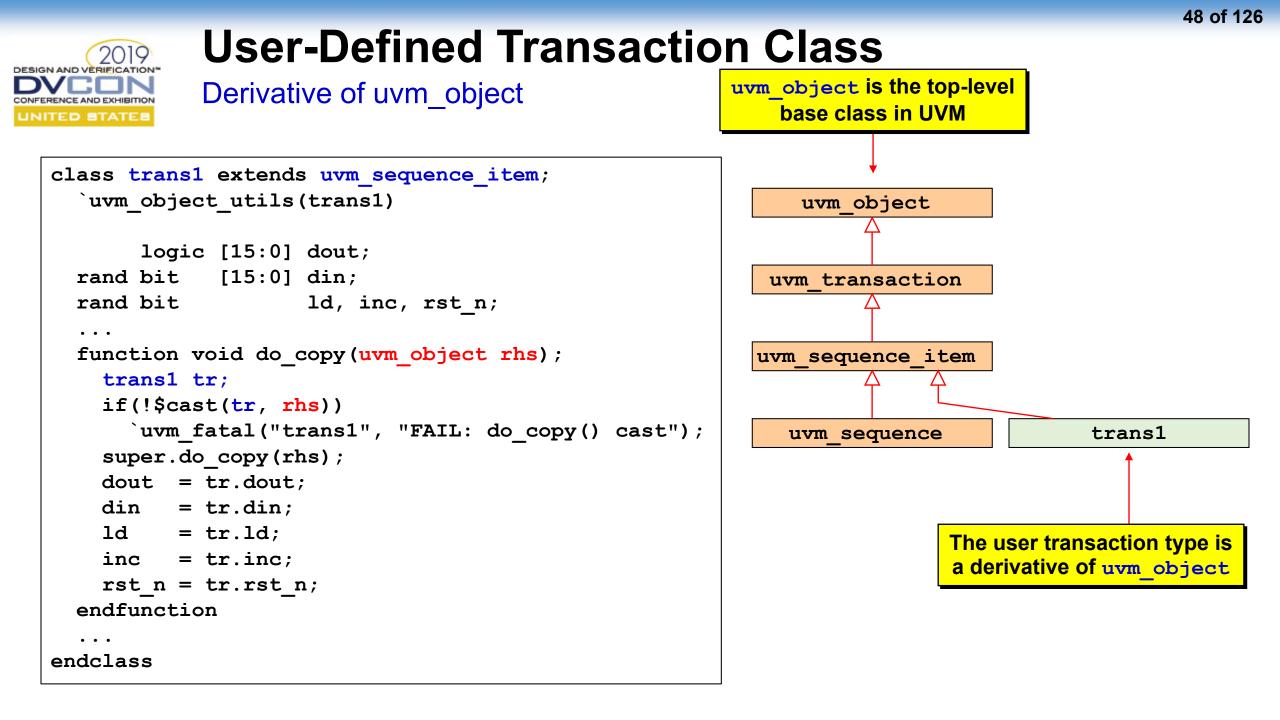

# **UVM Transaction Base Classes**

Good reference paper: UVM Transactions - Definitions, Methods and Usage

www.sunburst-design.com/papers/CummingsSNUG2014SV UVM Transactions.pdf

31 of 126

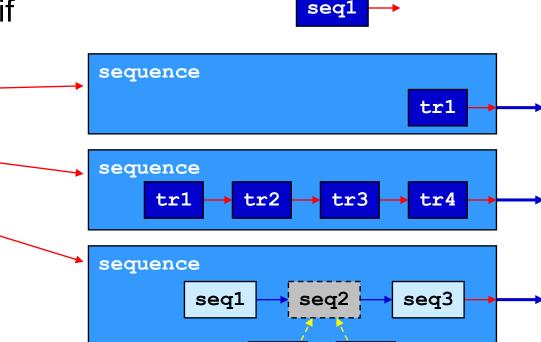

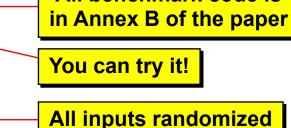

#### **Transactions & Sequences**

What Is Their Composition?

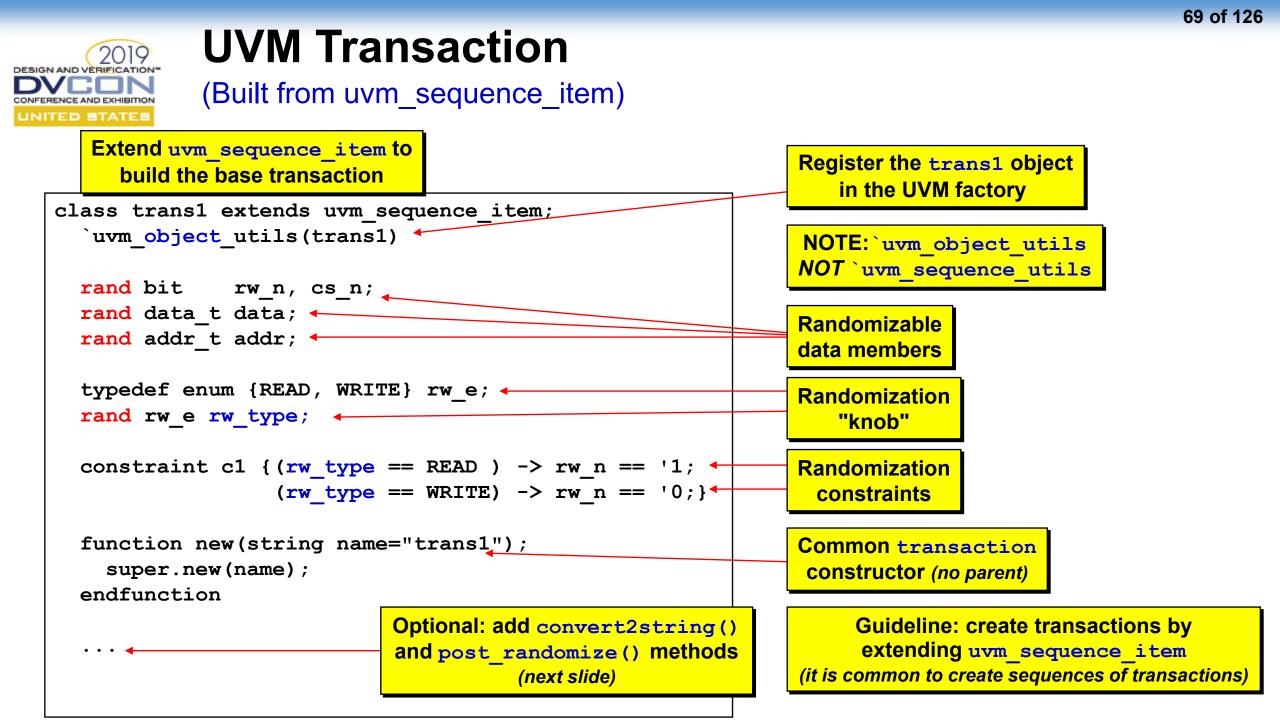

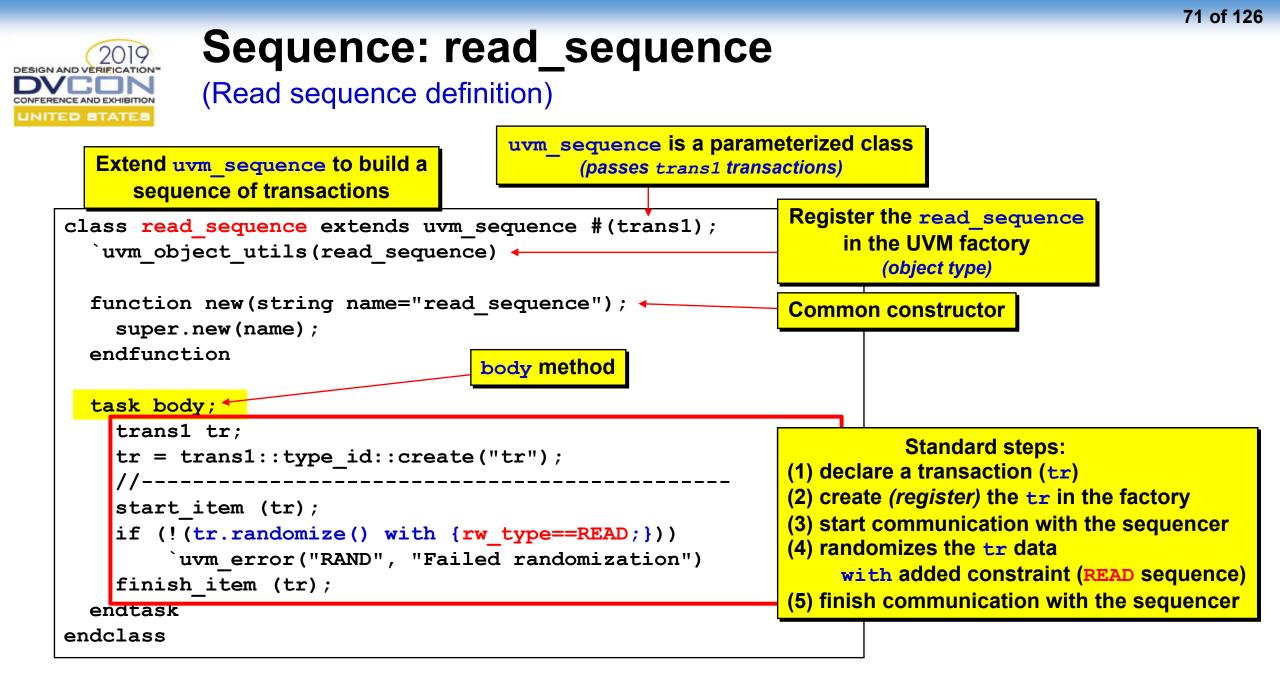

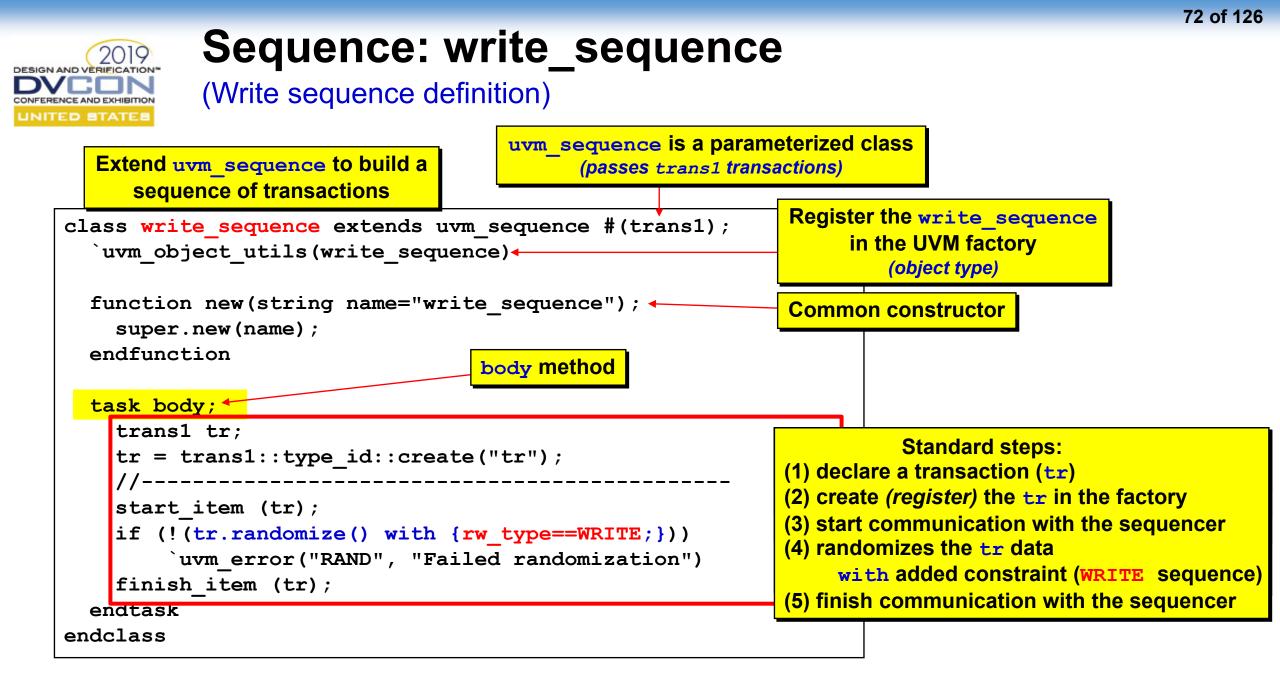

Basic transactions are extended from uvm\_sequence\_item

- Transactions are driven into the dut\_if

- Sequences can be built from:

- A single transaction

- Multiple transactions

- Multiple other sequences

tr1

tr2

#### **Transaction Data**

Why use classes? Why not use structs?

- Classes dynamic

- ✓ Multiple fields

- $\checkmark$  rand fields

- ✓ Randomization constraints

- ✓ Built-in methods

- ✓ Generate as many as needed at run time

- ✓ Classes can be extended

Allows more than one transaction type with a common base type

$\checkmark$  Can be in a factory for run-time substitution

**Classes are basically dynamic, ultra flexible structs that can**

be easily randomized

SYSTEMS INITIATIVE

- easily control the randomization

- be created whenever they are needed

- Structs static

- ✓ Multiple fields

- ✗ NO rand fields

- X NO randomization constraints

- ✗ NO built-in methods

- Must anticipate & statically declare all structs at the beginning of the simulation

Structs must be copied

Copies are modified if more than one transaction type is desired

✗ No factories for structs

The default transaction type used by UVM components is uvm\_sequence\_item

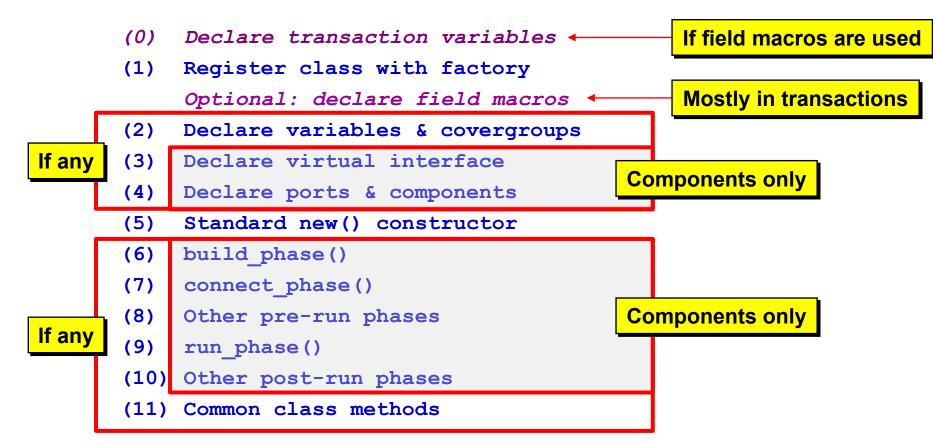

# **Standardized UVM Formatting**

#### **Standard UVM Coding Style**

#### Cliff's preferred styles

• UVM testbench components and UVM transaction definitions

#### **UVM Transactions Styles**

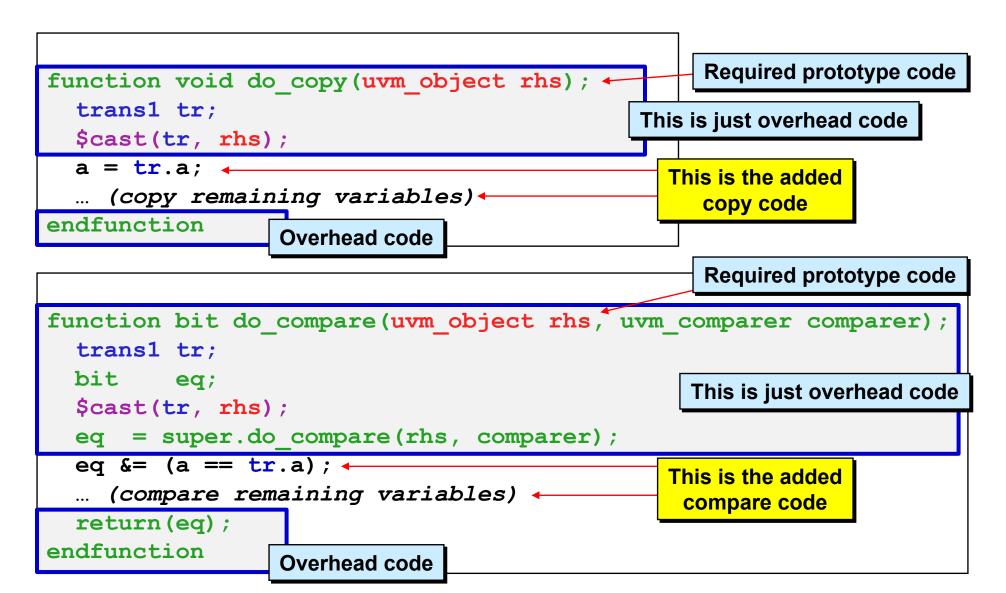

do\_methods() -vs- field macros

- Using do\_methods()

- (1) Register with factory

- (2) Declare vars/<del>covergroups</del>

- (5) new() constructor

```

(11) Common trans methods

convert2string()

do_copy() / do_compare()

other do_methods()

```

- Using field macros

- (0) Declare trans vars

- (1) Register with factory Optional: field macros

- (2) Declare vars/covergroups

- (5) new() constructor

- (11) Common trans methods

convert2string()

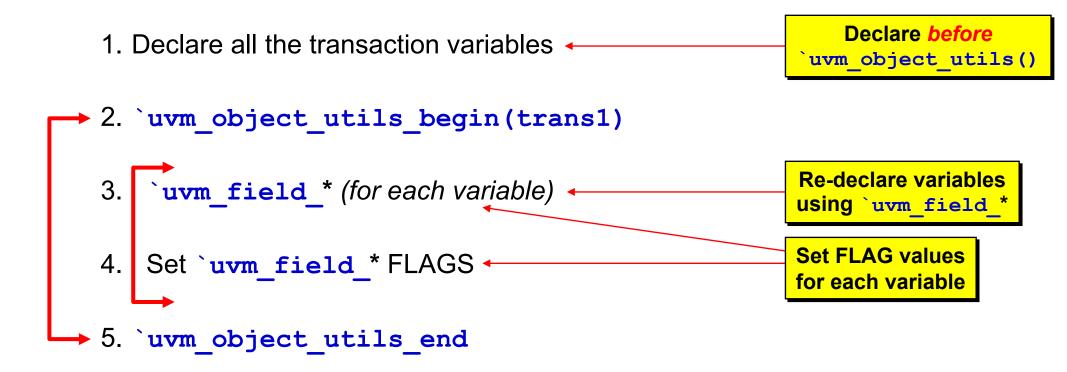

#### `uvm\_object\_utils Macro Usage

• Using do methods ()

| <pre>class trans1 extends uvm_sequence_item;<br/>`uvm_object_utils(trans1)<br/><declare variables=""> </declare></pre> | <pre>`uvm_object_utils()     <u>before</u> declarations</pre> |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| <pre><standard constructor=""> <override do_methods()=""></override></standard></pre>                                  | Variables declared <u>after</u><br>`uvm_object_utils()        |

• Using field macros

|                                                                                                                                                      | Variables declared <u>before</u>                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| class trans1 extends uvm_sequence_item;                                                                                                              | <pre>`uvm_object_utils()</pre>                               |

| <pre><declare variables="">  `uvm_object_utils_begin(trans1)  </declare></pre> <pre><declare field="" for="" macros="" variables=""></declare></pre> | <pre>`uvm_object_utils()     <u>after</u> declarations</pre> |

| <pre>`uvm_object_utils_end <standard constructor=""></standard></pre>                                                                                | Field macros declared <u>afte</u><br>`uvm_object_utils()     |

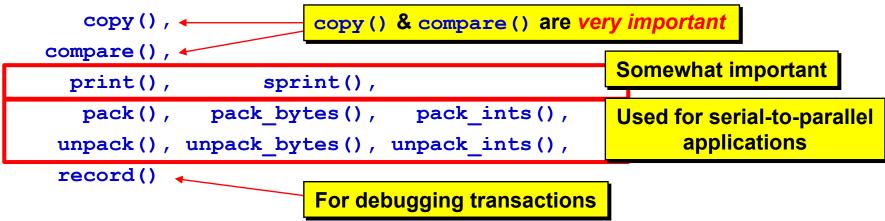

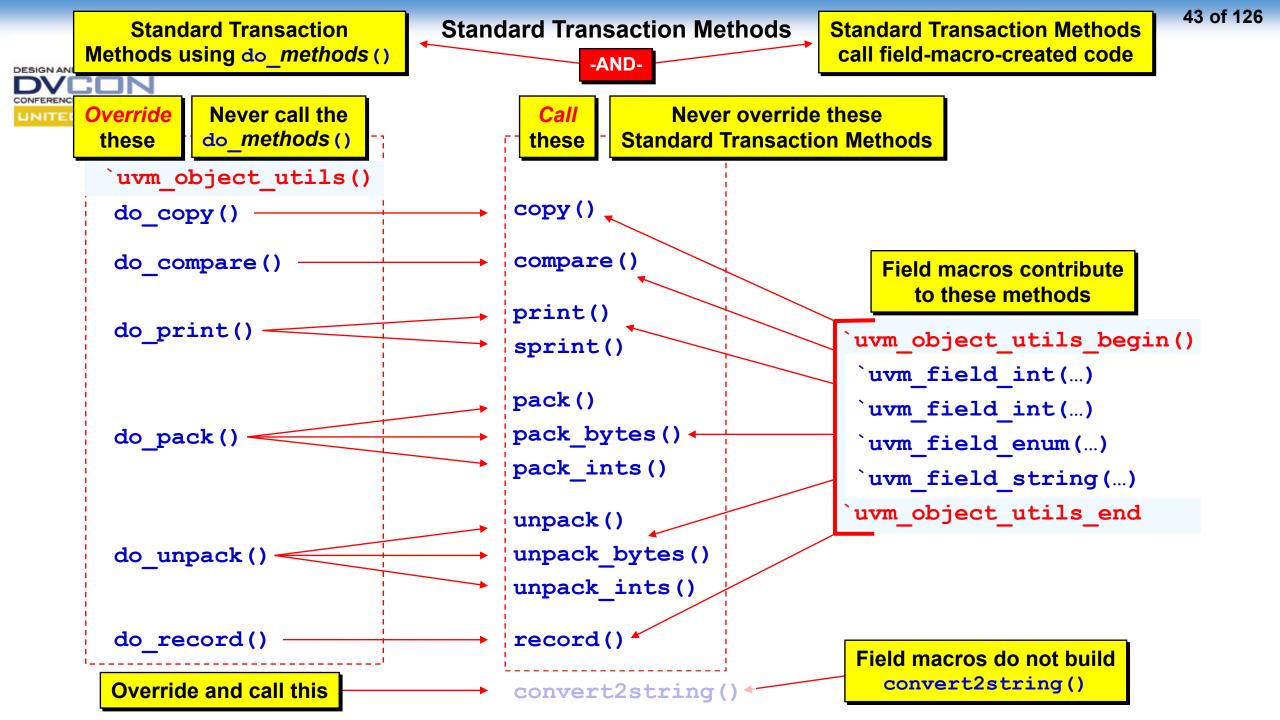

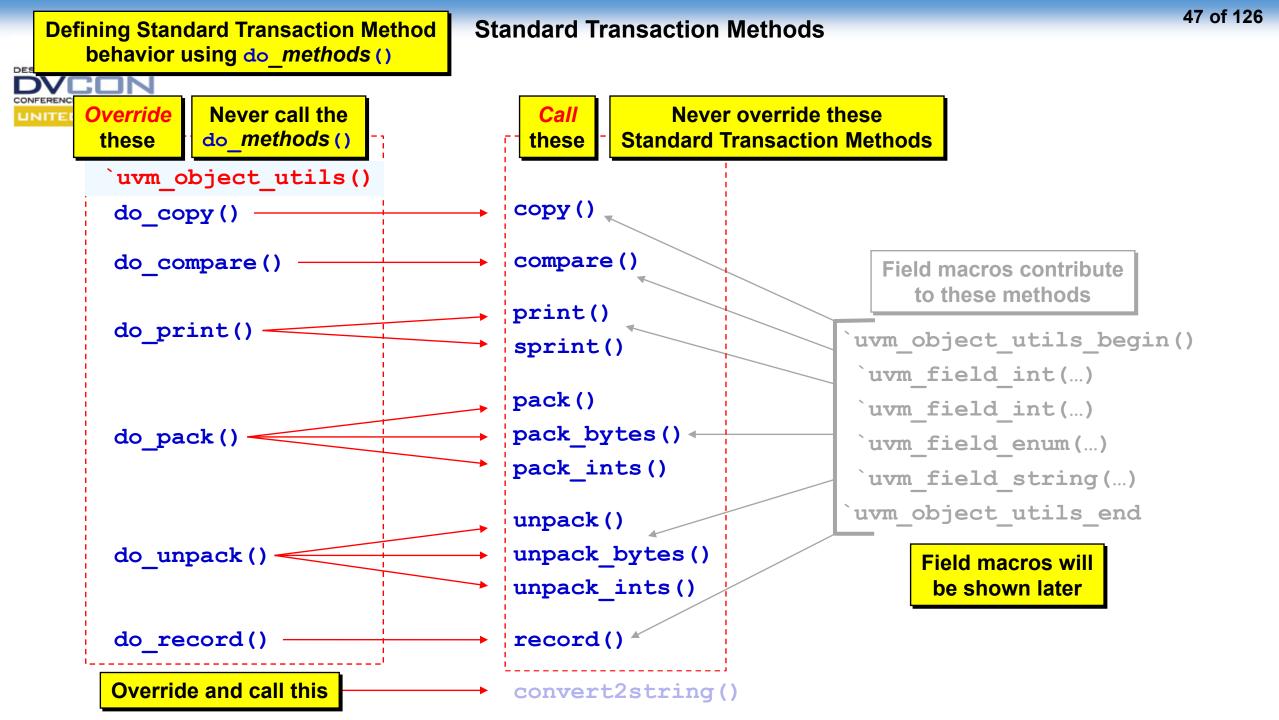

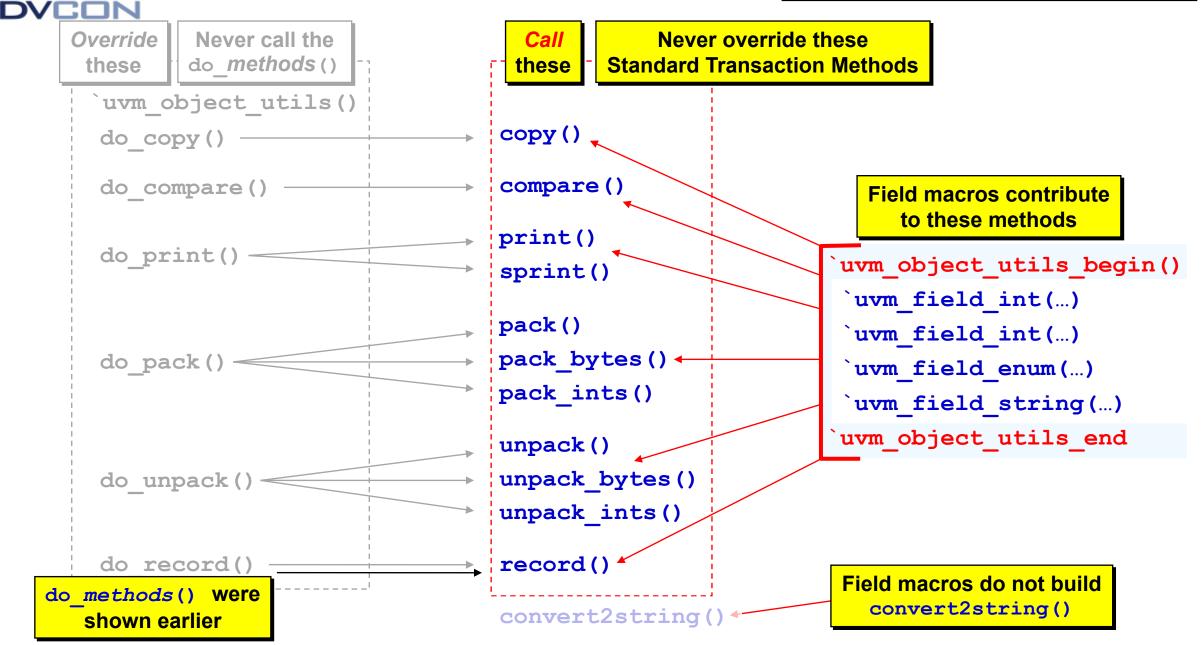

### **Standard Transaction Methods**

39 of 126

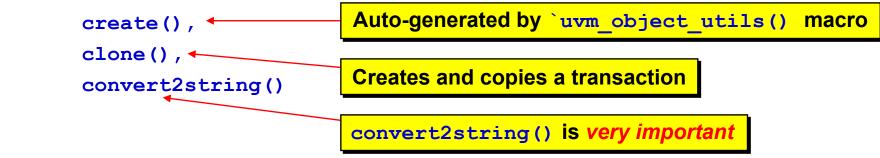

#### **Standard Transaction Methods**

Defined in uvm\_object() base class

• 11 Standard Transaction Methods

• 3 more transaction methods

41 of 126

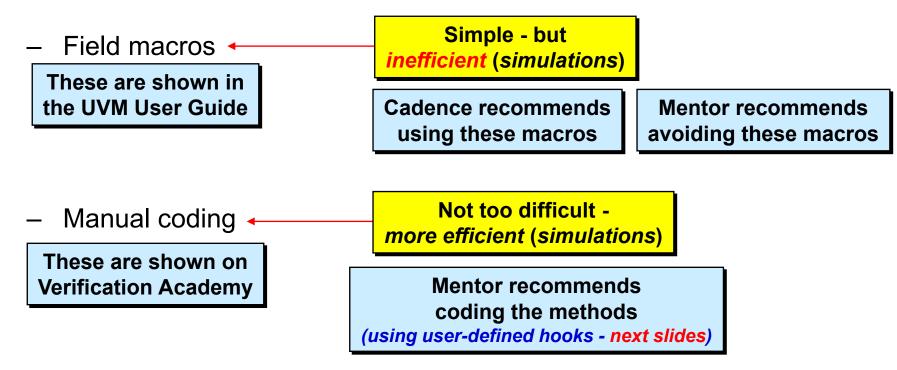

#### **Implementing Transaction Methods**

For User-Defined sequence\_items

- Each transaction should include important methods

- Two ways to implement important transaction methods:

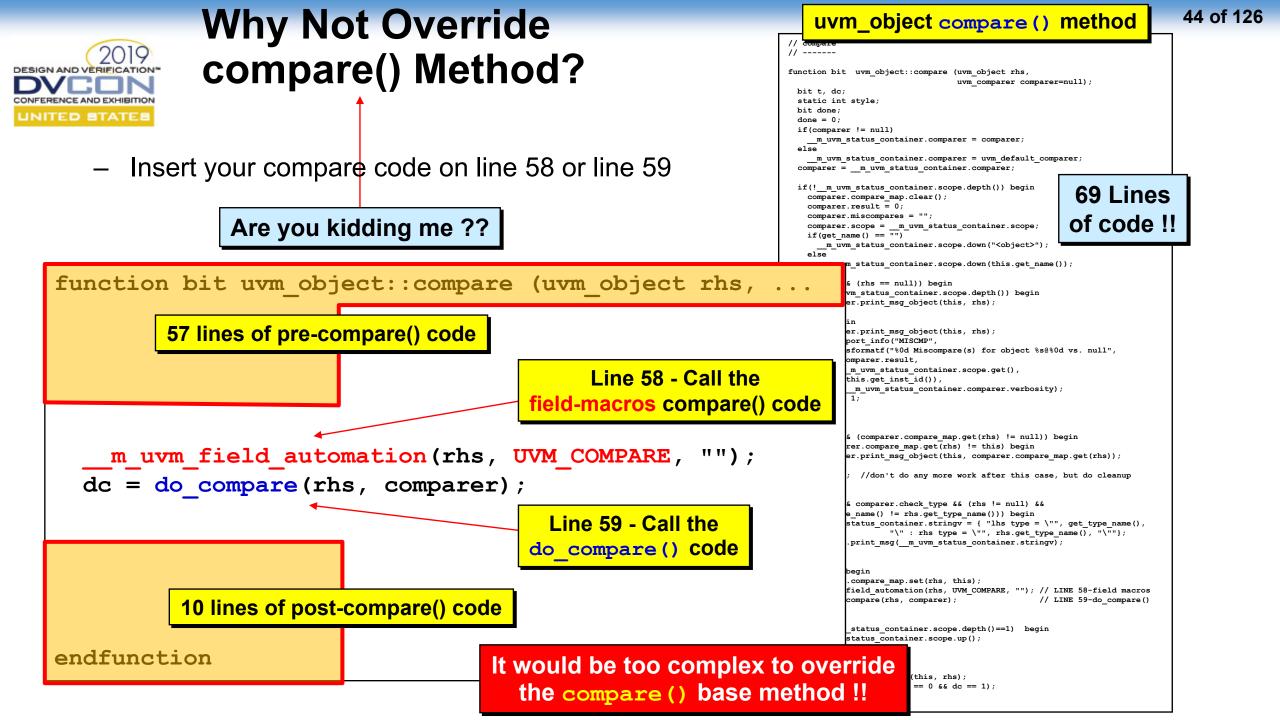

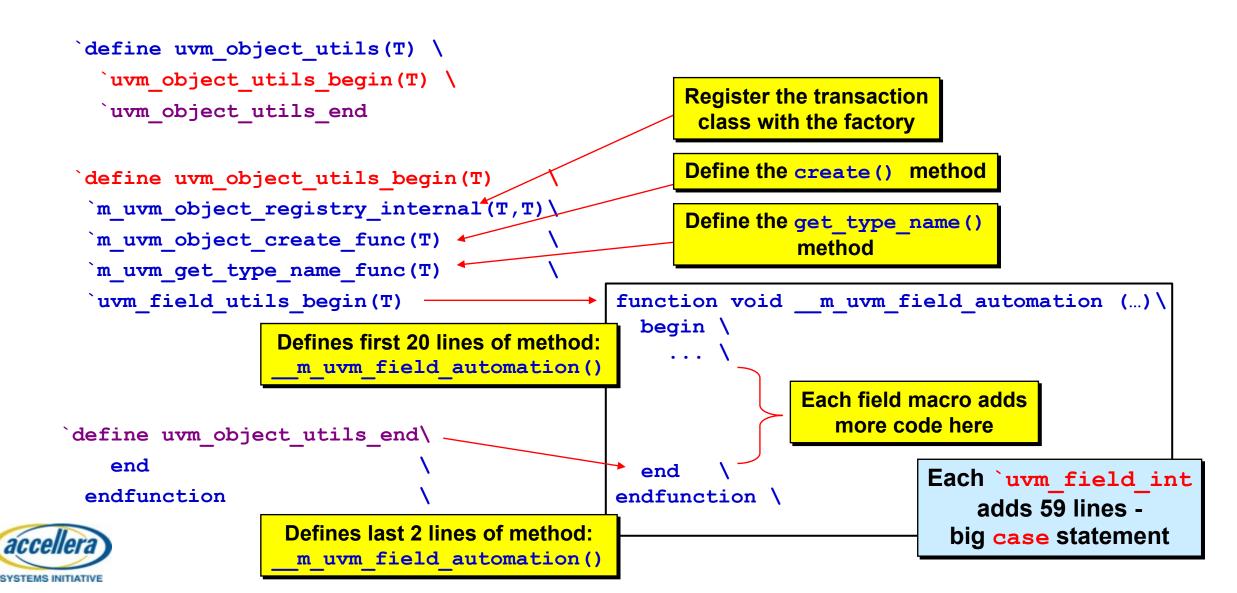

### `uvm\_object\_utils(T)

macros/uvm\_object\_defines.svh

2019 DESIGN AND VERIFICATION DVCDN CONFERENCE AND EXHIBITION UNITED STATES

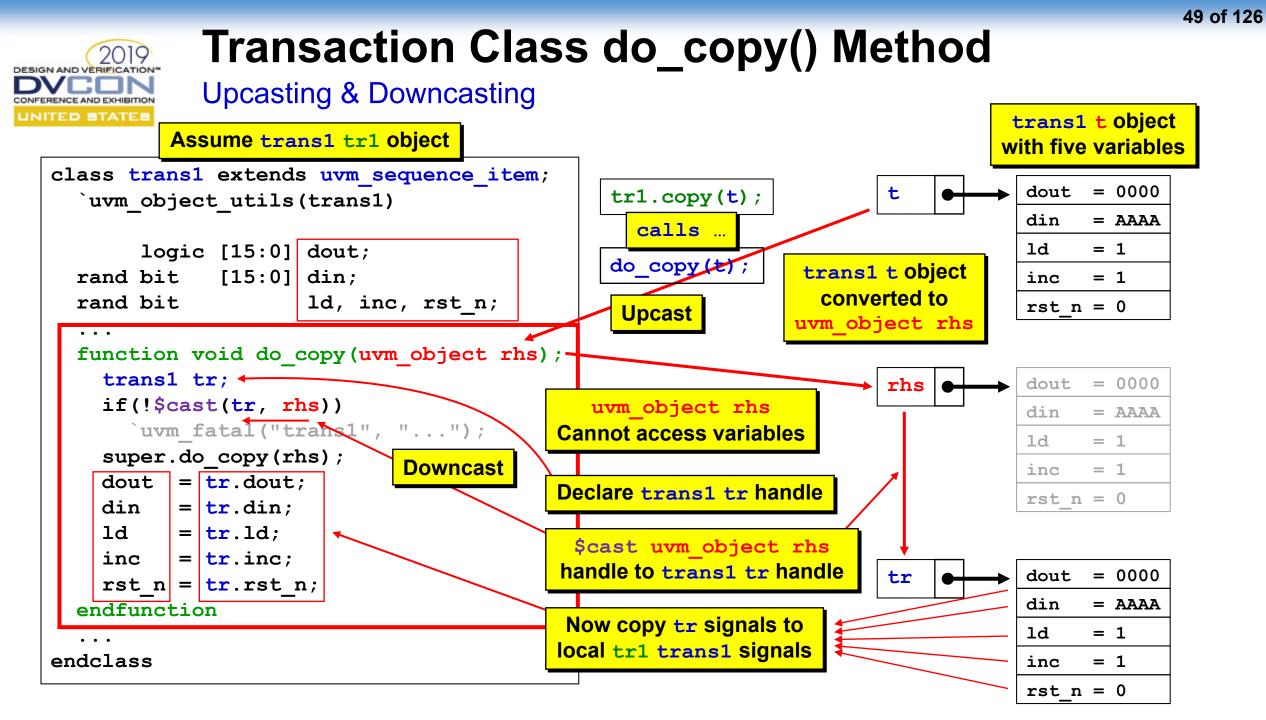

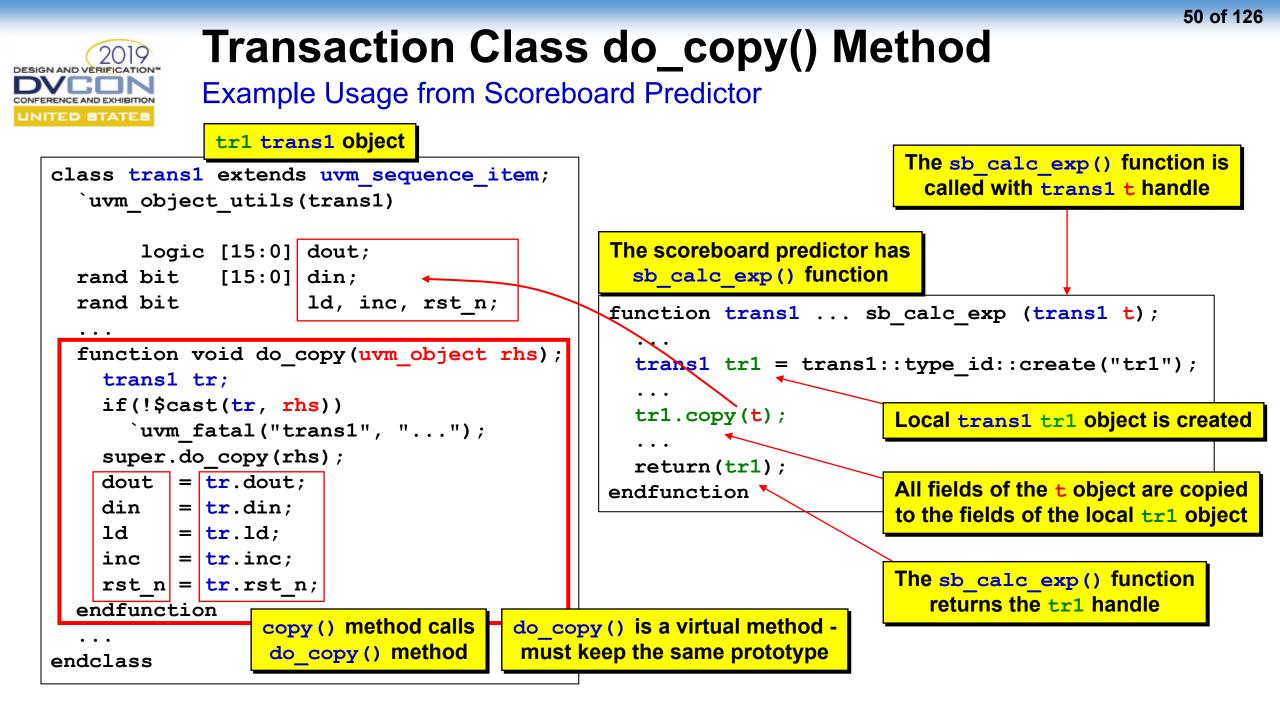

## **Overriding do\_methods()**

# Upcasting & Downcasting Variable Names

Previous slide - We named the local trans1 handle tr

- Many industry examples name the local transaction handle rhs

- Using rhs\_ means that casting is done in the form \$cast(rhs\_, rhs);

This is confusing and therefore a poor practice

• Causes fields to be referenced as rhs\_.field\_1 , ...

Easy to confuse the uvm\_object rhs handle with the transaction class rhs\_ handle

Better practice: Use a transaction handle name like tr

Or another name that is visually distinct

**Guideline:** Declare local transaction handles using distinct names such as tr and avoid local transaction handle names such as rhs\_

accellera

SYSTEMS INITIATIVE

## do\_copy() & do\_compare()

Template Methods

2019 DESIGN AND VERIFICATION DVCDN CONFERENCE AND EXHIBITION UNITED STATES

## **Using Field Macros**

2019 DESIGN AND VERIFICATION

of 126

#### Using Field Macros Requirements

What is required to use field macros?

accellera

SYSTEMS INITIATIVE

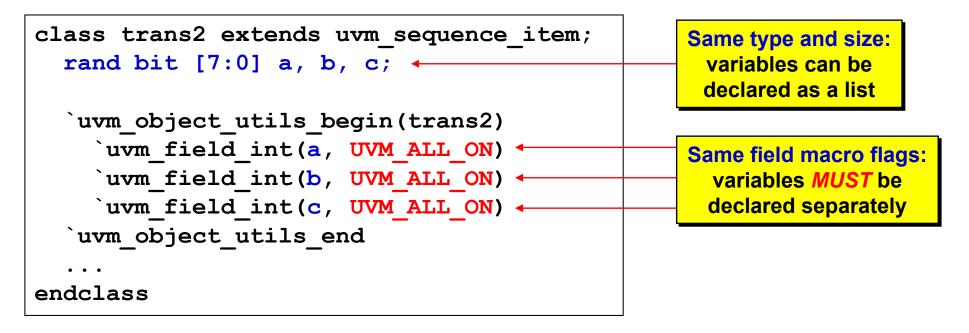

#### **Transaction with Field Macros**

Rules

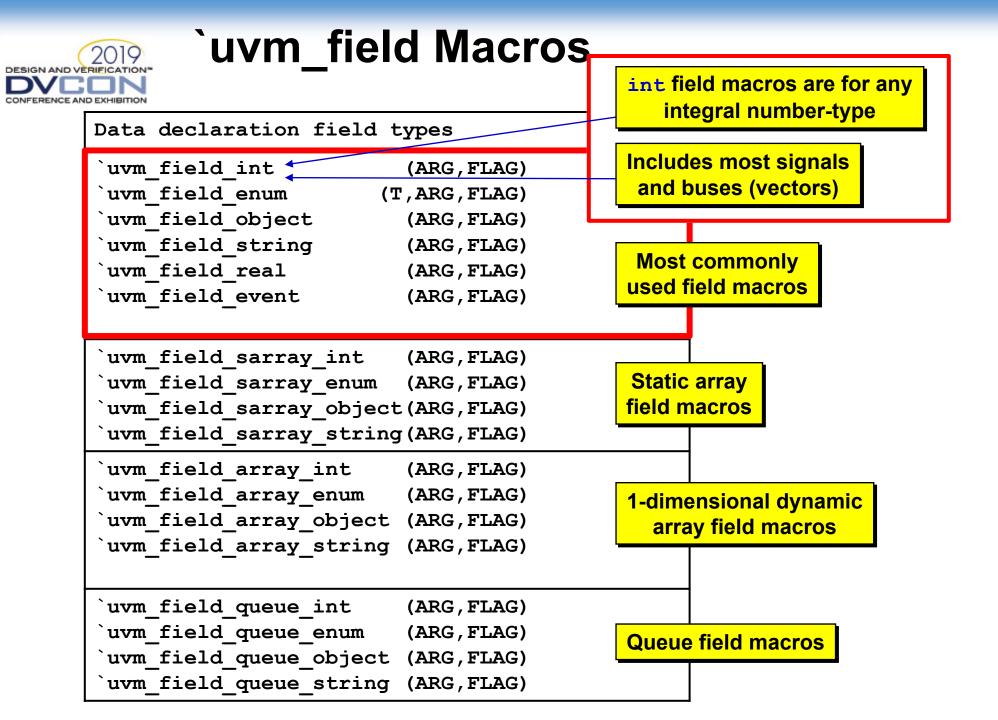

| 2019<br>DESIGN AND VERIFICATION | `uvm_field Mac                                                                                                                                                                 |                                                              | tive array<br>macros                                |                                       |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------|---------------------------------------|

| CONFERENCE AND EXHIBITION       | 1st argument =<br>data-field type2nd argun<br>argun<br>argun<br>array inde                                                                                                     |                                                              |                                                     |                                       |

|                                 | <pre>`uvm_field_aa_string_in `uvm_field_aa_string_st</pre>                                                                                                                     |                                                              | , FLAG)<br>, FLAG)                                  | String<br>associative arrays          |

|                                 | `uvm_field_aa_object_in<br>`uvm_field_aa_object_st                                                                                                                             |                                                              | , FLAG)<br>, FLAG)                                  | Object<br>associative arrays          |

|                                 | <pre>`uvm_field_aa_int_int<br/>`uvm_field_aa_int_int_u<br/>`uvm_field_aa_int_integ<br/>`uvm_field_aa_int_integ<br/>`uvm_field_aa_int_byte</pre>                                | nsigned (ARG<br>er (ARG<br>er_unsigned (ARG<br>(ARG          | , FLAG)<br>, FLAG)<br>, FLAG)<br>, FLAG)<br>, FLAG) |                                       |

|                                 | <pre>`uvm_field_aa_int_byte_<br/>`uvm_field_aa_int_short<br/>`uvm_field_aa_int_short<br/>`uvm_field_aa_int_longi<br/>`uvm_field_aa_int_longi<br/>`uvm_field_aa_int_strin</pre> | int (ARG<br>int_unsigned (ARG<br>nt (ARG<br>nt_unsigned (ARG | , FLAG)                                             | Integral-number<br>associative arrays |

| accellera                       | `uvm_field_aa_int_key<br>`uvm_field_aa_int_enumk                                                                                                                               | (KEY, ARG<br>ey (KEY, ARG                                    | ·                                                   |                                       |

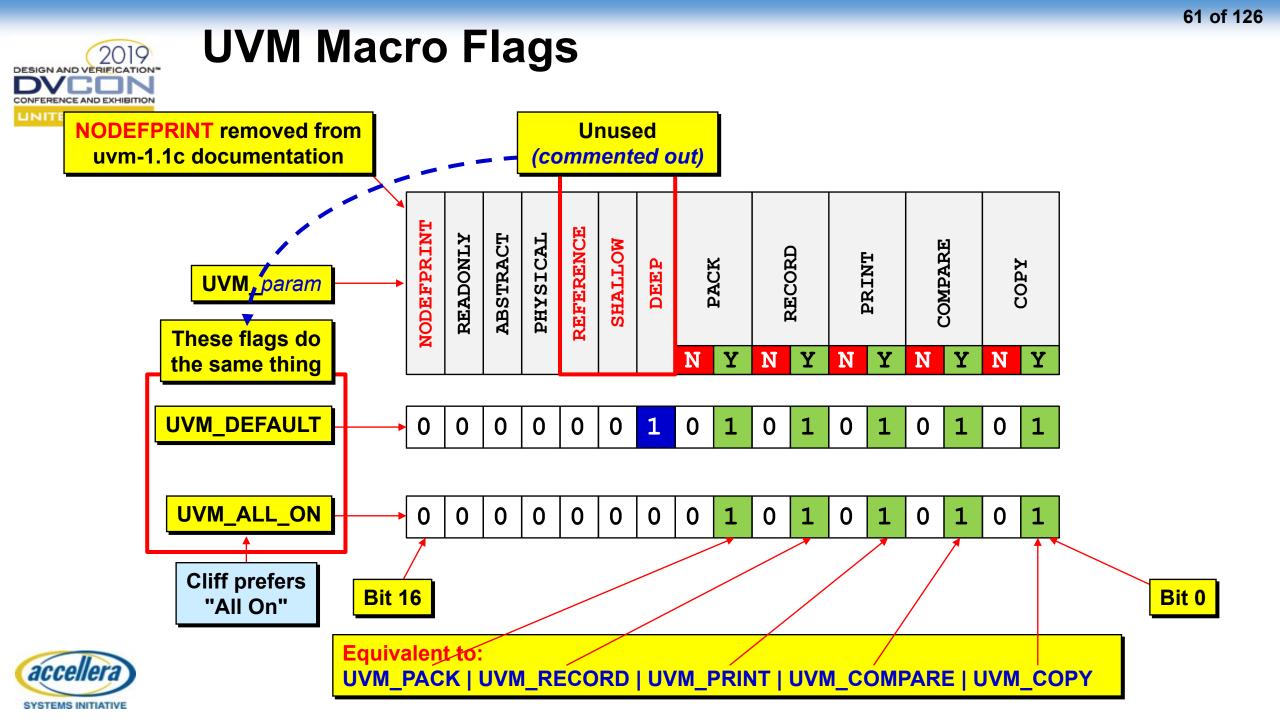

#### **UVM Field Macro Flags**

Other macro flags on the next slide

UVM\_ALL\_ON - Automatically creates the following important core data methods:

```

copy() & compare()

pack() & unpack()

record()

print() & sprint()

```

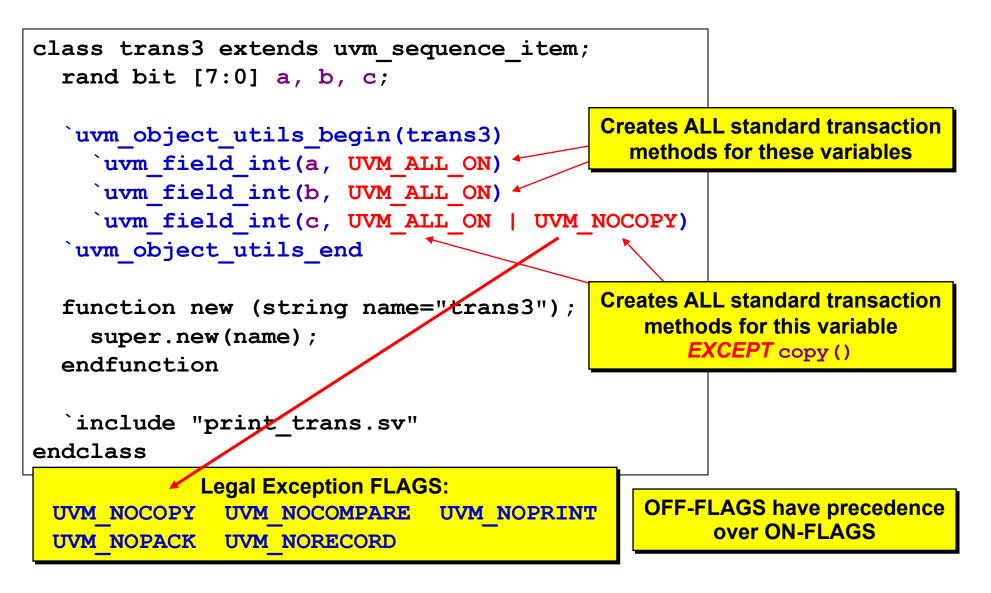

#### **UVM Field Macro Flags**

Multiple flags can be bitwise OR-ed together

UVM Field Macro Flags

UVM\_ALL\_ON UVM\_DEFAULT Set all operations on (default) Use the default flag settings

Do not copy this field

Do not compare this field

UVM\_NOCOPY UVM\_NOCOMPARE UVM\_NOPRINT UVM\_NODEFPRINT UVM\_NOPACK

Do not print this field (not documented in User Guide or Reference Manual) Do not pack or unpack this field

UVM\_PHYSICAL UVM\_ABSTRACT UVM\_READONLY Treat as a physical field. Use physical setting in policy class for this field Treat as an abstract field. Use the abstract setting in the policy class for this field Do not allow setting of this field from the set\_\*\_local methods

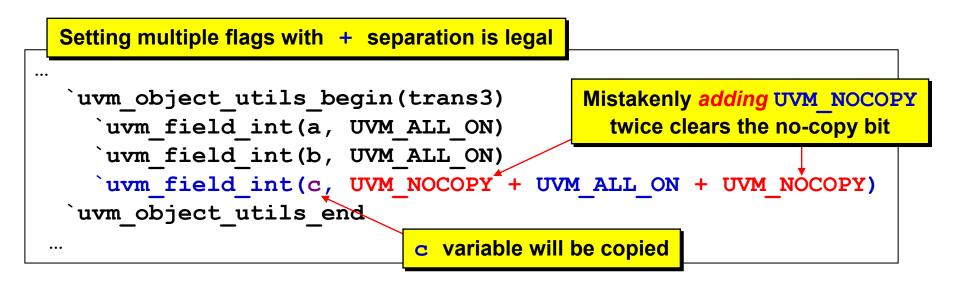

Can also add the flags together but bitwise or'ed is safer (avoids double incrementing)

accellera

SYSTEMS INITIATIVE

#### **Field Macro Flags**

#### Adding Multiple Flags

### **Adding Field Macro Flags**

Multiple Flags Using | or +

2019 DESIGN AND VERIFICATION DVCDN CONFERENCE AND EXHIBITION UNITED STATES

### **Efficiency Benchmarks**

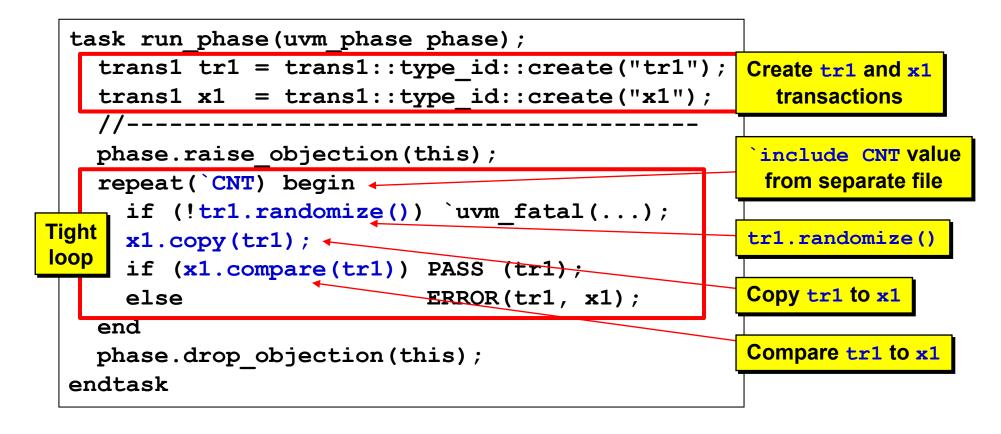

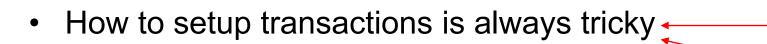

#### **Benchmarking Methodology**

From test1.sv File

- **test1** component with a tight loop:

- Transactions repeatedly: (1) randomize() (2) copy() (3) compare()

### **Benchmarking Methodology**

From trans1.sv Files

- trans1 transactions benchmarks:

- 5 rand inputs +

- 5 **rand** outputs

- 5 non-rand outputs

- do\_copy() & do\_compare()

- Field macros

- do\_copy() with & without super.do\_copy()

- do\_compare() with & without super.do\_compare()

All benchmark code is

Penalty for unnecessary randomization of outputs??

Penalty for using field macros??

Penalty for unnecessary calls to super-base methods??

#### **Benchmark Results**

2018 Benchmarks

| Penalty Benchmark                                                                               | Simulator A  | Simulator B  |                                                       |

|-------------------------------------------------------------------------------------------------|--------------|--------------|-------------------------------------------------------|

|                                                                                                 | CNT=100M     | CNT=100M     |                                                       |

| Unnecessary rand-outputs<br>-vs- non-randomized outputs<br><i>(Using</i> do_ <i>methods</i> ()) | 16.5% slower | 11.2% slower | Do NOT randomize                                      |

| Unnecessary rand-outputs -vs-<br>non-randomized outputs<br><i>(Using Field Macros)</i>          | 12.1% slower | 5.3% slower  | transaction output fields                             |

| Penalty for using Field Macros<br>-vs- using do_ <i>methods</i> ()                              | 6.0% slower  | 13.3% slower | Using Field Macros<br>has a penalty                   |

| Penalty for calling unnecessary<br>super.do_ <i>methods</i> ()                                  | 2.4% slower  | 6.7% slower  | Calling super.do_methods()<br>has a small-ish penalty |

#### **UVM Basic Transaction Objects**

• On the next slides, we will build:

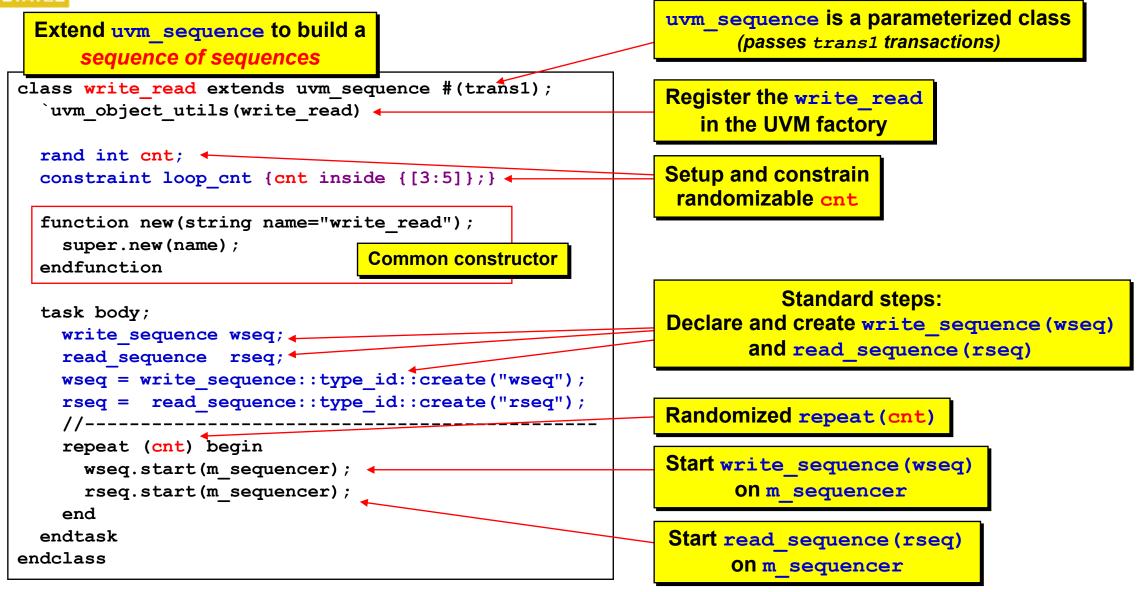

### Sequence: write\_read

(sequence defined using other sequences)

| 2019<br>DESIGN AND VERIFICATION* | `uv                    | /m_do l            | Macros                              |    |              |                   |                  |                |             |              |             |               |  |

|----------------------------------|------------------------|--------------------|-------------------------------------|----|--------------|-------------------|------------------|----------------|-------------|--------------|-------------|---------------|--|

|                                  | r                      |                    | uvm_do sequence<br>Dr sequence item |    |              |                   |                  |                |             | `uvi<br>acti | n_do<br>ons |               |  |

|                                  |                        | VI SEQUEICE I CEII |                                     |    | Macro Inputs |                   |                  | UV             | UVM actions |              |             |               |  |

|                                  |                        |                    |                                     |    | SEQ_OR_ITEM  | <b>S</b> equencer | <b>P</b> RIORITY | {CONSTRAINTS } | create()    | start_item() | randomize() | finish_item() |  |

| Commo                            |                        | `uvm_do(I)         |                                     |    | X            |                   |                  |                | Χ           | Χ            | Χ           | Х             |  |

|                                  | Common                 | `uvm_do_with       | n(I, <mark>{C}</mark> )             |    | Χ            |                   |                  | Χ              | Χ           | Χ            | Χ           | Χ             |  |

| Co                               | mmon                   | `uvm_do_on(]       | I,S)                                |    | X            | Χ                 |                  |                | Χ           | Χ            | Χ           | Х             |  |

| vseq                             | <mark>sequencer</mark> | `uvm_do_on_v       | with(I,S, <mark>{C}</mark> )        |    | X            | Χ                 |                  | Х              | Χ           | X            | Χ           | Х             |  |

|                                  |                        | `uvm_do_pri        | (I, <mark>P</mark> )                |    | X            |                   | Х                |                | Х           | X            | Χ           | Х             |  |

|                                  | Less                   | `uvm_do_pri_       | _with(I,P,{C})                      |    | X            |                   | X                | Х              | Х           | X            | Χ           | Х             |  |

| Co                               | Common                 | `uvm_do_on_p       | pri(I,S,P)                          |    | X            | X                 | Χ                |                | Χ           | X            | Χ           | Х             |  |

| accellera                        | [                      | `uvm_do_on_p       | pri_with(I,S,P,{C)                  | }) | X            | Χ                 | X                | Χ              | X           | Χ            | X           | X             |  |

SYSTEMS INITIATIVE

74 of 126

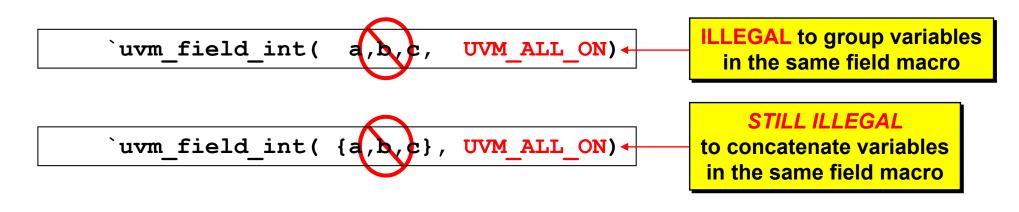

### Summary of Rules

- do\_methods() rule: you must use `uvm\_object\_utils()

- Field macros rule: declare the transaction variables before calling field macros

- Field macros rule: declare variables before registering the transaction with the factory

- Field macros rule: you must use: `uvm\_object\_utils\_begin() / `uvm\_object\_utils\_end

- Field macros rule: each variable in a separate field macro

Variables cannot be grouped into a common field macro definition

## Summary of Important Guidelines

• Guideline: do not directly override standard trans methods

copy(), compare(), etc.

- Guideline: never manually implement the create() method

Call `uvm\_object\_utils() to automatically implement create()

Get a life !!

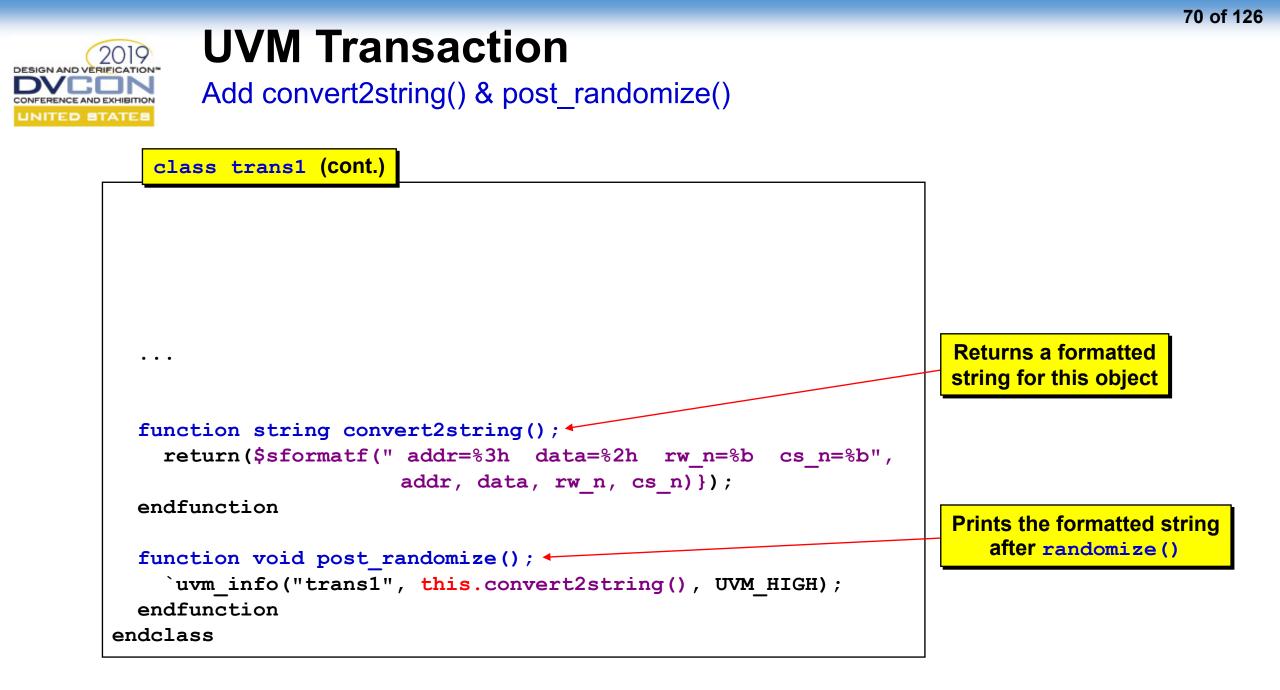

- Guideline: Transactions should include a convert2string() method

Always !!

- Guideline: Avoid using the print() and sprint() methods

The outputs are verbose

- Guideline: <u>If you must</u>, use **sprint()** over **print()**

Better yet ... use convert2string() convert2string() is more simulation

and more print-space efficient

CONFERENCE AND EXHIBITION

# **UVM Basic Message Commands**

Same techniques apply to OVM

**Good reference paper:**

UVM Message Display Commands - Capabilities, Proper Usage and Guidelines www.sunburst-design.com/papers/CummingsSNUG2014AUS\_UVM\_Messages.pdf

77 of 126

## Introduction

• UVM verbosity settings are **NOT** message priority settings!

UVM Verbosity *≠* Message Priority !!

- **UVM\_LOW** is not a low priority message

- **UVM\_LOW** is one of the highest priority messages !!

- Reference sources and public examples ... get it wrong !!

- The paper offers guidelines on proper usage

- The paper shows useful messaging tricks

UVM User Guide UVM Class Reference +2 recent UVM books

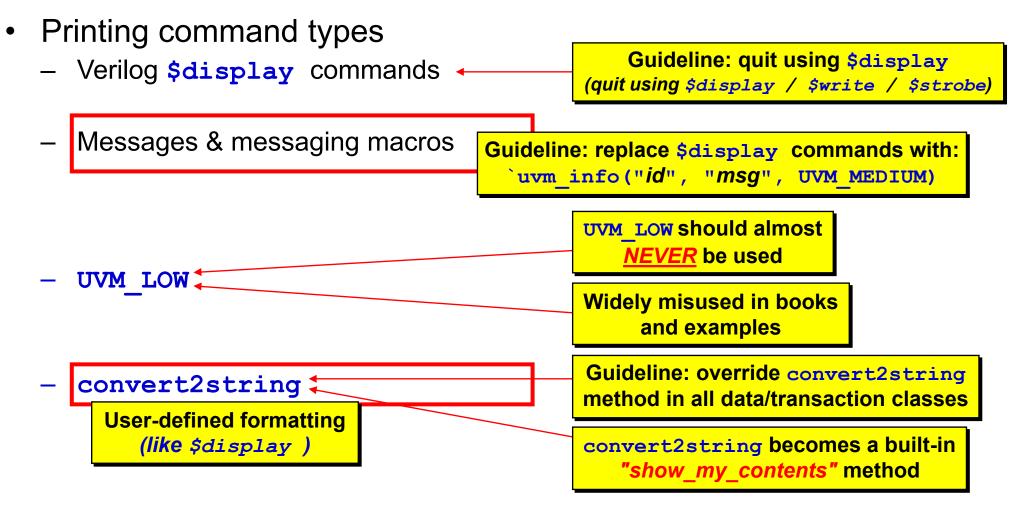

## **UVM Basic Printing Guidelines**

### **UVM Message Facilities**

Good messaging reference: *A Practical Guide to Adopting the Universal Verification Methodology (UVM)* Rosenberg & Meade

- \$display does not allow easy message filtering

- uvm\_report\_info/fatal\* methods allow message filtering

Macros avoid \$sformat processing

accelle

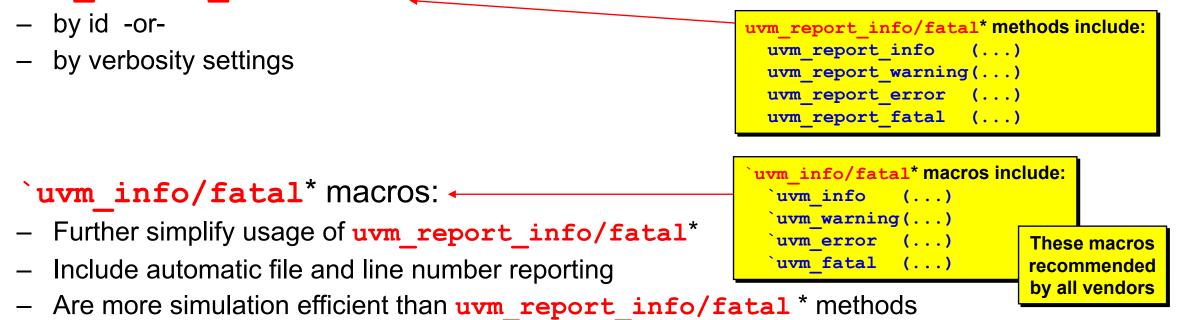

## uvm\_report\_info/fatal\* Messages

- UVM has reporting services built into all <u>uvm</u> component(s)

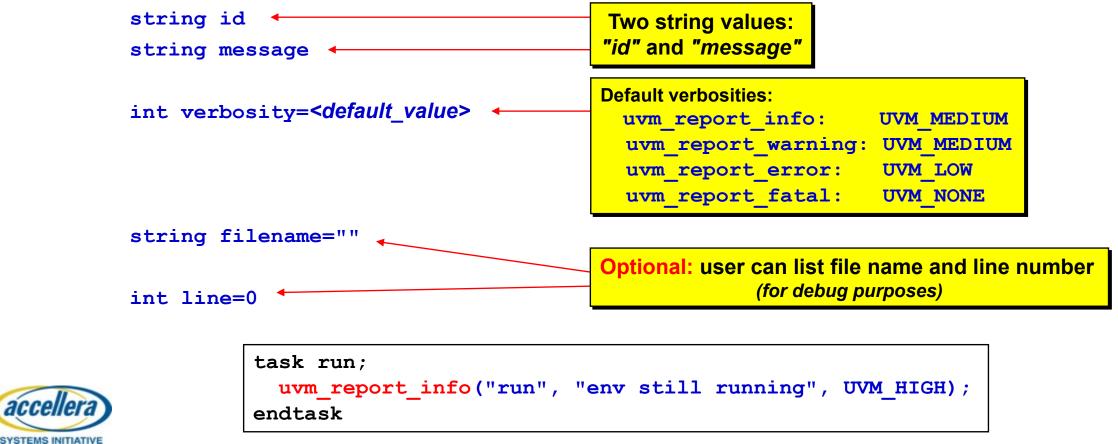

- UVM messages take up to 5 arguments (last 3 have defaults) •

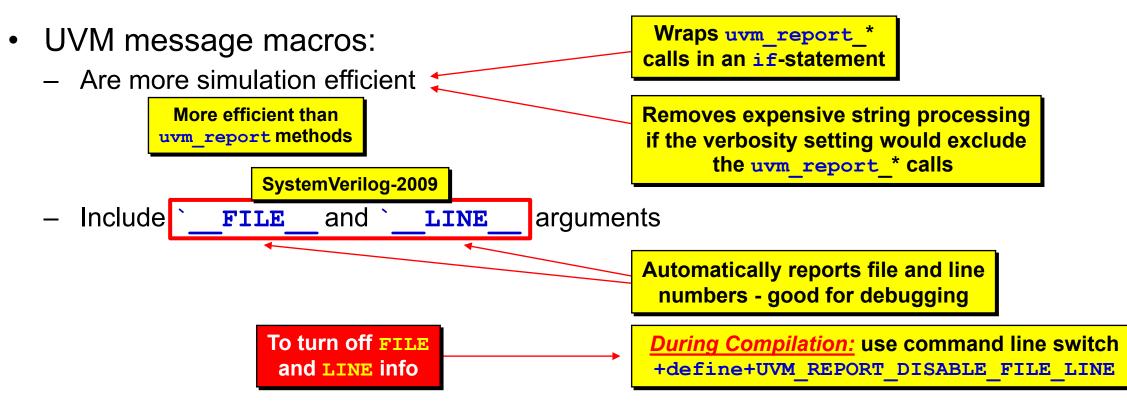

### `uvm\_info/fatal\* Macros

• UVM macros are more simulation efficient than messages

Explanation on the next slide

• UVM macros take 2-3 arguments, depending on macro type

string id

string message

int verbosity

Only uvm\_info allows

a verbosity setting

Default macro verbosities that cannot be changed: `uvm\_warning: UVM\_NONE

`uvm\_error: UVM\_NONE

`uvm\_fatal: UVM\_NONE

Macros automatically include file name and line number (good for debugging)

```

task run;

`uvm_info("run", " env still running", UVM_HIGH)

endtask

```

## **UVM Messaging Macro Advantages**

- `uvm\_warning / error / fatal include pre-defined default UVM\_VERBOSITY settings

Avoids new-user mistakes (like setting uvm\_report\_error verbosity to UVM\_HIGH)

### convert2string()

- convert2string() is a virtual function defined in uvm\_object

- **convert2string()** is user-defined in the data/transaction class

- This virtual function is a user-definable hook

- From uvm\_object base class

Default returns ""

Called directly by the user

Users provide object info in the form of a string

No uvm\_printer policy object required

Format is fully user-customizable

Guideline: add convert2string() to all data/transaction classes

Simple & simulation efficient

Simple & simulation efficient

Fields declared in `uvm\_field\_\* macros will not automatically appear in calls to convert2string()

No uvm\_printer policy object required

Good for applications that do not require consistent formatting offered by: print/sprint/do\_print

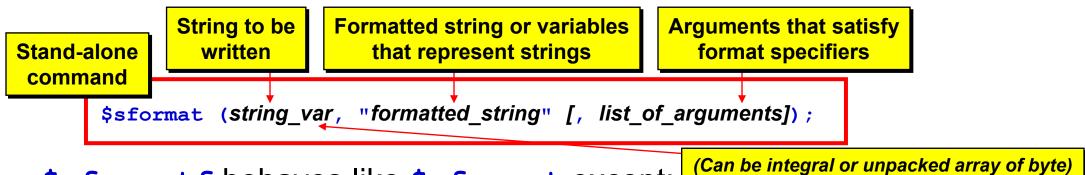

### **\$sformat, \$sformatf & \$psprintf Commands** What Are The Differences?

• **\$sformat** is used to generate a formatted string

- \$sformatf behaves like \$sformat except:

- Function that returns a string

- Therefore no first string\_var argument

### **UVM Message Verbosity**

- What is verbosity?

- Highly verbose simulations would show lots of messages

- *Minimally verbose* simulations would only show important messages

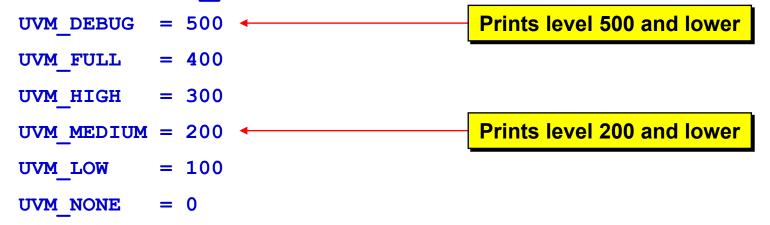

- UVM has built-in enumerated type: uvm\_verbosity

- Defines standard verbosity levels for reports:

| UVM_DEBUG  | Print if selected verbosity is <b>UVM_DEBUG</b>           |                         |

|------------|-----------------------------------------------------------|-------------------------|

| UVM_FULL   | Print if selected verbosity is <b>UVM_FULL</b> or lower   |                         |

| UVM_HIGH   | Print if selected verbosity is <b>UVM_HIGH</b> or lower   |                         |

| UVM_MEDIUM | Print if selected verbosity is <b>UVM_MEDIUM</b> or lower |                         |

| UVM_LOW    | Print if selected verbosity is <b>UVM_LOW</b> or lower    | Cannot be disabled by   |

| UVM_NONE   | Print always 🔸                                            | verbosity level setting |

Lower verbosity = fewer messages

Higher verbosity = more messages

## **UVM Message Verbosity**

**Equivalent Verbosity Values**

• UVM built-in **uvm\_verbosity** enumerated values:

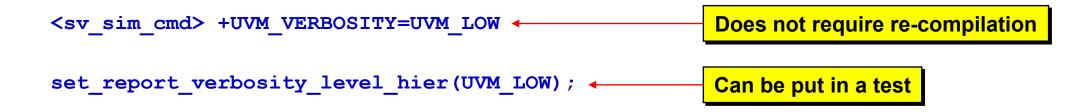

• Two ways to change the verbosity for debugging:

2019 DESIGN AND VERIFICATION DVCDN CONFERENCE AND EXHIBITION UNITED STATES

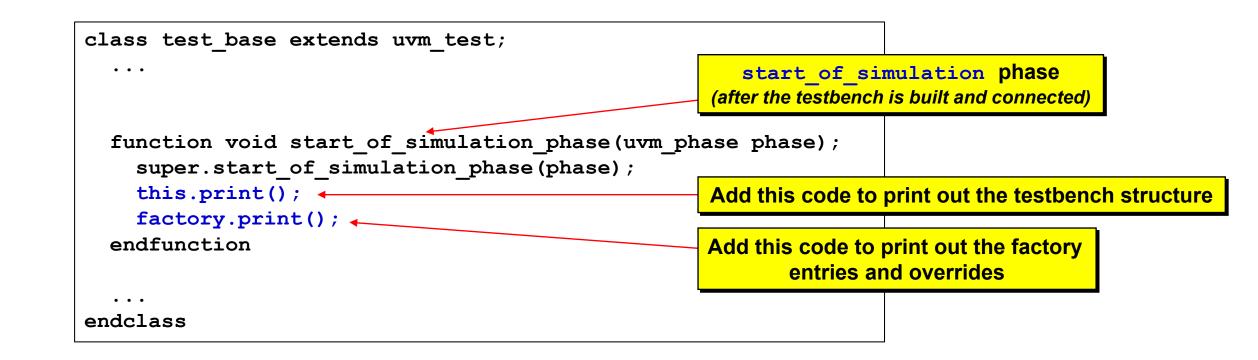

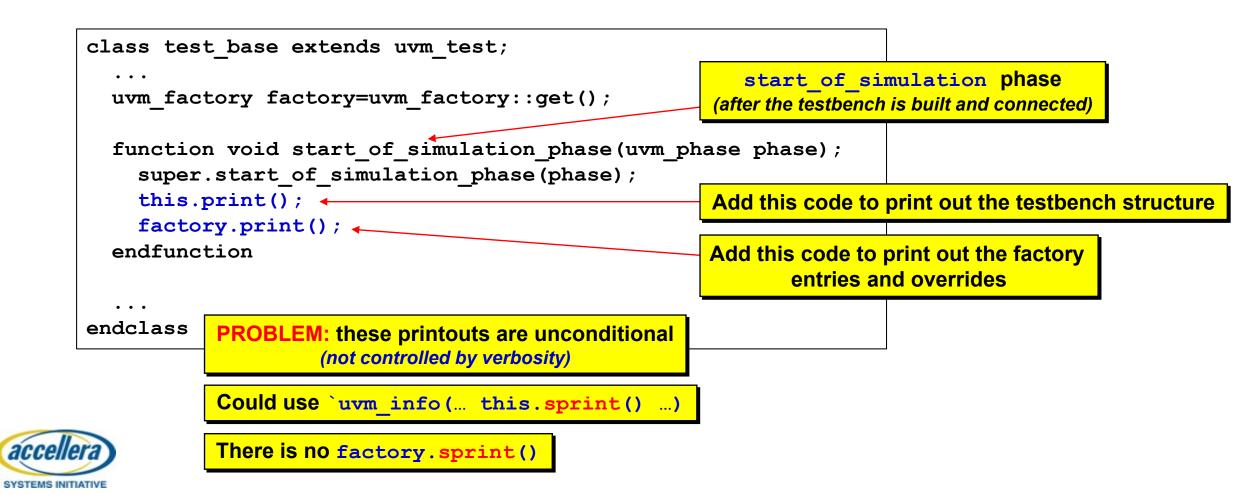

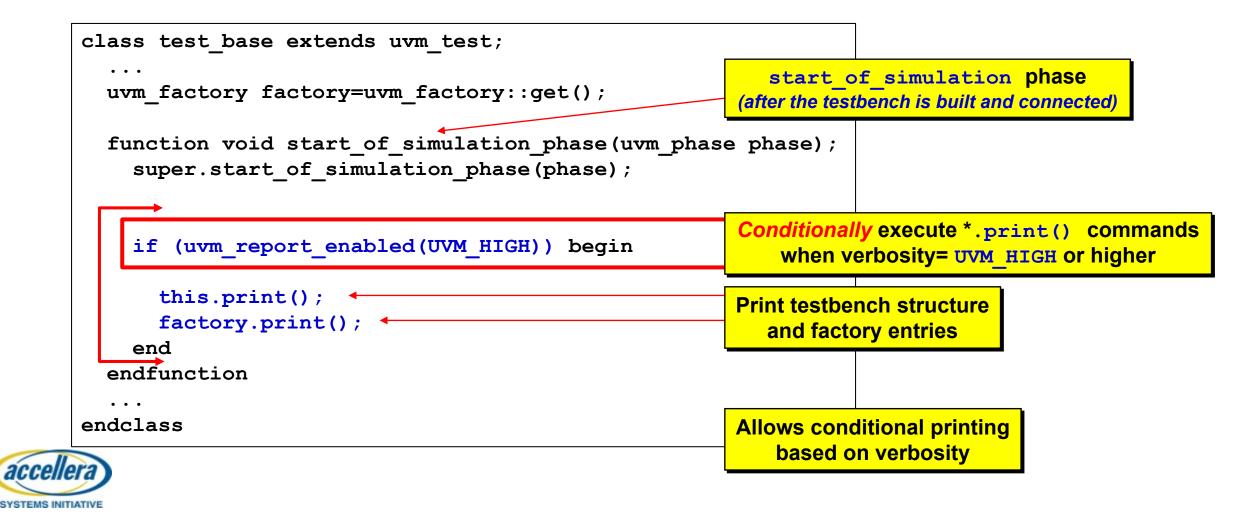

# **Useful Debugging Trick**

## **Testbench & Factory Debugging**

**Unconditional Printing**

Good technique to view testbench and factory setup

• Better technique to view testbench and factory setup

2019 DESIGN AND VERIFICATION DVCDN CONFERENCE AND EXHIBITION UNITED STATES

# **UVM Documentation Errors**

91 of 126

### **Existing Documentation Problems**

- UVM\_LOW is pervasive in References, Books & Examples

- UVM User Guide

- Uses **\$display** once

- Uses 3 `uvm\_info macros with bugs in the examples

- Uses 5 `uvm\_info macro examples with UVM\_LOW wrong verbosity

- Uses 2 `uvm\_info macro examples without UVM\_LOW correct!

#### - UVM Class Reference

- Uses 1 `uvm\_info macro with bugs in the example

- Uses 3 `uvm\_info macro examples with UVM\_LOW wrong verbosity

- Uses 2 `uvm\_info macro examples without UVM\_LOW correct!

- Popular UVM Book published in 2013

- More than 20 examples improperly use UVM\_LOW

- Popular UVM Beginner's Guide published in 2013

- More than 30 examples improperly use UVM\_LOW

No wonder the UVM books get it wrong!

For low-priority messages

### **Summary of Important Guidelines**

Sunburst Design Usage Guidelines Think of `uvm\_info as your new \$display command

| Macro Type/Verbosity            | Usage Guideline                         |                      |  |  |  |  |  |

|---------------------------------|-----------------------------------------|----------------------|--|--|--|--|--|

| `uvm_fatal ()                   | fatal - test-aborting errors            | Non-maskable*        |  |  |  |  |  |

| `uvm_error ()                   | non-aborting simulation errors          |                      |  |  |  |  |  |

| `uvm_warning ()                 | error-inject warnings                   | Use sparingly!       |  |  |  |  |  |

| `uvm_info ( UVM_NONE)           | for final reports                       |                      |  |  |  |  |  |

| `uvm_info ( UVM_LOW)            | high priority messages 🛛 🗸              | Almost always prints |  |  |  |  |  |

| `uvm_info ( UVM_MEDIUM)         | normal messages - replaces \$dis        | play                 |  |  |  |  |  |

| Above messages print by default |                                         |                      |  |  |  |  |  |

| `uvm_info ( UVM_HIGH)           | (1) passing transactions                |                      |  |  |  |  |  |

|                                 | (2) conditionally print testbench & fac | tory info            |  |  |  |  |  |

| `uvm_info ( UVM_FULL)           | print UVM status messages               |                      |  |  |  |  |  |

| `uvm_info ( UVM_DEBUG)          | add debug messages                      | Almost shugup OEE    |  |  |  |  |  |

|                                 |                                         | Almost always OFF    |  |  |  |  |  |

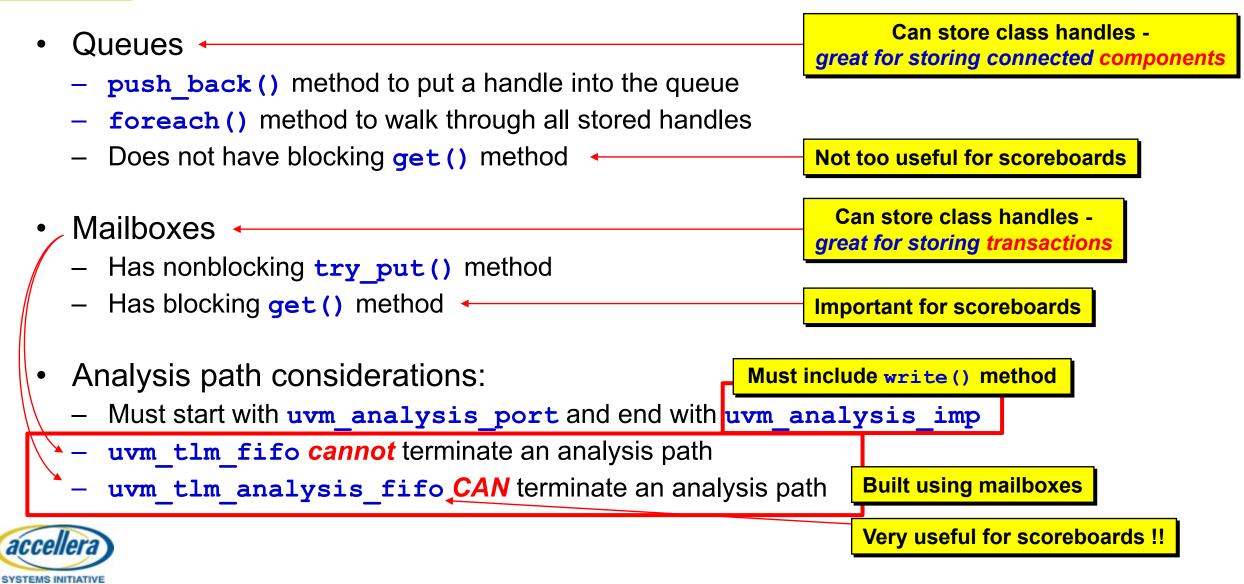

### Section Agenda

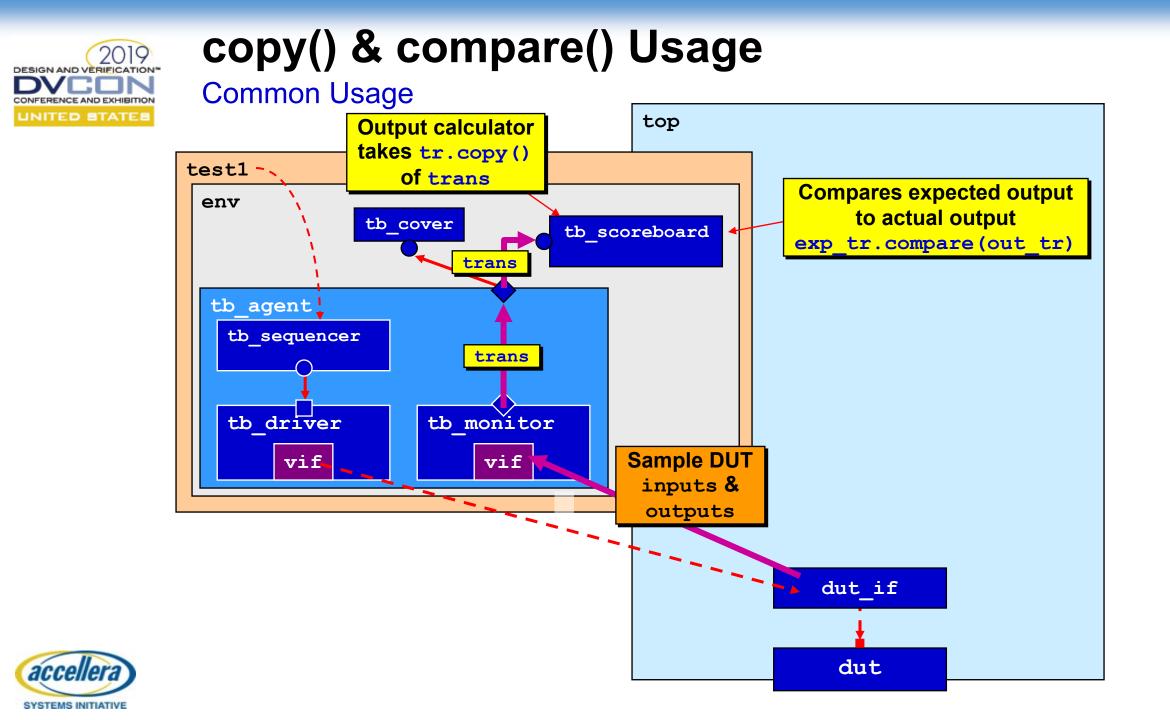

Using UVM Analysis Ports & Paths

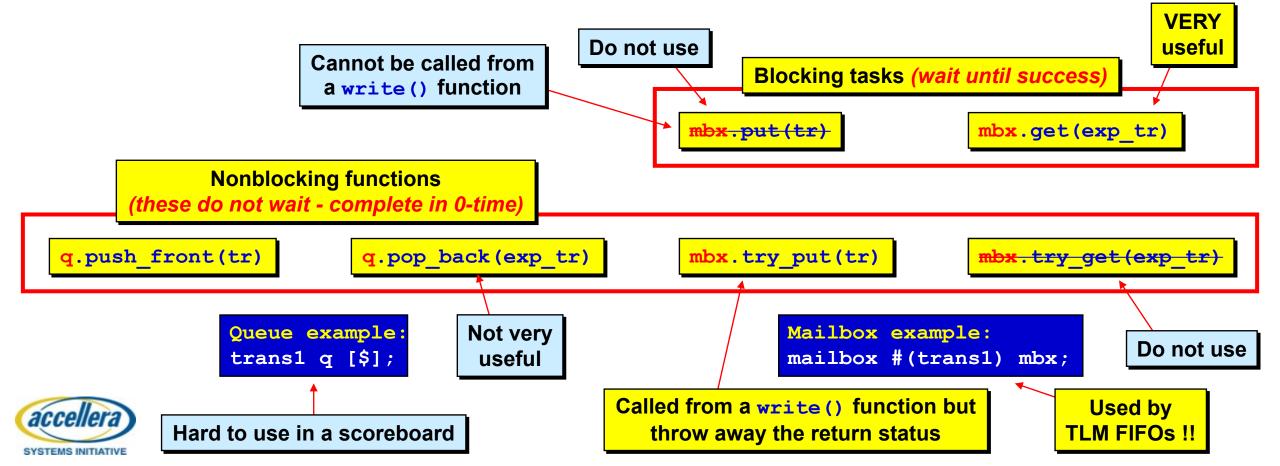

- Basic queues, mailboxes and TLM FIFOs

1<sup>st</sup> pass

- Subscriber satellite TV analogy

- Analysis paths & analysis ports, exports, and imps

- TLM FIFOs

- Importance of the copy () method

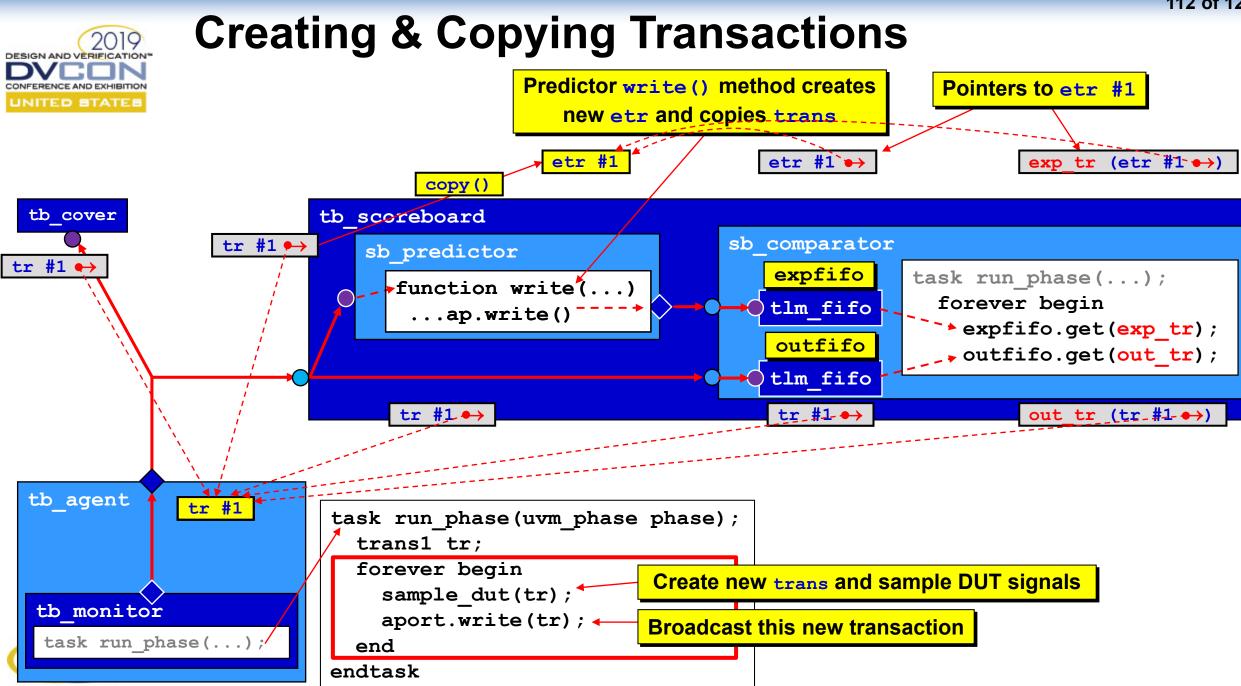

- How analysis port connections work write() method

- Summary & Conclusions

The paper has more details and more examples

More detail

## Important SystemVerilog Features

### Subscriber Satellite TV Analogy

- Two ways to watch a broadcast satellite TV program

- Watch the program live

- Record the program to a DVR to view later

- Satellite programs are broadcast as scheduled

- No way to restart a broadcast program

There might be 1,000's of viewers

There might be *NO* viewers

No way to communicate back to the satellite

Other viewers would object to restarting the program

Subscribers not allowed to change the live program

With the right equipment, you can modify your copy

2019 DESIGN AND VERIFICATION DVCDN CONFERENCE AND EXHIBITION UNITED STATES

# **Analysis Port Connections**

and TLM FIFOs

97 of 126

accelle

SYSTEMS INITIATIVE

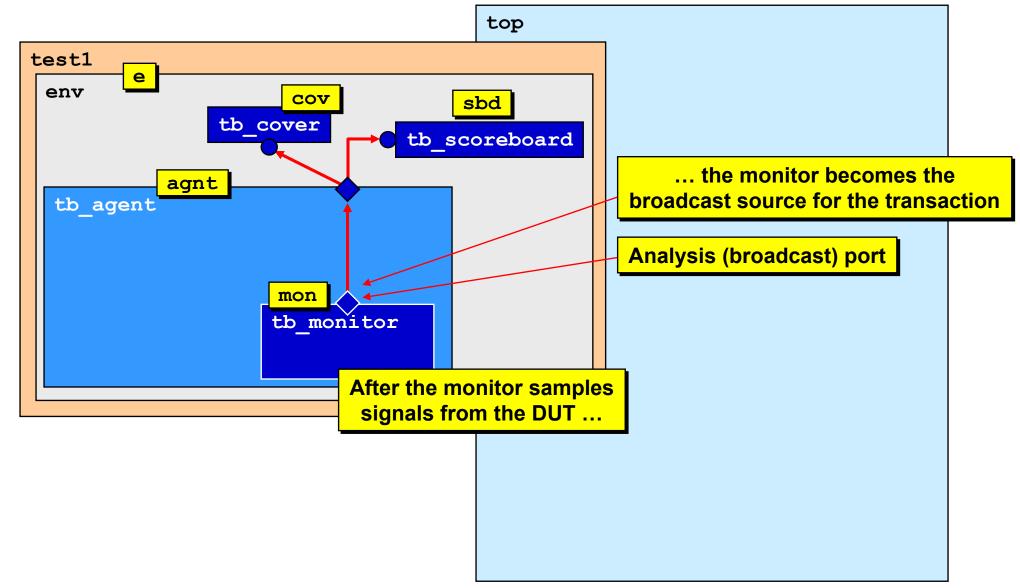

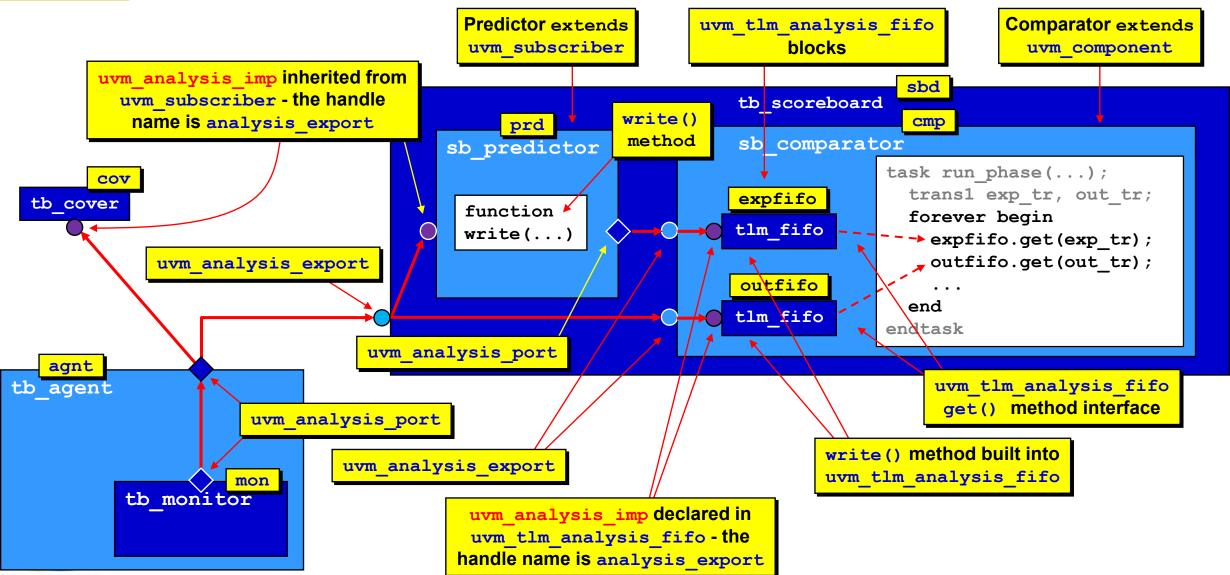

### **Common UVM Components**

**Overview Block Diagram**

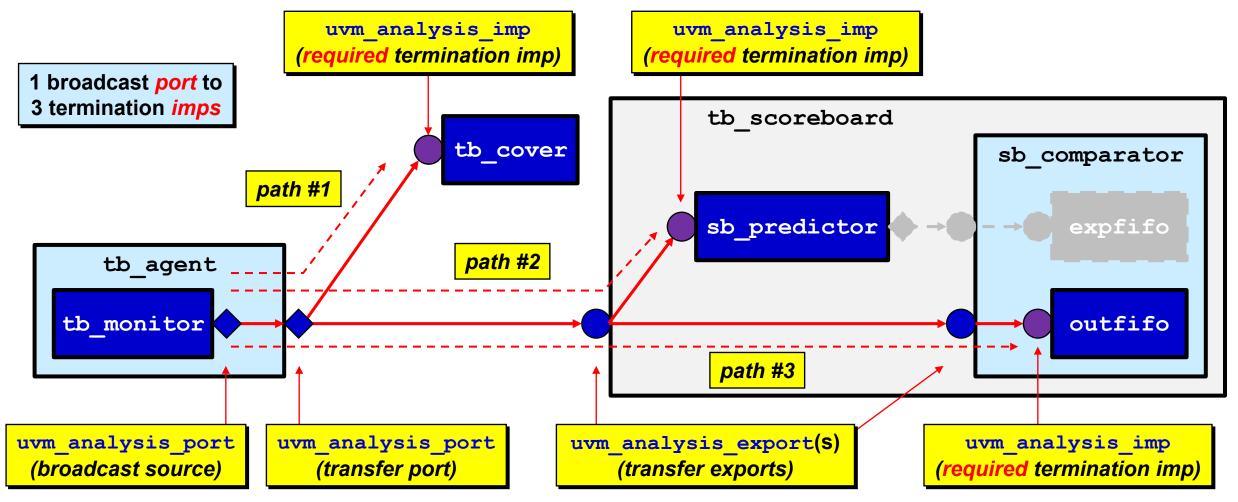

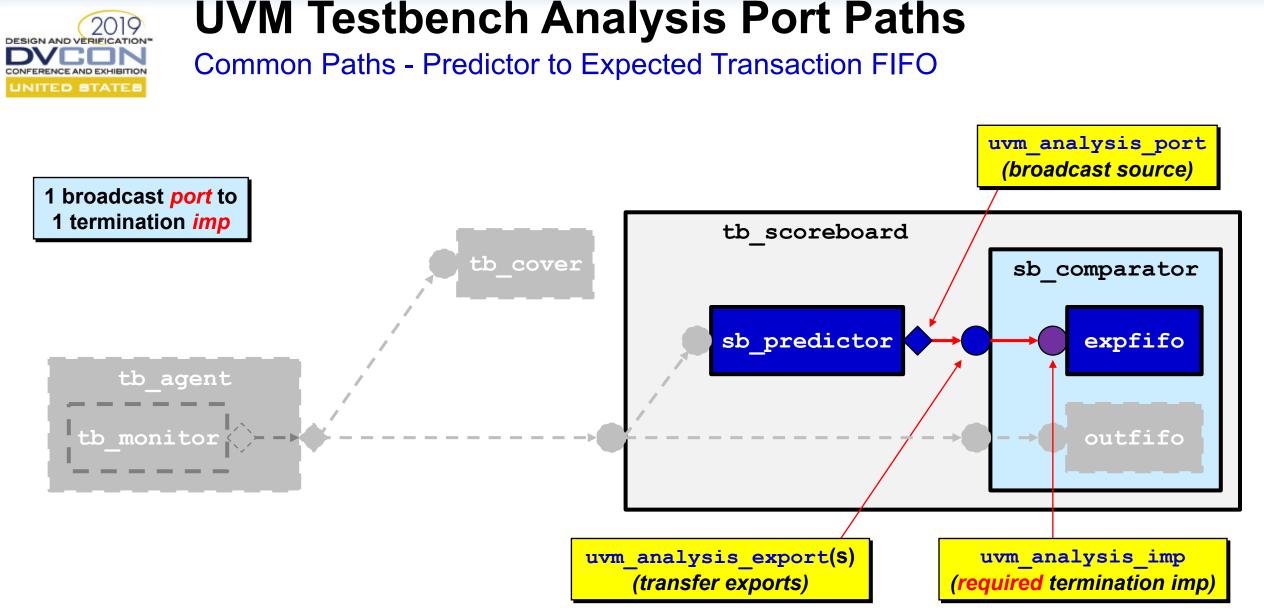

### **UVM Testbench Analysis Port Paths**

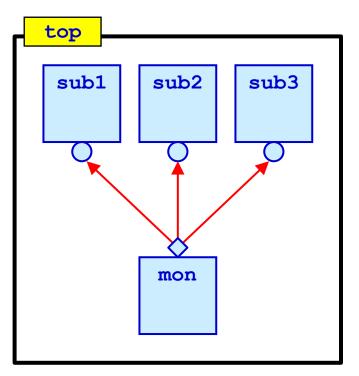

**Common Paths - Monitor to Multiple Subscribers**

100 of 126

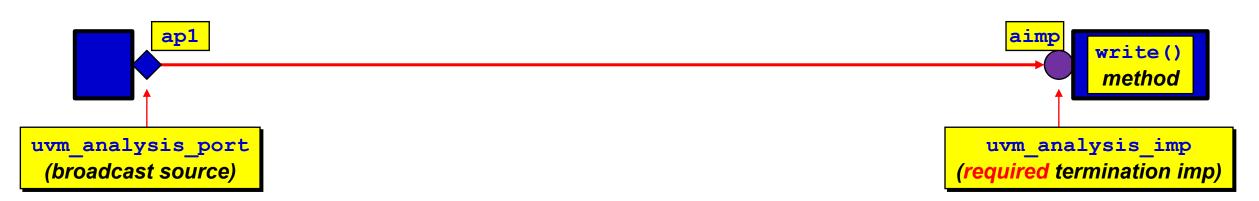

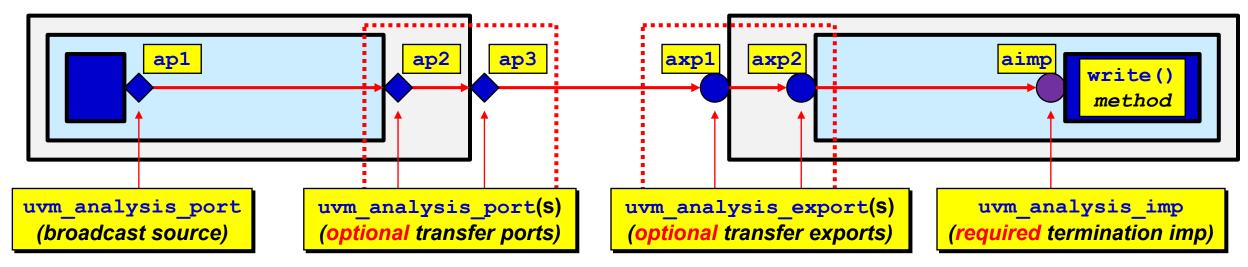

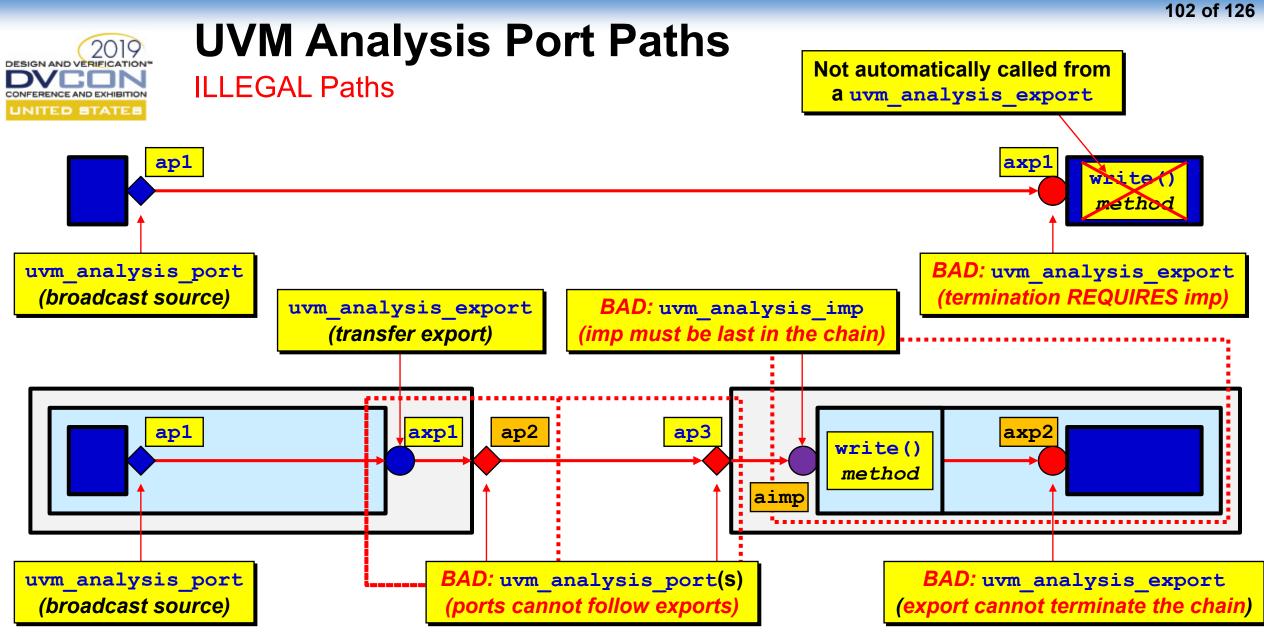

# **UVM Analysis Port Paths**

#### **LEGAL** Paths

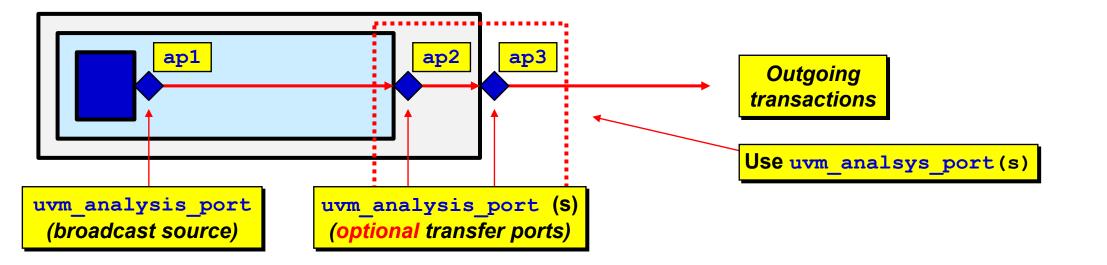

### **UVM Analysis Ports**

Recommended Usage

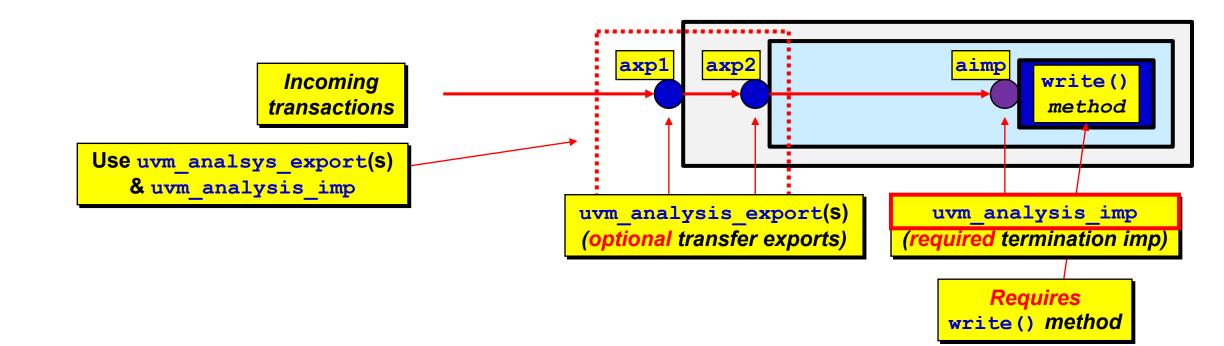

### **UVM Analysis Exports & Imps**

Recommended Usage

### **Common Analysis Port Connections**

**Recommended Connections**

2019 DESIGN AND VERIFICATION CONFERENCE AND EXHIBITION UNITED STATES

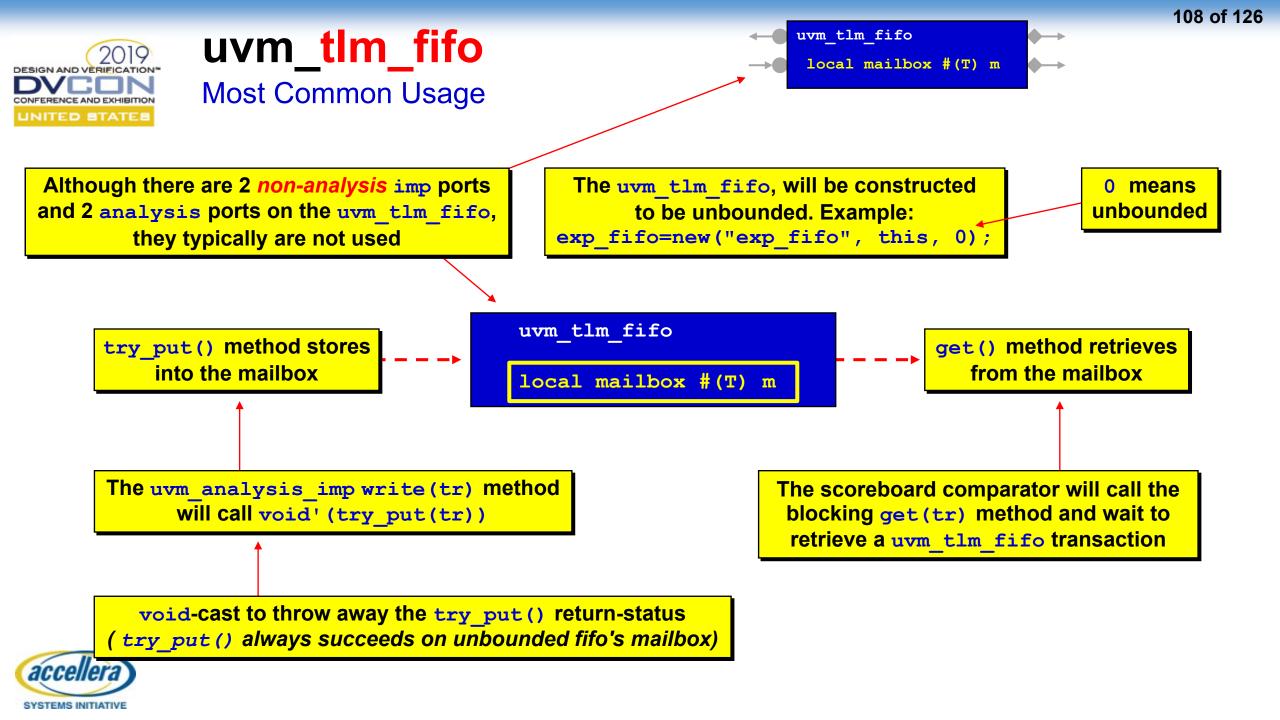

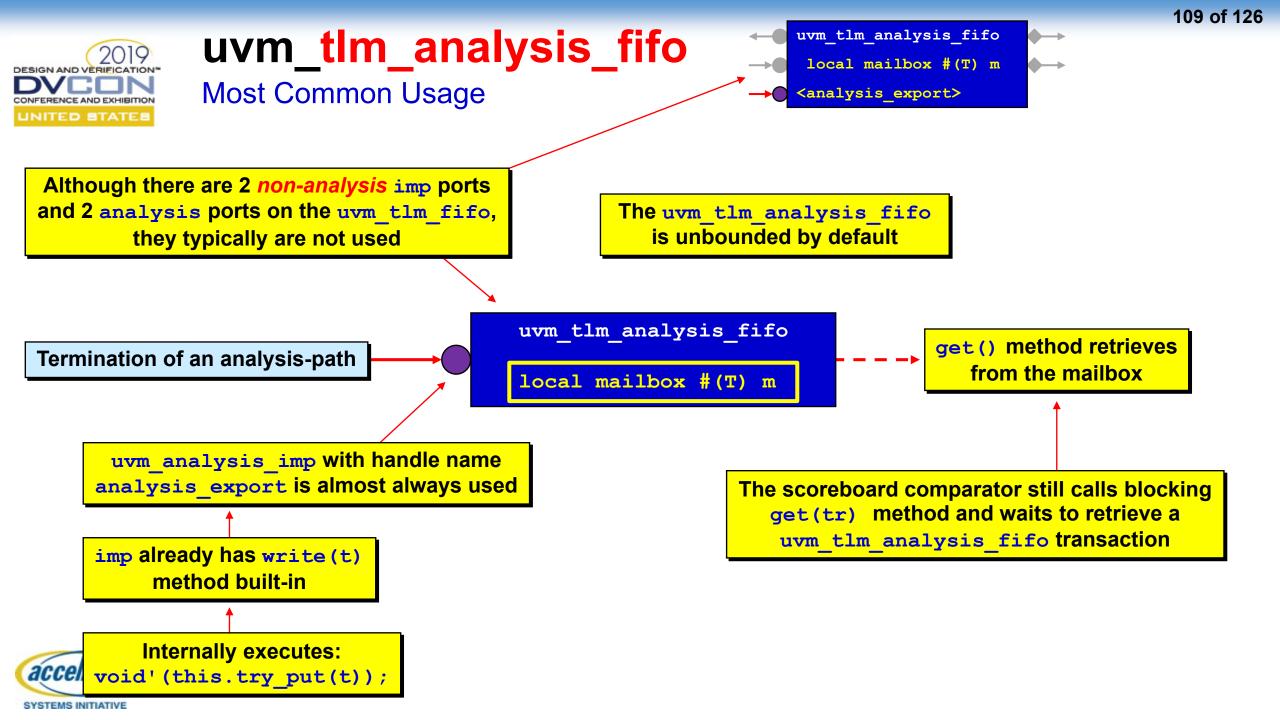

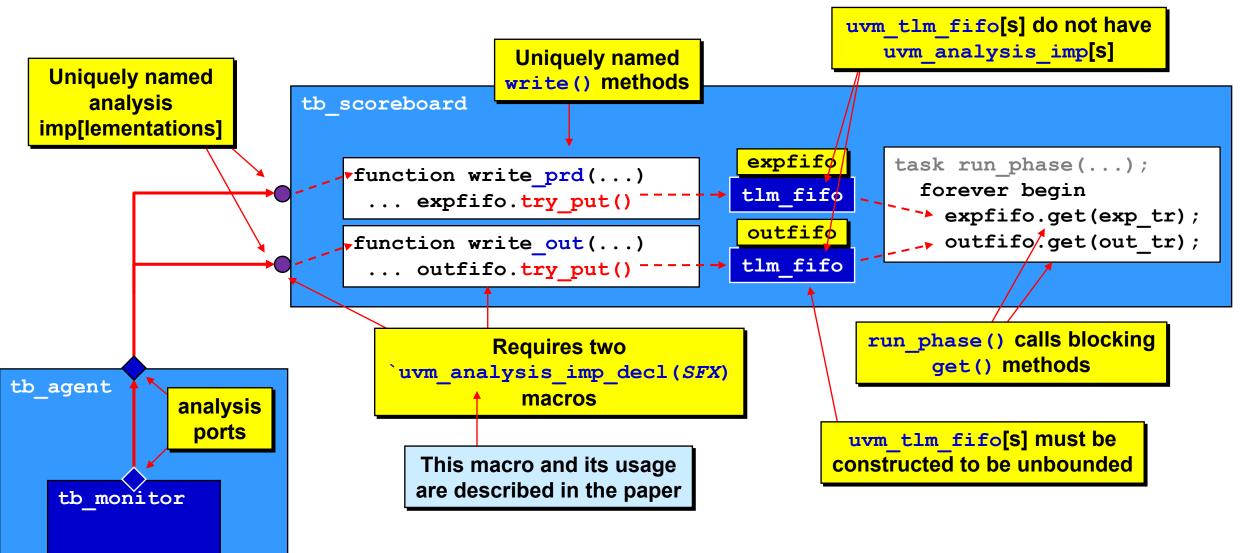

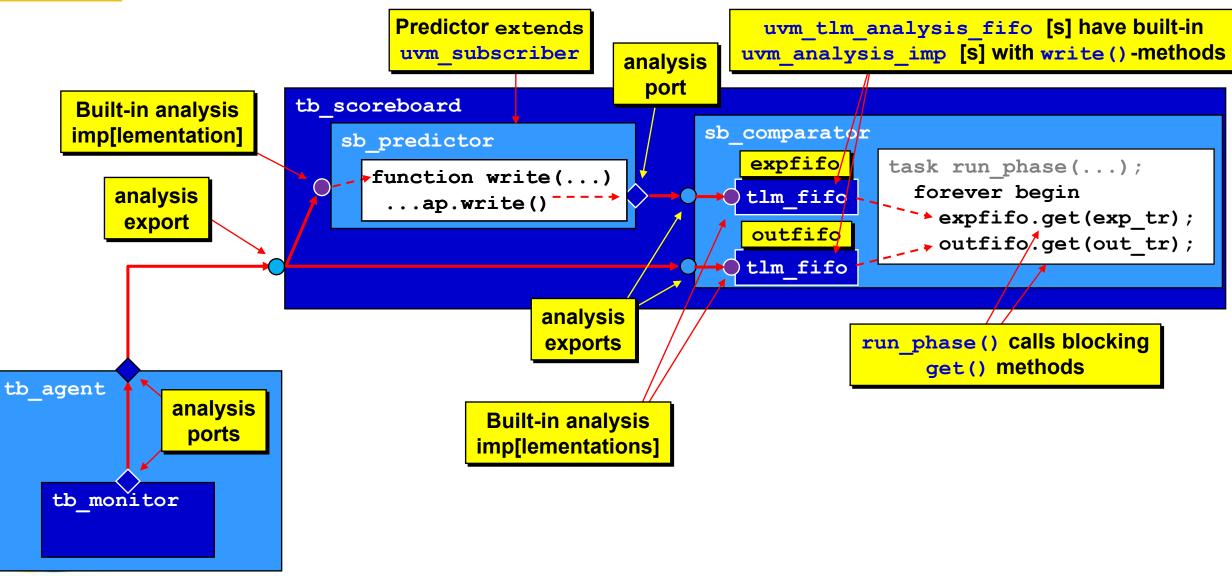

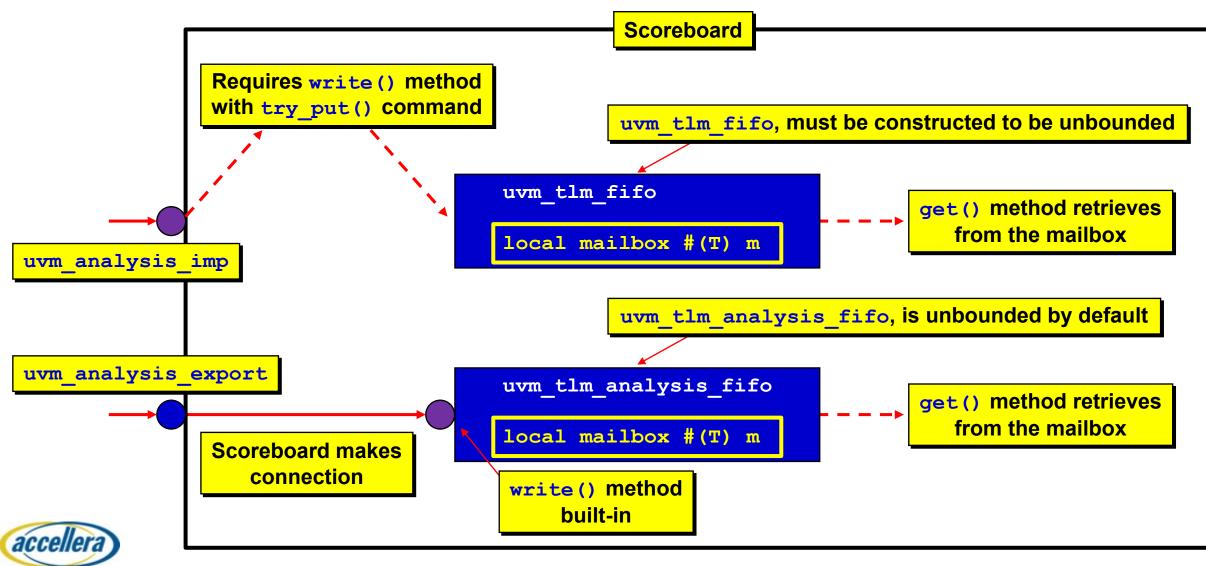

# **TLM FIFOs - Definitions & Usage**

106 of 126

### **TLM FIFOs & Scoreboards**

SystemVerilog Queues & Mailboxes

- Scoreboards typically store *expected* and *actual* transactions

### **Typical Scoreboard**

#### Using uvm\_tlm\_fifos

SYSTEMS INITIATIVE

### **Typical Scoreboard**

Using uvm\_tlm\_analysis\_fifos

SYSTEMS INITIATIVE

SYSTEMS INITIATIVE

SYSTEMS INITIATIVE

### **Comparing TLM FIFOs**

uvm\_tlm\_fifo -vs- uvm\_tlm\_analysis\_fifo

### **Ports & Exports** Is The Naming Backwards?

- How to think about *Ports* and *Exports*

- Automobile features:

- Steering wheel

- Accelerator Pedal

- Brake Pedal

- Hands-free Bluetooth-phone connection

115 of 126

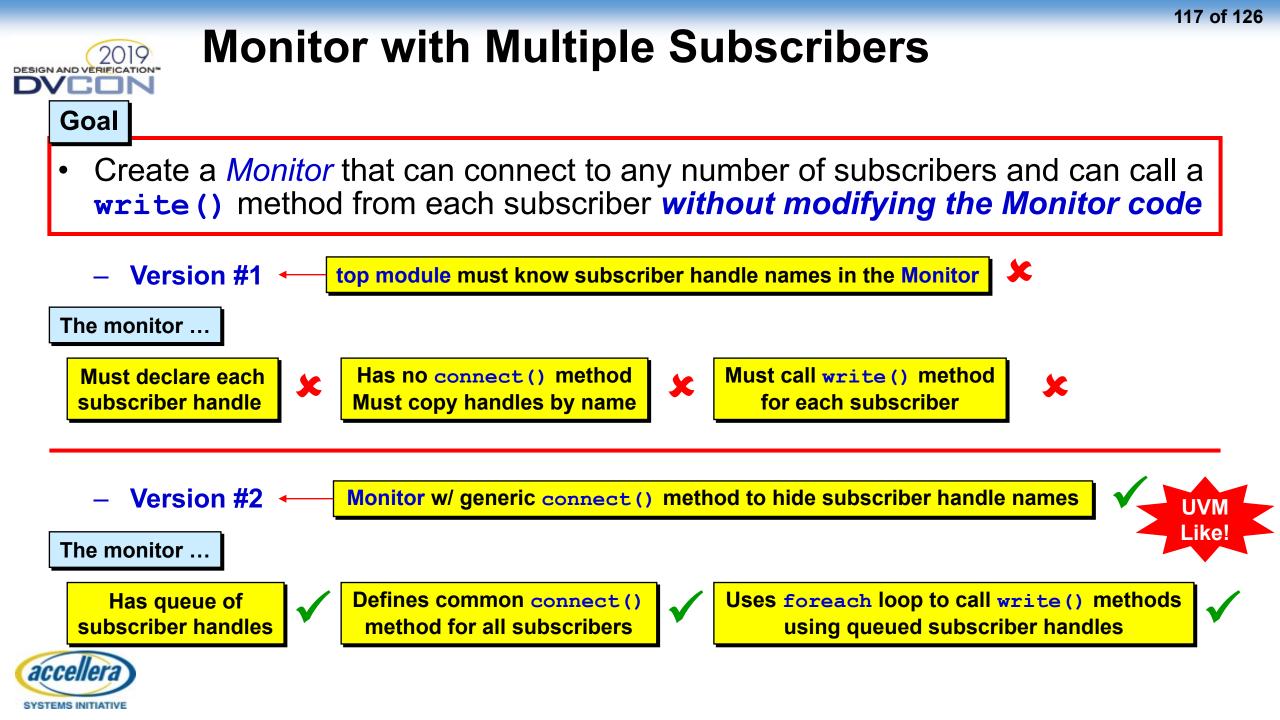

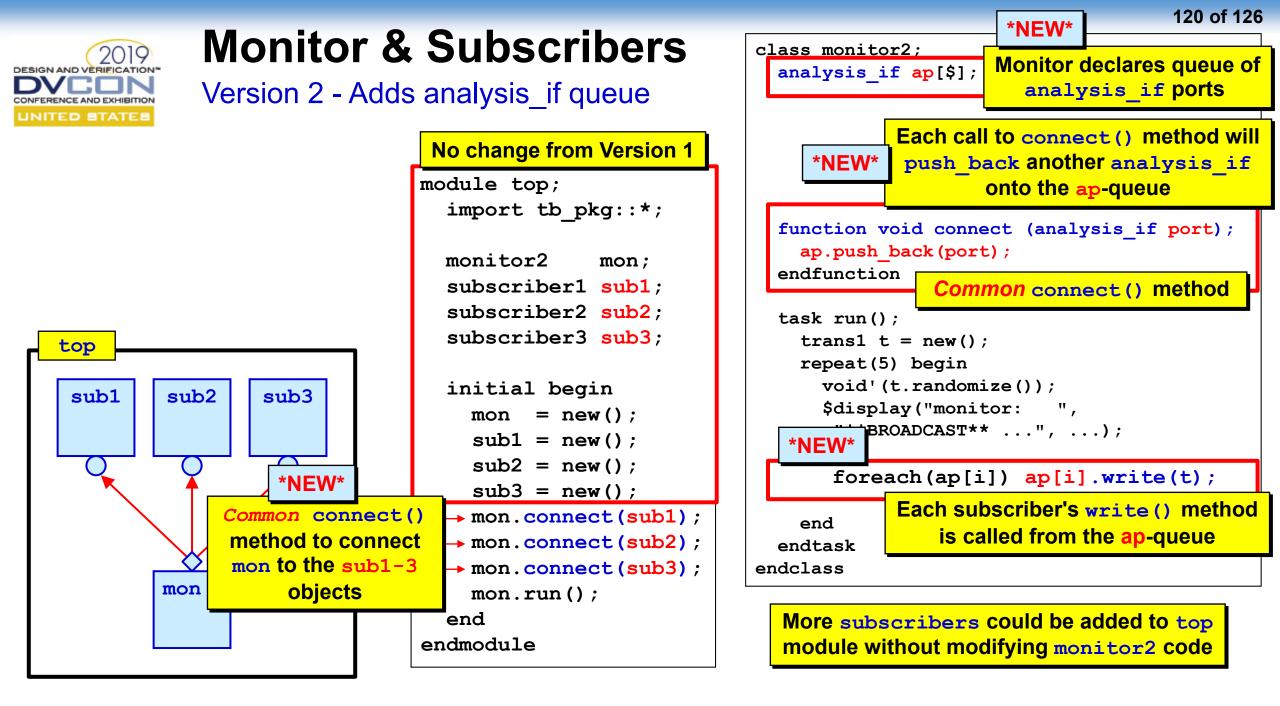

# **Analysis Path Basics**

In the software world, this is known as the *"Observer Pattern"*

How do analysis port-paths work?

- We have learned about analysis ports & TLM FIFOs +

- You do not have to know how UVM works

- The best engineers want to have <u>some</u> understanding on how UVM works •

- The remaining slides show how UVM makes subscribers work ٠

This is a **basic** version of what **UVM does internally**

These slides show how UVM uses *queues* and foreach loops to call each subscriber's write () method

You now know how to use:

uvm analysis port

uvm analysis imp

uvm tlm fifo

uvm analysis export

uvm tlm analysis fifo

You now have enough knowledge

to use analysis components

This is a high-level tutorial on how monitors and subscribers work

This is not exactly how UVM works, but it is close

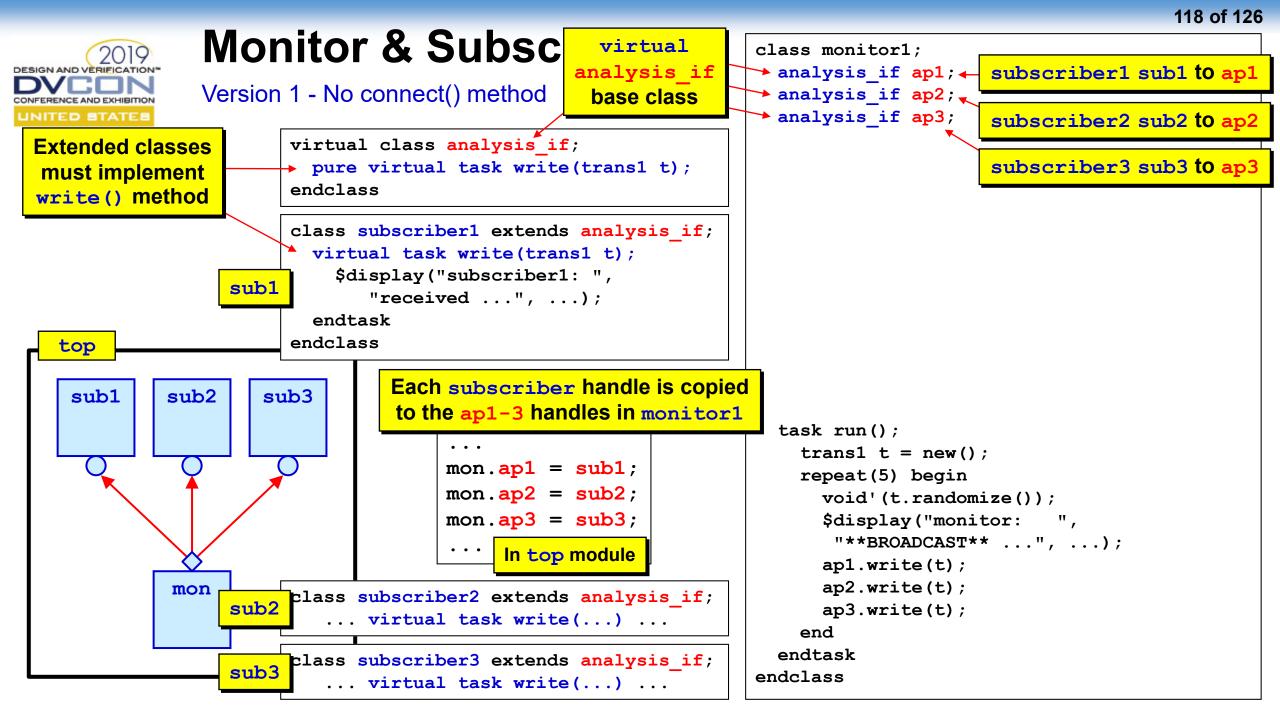

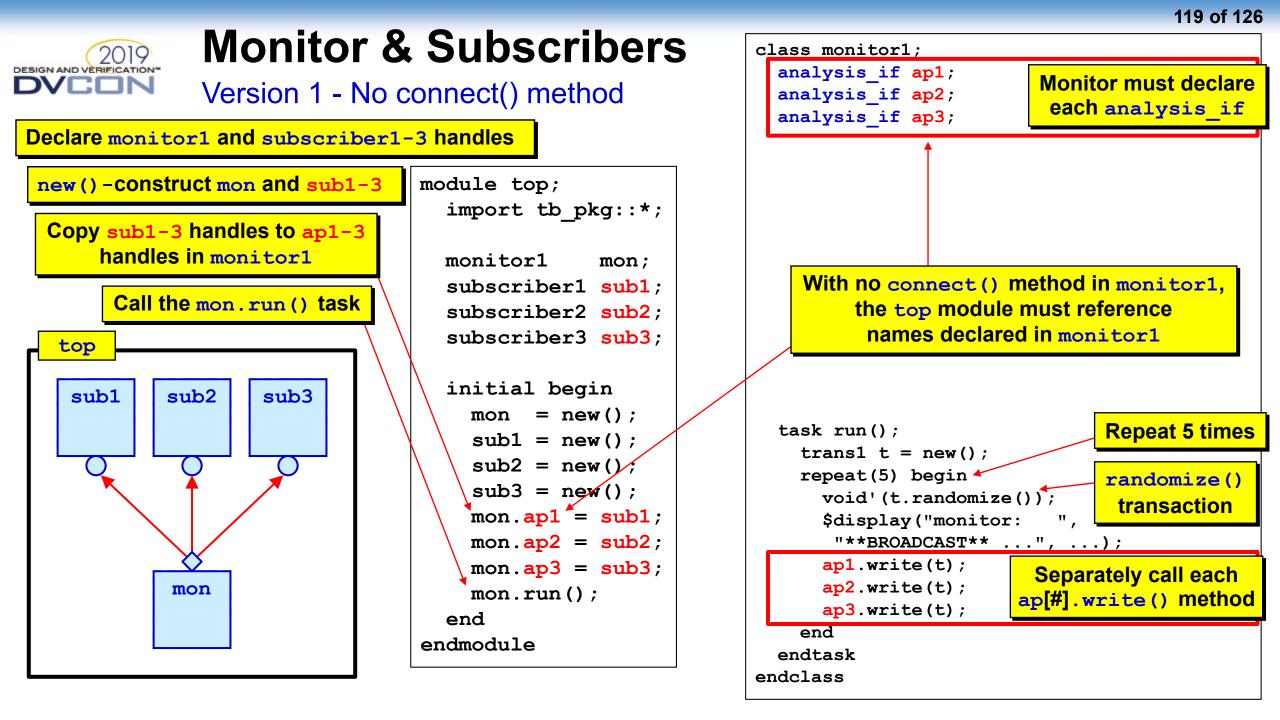

### **Monitor & Subscribers**

. . .

#### Simulation Output

| Randomized trans1 values<br>monitor: **BROADCAST**      | addr=f9<br>addr=f9 | data=50<br>data=50 |

|---------------------------------------------------------|--------------------|--------------------|

| subscriber1: received                                   | addr=f9            | data=50            |

| subscriber2: received                                   | addr=f9            | data=50            |

| subscriber3: received                                   | addr=f9            | data=50            |

|                                                         |                    |                    |

|                                                         |                    |                    |

| Randomized trans1 values                                | addr=e9            | data=27            |

| Randomized trans1 values<br>monitor: **BROADCAST**      | addr=e9<br>addr=e9 | data=27<br>data=27 |

|                                                         |                    |                    |

| monitor: **BROADCAST**                                  | addr=e9            | data=27            |

| <pre>monitor: **BROADCAST** subscriber1: received</pre> | addr=e9<br>addr=e9 | data=27<br>data=27 |

Each subscriber has seen the exact same addr and data values that were broadcast to all subscribers

### **Monitor & Subscribers**

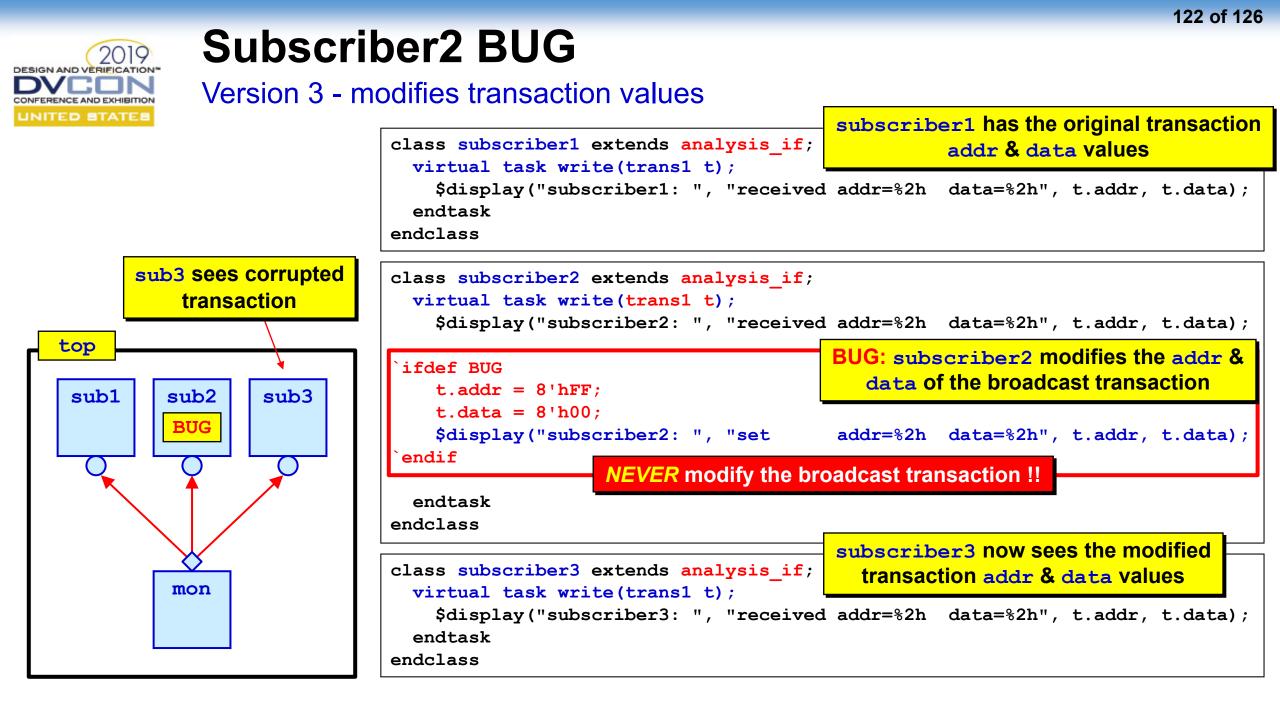

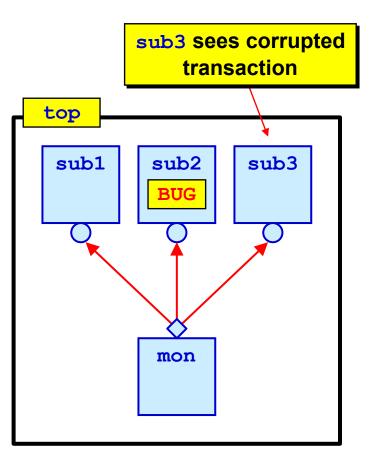

**BUG: Simulation Output**

| Randomized                 | trans1 valu | es addr=f9         | data=50            |

|----------------------------|-------------|--------------------|--------------------|

| monitor:                   | **BROADCASI | "** addr=f9        | data=50            |

| subscriber1                | : received  | addr=f9            | data=50            |

| subscriber2                | : received  | addr=f9            | data=50            |

| subscriber2                | : set       | addr=ff            | data=00            |

| subscriber3                | : received  | addr=ff            | data=00            |

| Randomized                 | trans1 valu | es addr=e9         | data=27            |

| monitor:                   | **BROADCASI | ** addr=e9         | data=27            |

| subscriber1                | : received  | addr=e9            | data=27            |

|                            |             |                    | data=27            |

| subscriber2                | : received  | addr=e9            | uala=z/            |

| subscriber2<br>subscriber2 |             | addr=e9<br>addr=ff | data=27<br>data=00 |

Depending on how the subscribers are pushed onto the ap - queue, sub1 might also see the bug

## **Transaction Copy() Method**

- All subscribers receive a handle to the same broadcast transaction

- A subscriber should **NEVER** modify contents of the received transaction

- Any subscriber that modifies transaction contents *MUST take a copy before making modifications*

This is described in the paper

Great feature for terminating an

analysis path in a scoreboard

## **Summary & Conclusions**

- Analysis ports are ports that broadcast transactions to 0 or more destinations

- Each subscriber chain terminates with a <u>uvm\_analysis\_imp</u> and corresponding <u>write()</u> method

- Subscribers should **NEVER** modify the broadcast transaction

- Subscribers need to use the transaction in 0-time -OR-

- Subscribers need to take a local copy

- If a component has multiple imp-inputs, use the macro:

`uvm\_analysis\_imp\_decl(SFX)

- The uvm\_tlm\_analysis\_fifo\_has a built-in uvm\_analysis\_imp port

- Prove that the scoreboard analysis paths are working

**DO NOT ASSUME** that the analysis paths are working correctly !!

To watch these presentations, go to: videos.accellera.org/videos.html

Access the SystemVerilog and UVM Forums

## **Resources Summary**

- Get a free Accellera login

www.accellera.org

Many great resources on this web site

- Register for free access to the DVCon 2017 and DVCon 2018 videos

- forums.accellera.org/ •

# IEEE 1800.2 UVM - Changes Useful UVM Tricks & Techniques

### **Clifford E. Cummings**

World Class Verilog, SystemVerilog & UVM Training

Life is too short for bad or boring training!

1639 E 1320 S, Provo, UT 84606 Voice: 801-960-1996 Email: cliffc@sunburst-design.com Web: www.sunburst-design.com

Reference Material

128

Thomas Alsop - Intel Corp.

- 14 Introduction to IEEE and Backward Compatibility

- 15 BCL compliance to the IEEE 1800.2 spec

- 16 Implementations artifacts and additive but non-IEEE APIs

- 17 Deprecation policy and roadmap

- 18 Removal of pre-1.2 deprecated code Motion pending

- 19 APIs that changed from 1.2 to IEEE Motion pending

Reference Material

Srivatsa Vasudevan - Synopsys, Inc.

- 28 UVM Policy Classes copy, compare, print, pack, record all have policy classes

- 29 **uvm\_policy** users can apply different printer or compare policy + many accessor methods

- 30 **uvm\_packer** new pack / unpack capabilities

- 31-32 uvm\_copier signature of copy() has changed to allow uvm\_copier

- 33-34 uvm\_comparer provides new accessor methods

- 35-36 uvm\_printer new printer knobs & accessor methods

- 37-39 uvm\_line\_printer / uvm\_table\_printer / uvm\_tree\_printer

- 40 **uvm\_recorder** new methods

- 41 Summary of core utility policies

Srivatsa Vasudevan - Synopsys, Inc.

130

- 43-45 UVM factory now supports abstract objects (virtual classes)

- 47 uvm\_component can turn off apply\_config\_settings()

- 49 uvm\_object small modifications & new methods

- 50 minor uvm\_transaction modifications

- 51 Removed from IEEE 1800.2 Deemed as not standard worthy uvm\_comparator uvm algorithmic comparator

uvm in order comparator

- 53-54 uvm\_report\_object minor modifications

- 55 **uvm\_report\_server UVM\_FILE** type change

- 56 **uvm\_report\_catcher** minor modifictions

- 58 Callbacks now extend from uvm\_callback functions documented

Reference Material

131

Mark Glasser - NVIDIA Corporation

- 63 Summary of TLM Mantis Items

- 68 Register models documentation enhanced / system level / dynamic

- 69 Reg model unlock models can now be unlocked & re-locked

- 70 Register changes virtual and non-virtual classes

Reference Material

133

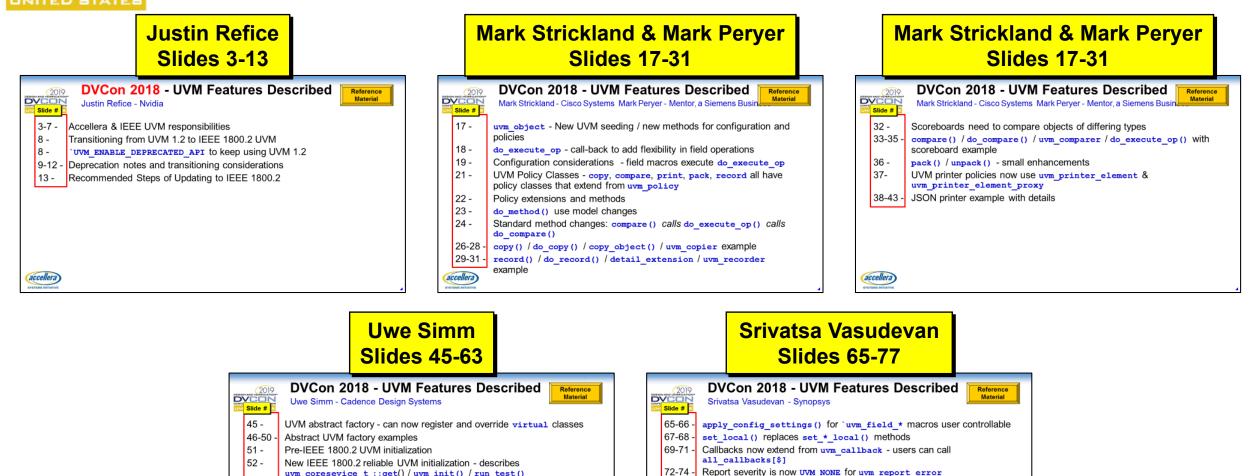

3-7 - Accellera & IEEE UVM responsibilities

Justin Refice - Nvidia

- 8 Transitioning from UVM 1.2 to IEEE 1800.2 UVM

- 8 **`UVM\_ENABLE\_DEPRECATED\_API** to keep using UVM 1.2

- 9-12 Deprecation notes and transitioning considerations

- 13 Recommended Steps of Updating to IEEE 1800.2

17 -

SYSTEMS INITIATIVE

# **DVCon 2018 - UVM Features Described**

134

Mark Strickland - Cisco Systems Mark Peryer - Mentor, a Siemens Busin

- uvm\_object New UVM seeding / new methods for configuration and policies

- 18 **do\_execute\_op** call-back to add flexibility in field operations

- 19 Configuration considerations field macros execute do\_execute\_op

- 21 UVM Policy Classes copy, compare, print, pack, record all have policy classes that extend from uvm\_policy

- 22 Policy extensions and methods

- 23 do\_method() use model changes

- 24 Standard method changes: compare() calls do\_execute\_op() calls do\_compare()

- 26-28 copy() / do\_copy() / copy\_object() / uvm\_copier example

- 29-31 record() / do\_record() / detail\_extension / uvm\_recorder example

|                                               | 135                                                                                                                                                    |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2019<br>N AND VERIFICATION<br>VCON<br>Slide # | DVCon 2018 - UVM Features Described<br>Mark Strickland - Cisco Systems Mark Peryer - Mentor, a Siemens Busin                                           |

| 32 -<br>33-35 -                               | Scoreboards need to compare objects of differing types<br><pre>compare() / do_compare() / uvm_comparer / do_execute_op() with scoreboard example</pre> |

| 36 -                                          | pack() / unpack() - small enhancements                                                                                                                 |

| 37-                                           | UVM printer policies now use <pre>uvm_printer_element &amp; uvm_printer_element_proxy</pre>                                                            |

| 38-43 -                                       | JSON printer example with details                                                                                                                      |

Reference Material

136

- 45 UVM abstract factory can now register and override **virtual** classes

- 46-50 Abstract UVM factory examples

- 51 Pre-IEEE 1800.2 UVM initialization

- 52 New IEEE 1800.2 reliable UVM initialization describes uvm\_coresevice\_t ::get() / uvm\_init() / run\_test()

- 53-56 UVM deferred initialization examples

- 57-58 uvm\_run\_test\_callback / pre\_run\_test() / post\_run\_test() /

pre\_abort()

- 59-62 uvm\_reg\_block.lock\_model() / unlock\_model()

**Uwe Simm - Cadence Design Systems**

63 - Miscellaneous <u>uvm\_reg</u> notes & changes including <u>uvm\_door\_e</u>

Reference Material

137

- 65-66 apply\_config\_settings() for `uvm\_field\_\* macros user controllable

- 67-68 set\_local() replaces set\_\*\_local() methods

- 69-71 Callbacks now extend from uvm\_callback users can call

all\_callbacks[\$]

- 72-74 Report severity is now UVM\_NONE for uvm\_report\_error

- 76 `uvm\_do replaces all earlier `uvm\_do\_\* macros

- `uvm\_do\_\* deprecation notes

Srivatsa Vasudevan - Synopsys

77 -