## How to Stay Out of the News with ISO26262-Compliant Verification

Charles Battikha (chuck\_battikha@mentor.com) Doug Smith (doug\_smith@mentor.com)

- Taking New Products into the Automotive Market... Welcome to Functional Safety

- From Analysis to Fault Campaigns

- Break

- How Formal Reduces Fault Analysis for ISO 26262

- Requirement Tracing in the ISO26262 World

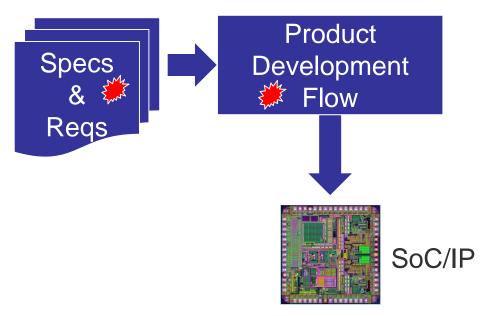

# **Entering the Automotive Market...**

Reviewing the challenges and requirements in the Automotive Market & ISO26262 Standard

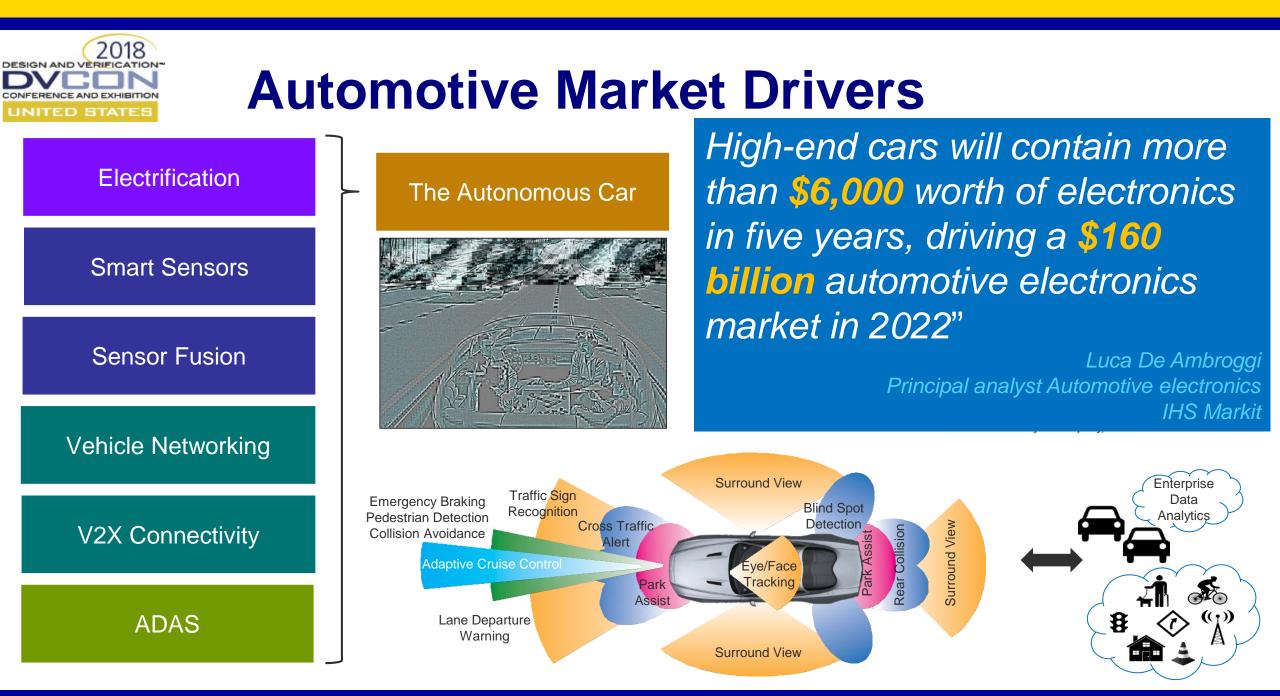

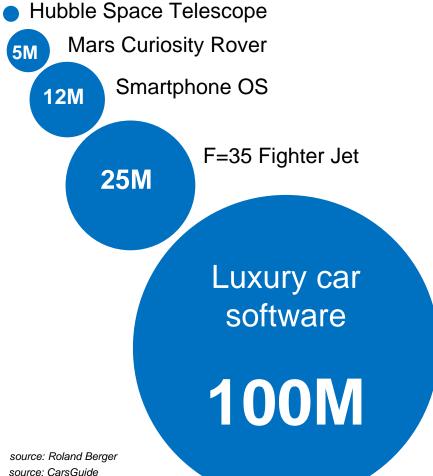

### **Complexity of Automotive Systems**

### LINES OF CODE

S-MB10 6 radar beams

8 cameras 12 parking sensors 144 electronic control units 500 LEDs 734 wire harnesses 2,400 wires 5,000 meters of cables

|     |                     | IBITION | F                         | un | ctional Safety = Tak                                  | ble                                              | S              | ta            | ke            | es     |                   |                                                 |

|-----|---------------------|---------|---------------------------|----|-------------------------------------------------------|--------------------------------------------------|----------------|---------------|---------------|--------|-------------------|-------------------------------------------------|

| Se  | everity<br>Injuries | + Pro   | obability<br>posure<br>C2 | T  | Driver<br>Control = ASIL Set by OEM                   | Rate of t<br>year of in<br>MODEL<br>YEAR<br>2013 | raffic fat     | alities per   |               |        | , by mode<br>2013 | el year and<br>RATE<br>— <b>3-5.9</b><br>deaths |

|     | E1                  | QM      | QM                        | QM | Goal is the create a <i>highly</i>                    | 12<br>11                                         |                |               | _             |        |                   |                                                 |

|     | E2                  | QM      | QM                        | QM | assured design by removing                            | '10<br>'09                                       |                |               |               |        | •                 | — 6-8.9                                         |

| S1  | E3                  | QM      | QM                        | A  | unreasonable risk                                     | '08<br>'07                                       |                |               |               |        |                   |                                                 |

|     | E4                  | QM      | A                         | В  |                                                       | '06<br>'05                                       |                |               |               |        |                   | — 9-11.9                                        |

|     | E1                  | QM      | QM                        | QM | -                                                     | '04<br>'03                                       |                |               |               |        |                   |                                                 |

| 0.0 | E2                  | QM      | QM                        | A  | -                                                     | '02                                              |                |               |               |        |                   |                                                 |

| S2  | E3                  | QM      | A                         | В  | -                                                     | '01<br>2000                                      |                |               |               |        |                   |                                                 |

|     | E4                  | A       | В                         | С  | -                                                     | '99<br>'98                                       |                |               |               |        |                   | - 12-14.9                                       |

|     | E1                  | QM      | QM                        | A  |                                                       | '97<br>'96                                       |                |               |               |        |                   |                                                 |

|     | E2                  | QM      | A                         | В  |                                                       | '95                                              |                |               |               |        |                   |                                                 |

| S3  | E3                  | A       | В                         | С  | ASIL D<br>S3=Life-threatening, fatal injuries         | '94<br>'93                                       |                |               |               |        |                   |                                                 |

|     | E4                  | В       | С                         | D  | <ul> <li>→ E4=High probability of exposure</li> </ul> | '92<br>'91                                       |                |               |               |        |                   |                                                 |

|     |                     |         |                           |    | C3=Difficult for driver to control                    | '90<br>Source: WS                                | 5J analysis; I | Experian Info | ormation Solu | utions | The Wa            | II Street Journal                               |

Source: WSJ analysis; Experian Information Solutions

The Wall Street Journal

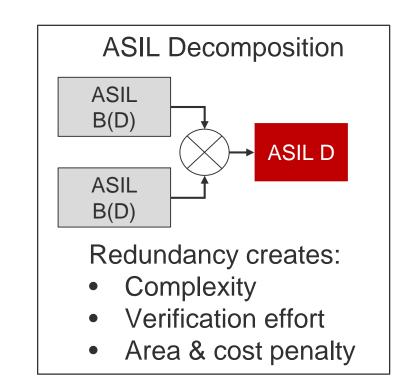

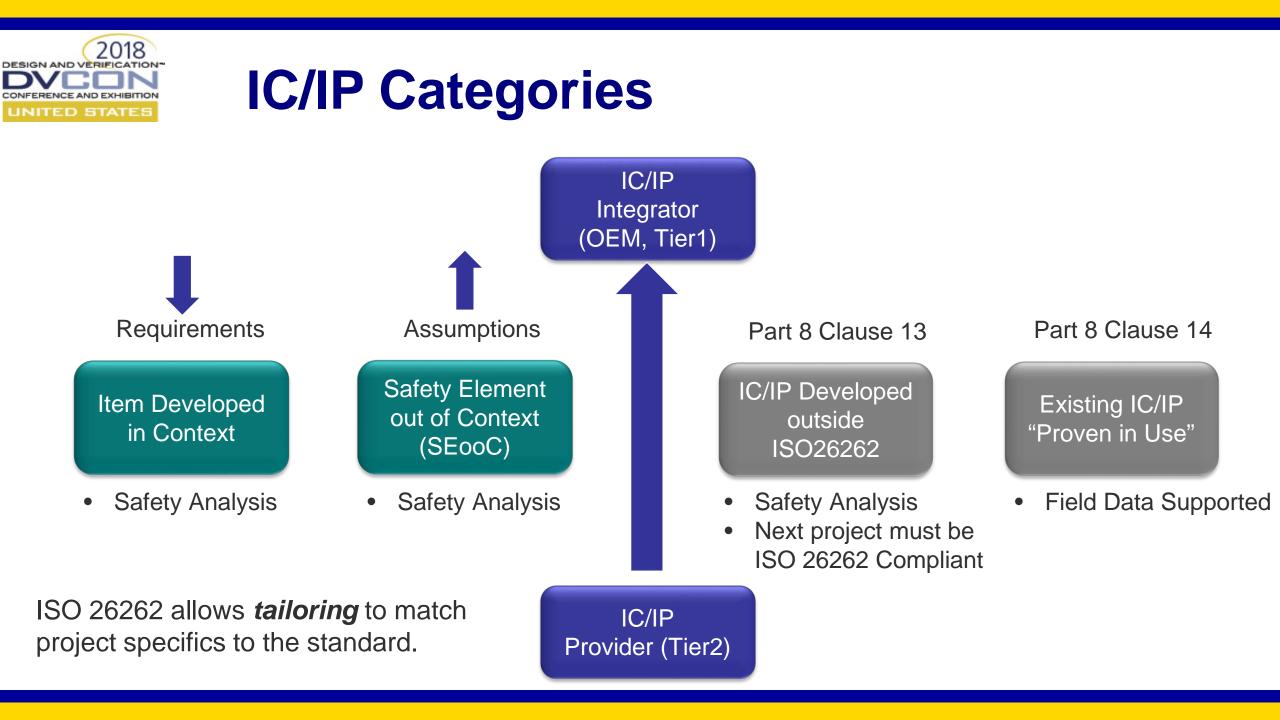

# **Functional Safety Tradeoffs**

Integrator Cost (Components) Integrator Development Effort

IP / IC Cost (Area) IP / IC Power (Area) IP / DC Development Effort Increased ASIL

2018

SIGN AND VERIFIC

JNITED STATE

IC/IP with ISO Compliance and higher ASIL ratings reduces effort, cost, and complexity for integrators. Increased Cost & Development Examples:

- Reviews, Audits, Assessments

- Additional Logic in Safety Mechanisms

- Additional Rigor & Deliverables

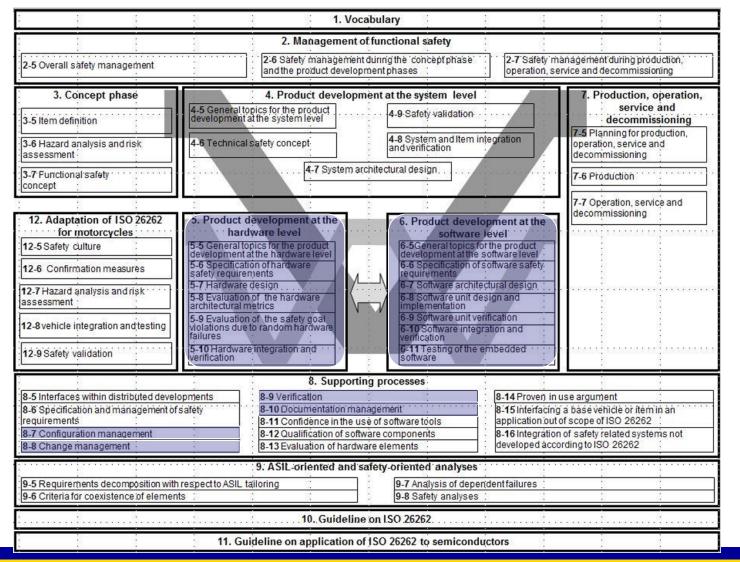

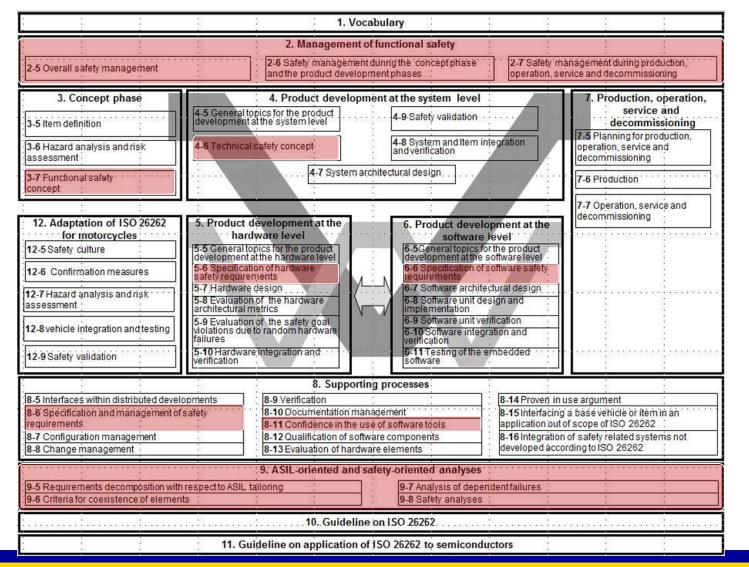

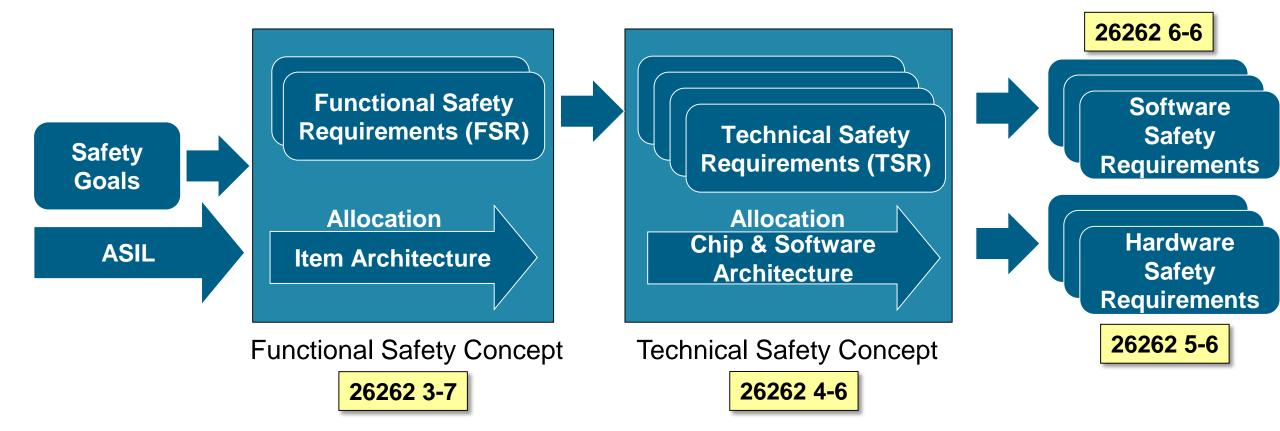

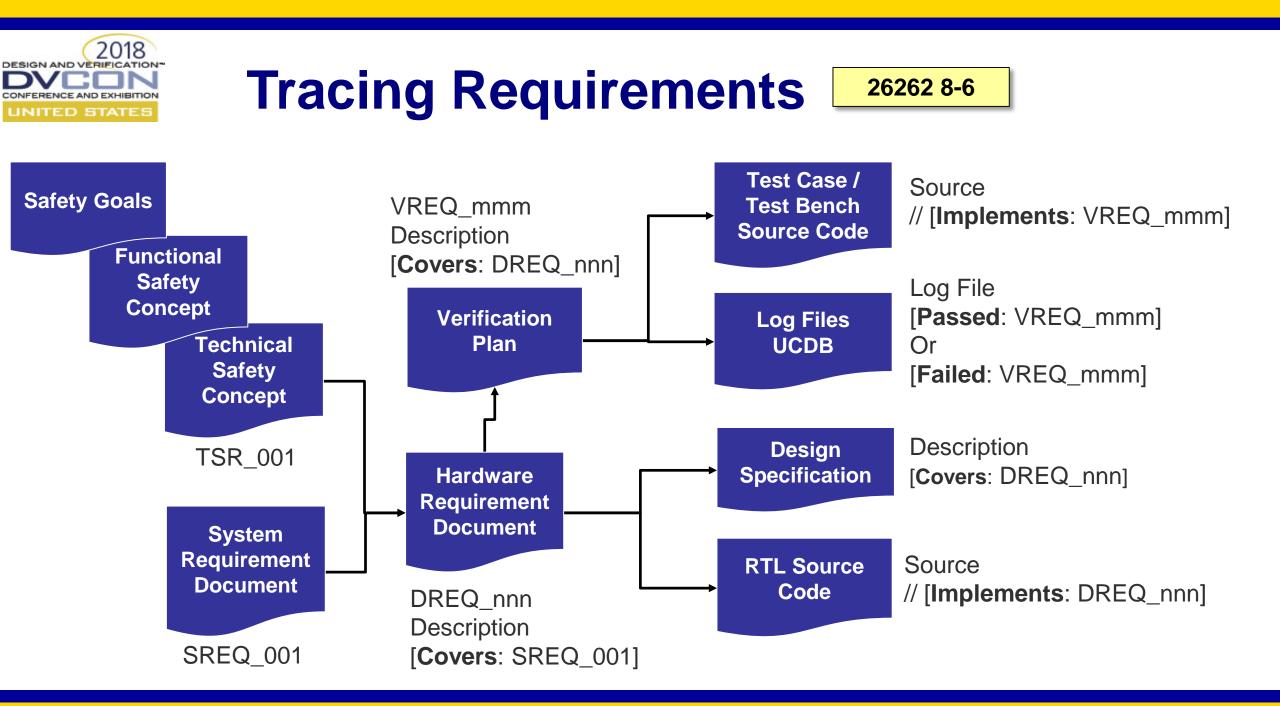

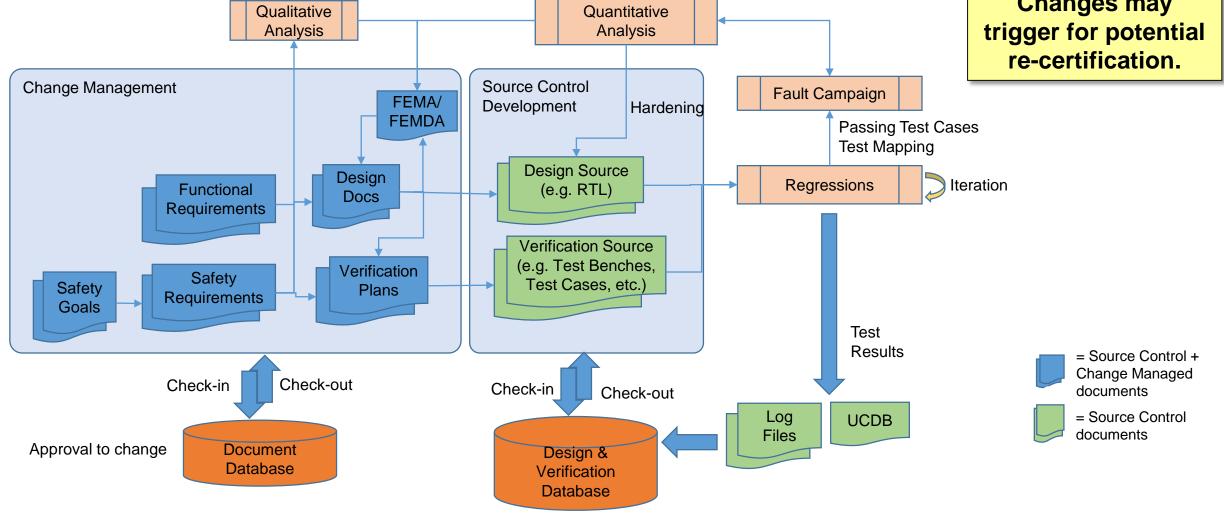

### ISO26262 – The known

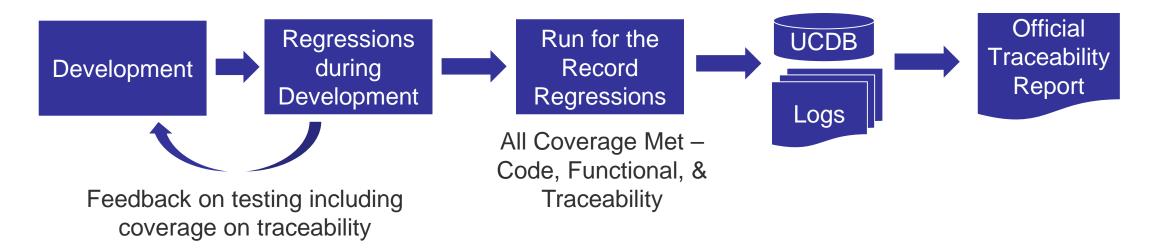

Established IC/IP Developers likely have strong development & verification processes:

- Development process well documented

- ... & shown to be followed

- Create and maintain artifacts

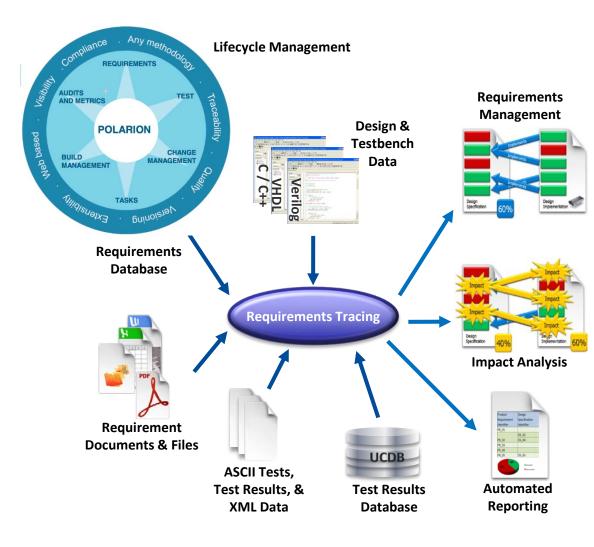

- Requirements tracing

- Source Control

- Change Management

- Documentation Control

### ISO26262 – The unknown

IC/IP developers new to the automotive market will find:

- Safety Culture

- Safety Requirements

- Safety Mechanisms

- Safety Analysis

- FMEA / FMEDA / DFA / FTA

- Fault Metrics

- Fault Insertion Campaign

- Safety Manual

- Tool Qualification

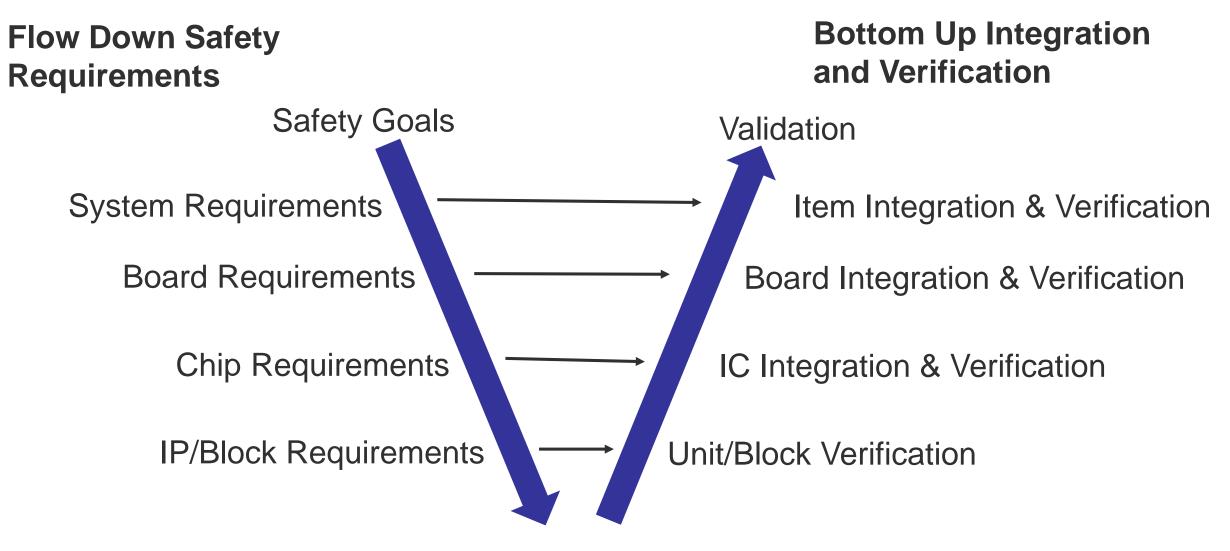

## **"V" Development & Verification**

# **Requires Two Testing Approaches**

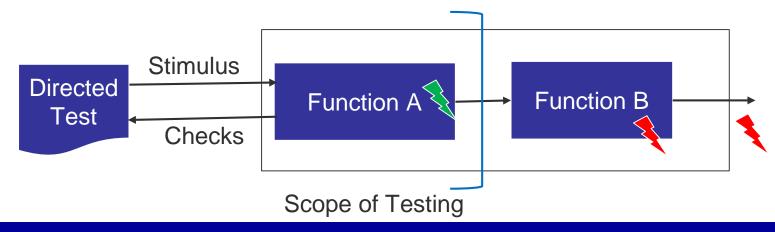

#### Systematic Failures Introduced in product development

- Incorrect Requirements

- Inaccurate/incomplete specs

- RTL Errors

- Timing Errors

#### Random Failures Introduced by the environment

- Vibration

- Moisture/Dirt

- Noise

- EMI

- Electro-migration

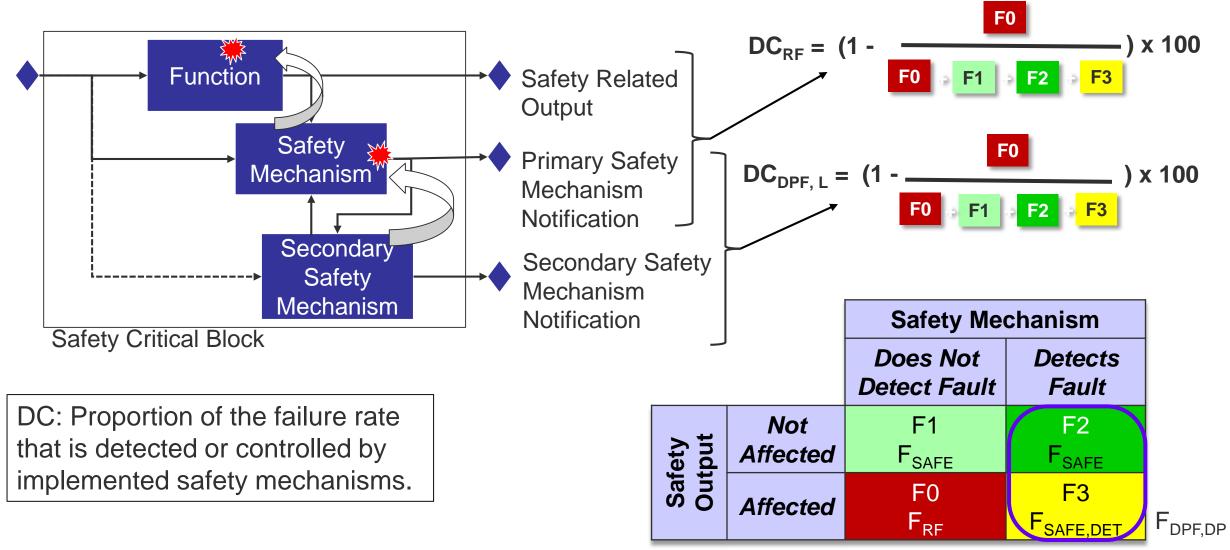

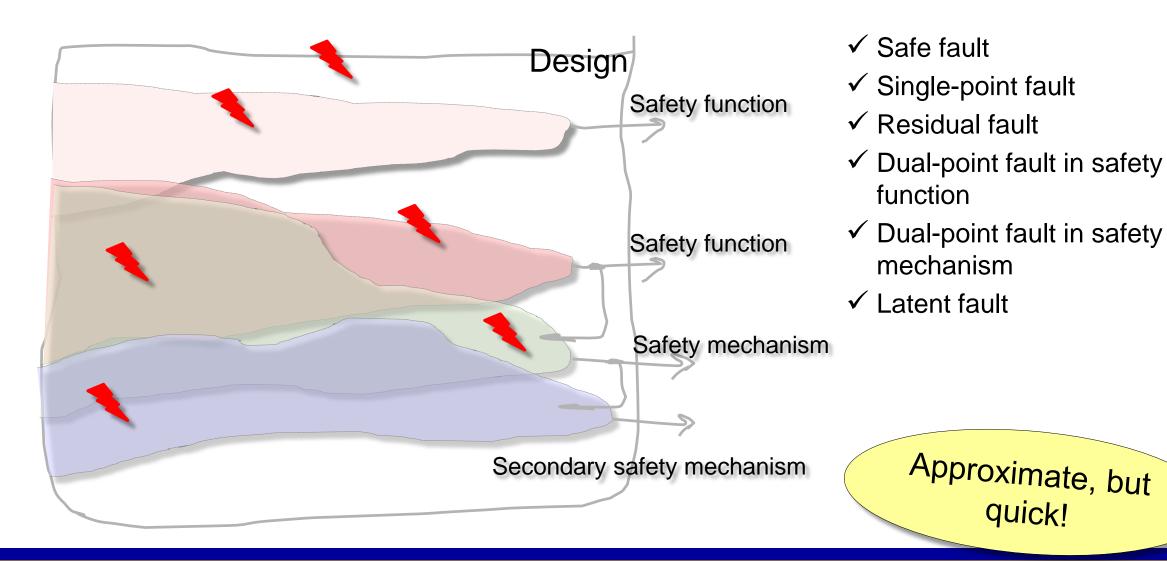

| $\lambda_{s}$   | Safe Faults; Does not effect the Safety Requirements                                                                                                                                                                                                                                                                                                                               |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\lambda_{SPF}$ | <b>Single Point Fault</b> ; Fault violating a Safety Requirements. Not covered by a Safety Mechanism. <u>Should be addressed</u> .                                                                                                                                                                                                                                                 |

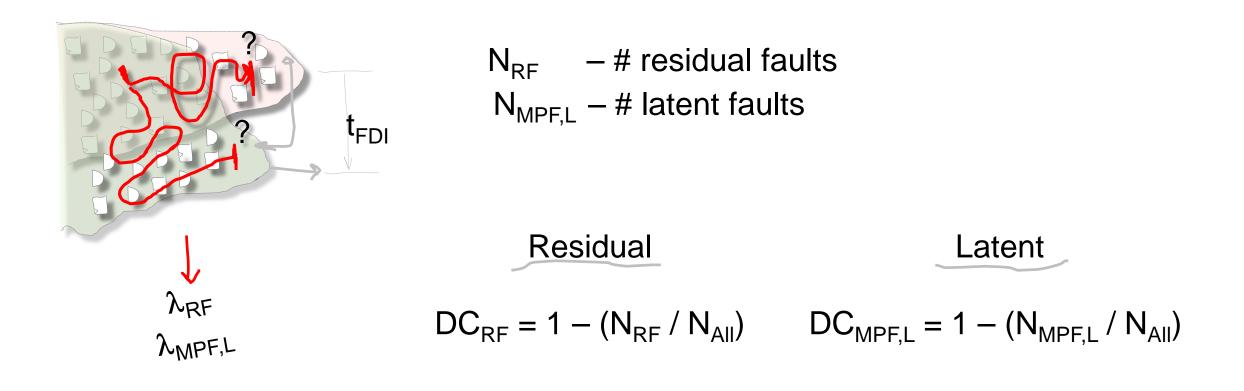

| λ <sub>rf</sub> | <ul> <li>Residual Faults; Faults not detected by an intended Safety Mechanism and lead to a violation of Safety Requirements.</li> <li>Single Point Faults and Residual Fault are not differentiated from a fault analysis perspective.</li> <li>Diagnostic Coverage measures effectiveness of safety mechanism in detecting Residual Faults – permanent and transient.</li> </ul> |

| λ <sub>DPF,DP</sub> | Dual-Point Faults – Detected/Perceived; Combination of independent faults                                                                                                                        |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | that may lead to a violation of Safety requirements.                                                                                                                                             |

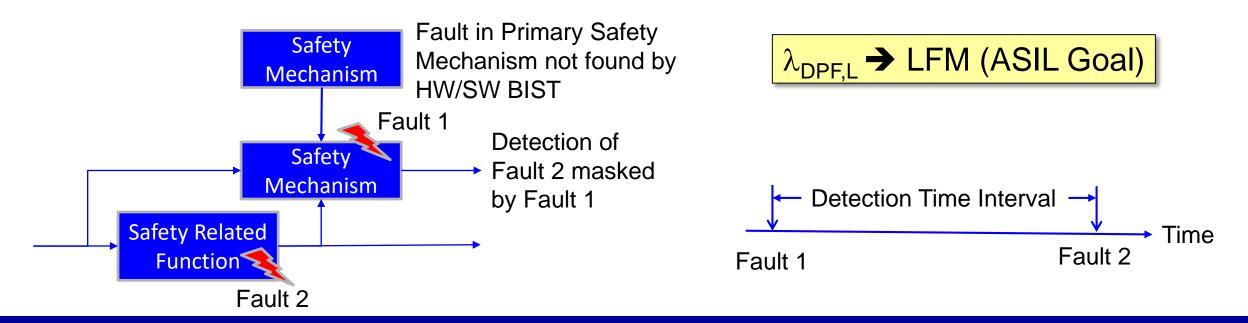

| λ <sub>dpf,l</sub>  | <b>Dual-Point Faults – Latent</b> ; Faults not detected by safety mechanisms that would lead to a dual-point failure. Considered to be a fault in primary safety mechanism that is undetectable. |

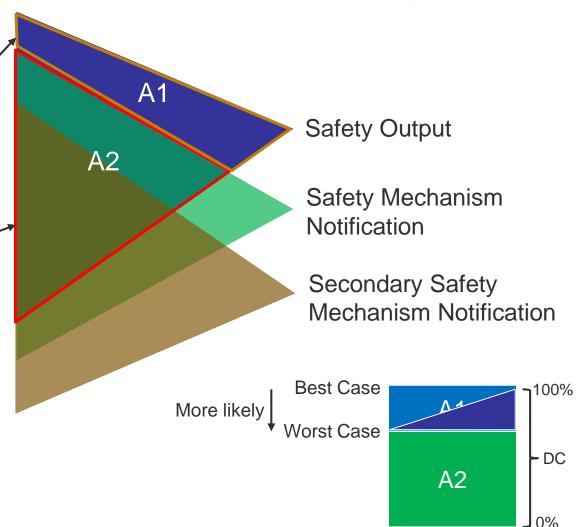

### **Diagnostic Coverage**

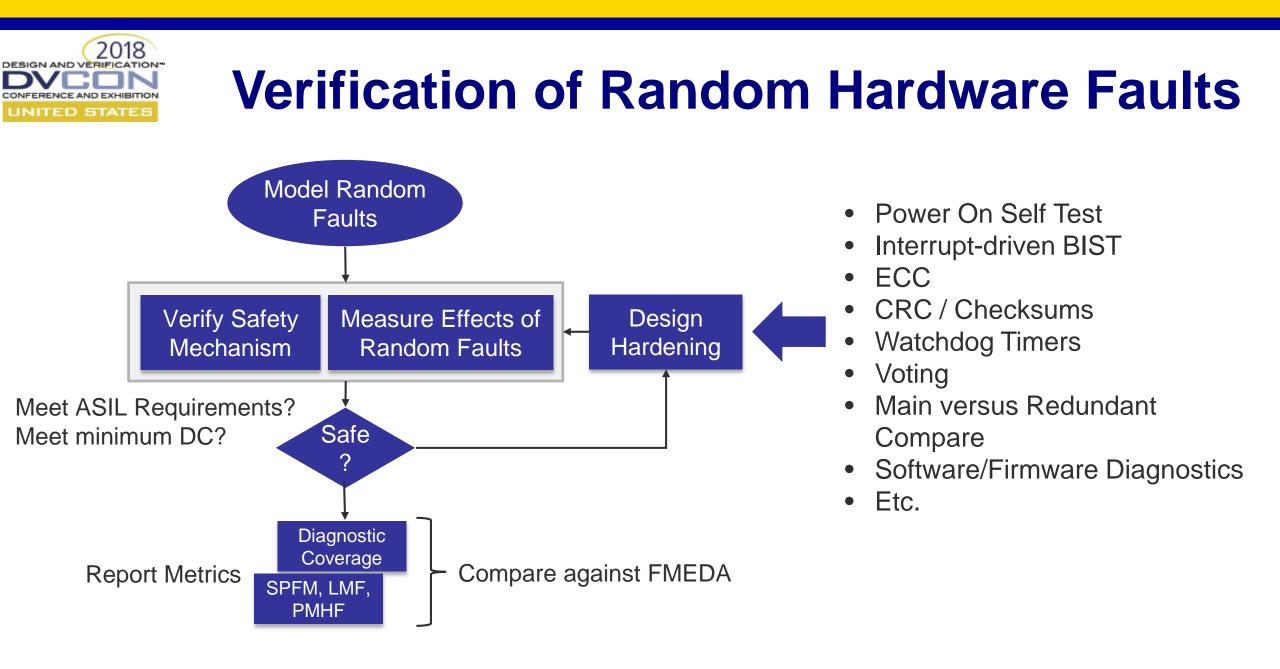

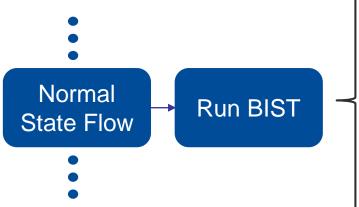

# **POST & Interrupt Driven BIST as SM**

FTTI determines:

2018

DESIGN AND VERIFICATION

UNITED STATES

- 1. If POST only sufficient

- 2. Frequency of BIST

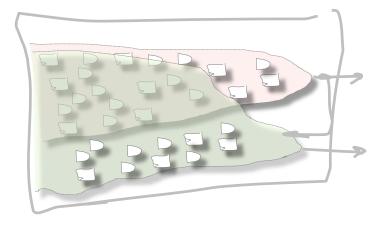

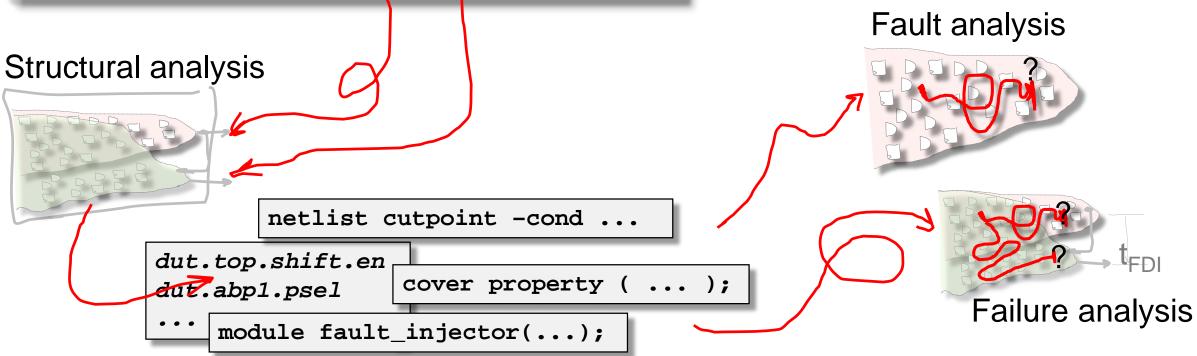

**Structural Analysis**

Represents no coverage of SM / against function.

Represents potential coverage of SM against function.

$A1 = combination(F_{RF} F_{SAFE})$  $A2 = combination(F_{DP,DET} F_{RF} F_{SAFE})$

Likely residual fault distribution:  $F_{RF,A1} >> F_{RF,A2}$ Creates a max ceiling for DC.

Goal: Reduce area of A1 before starting fault campaign.

#### 2018 ESIGN AND VERIFICATIO JNITED STATES

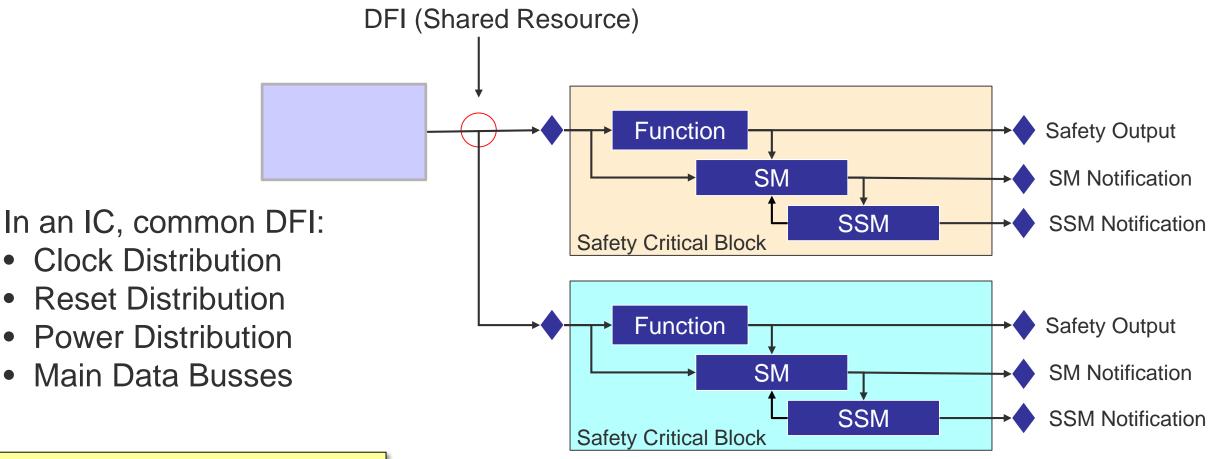

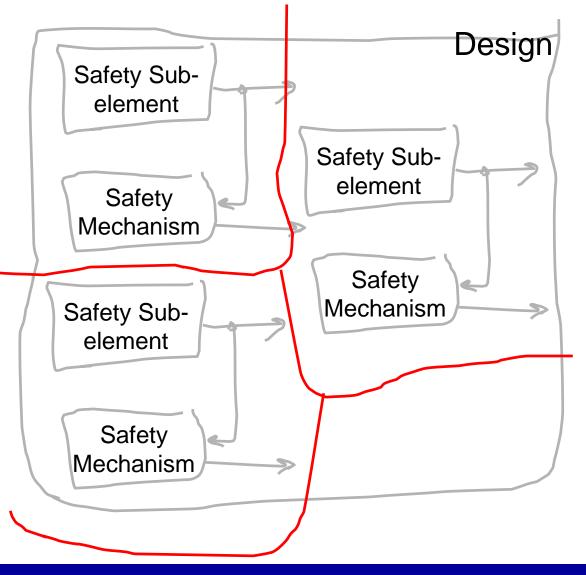

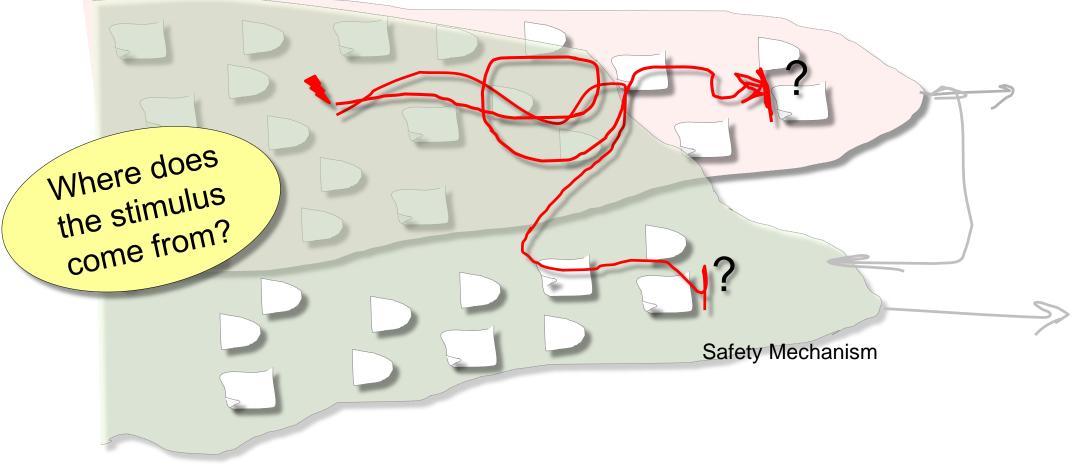

# **Dependent Fault Analysis (DFA)**

But easy in an IC to create DFI...

- Use COI to find unintended overlap which implies shared resources

- Cutpoints & black-boxes stop COI tracing when function is protected

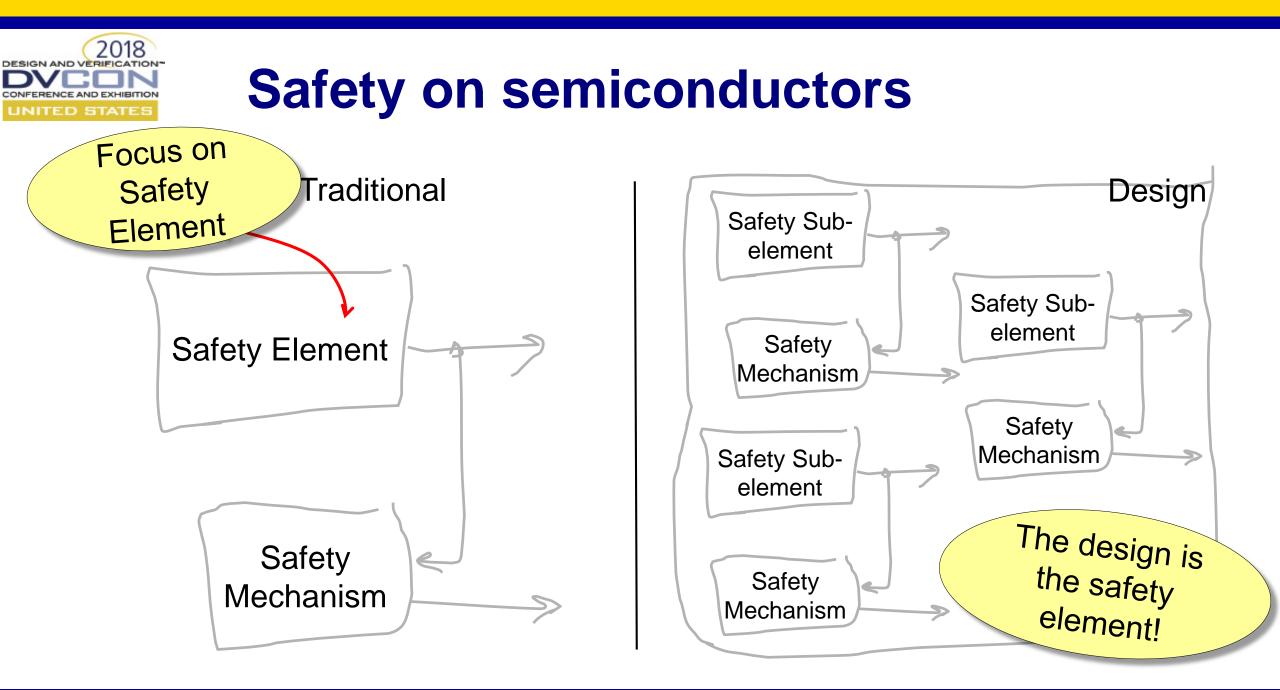

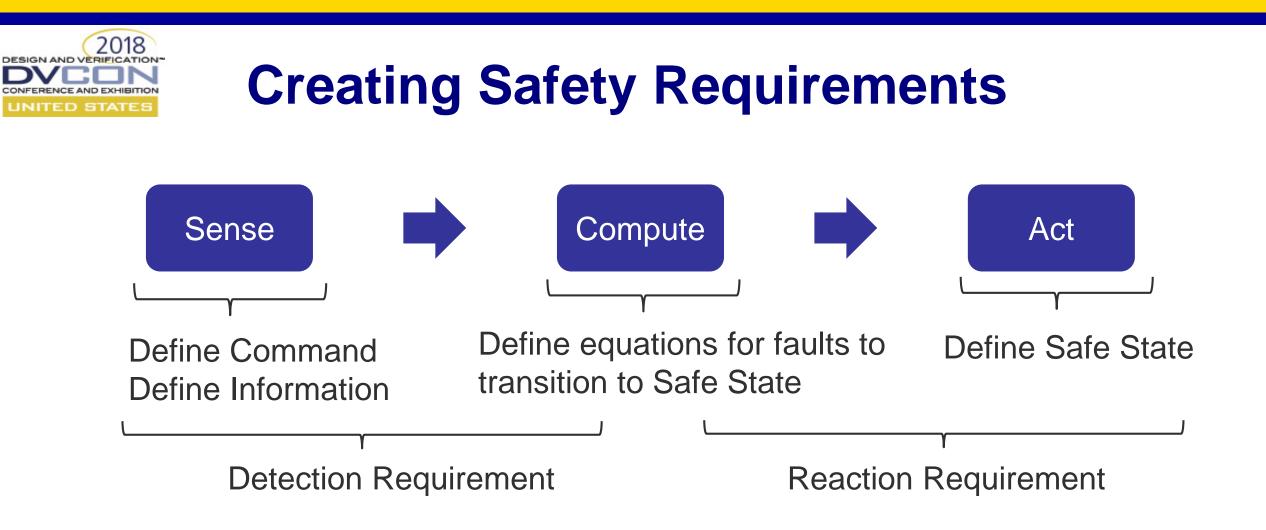

- ISO26262 *is* Functional Safety

- Requires many companies to create a Safety Culture

- Requires strong development and verification processes

- Requires analysis to address random hardware faults

- Reaching higher ASIL ratings will increase effort and costs

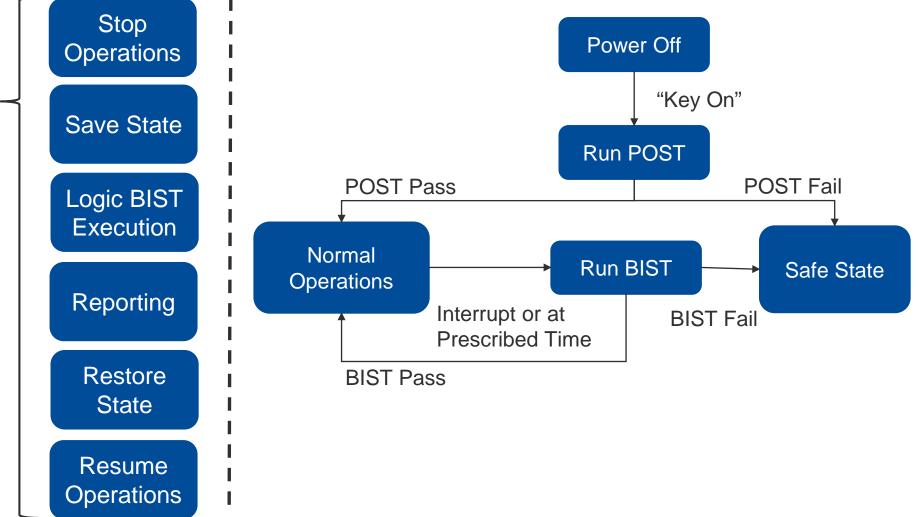

## **From Analysis to Fault Campaigns**

### Charles Battikha (chuck\_battikha@mentor.com)

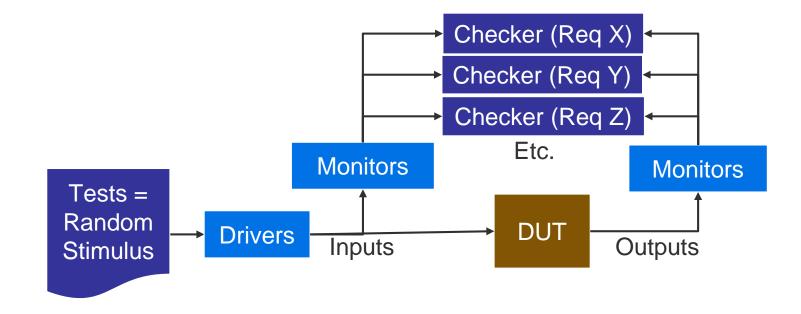

- Recap of Safety Analysis

- Usage of Metrics

- Analysis

- Fault Injection Campaign

- Summary

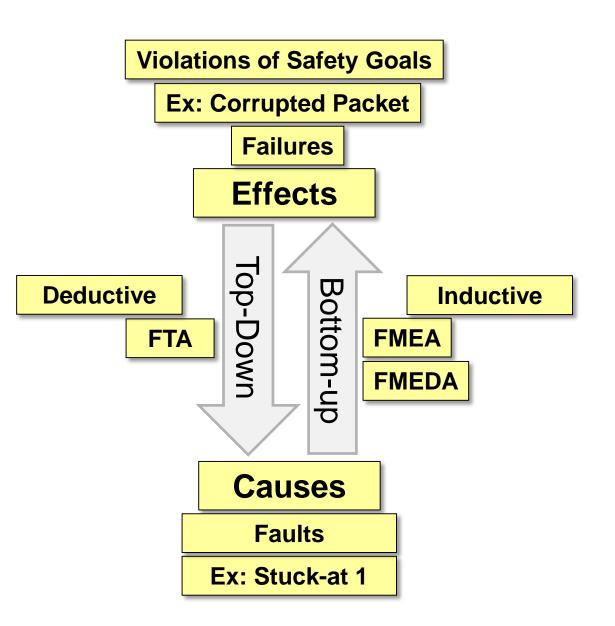

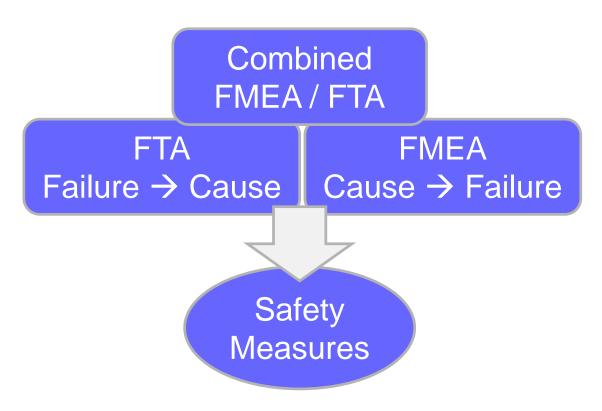

## **Safety Analysis**

- Qualitative Analysis

- Effects & Causes  $\rightarrow$  FMEA, FTA

- Dependent Failure Analysis

- Quantitative Analysis

- Metrics  $\rightarrow$  FMEDA, FTA

- Analysis of Random Faults

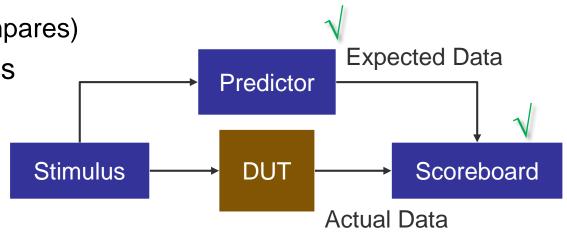

- Fault Injection Testing

- Verification of Safety Mechanisms

- Metrics

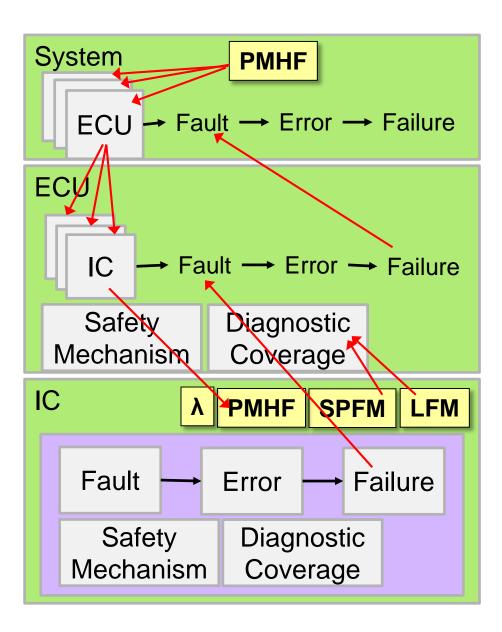

# **Usage of Metrics**

- PMHF Targets distributed top-down

- SPFM/LFM –Bottom-up, abstracts details of diagnostic coverage within the IC/IP

# FMEA & FTA

- Analysis Process to Identify

- Failure Modes in a function

- Effects of the failure

- Potential Causes of the failure

- Information allows definition of

- Safety Mechanisms

- Reaction to failure / Safe States

- Safety Requirements

- FMEA versus FTA versus FMEDA

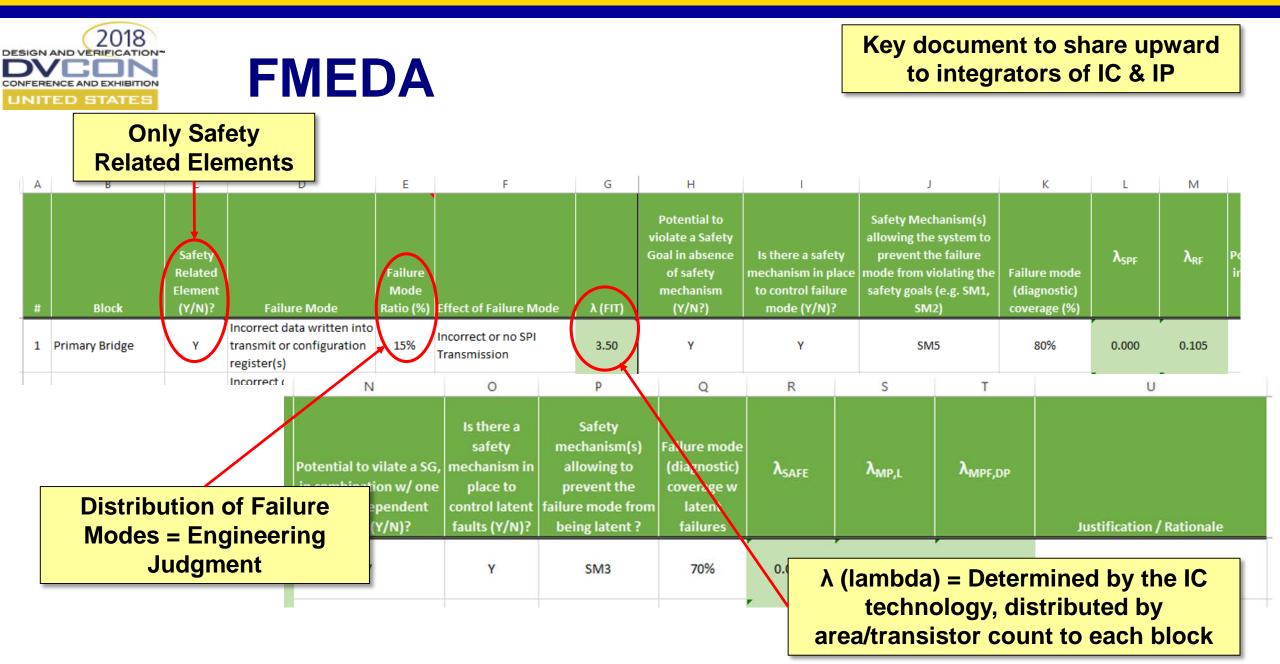

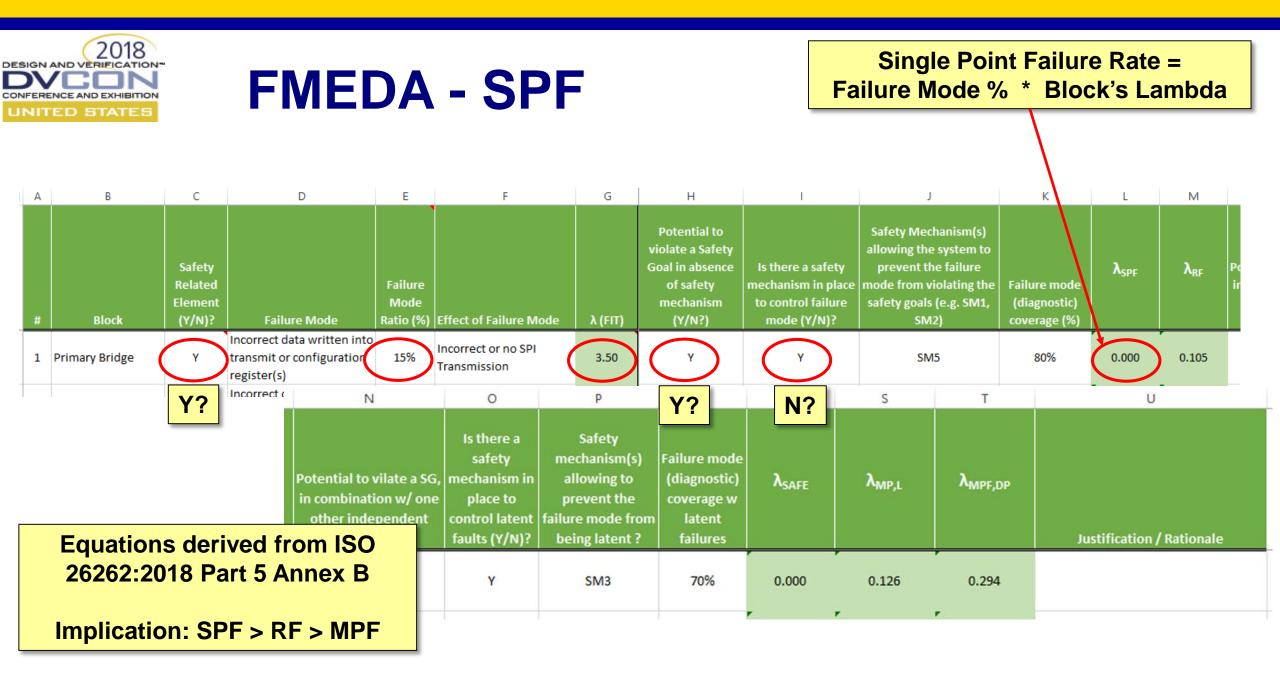

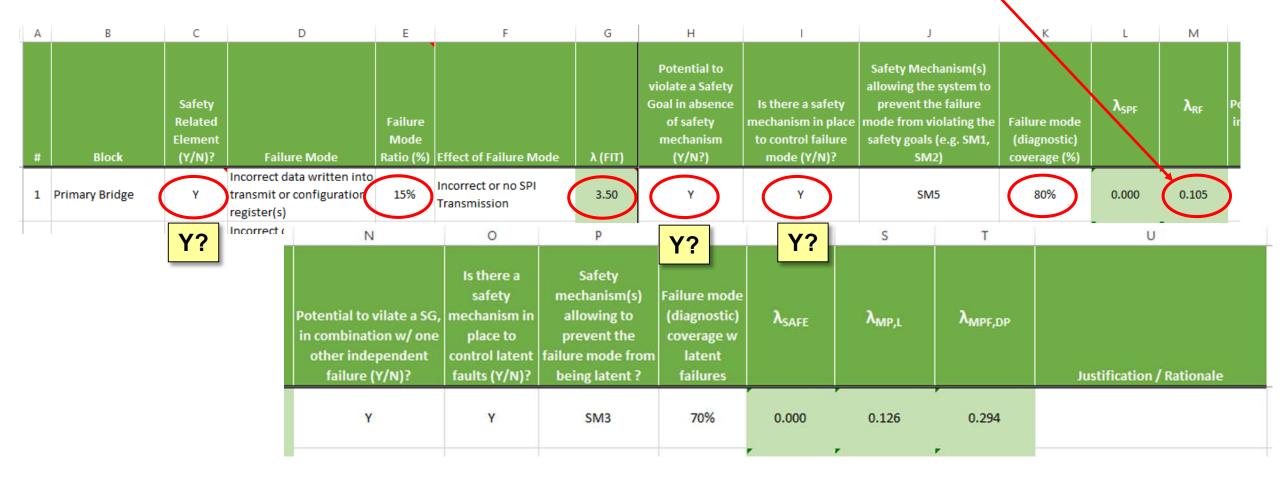

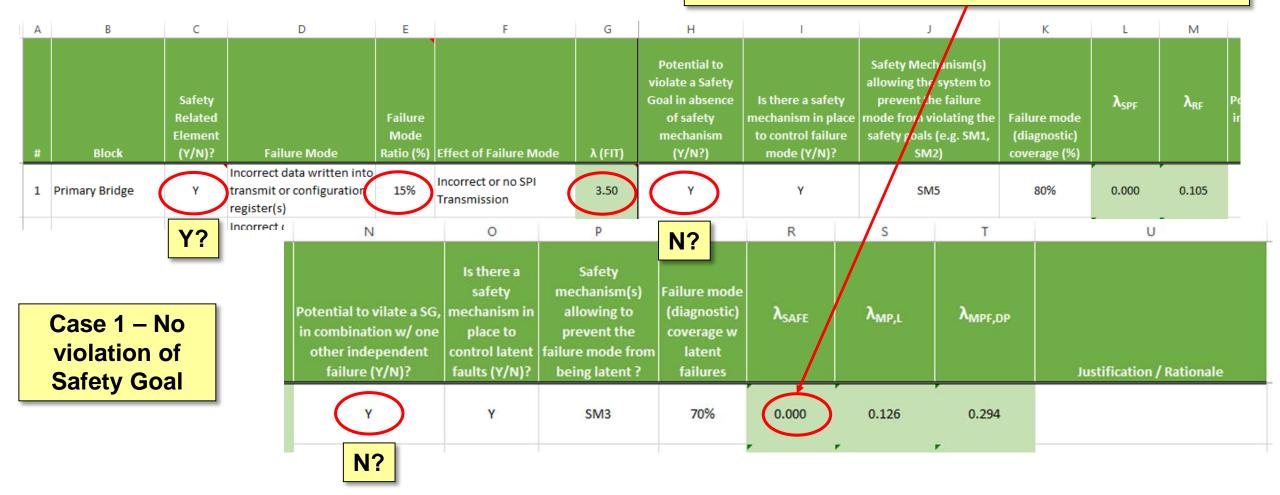

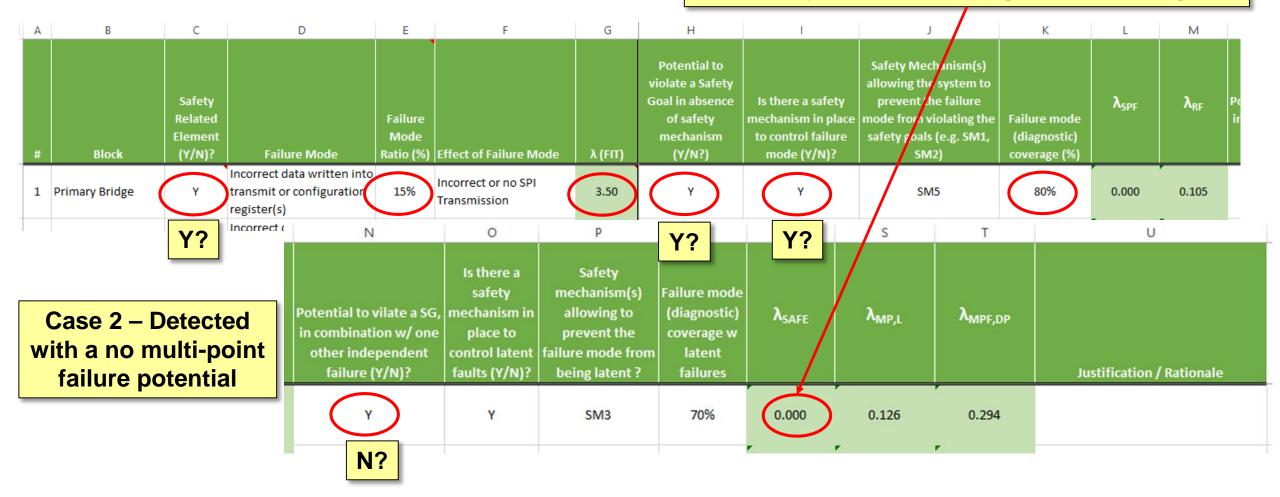

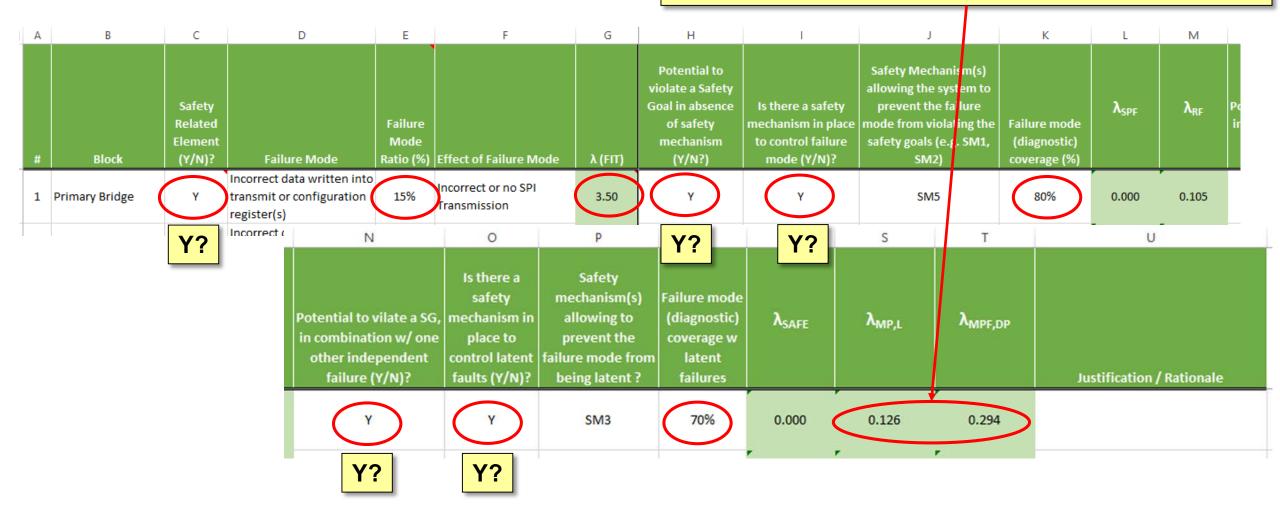

### **FMEDA – General Structure**

| Α | В              | С                                      | D                                                                       | E                                                                                              | F                                   | G                                          | Н                                                                                       | I                                                                           | J     |                                                                                            | К                                            | L                 | М                        |                    |  |               |                        |

|---|----------------|----------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------|--------------------------------------------------------------------------------------------|----------------------------------------------|-------------------|--------------------------|--------------------|--|---------------|------------------------|

| # | Block          | Safety<br>Related<br>Element<br>(Y/N)? | Failure Mode                                                            | Failure<br>Mode<br>Ratio (%)                                                                   | Effect of Failure M                 |                                            | Potential to<br>violate a Safety<br>Goal in absence<br>of safety<br>mechanism<br>(Y/N?) | Is there a safety<br>mechanism in plac<br>to control failure<br>mode (Y/N)? |       | system to<br>e failure<br>olating the<br>(e.g. SM1,                                        | Failure mode<br>(diagnostic)<br>coverage (%) | λ <sub>spf</sub>  | λ <sub>RF</sub> Po<br>ir |                    |  |               |                        |

| 1 | Primary Bridge | Y                                      | Incorrect data written into<br>transmit or configuration<br>register(s) | 15%                                                                                            | Incorrect or no SPI<br>Transmission | 3.50                                       | Y                                                                                       | Y                                                                           | SM    | 5                                                                                          | 80%                                          | 0.000             | 0.105                    |                    |  |               |                        |

|   |                |                                        | Incorrect ( N                                                           | I                                                                                              | 0                                   | P                                          | Q                                                                                       | R                                                                           | S     | Т                                                                                          |                                              | U                 |                          |                    |  |               |                        |

|   |                |                                        | in combinat<br>other inde                                               | Potential to vilate a SG,<br>in combination w/ one<br>other independent<br>failure (Y/N)?<br>Y |                                     | in combination w/ one<br>other independent |                                                                                         | in combination w/ one<br>other independent                                  |       | Safety<br>mechanism(s)<br>allowing to<br>prevent the<br>failure mode fro<br>being latent ? |                                              | λ <sub>safe</sub> | λ <sub>mp,L</sub>        | λ <sub>mpf,c</sub> |  | stification / | <sup>/</sup> Rationale |

|   |                |                                        | Ŷ                                                                       |                                                                                                |                                     | SM3                                        | 70%                                                                                     | 0.000                                                                       | 0.126 | 0.294                                                                                      |                                              |                   |                          |                    |  |               |                        |

#### Residual Failure Rate = Failure Mode % \* Block's Lambda \* (1- Safety Mechanism Diagnostic Coverage)

# FMEDA - Safe

#### Safe Failure Rate = Case 1: Failure Mode % \* Block's Lambda = Case 2: Failure Mode % \* Block's Lambda \* Safety Mechanism Diagnostic Coverage

# **FMEDA - Safe**

#### Safe Failure Rate = Case 1: Failure Mode % \* Block's Lambda = Case 2: Failure Mode % \* Block's Lambda \* Safety Mechanism Diagnostic Coverage

#### **MPF, Detected Failure Rate**

= Failure Mode % \*

#### Block's Lambda \*

#### **Diagnostic Coverage of both Safety Mechanisms.**

Where does Diagnostic Coverage come from? Answer: ISO 26262 Part 5 Annex D & Part 11 OR Fault Campaign OR Expert Judgement

| А | В              | с                                      |             | D                                                         | E                            | F                                   | G                                                                                          | н                                                                                       |                    | I.                                                                                                 | L                                                                                    |                                                | К            | L                      | м                        |

|---|----------------|----------------------------------------|-------------|-----------------------------------------------------------|------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------|--------------|------------------------|--------------------------|

| # | Block          | Safety<br>Related<br>Element<br>(Y/N)? | Failu       | ıre Mode                                                  | Failure<br>Mode<br>Ratio (%) | Effect of Failure M                 | ode λ(FIT)                                                                                 | Potential to<br>violate a Safety<br>Goal in absence<br>of safety<br>mechanism<br>(Y/N?) | mechani<br>to cont | e a safety<br>sm in place<br>rol failure<br>e (Y/N)?                                               | Safety Piech<br>allowing the<br>provent the<br>mode from vio<br>afety goals (<br>SM2 | ystem to<br>failure<br>lating the<br>e.g. SM1, | $\mathbf{N}$ | $\lambda_{\text{SPF}}$ | λ <sub>RF</sub> Po<br>ir |

| 1 | Primary Bridge | Y                                      |             | ata written into<br>r configuration                       | 15%                          | Incorrect or no SPI<br>Transmission | 3.50                                                                                       | Y                                                                                       |                    | ¥                                                                                                  | SM5                                                                                  | >                                              | 80%          | 0.000                  | 0.105                    |

|   |                |                                        | Incorrect ( | N                                                         |                              | 0                                   | P                                                                                          | Q                                                                                       | F                  |                                                                                                    | S                                                                                    | Ţ                                              | $\smile$     | U                      |                          |

|   |                |                                        |             | Potential to v<br>in combinati<br>other inde<br>failure ( | on w/ one<br>pendent         |                                     | Safety<br>mechanism(s)<br>allowing to<br>prevent the<br>failure mode fro<br>being latent ? | (diagnostic)<br>coverage w<br>m latent                                                  | λ <sub>s</sub> ,   |                                                                                                    | λ <sub>MP,L</sub>                                                                    | λ <sub>MPE</sub>                               |              |                        |                          |

|   |                |                                        |             | Y                                                         |                              | Y                                   | SM3                                                                                        | 70%                                                                                     | 0.0                | Safety Mechanisms that are star<br>well understood can rely solely<br>standard / documented source |                                                                                      |                                                |              |                        | on the                   |

|   |                |                                        |             |                                                           |                              |                                     |                                                                                            |                                                                                         |                    | Posi                                                                                               | ition ten                                                                            | ds to                                          | o vary wi    | th cus                 | tomers.                  |

### **Increase Confidence**

# **Design Hardening**

- Beyond providing/validation of Metrics, Fault Campaigns provide

- Verification of safety mechanisms

- Insight into improving coverage

- Need insight into where faults fall

|       |                                                                                              | Faults o                                                                                     | utside the cone of                                                                                                                                                                                                                              | influence of any safety critical pa                                   | th |  |

|-------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----|--|

| ļ     | 9                                                                                            | - s                                                                                          | afe Faults (252)                                                                                                                                                                                                                                |                                                                       |    |  |

|       |                                                                                              |                                                                                              | dat_i[14]                                                                                                                                                                                                                                       |                                                                       |    |  |

|       |                                                                                              |                                                                                              | dut.i_run_bist_i                                                                                                                                                                                                                                |                                                                       |    |  |

|       |                                                                                              |                                                                                              | dut.s_wbspi.first_edg                                                                                                                                                                                                                           | e                                                                     |    |  |

|       |                                                                                              |                                                                                              | dat_i[15]                                                                                                                                                                                                                                       |                                                                       |    |  |

|       |                                                                                              |                                                                                              | miso                                                                                                                                                                                                                                            |                                                                       |    |  |

|       |                                                                                              |                                                                                              |                                                                                                                                                                                                                                                 |                                                                       |    |  |

| Safet | ty critical p                                                                                | oath name:                                                                                   |                                                                                                                                                                                                                                                 | TSR-1                                                                 |    |  |

| Safet | y critical exp                                                                               | pression:                                                                                    |                                                                                                                                                                                                                                                 | dat_o                                                                 |    |  |

| Safet | y detection                                                                                  | expression:                                                                                  |                                                                                                                                                                                                                                                 | p_error                                                               |    |  |

| Total |                                                                                              |                                                                                              |                                                                                                                                                                                                                                                 | 2221                                                                  |    |  |

|       |                                                                                              |                                                                                              | ifety mechanism) (0)<br>ed by safety mechani                                                                                                                                                                                                    | sm) (8)                                                               |    |  |

| Unve  | Single-poi<br>Residual f<br>Dual poin<br><b>Fault</b>                                        | ault (not cover<br>t fault (detecte                                                          | ed by safety mechani<br>d/perceived) (211)                                                                                                                                                                                                      | sm) (8)                                                               |    |  |

|       | Single-poi<br>Residual f<br>Dual poin<br>Fault<br>Id                                         | ault (not cover                                                                              | ed by safety mechani<br>d/perceived) (211)<br>Signal Name                                                                                                                                                                                       |                                                                       |    |  |

|       | Single-pol<br>Residual f<br>Dual poin<br>Fault<br>Id                                         | ault (not cover<br>t fault (detecte                                                          | ed by safety mechani<br>d/perceived) (211)<br>Signal Name<br>dut.p_wbspi.wb_da                                                                                                                                                                  | ıt_o[0]                                                               |    |  |

|       | Single-poi<br>Residual f<br>Dual poin<br>Fault<br>Id<br>0<br>1                               | ault (not cover<br>t fault (detecte                                                          | ed by safety mechani<br>d/perceived) (211)<br>Signal Name<br>dut.p_wbspi.wb_da<br>dut.p_wbspi.shift.d                                                                                                                                           | t_o[0]<br>ata[0]                                                      |    |  |

|       | Single-pol<br>Residual f<br>Dual poin<br>Fault<br>Id                                         | ault (not cover<br>t fault (detecte                                                          | ed by safety mechani<br>d/perceived) (211)<br>Signal Name<br>dut.p_wbspi.wb_da<br>dut.p_wbspi.shift.d<br>dut.p_wbspi.shift.d                                                                                                                    | t_o[0]<br>ata[0]<br>ata[32]                                           |    |  |

|       | Single-poil<br>Residual f<br>Dual point<br>Fault<br>Id<br>0<br>1<br>2                        | ault (not cover<br>t fault (detecte                                                          | ed by safety mechani<br>d/perceived) (211)<br>Signal Name<br>dut.p_wbspi.wb_da<br>dut.p_wbspi.shift.d                                                                                                                                           | t_o[0]<br>ata[0]<br>ata[32]<br>ata[64]                                |    |  |

|       | Single-pol<br>Residual f<br>Dual poin<br>Fault<br>Id<br>0<br>1<br>2<br>3                     | ault (not cover<br>t fault (detecte                                                          | ed by safety mechani<br>d/perceived) (211)<br>Signal Name<br>dut.p_wbspi.wb_da<br>dut.p_wbspi.shift.d<br>dut.p_wbspi.shift.d                                                                                                                    | t_o[0]<br>ata[0]<br>ata[32]<br>ata[64]<br>ata[96]                     |    |  |

|       | Single-poi<br>Residual f<br>Dual poin<br>Fault<br>Id<br>0<br>1<br>2<br>3<br>4                | ault (not cover<br>t fault (detecte                                                          | ed by safety mechani<br>d/perceived) (211)<br>Signal Name<br>dut.p_wbspi.wb_da<br>dut.p_wbspi.shift.d<br>dut.p_wbspi.shift.d<br>dut.p_wbspi.shift.d<br>dut.p_wbspi.shift.d                                                                      | t_o[0]<br>ata[0]<br>ata[32]<br>ata[64]<br>ata[96]<br>r[0]             |    |  |

|       | Single-pol<br>Residual f<br>Dual poin<br>Fault<br>Id<br>0<br>1<br>2<br>3<br>4<br>5           | ault (not cover<br>t fault (detecte                                                          | ed by safety mechani<br>d/perceived) (211)<br>Signal Name<br>dut.p_wbspi.wb_da<br>dut.p_wbspi.shift.d<br>dut.p_wbspi.shift.d<br>dut.p_wbspi.shift.d<br>dut.p_wbspi.shift.d<br>dut.p_wbspi.shift.d                                               | r[0]<br>ata[32]<br>ata[96]<br>r[0]                                    |    |  |

|       | Single-poil<br>Residual f<br>Dual poin<br>Fault<br>Id<br>0<br>1<br>2<br>3<br>4<br>5<br>6     | ault (not cover<br>t fault (detecte<br>Property<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | ed by safety mechani<br>d/perceived) (211)<br>Signal Name<br>dut.p_wbspi.wb_da<br>dut.p_wbspi.shift.d<br>dut.p_wbspi.shift.d<br>dut.p_wbspi.shift.d<br>dut.p_wbspi.shift.d<br>dut.p_wbspi.shift.d<br>dut.p_wbspi.dividei<br>dut.p_wbspi.dividei | r[0]<br>ata[32]<br>ata[96]<br>r[0]                                    |    |  |

|       | Single-pol<br>Residual f<br>Dual poin<br>Fault<br>Id<br>0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | ault (not cover<br>t fault (detecte<br>Property<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | ed by safety mechani<br>d/perceived) (211)<br>Signal Name<br>dut.p_wbspi.wb_da<br>dut.p_wbspi.shift.d<br>dut.p_wbspi.shift.d<br>dut.p_wbspi.shift.d<br>dut.p_wbspi.shift.d<br>dut.p_wbspi.shift.d<br>dut.p_wbspi.shift.d<br>dut.p_wbspi.shift.d | t_o[0]<br>ata[0]<br>ata[32]<br>ata[64]<br>ata[96]<br>r[0]<br>h_reg[0] |    |  |

Fault Details

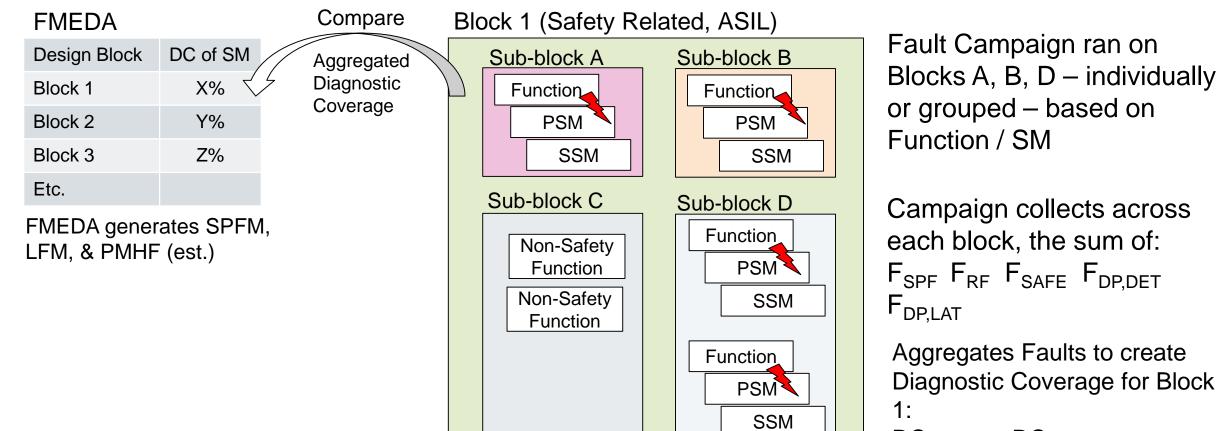

# **Aggregating / Mapping Coverage**

DC<sub>RF,Block1</sub> DC<sub>LF,Block1</sub>

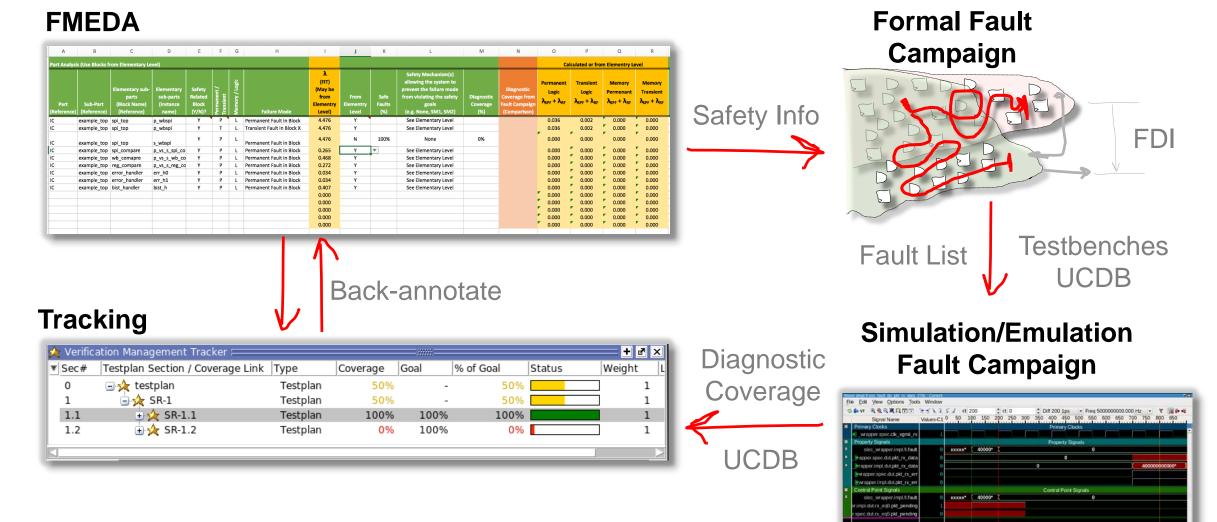

# **Management & Tracing**

- Challenges:

- Managing the Size/Complexity of FMEDA Spreadsheet

- Supporting internal reviews and audits

- Supporting external assessments

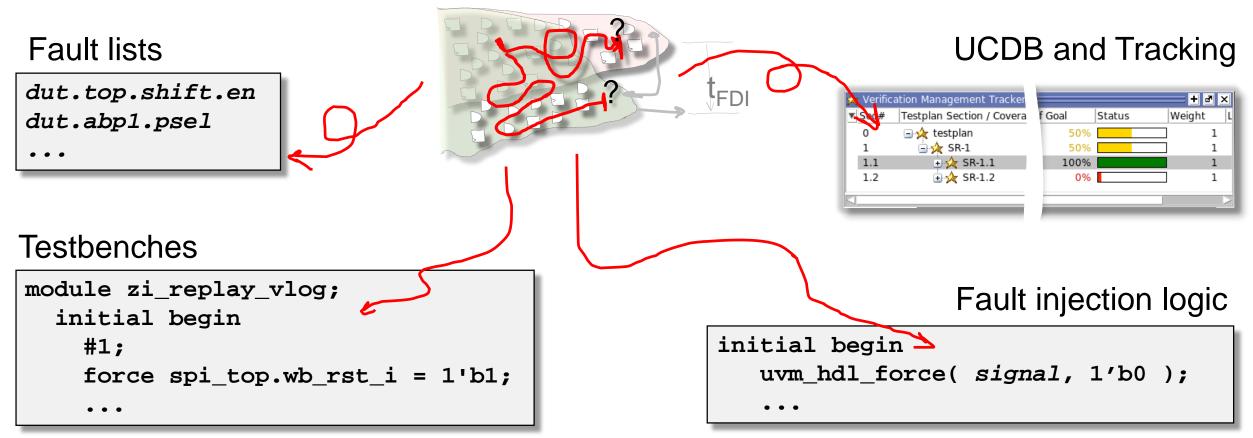

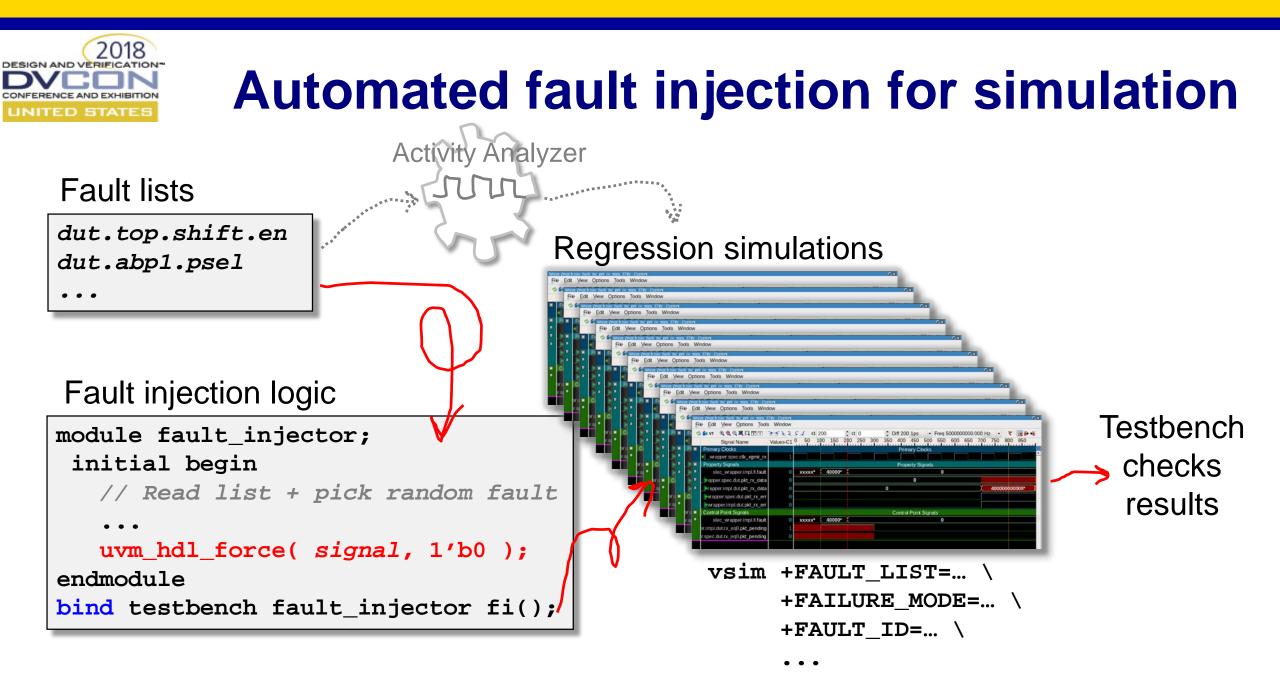

# Fault campaign process (1)

2018

DESIGN AND VERIFICATION~

UNITED STATES

# Fault campaign process (2)

#### **Safety Definitions**

| Section | Title  | Description                                           | Safety Path Expression | Primary Safey<br>Mechanism<br>Expression | Secondary Safey<br>Mechanism<br>Expression | Fault<br>Detection<br>Time | Multi-Point<br>Fault<br>Detection | Link         |

|---------|--------|-------------------------------------------------------|------------------------|------------------------------------------|--------------------------------------------|----------------------------|-----------------------------------|--------------|

| 1       | SR-1   | top_module                                            |                        |                                          |                                            |                            |                                   |              |

| 1.1     | SR-1.1 | Permanent Fault leading to wrong results in Register. | dat_o & (stb && cyc)   | p_error                                  | s_error                                    | 5                          | 5                                 | TEST_ATTRIBL |

| 1.2     | SR-1.2 | Permanent Fault leading to wrong results in Register. | ack & (stb && cyc)     | p_error                                  | s_error                                    | 5                          | 5                                 | TEST_ATTRIBL |

| 1.3     | SR-1.3 | Permanent Fault leading to wrong results in Register. | interrupt              | p_error                                  | s_error                                    | 5                          | 5                                 | TEST_ATTRIBL |

| 1.4     | SR-1.4 | Permanent Fault leading to wrong results in Register. | ss                     | p_error                                  | s_error                                    | 5                          | 5                                 | TEST_ATTRIBL |

| 1.5     | SR-1.5 | Permanent Fault leading to wrong results in Register. | sclk                   | p_error                                  | s_error                                    | 5                          | 5                                 | TEST_ATTRIBL |

| 1.6     | SR-1.6 | Permanent Fault leading to wrong results in Register. | mosi                   | p_error                                  | s_error                                    | 5                          | 5                                 | TEST_ATTRIBL |

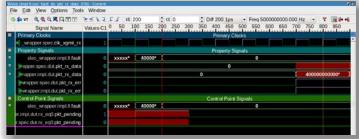

#### **Fault Campaigns**

: @ 0

2 Diff 200 1ps

¢\$ 200

XXXXX\* 40000\*

XXXXX\* 40000\*

ver.spec.dut.pkt\_rx\_dal per.impl.dut.pkt\_rx\_dal sper.spec.dut.pkt\_rx\_e sper.impl.dut.pkt\_rx\_e

sutrx eq0.pkt pend

#### Tracking

F

| Verifica | tion Man<br>Testplar |                            |                                                         |                                               | nk  1                                | Гуре                     |                | Coverag                                       | e (                                                  | <br>Goal                   | %                     | 6 of Goal                                                                                                                                | Status                        |                                                               | Weigh                                                    | ∎×<br>t L                                                |                                                           |          | Coverage            |

|----------|----------------------|----------------------------|---------------------------------------------------------|-----------------------------------------------|--------------------------------------|--------------------------|----------------|-----------------------------------------------|------------------------------------------------------|----------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------|----------|---------------------|

| 0        | 🖃 🔆 te               | estplan                    |                                                         |                                               |                                      | Tes                      | tplan          | 5                                             | 0%                                                   |                            | -                     | 50%                                                                                                                                      |                               |                                                               |                                                          | 1                                                        |                                                           | K        |                     |

| 1        | - ÷                  | SR-1                       |                                                         |                                               |                                      | Tes                      | tplan          | 5                                             | 0%                                                   |                            | -                     | 50%                                                                                                                                      |                               |                                                               |                                                          | 1                                                        |                                                           | <u> </u> |                     |

| 1.1      | ŧ                    | 🔆 🙀 SR                     | -1.1                                                    |                                               |                                      | Tes                      | tplan          | 10                                            | 0%                                                   | 100                        | %                     | 100%                                                                                                                                     |                               |                                                               |                                                          | 1                                                        |                                                           |          | UCDB                |

| 1.2      | ÷                    | 🕁 SR                       | -1.2                                                    |                                               |                                      | Tes                      | tplan          |                                               | 0%                                                   | 100                        | %                     | 0%                                                                                                                                       | -                             |                                                               |                                                          | 1                                                        | L                                                         |          |                     |

|          | A                    | В                          | С                                                       | D                                             | E                                    | F                        | G              | н                                             | 1                                                    | 1                          | К                     | L                                                                                                                                        | м                             | N                                                             | 0                                                        | Р                                                        | Q                                                         | R        |                     |

|          | Part Analys          | is (Use Blocks fi          | rom Elementary L                                        | evel)                                         |                                      |                          |                |                                               |                                                      |                            |                       |                                                                                                                                          |                               |                                                               | Ca                                                       | lculated or fro                                          | m Elementry L                                             | evel     |                     |

|          | Part<br>(Reference   | Sub-Part<br>(Reference)    | Elementary sub-<br>parts<br>(Block Name)<br>(Reference) | Elementary<br>sub-parts<br>(instance<br>name) | Safety<br>Related<br>Block<br>(Y/N)? | Permanent /<br>Transient | Memory / Logic | Failure Mode                                  | λ<br>(FIT)<br>(May be<br>from<br>Elementry<br>Level) | From<br>Elementry<br>Level | Safe<br>Faults<br>(%) | Safety Mechanism(s)<br>allowing the system to<br>prevent the failure mode<br>from violating the safety<br>goals<br>(e.g. None, SM1, SM2) | Diagnostic<br>Coverage<br>(%) | Diagnostic<br>Coverage from<br>Fault Campaign<br>(Comparison) | Permanent<br>Logic<br>λ <sub>SPF</sub> + λ <sub>RF</sub> | Transient<br>Logic<br>λ <sub>SPF</sub> + λ <sub>RF</sub> | Memory<br>Permenant<br>λ <sub>SPF</sub> + λ <sub>RF</sub> |          |                     |

|          | IC<br>IC             | example_top<br>example_top |                                                         | p_wbspi<br>p_wbspi                            | Y                                    | Р                        |                | anent Fault in Block<br>ient Fault in Block X | 4.476<br>4.476                                       | Y                          |                       | See Elementary Level<br>See Elementary Level                                                                                             |                               | _                                                             | 0.036                                                    | 0.002                                                    | 0.000                                                     | 0.000    |                     |

|          | IC                   | example_top                | spi_top                                                 | s_wbspi                                       | Ŷ                                    | P                        | L<br>Perma     | anent Fault in Block                          | 4.476                                                | N                          | 100%                  | None                                                                                                                                     | 0%                            |                                                               | 0.000                                                    | 0.000                                                    | 0, 0                                                      |          | Template<br>Annotat |

|          | IC                   | example_top<br>example_top |                                                         | p_vs_s_spi_co<br>p_vs_s_wb_co                 |                                      | P                        |                | anent Fault in Block<br>anent Fault in Block  | 0.265<br>0.468                                       | Y                          | ▼                     | See Elementary Level<br>See Elementary Level                                                                                             |                               |                                                               | 0.000                                                    | 0.000                                                    | 0.000                                                     | 0.000    | Templat             |

| ĐΑ       |                      |                            |                                                         |                                               |                                      |                          |                |                                               |                                                      |                            |                       |                                                                                                                                          |                               |                                                               |                                                          |                                                          |                                                           |          |                     |

- Qualitative Analysis with a FMEA/FTA & Quantitative Analysis with a FMEDA are standard practices

- FMEDA is a key document to allows integrators of IC/IP to understand functional safety metrics

- Especially important when considering configuration / feature options

- Connecting information from Fault Injection Campaigns to the FMEDA

- Validates early predictions of Diagnostic Coverage and Hardware Architectural Metrics

- With challenging architectures, the only means to determine coverage

- Fault Injection Campaigns serve as verification of safety mechanisms

### **Break**

# How Formal Reduces Fault Analysis for ISO 26262

Doug Smith Doug\_Smith@mentor.com Verification Consultant Mentor Consulting

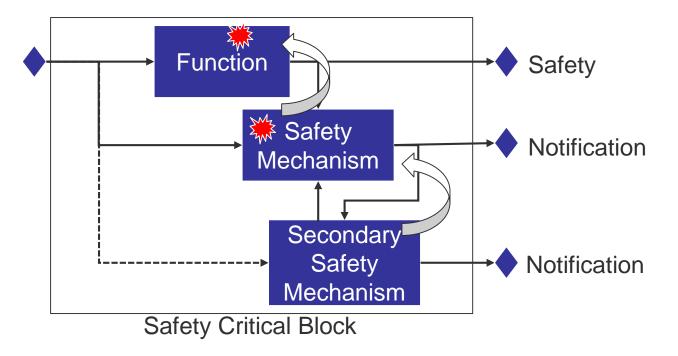

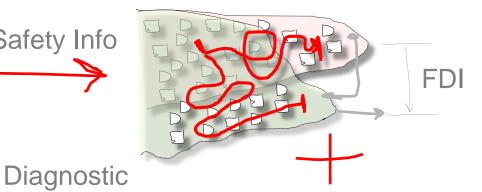

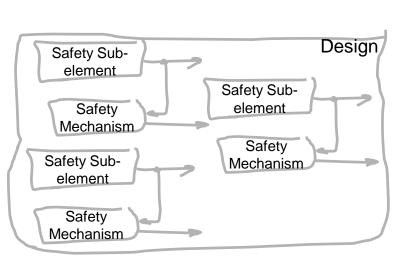

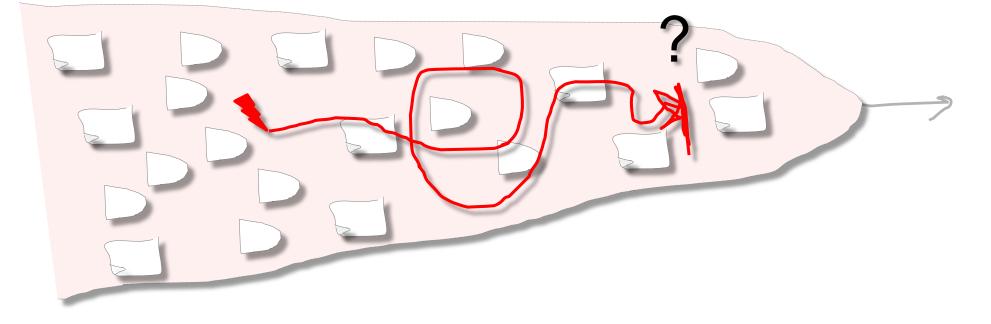

### ICs are harder

- Potentially lots of

- Safety critical functions

- Safety mechanisms

- Secondary safety mechanisms

- Large designs  $\rightarrow$  thousands of random faults to inject!

- How to categorize faults shared between shared logic?

- Need tests that allow faults to propagate and be detected

- Large simulation time to test software safety mechanisms

- May have large fault detection time intervals

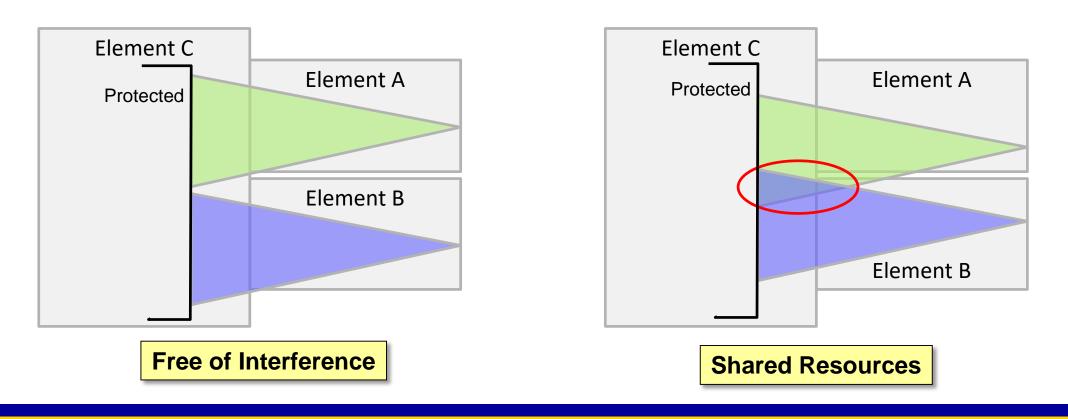

# Try breaking up the problem!

- Not allowed  $\,\, \ensuremath{\mathfrak{S}}$

- Must show independence with Dependent Fault Analysis (DFA)

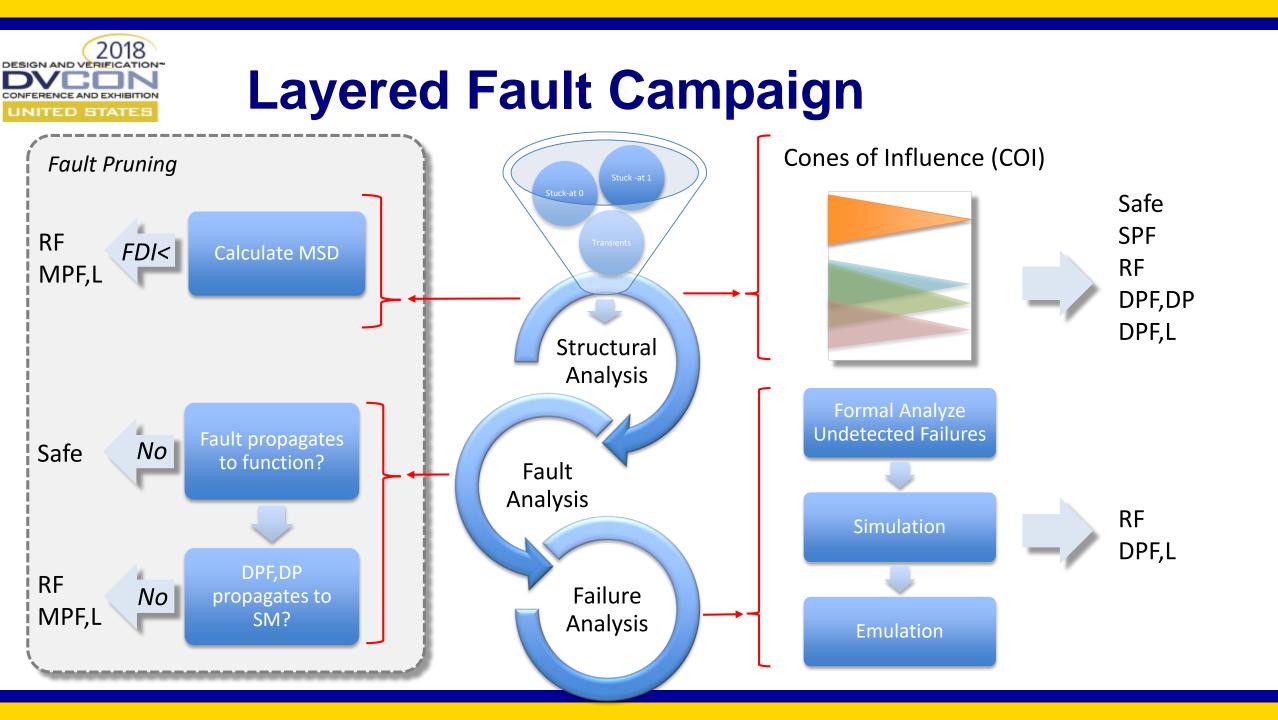

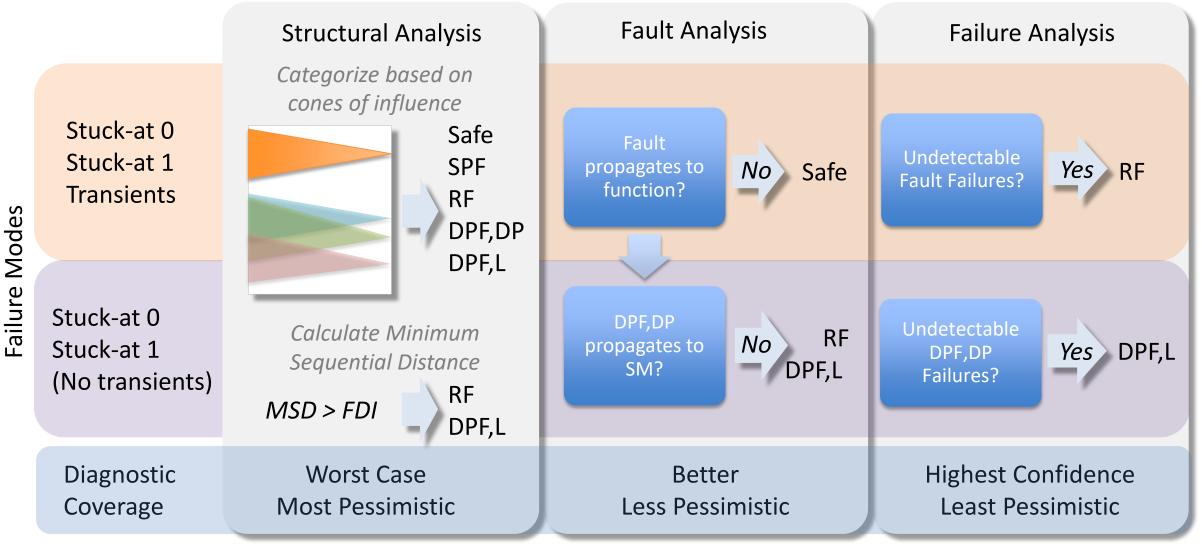

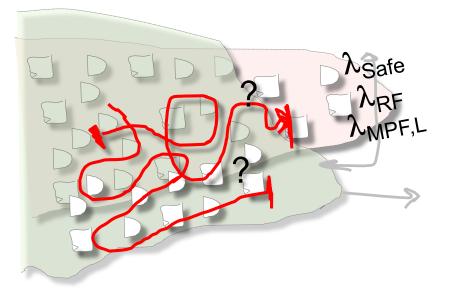

### **COI fault analysis**

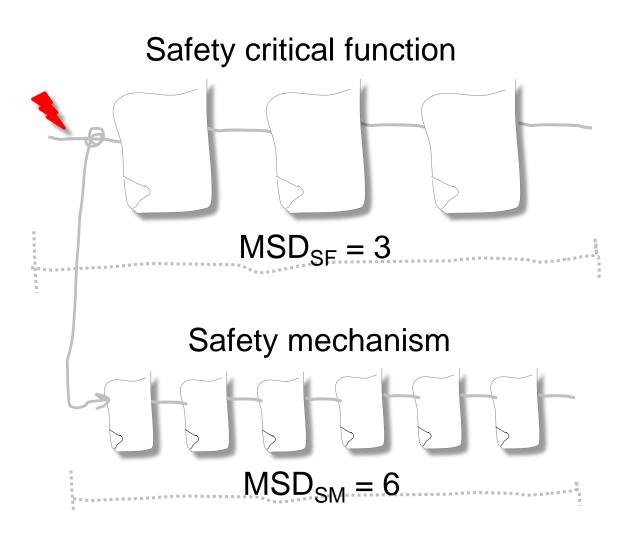

### Minimum sequential distance Not FTTI! Not FTTI!

• Fault Detection Interval (FDI)

• Violation if  $MSD_{SM} - MSD_{SF} > FDI$

```

E.g.,

FDI = 2

6 - 3 > 2

Residual or Latent Fault

```

∴, Too long to propagate.... safety goal violation!

### Safety function fault propagation

No propagation -> Safe fault!

### Safety mechanism fault propagation

No propagation -> undetectable fault!

# **Traditional formal**

• Input constraints and assumptions

| asm_drive_data      | : | assume property ( pkt_val | -> | pkt_data == data              | ); |

|---------------------|---|---------------------------|----|-------------------------------|----|

| asm_pkt_stable      | : | assume property ( pkt_val | -> | <pre>\$stable(packet)</pre>   | ); |

| asm_payload_stable  | : | assume property ( pkt_val | -> | <pre>\$stable(payload)</pre>  | ); |

| asm_pkt_kind_stable | : | assume property ( pkt_val | -> | <pre>\$stable(pkt_type)</pre> | ); |

- Issues

- Need input requirements

- Labor intensive

- Not automated

- Typically incomplete formal tries everything!

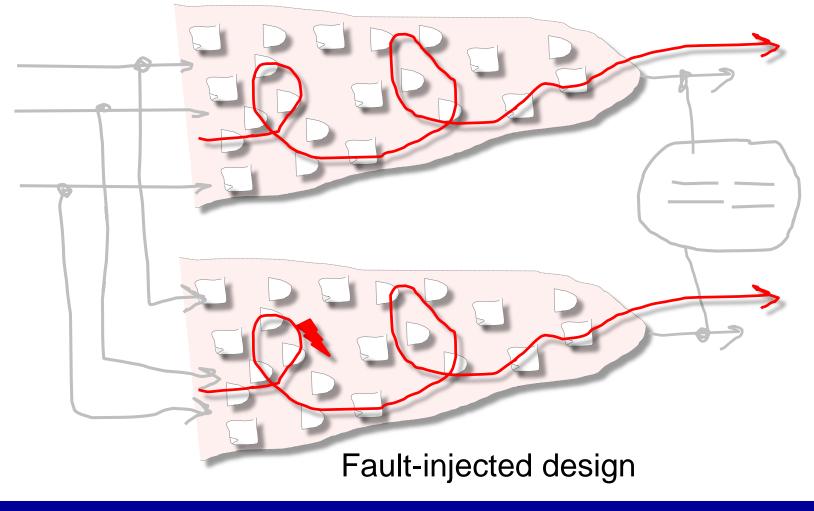

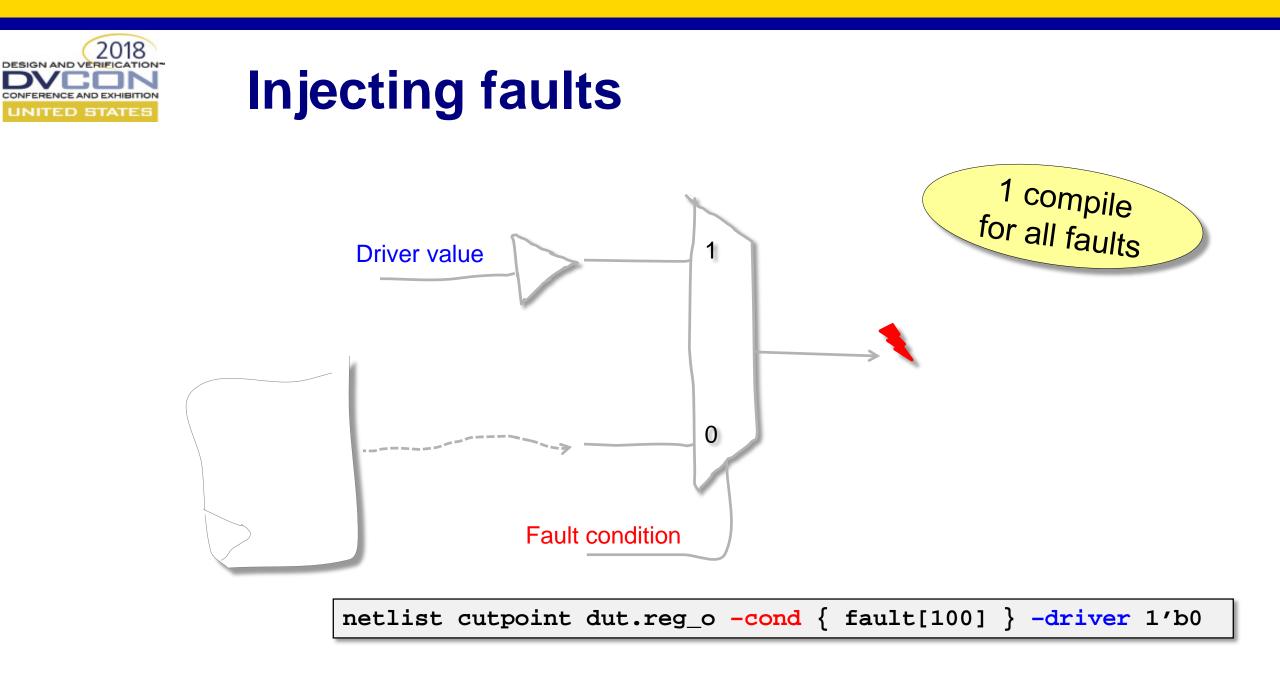

### **Sequential Equivalency Checking**

Original design

Conditional cutpoint

netlist cutpoint {impl.dut.tx\_data\_fif00.fif00.genblk2.mem0.rdata[2]} \

-cond {impl.fi fault[1]} -driver 1'b0

• SLEC target

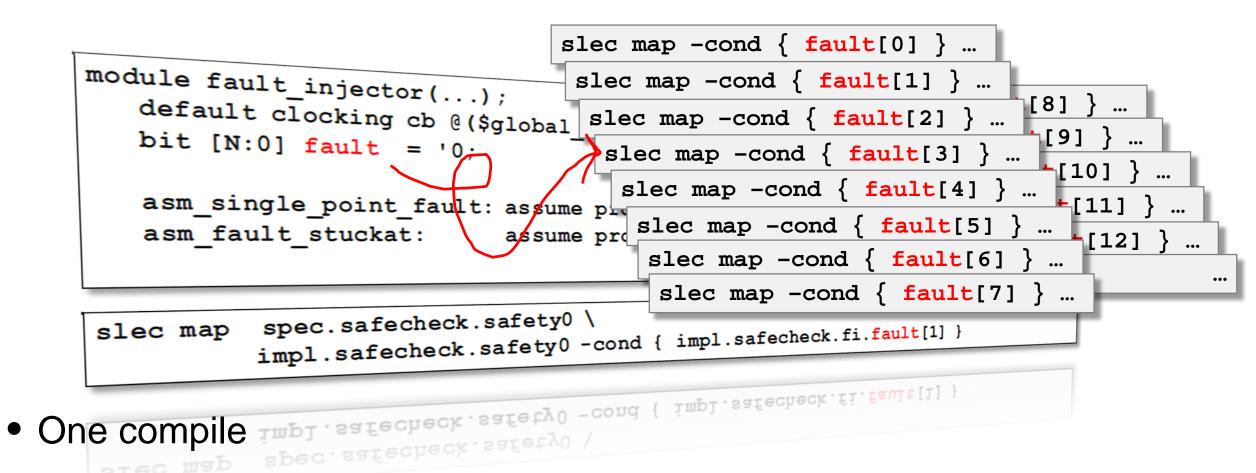

slec map spec.safecheck.safety0 \

impl.safecheck.safety0 -cond { impl.safecheck.fi fault 1] }

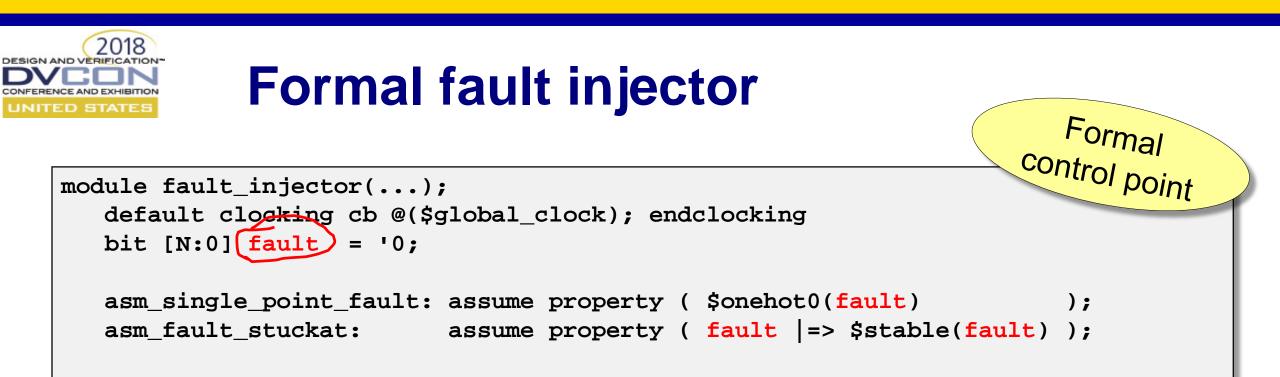

### **Parallel fault analysis**

Thousands of parallel fault targets analyzed by formal

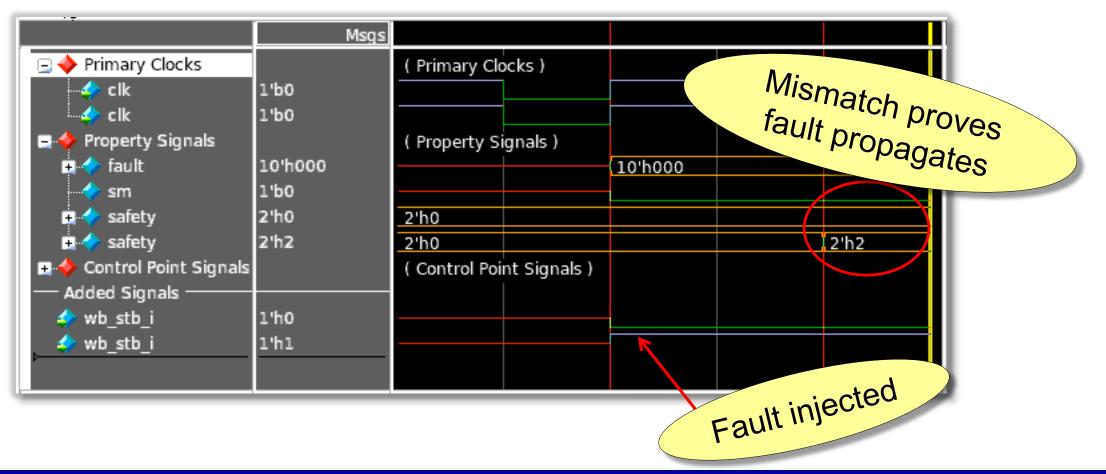

### Proving a fault propagates

#### SLEC

Structural analysis

- Quick and easy

- But do all faults really propagate?

Fault analysis

# Need failure analysis ...

- Simultaneous propagation to output and safety mechanism?

- Within time window?

#### Failure analysis

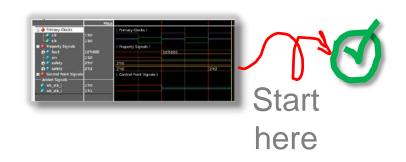

### **Example undetected failure**

| 3 | 💠 VT 🔍 🤻 🔍 🅱 🏹 🎹 🗊             | ᡄᢣᡄᠽ      | ीम है कि जि | 200 :    | ¢ C2 0     | 韋 Diff 200 | 1ps 🚽        | Freq 5000 | 000000. | 000 Hz |                        | 🔀 🛃 📲 |

|---|--------------------------------|-----------|-------------|----------|------------|------------|--------------|-----------|---------|--------|------------------------|-------|

|   | Signal Name                    | Values-C1 | 0 50 1      | 00 150 2 | 00 250 300 | 350 400    | 450 500      | 550 60    | 0 650   | 700    | 750 8 <mark>0</mark> 0 | 850   |

| 3 | Primary Clocks                 |           |             |          |            | Prim       | ary Clocks   |           |         |        |                        |       |

|   | 🕺 _wrapper.spec.clk_xgmii_rx   | 1         |             |          |            |            |              |           |         |        |                        |       |

| 3 | Property Signals               |           |             |          |            | Prope      | erty Signals |           |         |        |                        |       |

| Ð | slec_wrapper.impl.fi.fault     | 0         | XXXXX*      | 40000*   | ¥<br>/     |            |              | 0         |         |        |                        |       |

| Ð | ₿apper.spec.dut.pkt_rx_data    | 0         |             |          |            |            | 0            |           |         |        |                        |       |

| Ð |                                | 0         |             |          |            | 0          |              |           |         | X      | 400000000              | 0000* |

|   | ▶wrapper.spec.dut.pkt_rx_err   | 0         |             |          |            |            |              |           |         |        |                        |       |

|   | wrapper.impl.dut.pkt_rx_err    | 0         |             |          |            |            |              |           |         |        |                        |       |

| ] | Control Point Signals          |           |             |          |            | Control    | Point Signa  | ls        |         |        | Safe<br>necha          | ety   |

| Ð | slec_wrapper.impl.fi.fault     | 0         | XXXXX*      | 40000*   | X          |            |              | 0         |         | 7      |                        | niem  |

|   | er.impl.dut.rx_eq0.pkt_pending | 1         |             |          |            |            |              |           |         | n      | necha                  | 11311 |

|   | r.spec.dut.rx_eq0.pkt_pending  | 0         |             |          | 1          |            |              |           |         |        | fai                    | S     |

|   |                                |           |             |          |            |            |              |           |         |        |                        |       |

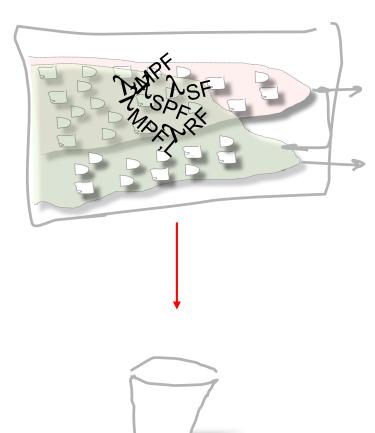

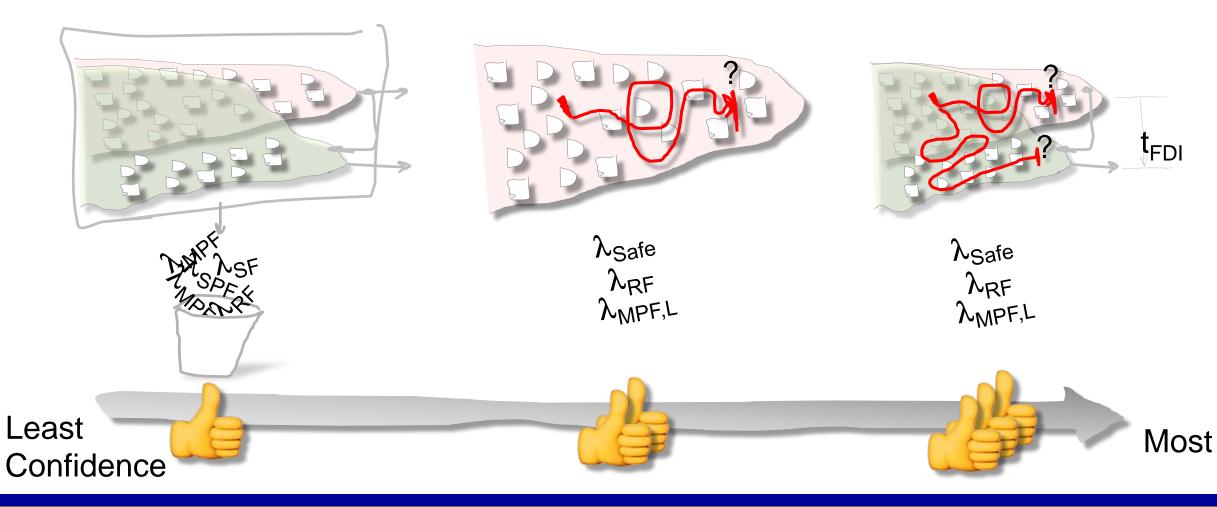

### **Building confidence**

#### Structural analysis

#### Fault analysis

#### Failure analysis

# **Diagnostic coverage**

• DC = % of safety element covered by safety mechanism

# A range for diagnostic cov Potential Latent

| Potential RF                      | Structura  | l analysis | Fault an   | alysis   | Failure a  | nalysis   |  |  |

|-----------------------------------|------------|------------|------------|----------|------------|-----------|--|--|

| Potential                         | Unverified | Verified   | Unverified | Verified | Unverified | Verified  |  |  |

| Safe                              | 286        | 286        | 0          | 299      | 0          | 301       |  |  |

| Residual                          | 8          | 0          | 0          | 12       | 0          | 17        |  |  |

| Dual-point in Safey Function      | 219        | 0          | 215        | 0        | 134        | 84        |  |  |

| Dual-point in Safety<br>Mechanism | 2013       | 0          | 1704       | 28       | 1554       | 132       |  |  |

| Latent                            | 0          | 0          | 0          | 296      | 0          | 307       |  |  |

| DC <sub>Residual</sub>            | 91.0%      | 99.7%      | 91.0% -    | 99.5%    | 94,0% -    | 6 - 99.3% |  |  |

| DC <sub>Latent</sub>              | 20.3%      | - 100%     | 20.8% -    | 88.2%    | 26.3%      | 87.8%     |  |  |

| Continuous refinement             |            |            |            |          |            |           |  |  |

SAFECH

Project

Fault Sun

Fault Deta

Transcript

### **Example report**

| K A | All Faults (All Safety Critical Paths)                        |              |              |                  |          |  |  |

|-----|---------------------------------------------------------------|--------------|--------------|------------------|----------|--|--|

|     | Fault Type                                                    | Previous A   | Analysis     | Current Analysis |          |  |  |

| y   |                                                               | Unverified   | Verified     | Unverified       | Verified |  |  |

|     | Safe faults (outside cone of influence)                       | 0            | 287          | 0                | 287      |  |  |

|     | Safe faults (fault detected by a safety mechanism)            | 0            | 0            | 0                | 120      |  |  |

|     | Single-point faults (no safety mechanism)                     | 0            | 0            | 0                | 0        |  |  |

|     | Residual fault (not covered by safety mechanism)              | 8            | 0            | 8                | 0        |  |  |

|     | Dual point fault (detected/perceived) in safety function      | 202          | 0            | 192              | 0        |  |  |

|     | Dual point fault (detected/perceived) in the safety mechanism | 2035         | 0            | 1841             | 0        |  |  |

|     | Dual point fault latent                                       | 0            | 0            | 0                | 84       |  |  |

|     | Subtotal                                                      | 2245         | 287          | 2041             | 491      |  |  |

|     | Total                                                         | 2532 2532    |              |                  |          |  |  |

|     | Number of randomly sampled faults                             | 2245 (88.7%) |              |                  |          |  |  |

|     | Design bits                                                   |              | 2245 (unsafe | e) / 2532 (all)  |          |  |  |

|     | Residual Diagnostic Coverage                                  |              | 92.10% -     | 100.00%          |          |  |  |

|     | Latent Diagnostic Coverage                                    |              | 23.97%       | - 96.68%         |          |  |  |

• Formal can run on gates, but ...

- RTL more likely pessimistic

- Gates likely mask faults

$$DC_{RTL} = N_{RF-RTL} / N_{RTL}$$

$$DC_{Gates} = N_{RF-Gates} / N_{Gates}$$

$\therefore$ , DC<sub>Gates</sub> > DC<sub>RTL</sub>

### **RTL to gates equivalency**

#### **RTL Structural analysis**

#### Gates Structural analysis

| DC <sub>Residual</sub> | 91% - 99.7% |

|------------------------|-------------|

| DC <sub>Latent</sub>   | 20% - 100%  |

| DC <sub>Residual</sub> | 94% 97%   |

|------------------------|-----------|

| DC <sub>Latent</sub>   | 18% - 98% |

• If RTL more pessimistic, gates are unnecessary ...

# **Potential limitations using formal** ...

- Large number of formal targets

- Long formal run times

- Large number of inconclusives

- Results biased towards formal friendly designs and design areas

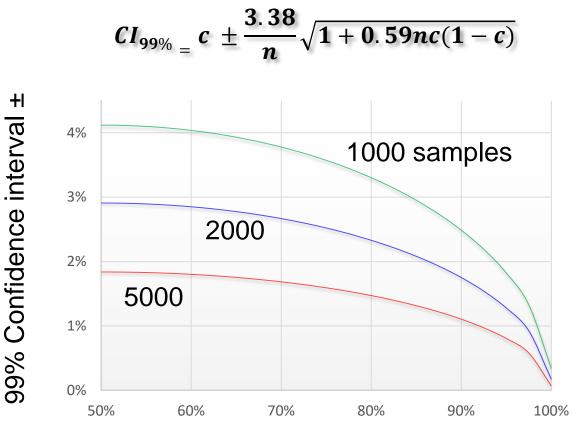

# **Random sampling**

- Confidence interval

- Allows picking random samples

- Solves

- Large numbers of formal targets

- Large numbers of inconclusives

- Unmanageable results

Fault Coverage (in samples)

Agrawal & Kata, D&T 1990

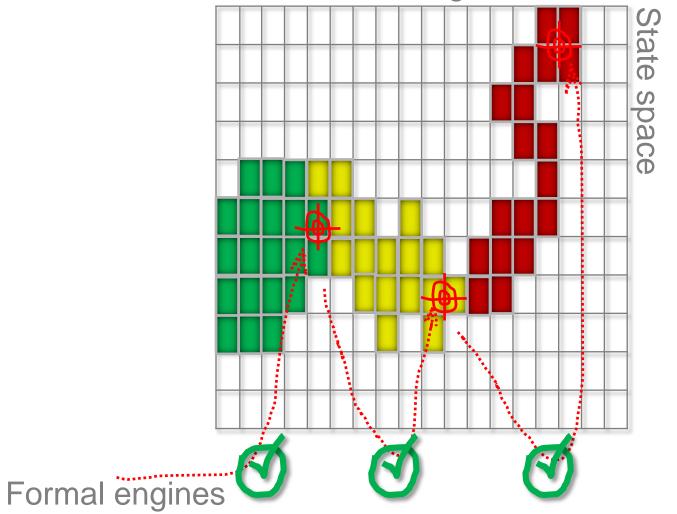

Intermediate targets

- Possibilities

- Write temp targets

- Automatic goal-posting formal engines

- Seed formal with waveforms

- Find activity around faults

### **Automated flow**

#### Safety Definitions

| Section | Title    | Description                                           | Safety Path Expression | Primary Safey<br>Mechanism | Secondary Safey<br>Mechanism | Fault<br>Detection | Multi-Point<br>Fault | Link        |

|---------|----------|-------------------------------------------------------|------------------------|----------------------------|------------------------------|--------------------|----------------------|-------------|

|         |          |                                                       |                        | Expression                 | Expression                   | Time               | Detection            |             |

| 1       | SR-1     | top_module                                            |                        |                            |                              |                    |                      |             |

| 1.1     | SR-1.1   | Permanent Fault leading to wrong results in Register. | dat_o & (stb && cyc)   | p_error                    | s_error                      | 5                  | 5                    | TEST_ATTRIB |

| 1.2     | 2 SR-1.2 | Permanent Fault leading to wrong results in Register. | ack & (stb && cyc)     | p_error                    | s_error                      | 5                  | 5                    | TEST_ATTRIB |

| 1.3     | 8 SR-1.3 | Permanent Fault leading to wrong results in Register. | interrupt              | p_error                    | s_error                      | 5                  | 5                    | TEST_ATTRIB |

| 1.4     | SR-1.4   | Permanent Fault leading to wrong results in Register. | ss                     | p_error                    | s_error                      | 5                  | 5                    | TEST_ATTRIB |

| 1.5     | 5 SR-1.5 | Permanent Fault leading to wrong results in Register. | sclk                   | p_error                    | s_error                      | 5                  | 5                    | TEST_ATTRIB |

| 1.6     | 5 SR-1.6 | Permanent Fault leading to wrong results in Register. | mosi                   | p_error                    | s_error                      | 5                  | 5                    | TEST_ATTRIB |

#### Handoff to simulation and emulation

Formal Fault Campaign

#### Fault campaign from the top down

dut.rx\_eq0.pkt\_pendi

#### **FMEDA**

| FMEDA<br>A B C D E F G H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I J K L M N O P Q R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Fc             | ormal Fault Campaign                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Part         Sub-Part<br>(Reference)         Elementary sub-<br>parts<br>(Block from Elementary sub-<br>parts)         Elementary<br>sub-parts<br>(Instance<br>name)         Safety<br>Related<br>Block<br>(Instance<br>Block         T         L         Partmanent Fault in Block           1C         coample_top spl_top         p_wtspl         Y         T         L         Permanent Fault in Block           1C         coample_top spl_top         p_wtspl         Y         P         L         Permanent Fault in Block           1C         coample_top spl_top         p_wtspl         Y         P         L         Permanent Fault in Block           1C         coample_top spl_top         p_wtspl         Y         P         L         Permanent Fault in Block           1C         coample_top spl_top         p_wts_twb_co         Y         P         L         Permanent Fault in Block           1C         coample_top spl_compare         p_ws_tspl_co         Y         P         L         Permanent Fault in Block           1C         coample_top spl_compare         p_ws_tspl_co         Y         P         L         Permanent Fault in Block           1C         coample_top error_handler         err_h1         Y         P         L         Permanent Fault in Block           1C         coample_top bist_handler | Y         See Elementary Level         0.036         0.002         0.000         0.000           4.476         N         100%         None         0%         0.000         0.000         0.000         0.000           4.476         N         100%         None         0%         0.000         0.000         0.000         0.000           4.476         Y         See Elementary Level         0.000         0.000         0.000         0.000           4.0272         Y         See Elementary Level         0.000         0.000         0.000         0.000           4.034         Y         See Elementary Level         0.000         0.000         0.000         0.000           4.034         Y         See Elementary Level         0.000         0.000         0.000         0.000 | Safety<br>info | t FDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |