# Holistic Approach to IO Timing Verification Using **Portable Stimulus and Assertions Amitesh Khandelwal and Praveen Kumar**

## Overview

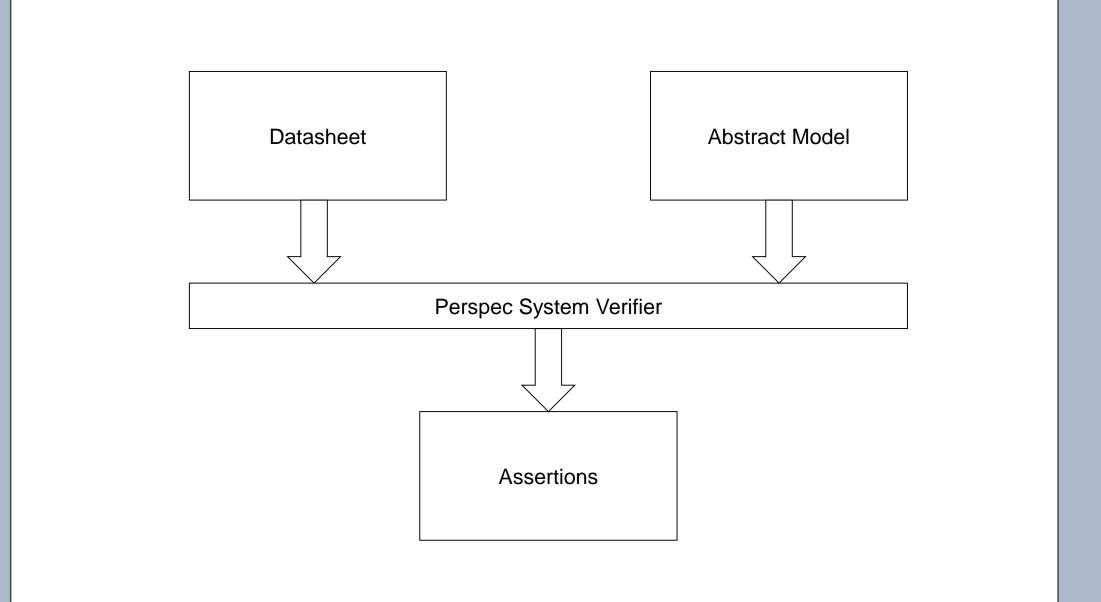

- Datasheet input must be in tabular format.

- Abstract model is coded in Cadence specific System Level Notation (SLN) Language.

- Assertions are generated in SystemVerilog Assertion (SVA) format.

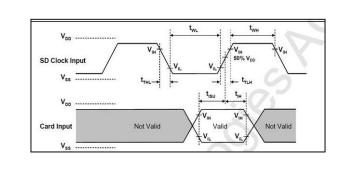

#### Extraction of IO timing parameters

| Parameter                                             | Symbol | Min | Max | Unit | Notes   |

|-------------------------------------------------------|--------|-----|-----|------|---------|

| lock frequency in data transfer mode                  | fPP    | 0   | 50  | MHz  |         |

| lock low time                                         | tWL    | 7.0 |     | ns   |         |

| lock high time                                        | tWH    | 7.0 |     | ns   |         |

| lock rise time                                        | tTLH   |     | 3   | ns   |         |

| lock fall time                                        | tTHL   |     | 3   | ns   | CL≤10pF |

| MD, DAT input setup time                              | tISU   | 6   |     | ns   | CL210pF |

| MD, DAT input hold time                               | tIH    | 2   |     | ns   |         |

| MD, DAT output delay time during data<br>ransfer mode | tODLY  |     | 14  | ns   |         |

| MD. DAT output hold time                              | t0H    | 2.5 |     | ns   |         |

|       | #Check Mod  | te. ∔Si | g Port, #  | lk Port.               | #TParam. | #Min. | #Max. | #Offset |

|-------|-------------|---------|------------|------------------------|----------|-------|-------|---------|

|       | Clock duty  |         |            |                        |          |       |       |         |

|       | out,output  |         |            |                        |          |       |       |         |

|       | out,output  |         |            |                        |          |       |       |         |

| sdmmc | out,output  | delay   | to,p20 8,  | o15 1,t5,-             | 3,3,4,   |       |       |         |

| sdmmc | out,output  | delay   | to,p20 10  | p15 1,t5,              | -3,3,4,  |       |       |         |

| sdmmc | out,output  | delay   | to,p20_11  | p15_1,t5,              | -3,3,4,  |       |       |         |

| sdmmc | out,output  | delay   | to,p20_12  | p15 1,t5,              | -3,3,4,  |       |       |         |

| sdmmc | out,output  | delay   | to,p20_13  | p15_1,t5,              | -3,3,4,  |       |       |         |

| sdmmc | out,output  | delay   | to,p20_14  | ,p15 <sup>1</sup> ,t5, | -3,3,4,  |       |       |         |

| sdmmc | out,output  | delay   | to,p15_0,  | 015_1,t5,-             | 3,3,4,   |       |       |         |

| sdmmc | in,output o | delay t | co,p15 3,p | 15 1,t5,2.             | 5,6.3,0, |       |       |         |

If IO Timing Parameters are specified in the datasheet, extract them to a csv (comma separated vector) format file.

If parameters are not available in the datasheet, extract them from STA report into a csv file.

www.PosterPresentations.co

Infineon Technologies Asia Pacific Pte Ltd, 8 Kallang Sector, SINGAPORE. 349282.

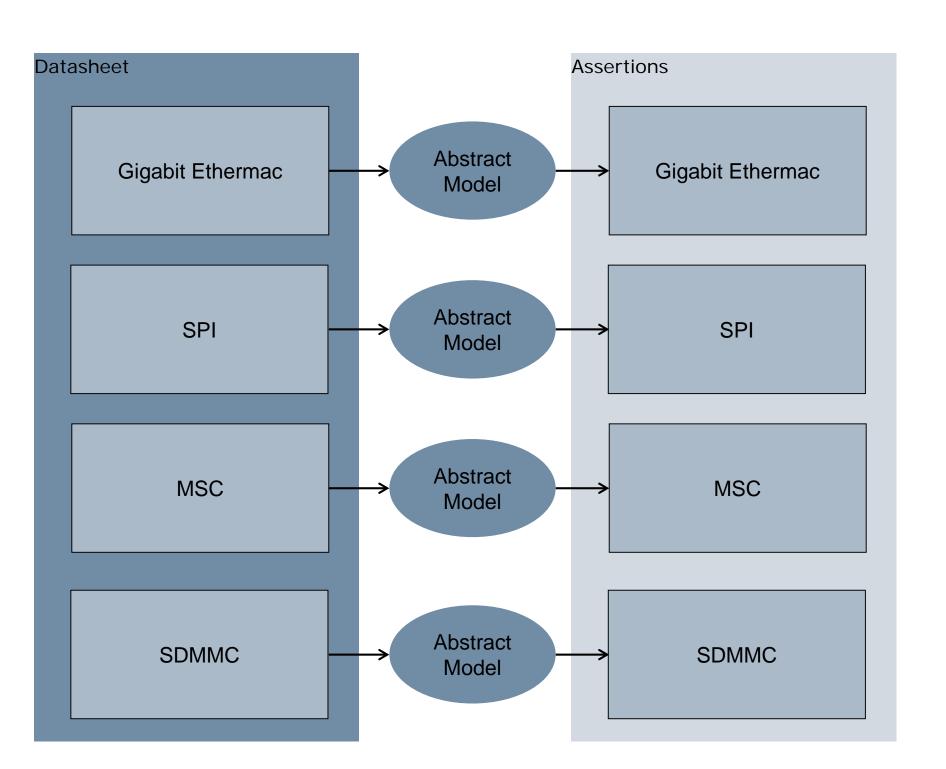

# Abstract Model

The abstract model to generate the assertions is written in SLN. It can be reused for different modules i.e. Gigabit Ethermac, SPI, MSC and SDMMC etc

[var index : uint = 0;]> <[table from csv to table(LIST OF MODULES, "TC38x") with { ]> <[table from csv to table(DATASHEET PARAMS FILE, "<#Peripheral>", ((csv column("Check Mode") == "Clock duty e deviation at"))) with { ]> wire <##Peripheral>\_dcd<(index)>\_enable assign <##Peripheral> dcd<(index)> enable =

check\_deviation #(.pClkPeriod(pClkPeriod), .pMaxDelay(<#Max>ns), .pMinDelay(<#Min>ns),.msg("AssertFail Duty Cycle Deviation in <#Mode> mode for clock on port <#Clk\_Port> ")) <##Peripheral>\_dcd<(index) (<#Clk\_Port>, global\_enable\_iotiming\_checks && <##Peripheral>\_enable\_iotiming\_checks && <##Peripheral>\_dcd<(index enable); <[index = index+] <[};]>

<[index = 0;]> <[table from csv to table(DATASHEET PARAMS FILE, "<#Peripheral>", ((csv\_column("Check Mode") == "output del '))) with { ] wire <##Peripheral> od<(index)> enable; assign <##Peripheral> od<(index)> enable =

check\_delay #(.pDataOffset(<#Offset>ns), .pMaxDelay(<#Max>ns),.pMinDelay(<#Min>ns), .msg("AssertFaile )>:Output Delay Deviation in <#Mode> mode, clk=<#Clk Port>, sig=<#Sig Port>")) <##Peripheral> od<(inde x)> (<#Clk\_Port>,<#Sig\_Port>, global\_enable\_iotiming\_checks && <##Peripheral>\_enable\_iotiming\_checks && <##Peripheral>\_enable\_iotiming\_checks & >> (<#Clk\_Port>,<#Sig\_Port>, global\_enable\_iotiming\_checks & >> (<#Clk\_Port>,</#Sig\_Port>, global\_enable\_iotiming\_checks & >> (<#Clk\_Port>,<#Sig\_Port>, global\_enable\_iotiming\_checks & >> (<#Clk\_Port>,<#Sig\_Port>,<#Sig\_Port>, global\_enable\_iotiming\_checks & >> (<#Clk\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig\_Port>,<#Sig ral> od<(index)> enable); <[index = index+1;] <[};]>

<[3:1>

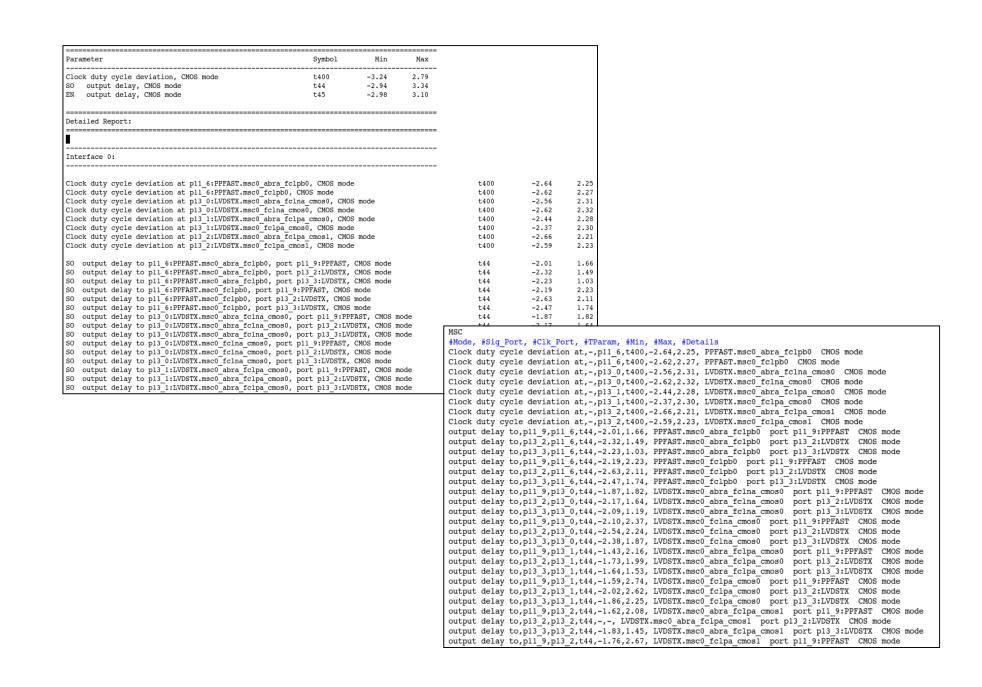

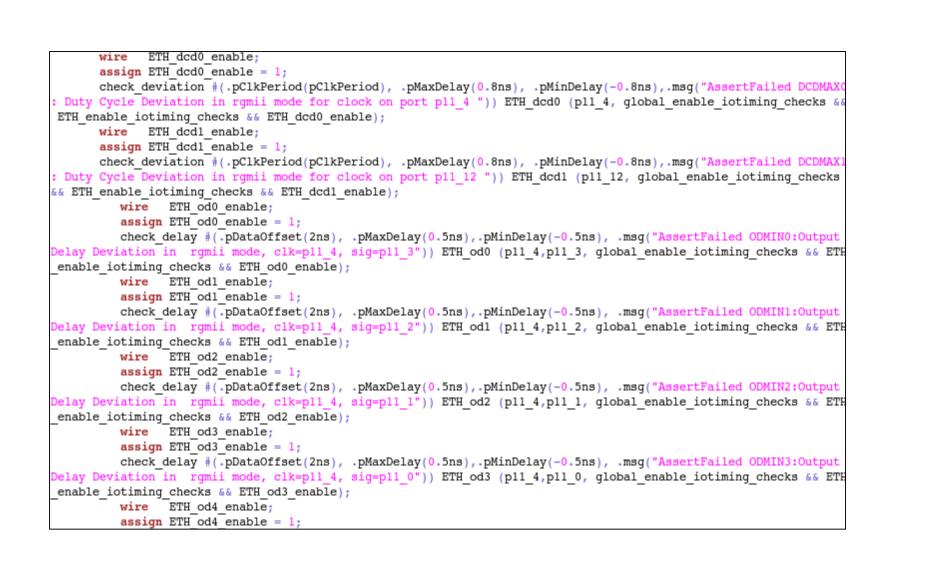

#### Perspec generated assertions

The code snippet above shows how Perspec reads the timing parameters from the csv files to generate all the required assertions for Ethermac module. Similar assertions are generated for all the modules.

Look at all the steps together in the snippet below which highlights how information from datasheet csv is extracted and instantiated in the generated assertions

| Rasic  | Assertions  |

|--------|-------------|

| Dasici | 73351110113 |

| <pre>module check_delay(input clk, input data, input enable_cond);</pre>                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>parameter string msg = "AssertFailed : Output delay violation";<br/>parameter realtime pMaxDelay = 20ns;<br/>parameter realtime pMinDelay = 10ns;<br/>parameter realtime pDataOffset = 0ns; //This should be more than modulo(maxium of all the min delays)</pre> |

| <pre>wire data_del; assign #pDataOffset data_del = data;</pre>                                                                                                                                                                                                         |

| <pre>realtime tClkEdge =0;<br/>realtime tDataEdge=0;<br/>//store delta time<br/>always begin<br/>@(clk);<br/>if(enable_cond) begin<br/>tClkEdge = \$realtime;<br/>end<br/>end</pre>                                                                                    |

| <pre>always begin<br/>@(data_del);<br/>if(enable_cond) begin<br/>tDataEdge = \$realtime - tClkEdge - pDataOffset;<br/>a_delta_delay: assert ((tDataEdge &lt; pMaxDelay) &amp;&amp; (tDataEdge &gt;= pMinDelay))<br/>else<br/>begin</pre>                               |

| endmodule                                                                                                                                                                                                                                                              |

Basic assertion to check output delay parameter

| <pre>module check_deviation(input clk, input enable_cond);</pre>                                    |

|-----------------------------------------------------------------------------------------------------|

| <pre>parameter string msg = "AssertFailed : clock cyle deviation violation";</pre>                  |

| <pre>parameter realtime pMaxDelay = 20ns;</pre>                                                     |

| <pre>parameter realtime pMinDelay = 10ns;</pre>                                                     |

| <pre>parameter realtime pClkPeriod = 200ns;</pre>                                                   |

| <pre>realtime tClkPosEdge =0;</pre>                                                                 |

| <pre>realtime tClkDeviation=0;</pre>                                                                |

| //store delta time                                                                                  |

| always begin                                                                                        |

| <pre>@(posedge clk);</pre>                                                                          |

| if(enable cond) begin                                                                               |

| tClkPosEdge = \$realtime;                                                                           |

| <pre>@(negedge clk);</pre>                                                                          |

| tClkDeviation = <pre>\$realtime - tClkPosEdge - pClkPeriod/2;</pre>                                 |

| a check deviation: assert ((tClkDeviation < pMaxDelay) && (tClkDeviation >= pMinDelay))             |

| else                                                                                                |

| begin                                                                                               |

| <pre>\$error(msg);</pre>                                                                            |

| <pre>\$display("\t(actual=%3.3f, min=%3.3f,max=%3.3f)\n",tClkDeviation, pMinDelay,pMaxDelay);</pre> |

| end                                                                                                 |

| end                                                                                                 |

| end                                                                                                 |

| endmodule                                                                                           |

Basic assertion to check clock cycle deviation parameter

Complete Flow

| 1    | ETH,,,,,,,,                                                                                                                   |

|------|-------------------------------------------------------------------------------------------------------------------------------|

| 2    | #Mode, #Check Mode, #Sig Port, #Clk Port, #TParam, #Min, #Max, #Offset                                                        |

|      | rqmii,Clock duty cycle deviation at,8,pll 4,t19,-0.8,0.8,,                                                                    |

|      | rgmii,Clock duty cycle deviation at,8,pl1 12,t19,-0.8,0.8,,                                                                   |

|      | rqmii,output delay to,pll 3,pll 4,t20,-0.5,0.5,2,                                                                             |

|      | rgmii,output delay to,p11 2, <b>p</b> 11 4,t20,-0.5,0.5,2,                                                                    |

|      | rgmii,output delay to,p11 1,p11 4,t20,-0.5,0.5,2,                                                                             |

|      | rgmii,output delay to,p11 0,p11 4,t20,-0.5,0.5,2,                                                                             |

|      | rgmii,output delay to,p11 10,p11 12,t21,1,2.6,0,                                                                              |

|      | rgmii,output delay to,p11 9,p11 12,t22,1,2.6,0,                                                                               |

|      | rgmii,output delay to,p11 8,p11 12,t23,1,2.6,0,                                                                               |

|      | rgmii,output delay to,p11 7,p11 12,t24,1,2.6,0,                                                                               |

| 13   |                                                                                                                               |

|      | 9x ds auto.csv                                                                                                                |

| 116  |                                                                                                                               |

| 117  |                                                                                                                               |

| 118  | assign <##Peripheral> od<(index)> enable = 1;                                                                                 |

| 119  |                                                                                                                               |

| 119  | <pre>check_delay #(.pDataOffset(&lt;#Offset&gt;ns), .pMaxDelay(&lt;#Max&gt;ns),.pMinDelay(&lt;#Min&gt;ns), .m</pre>           |

|      | t Delay Deviation in <#Mode> mode, clk=<#Clk_Port>, sig=<#Sig_Port>")) <##Peripheral>_od<(index)                              |

| 120  | nable_iotiming_checks && <##Peripheral>_enable_iotiming_checks && <##Peripheral>_od<(index)>_ena                              |

| 120  | <[index = index+1;]>                                                                                                          |

| 121  | <[};]>                                                                                                                        |

| 122  | <[];]>                                                                                                                        |

|      | t_cfg.sln [RO]                                                                                                                |

| 195  | wire ETH_od0_enable;                                                                                                          |

| 196  |                                                                                                                               |

| 197  |                                                                                                                               |

|      | rgmii mode, clk=pl1_4, sig=pl1_3")) ETH_od0 (pl1_4,pl1_3, global_enable_iotiming_checks && ETH_                               |

|      | ble);                                                                                                                         |

| 198  | wire ETH_odl_enable;                                                                                                          |

| 199  |                                                                                                                               |

| 200  |                                                                                                                               |

|      | rgmii mode, clk= <mark>pll_4</mark> , sig=pll_2")) ETH_odl ( <mark>pll_4</mark> ,pll_2, global_enable_iotiming_checks && ETH_ |

|      | ble);                                                                                                                         |

| 201  | /                                                                                                                             |

| 202  |                                                                                                                               |

| 203  |                                                                                                                               |

|      | rgmii mode, clk= <pre>pll_4</pre> , sig=pll_1")) ETH_od2 ( <pre>pll_4</pre> ,pll_1, global_enable_iotiming_checks && ETH_     |

|      | ble);                                                                                                                         |

| 204  | wire ETH_od3_enable;                                                                                                          |

| 205  | assign ETH_od3_enable = 1;                                                                                                    |

| 206  | <pre>check_delay #(.pDataOffset(2ns), .pMaxDelay(0.5ns),.pMinDelay(-0.5ns), .msg("AssertFai</pre>                             |

|      | rgmii mode, clk=pll_4, sig=pll_0")) ETH_od3 (pll_4,pll_0, global_enable_iotiming_checks && ETH_                               |

|      | ble);                                                                                                                         |

| 207  | wire ETH od4 enable;                                                                                                          |

| 208  | assign ETH od4 enable = 1;                                                                                                    |

| 6    |                                                                                                                               |

| 0    |                                                                                                                               |

| qen. | /TC38x/playground 1/io timing assertions.sv                                                                                   |

| <br>io | tim  | ing    |

|--------|------|--------|

| <br>4  | _\$\ | /ac    |

|        |      |        |

|        |      |        |

|        |      |        |

|        |      |        |

|        |      |        |

|        |      |        |

|        |      |        |

|        |      | ŧ      |

|        |      | i      |

|        |      |        |

|        |      | :<br>+ |

|        |      | ±      |

|        |      |        |

|        |      |        |

|        | ÷    |        |

|        | ÷    | l      |

|        | ÷    |        |

Clock duty cycle check fails because testcase changed the clock frequency midway through the simulation.

Some output delay checks pass while some fail. This would require offline debug using logs and waveforms.

Use of SVA to verify IO timings is very useful. However manually creating all the required assertions could be very challenging. Deploying the power of portable stimulus using Cadence's Perspec tool helps to overcome these challenges with minimal effort in modelling and scripting. A successful regression with these assertions running in full timing gate level simulation gives a very high confidence for the IO timing sign off.

8, Ka Singa

# Simulation results for Gigabit Ethermac

| iotiming_sva.dcd0.clk 1                                                           |                                |                                  |                                           |                                 |                                        |                                             |

|-----------------------------------------------------------------------------------|--------------------------------|----------------------------------|-------------------------------------------|---------------------------------|----------------------------------------|---------------------------------------------|

| <pre></pre>                                                                       |                                | finished                         |                                           | fin <b>⊳ <sup>©</sup> faile</b> | đ                                      | fin 🖡 😫 failed                              |

| ≤_sva.dcd0.clk 1                                                                  |                                |                                  |                                           |                                 |                                        |                                             |

| <pre>sva.dcd0.a_check_deviation.a_check_deviation finished (inactive</pre>        |                                | finished                         |                                           | fin 🎙 🍄 faile                   | đ                                      | fin> 🎖 failed                               |

| a_check_deviation contributors (1) simulator::iotiming<br>iotiming_sva.dcd1.clk 0 | _sva.dcd0.a_check_deviation.a_ | _check_deviation contributors    |                                           |                                 |                                        |                                             |

| <pre></pre>                                                                       |                                | finished                         |                                           |                                 | d                                      | fin) 🖓 failed                               |

|                                                                                   | _                              |                                  |                                           |                                 |                                        |                                             |

| ⊕ <u>™</u> II iotiming_sva.od7.a_delta_delay.a_delta_delay                        | 🙁 failed                       | 🎖 failed                         |                                           |                                 |                                        |                                             |

| ⊕… <sup>_</sup>                                                                   | <pre>\$ failed 1</pre>         | * failed                         |                                           |                                 | 7                                      |                                             |

|                                                                                   | 1                              | S failed<br>finished             |                                           |                                 | ANNANAA<br>Stailed                     |                                             |

| iotiming_sva.dcd0.clk                                                             | 1                              |                                  |                                           |                                 | AAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAA |                                             |

|                                                                                   | 1<br>on finished<br>1          |                                  |                                           |                                 | failed                                 |                                             |

| iotiming_sva.dcd0.clk<br>⊡ <mark>m</mark> 1                                       | 1<br>on finished<br>1          | finished<br>finished<br>finished | www.www.<br>www.www.<br>sva.dcd0.a_check_ | deviation.a_ch                  |                                        | <b>กลากสามากการการการ</b><br>การการ         |

|                                                                                   | 1<br>on finished<br>1          | finished<br>finished<br>finished | sva.dcd0.a_check                          | deviation.a_ch                  | S failed                               | กกกกกกกกกกกกกกกก<br>กการ<br>กกกกกกกกกกกกกกก |

| Baseline ▼= 1,817,312.27825ns<br>Baseline ▼= -7.95675ns            |                |       |                                  |                       |                               |               | l           | TimeA = 1,81  | ,817,312.27825ns<br>7,304.3215ns | I           |             |

|--------------------------------------------------------------------|----------------|-------|----------------------------------|-----------------------|-------------------------------|---------------|-------------|---------------|----------------------------------|-------------|-------------|

|                                                                    | o - Cursor     | r ¢≖  |                                  | 500,000ns             | 1,000                         | ,000ns        | 1,500,000ns |               | 000,000ns                        | 2,500,000ns | 3,00        |

| iotiming_sva.od0.clk                                               | 1              |       |                                  |                       |                               |               |             |               |                                  |             |             |

| iotiming_sva.od0.data                                              | 0              |       |                                  |                       |                               |               |             |               |                                  |             |             |

| iotiming_sva.od0.a_delta_delay.a_delta_delay                       | 🔹 📀 fail       | Led   | finished                         |                       | Sail▶ finished                |               | <b>8</b> I: | ail) finished | 🍣 failed                         |             | (finished   |

| iotiming_sva.od1.clk                                               | 1              |       |                                  |                       |                               |               |             |               |                                  |             |             |

| iotiming_sva.od1.data                                              | U<br>0 (1) (1) |       | 1 1 1 1 1 1 1                    |                       |                               |               |             |               |                                  |             |             |

| iotiming_sva.od1.a_delta_delay.a_delta_delay                       | 🚯 fail         | Lea   | finished                         |                       | Sail▶ finished                |               | <b>1</b>    | ail) finished | 🏶 failed                         |             | finished    |

| iotiming_sva.od2.clk                                               | 1              |       |                                  |                       |                               |               |             |               |                                  |             |             |

| iotiming_sva.od2.data                                              | 0              | l e d | finished                         |                       | <pre>\$ fail▶ (finished</pre> | 2 6 . i 1 . d |             | finished      | 🏶 failed                         |             | (finished ) |

| iotiming_sva.od2.a_delta_delay.a_delta_delay                       |                | reu   | THISNED                          |                       | • Talle Thushed               | • LATIEN      |             | Thirsten      | • IAIIEU                         |             | THITSHEE    |

| iotiming_sva.od3.clk                                               | <u>^</u>       |       |                                  |                       |                               |               |             |               |                                  |             |             |

| iotiming_sva.od3.data                                              | • 📀 fail       | lad   | finished                         |                       | <pre>\$ fail▶ finished</pre>  | 2 failed      |             | finished      | 📽 failed                         |             | finished    |

| iotiming_sva.od3.a_delta_delay.a_delta_delay                       |                | Leu   | THUSHED                          |                       | • Tail) Thushed               | . laiieu      |             | Thusheu       | • Talleu                         |             | THISNEY     |

| iotiming_sva.od4.clk<br>iotiming_sva.od4.data                      | ů              |       |                                  |                       |                               |               |             |               |                                  |             |             |

| iotiming_sva.od4.a_delta_delay.a_delta_delay                       | •<br>• fail    | led   | <pre>\$ failed</pre>             |                       | 🏶 failed                      |               |             |               |                                  |             |             |

| iotiming_sva.od4.a_dena_delay.a_dena_delay<br>iotiming_sva.od5.clk | 0              |       |                                  |                       | 0 101100                      |               |             |               |                                  |             |             |

| iotiming_sva.od5.data                                              | ů              |       |                                  |                       |                               |               |             |               |                                  |             |             |

| iotiming_sva.od5.a_delta_delay.a_delta_delay                       | •<br>• fail    | led   | <pre>\$ failed</pre>             |                       | failed                        |               |             | -             |                                  |             |             |

| iotiming_sva.od6.clk                                               | 0              |       |                                  |                       |                               |               |             |               |                                  |             |             |

| iotiming_sva.od6.data                                              | ů              |       |                                  |                       |                               |               |             |               |                                  |             |             |

| iotiming_sva.od6.a_delta_delay.a_delta_delay                       | s fail         | led   | <pre>\$ failed</pre>             | l                     | failed                        | ]             |             |               |                                  |             |             |

| iotiming_sva.od0.a_uena_uelay.a_uena_uelay<br>iotiming_sva.od7.clk | 0              |       |                                  |                       | a rantea                      |               |             |               |                                  |             |             |

| iotiming_sva.od7.data                                              | 0              |       |                                  |                       |                               |               |             | 11            |                                  |             |             |

| iotiming_sva.od7.a_delta_delay.a_delta_delay                       | 😵 fail         | led   | <pre>\$ failed</pre>             |                       | S failed                      |               |             |               |                                  |             |             |

| iotiming_sva.dcd0.clk                                              | 1              |       |                                  |                       |                               |               |             |               |                                  |             |             |

| <pre>{va.dcd0.a_check_deviation.a_check_deviati</pre>              | on finish      | ed    | inactive                         |                       | finished                      |               | l fi        | in) 😫 failed  |                                  | (fint)      | failed      |

| sva.dcd0.clk                                                       | 1              |       |                                  |                       |                               |               |             |               |                                  |             |             |

|                                                                    | tion finish    | ed    | inactive                         |                       | finished                      |               | fi          | in) 😫 failed  |                                  | fin> 1      | ailed 3     |

|                                                                    |                |       | simulator::iotiming_sva.dcd0.a_c | heck_deviation.a_chec | ck_deviation contributo       | rs            |             |               |                                  |             |             |

| otiming_sva.dcd1.clk                                               | 0              |       |                                  |                       |                               |               |             |               |                                  |             |             |

| _sva.dcd1.a_check_deviation.a_check_devia                          | tion finish    | ed    | (inactive                        |                       | finished                      |               | fi          | in🕨 🏶 failed  |                                  | (fin)       | failed      |

#### Summary

### Contact information

Infineon Technologies Asia Pacific Pte. Ltd.

| llang Sector, | T: +65 6876 2096                   |

|---------------|------------------------------------|

| apore. 349282 | E: amitesh.khandelwal@infineon.com |